Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 3KB (2K x 12)                                                             |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                |                                                                           |

| RAM Size                   | 73 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                               |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c58b-40-ss |

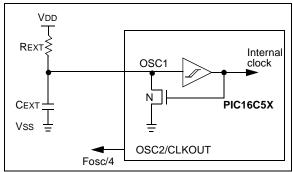

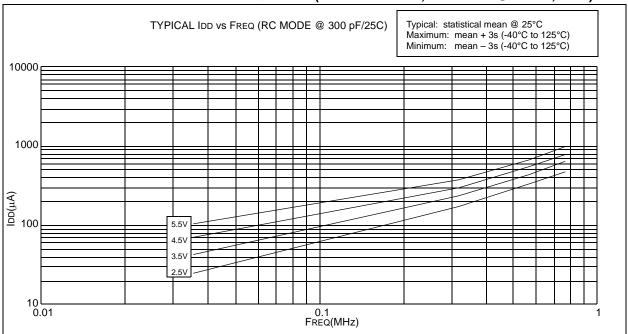

#### 4.4 RC Oscillator

For timing insensitive applications, the RC device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used.

Figure 4-5 shows how the R/C combination is connected to the PIC16C5X. For REXT values below 2.2 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high REXT values (e.g., 1 M $\Omega$ ) the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend keeping REXT between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (CEXT = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

The Electrical Specifications sections show RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

Also, see the Electrical Specifications sections for variation of oscillator frequency due to VDD for given REXT/CEXT values as well as frequency variation due to operating temperature for given R, C, and VDD values.

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin, and can be used for test purposes or to synchronize other logic.

#### FIGURE 4-5: RC OSCILLATOR MODE

**Note:** If you change from this device to another device, please verify oscillator characteristics in your application.

#### 6.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral functions to control the operation of the device (Table 6-1).

The Special Registers can be classified into two sets. The Special Function Registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section for each peripheral feature.

TABLE 6-1: SPECIAL FUNCTION REGISTER SUMMARY

| Address            | Name   | Bit 7    | Bit 6                                      | Bit 5       | Bit 4     | Bit 3    | Bit 2     | Bit 1      | Bit 0                    | Value on<br>Power-on<br>Reset | Details<br>on Page |

|--------------------|--------|----------|--------------------------------------------|-------------|-----------|----------|-----------|------------|--------------------------|-------------------------------|--------------------|

| N/A                | TRIS   | I/O Cont | /O Control Registers (TRISA, TRISB, TRISC) |             |           |          |           |            |                          | 1111 1111                     | 35                 |

| N/A                | OPTION | Contains | s control b                                | oits to con | figure Ti | mer0 and | Timer0/V  | VDT pres   | caler                    | 11 1111                       | 30                 |

| 00h                | INDF   | Uses co  | ntents of                                  | FSR to ac   | ddress da | ata memo | ry (not a | physical r | egister)                 | XXXX XXXX                     | 32                 |

| 01h                | TMR0   | Timer0 N | Timer0 Module Register                     |             |           |          |           | XXXX XXXX  | 38                       |                               |                    |

| 02h <sup>(1)</sup> | PCL    | Low ord  | er 8 bits c                                | of PC       |           |          |           |            |                          | 1111 1111                     | 31                 |

| 03h                | STATUS | PA2      | PA1                                        | PA0         | TO        | PD       | Z         | DC         | С                        | 0001 1xxx                     | 29                 |

| 04h                | FSR    | Indirect | Indirect data memory address pointer       |             |           |          |           |            | 1xxx xxxx <sup>(3)</sup> | 32                            |                    |

| 05h                | PORTA  | _        | _                                          | _           | _         | RA3      | RA2       | RA1        | RA0                      | XXXX                          | 35                 |

| 06h                | PORTB  | RB7      | RB6                                        | RB5         | RB4       | RB3      | RB2       | RB1        | RB0                      | XXXX XXXX                     | 35                 |

| 07h <sup>(2)</sup> | PORTC  | RC7      | RC6                                        | RC5         | RC4       | RC3      | RC2       | RC1        | RC0                      | xxxx xxxx                     | 35                 |

Legend: x = unknown, u = unchanged, -= unimplemented, read as '0' (if applicable). Shaded cells = unimplemented or unused

**Note** 1: The upper byte of the Program Counter is not directly accessible. See Section 6.5 for an explanation of how to access these bits.

<sup>2:</sup> File address 07h is a General Purpose Register on the PIC16C54, PIC16CR54, PIC16C56, PIC16CR56, PIC16C58 and PIC16CR58.

<sup>3:</sup> These values are valid for PIC16C57/CR57/C58/CR58. For the PIC16C54/CR54/C55/C56/CR56, the value on RESET is 111x xxxx and for MCLR and WDT Reset, the value is 111u uuuu.

#### 7.6 I/O Programming Considerations

#### 7.6.1 BI-DIRECTIONAL I/O PORTS

Some instructions operate internally as read followed by write operations. The BCF and BSF instructions, for example, read the entire port into the CPU, execute the bit operation and re-write the result. Caution must be used when these instructions are applied to a port where one or more pins are used as input/outputs. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU, bit5 to be set and the PORTB value to be written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (say bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the Input mode, no problem occurs. However, if bit0 is switched into Output mode later on, the content of the data latch may now be unknown.

Example 7-1 shows the effect of two sequential readmodify-write instructions (e.g., BCF, BSF, etc.) on an I/O port.

A pin actively outputting a high or a low should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

# EXAMPLE 7-1: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

```

; Initial PORT Settings

; PORTB<7:4> Inputs

; PORTB<3:0> Outputs

;PORTB<7:6> have external pull-ups and are

; not connected to other circuitry

PORT latch PORT pins

BCF

PORTB, 7

;01pp pppp

11pp pppp

BCF

PORTB. 6

;10pp pppp

11pp pppp

MOVLW H'3F'

;

TRIS

PORTB

;10pp pppp

10pp pppp

; Note that the user may have expected the pin

; values to be 00pp pppp. The 2nd BCF caused

```

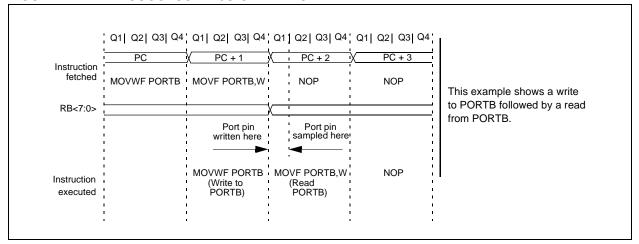

## 7.6.2 SUCCESSIVE OPERATIONS ON I/O PORTS

; RB7 to be latched as the pin value (High).

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 7-2). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should allow the pin voltage to stabilize (load dependent) before the next instruction, which causes that file to be read into the CPU, is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

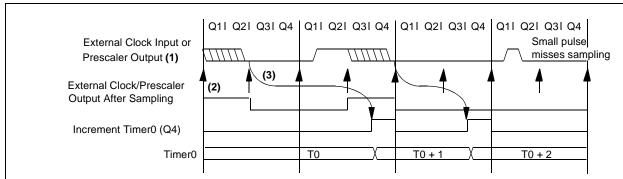

### 8.1 Using Timer0 with an External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

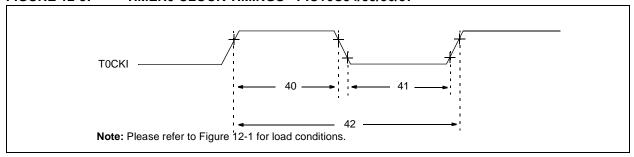

### 8.1.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 8-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple counter-type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 8.1.2 TIMERO INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 8-5 shows the delay from the external clock edge to the timer incrementing.

FIGURE 8-5: TIMERO TIMING WITH EXTERNAL CLOCK

- **Note 1:** External clock if no prescaler selected, prescaler output otherwise.

- 2: The arrows indicate the points in time where sampling occurs.

- 3: Delay from clock input change to Timer0 increment is 3Tosc to 7Tosc (duration of Q = Tosc). Therefore, the error in measuring the interval between two edges on Timer0 input =  $\pm$  4Tosc max.

### PIC16C5X

NOTES:

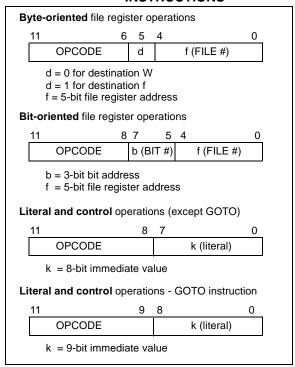

#### 10.0 INSTRUCTION SET SUMMARY

Each PIC16C5X instruction is a 12-bit word divided into an OPCODE, which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16C5X instruction set summary in Table 10-2 groups the instructions into byte-oriented, bit-oriented, and literal and control operations. Table 10-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator is used to specify which one of the 32 file registers in that bank is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8 or 9-bit constant or literal value.

TABLE 10-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                     |

|---------------|-------------------------------------------------|

| f             | Register file address (0x00 to 0x1F)            |

| W             | Working register (accumulator)                  |

| b             | Bit address within an 8-bit file register       |

| k             | Literal field, constant data or label           |

| х             | Don't care location (= 0 or 1)                  |

|               | The assembler will generate code with $x = 0$ . |

|               | It is the recommended form of use for com-      |

|               | patibility with all Microchip software tools.   |

| d             | Destination select;                             |

|               | d = 0 (store result in W)                       |

|               | d = 1 (store result in file register 'f')       |

|               | Default is d = 1                                |

| label         | Label name                                      |

| TOS           | Top of Stack                                    |

| PC            | Program Counter                                 |

| WDT           | Watchdog Timer Counter                          |

| TO            | Time-out bit                                    |

| PD            | Power-down bit                                  |

| dest          | Destination, either the W register or the       |

|               | specified register file location                |

| [ ]           | Options                                         |

| ( )           | Contents                                        |

| $\rightarrow$ | Assigned to                                     |

| < >           | Register bit field                              |

| €             | In the set of                                   |

| italics       | User defined term (font is courier)             |

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time would be 1  $\mu s.$  If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time would be 2  $\mu s.$

Figure 10-1 shows the three general formats that the instructions can have. All examples in the figure use the following format to represent a hexadecimal number:

0xhhh

where 'h' signifies a hexadecimal digit.

### FIGURE 10-1: GENERAL FORMAT FOR INSTRUCTIONS

| CALL                                                                                                                                | Subroutine Call                                                                                                                                             | CLRW                                                                 | Clear W                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                                                             | [ label ] CALL k                                                                                                                                            | Syntax:                                                              | [ label ] CLRW                                                                                                                                                                                                                                                                                                                                                                                       |

| Operands:                                                                                                                           | $0 \leq k \leq 255$                                                                                                                                         | Operands:                                                            | None                                                                                                                                                                                                                                                                                                                                                                                                 |

| Operation:                                                                                                                          | (PC) + 1→ TOS;<br>k → PC<7:0>;                                                                                                                              | Operation:                                                           | $00h \rightarrow (W);$ $1 \rightarrow Z$                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                     | (STATUS<6:5>) → PC<10:9>;<br>0 → PC<8>                                                                                                                      | Status Affected:                                                     | Z                                                                                                                                                                                                                                                                                                                                                                                                    |

| Status Affected:                                                                                                                    | None                                                                                                                                                        | Encoding:                                                            | 0000 0100 0000                                                                                                                                                                                                                                                                                                                                                                                       |

| Encoding:                                                                                                                           | 1001 kkkk kkkk                                                                                                                                              | Description:                                                         | The W register is cleared. Zero bit (Z) is set.                                                                                                                                                                                                                                                                                                                                                      |

| Description:                                                                                                                        | Subroutine call. First, return address (PC+1) is pushed onto the                                                                                            | Words:                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                     | stack. The eight bit immediate                                                                                                                              | Cycles:                                                              | 1                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                     | address is loaded into PC bits                                                                                                                              | Example:                                                             | CLRW                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                     | <7:0>. The upper bits PC<10:9> are loaded from STATUS<6:5>, PC<8> is cleared. CALL is a two-cycle instruction.                                              | After Instruc                                                        | = 0x5A                                                                                                                                                                                                                                                                                                                                                                                               |

| Words:                                                                                                                              | 1                                                                                                                                                           | Z =                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                      |

| Cycles:                                                                                                                             | 2                                                                                                                                                           |                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                      |

| _                                                                                                                                   |                                                                                                                                                             |                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                      |

| Example:                                                                                                                            | HERE CALL THERE                                                                                                                                             | CLRWDT                                                               | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                 |

| Before Instr                                                                                                                        | uction                                                                                                                                                      | CLRWDT                                                               | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                     | uction<br>= address (HERE)                                                                                                                                  | Syntax:                                                              | [ label ] CLRWDT                                                                                                                                                                                                                                                                                                                                                                                     |

| Before Instr<br>PC =<br>After Instruc<br>PC =<br>TOS =                                                                              | uction = address (HERE) ction = address (THERE) = address (HERE + 1)                                                                                        | _                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                      |

| Before Instr<br>PC =<br>After Instruc<br>PC =                                                                                       | uction = address (HERE) ction = address (THERE) = address (HERE + 1)  Clear f                                                                               | Syntax: Operands:                                                    | [ label ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow WDT$ prescaler (if assigned);<br>$1 \rightarrow \overline{10};$                                                                                                                                                                                                                                                                 |

| Before Instruction PC = After Instruction PC = TOS = CLRF Syntax:                                                                   | uction = address (HERE) ction = address (THERE) = address (HERE + 1)  Clear f  [ label ] CLRF f                                                             | Syntax: Operands: Operation:                                         | [ label ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow \frac{WD}{T}$ prescaler (if assigned);<br>$1 \rightarrow \frac{TO}{PD};$<br>$1 \rightarrow \overline{PD}$                                                                                                                                                                                                                       |

| Before Instruction PC = After Instruction PC = TOS =  CLRF  Syntax: Operands:                                                       | uction = address (HERE) ction = address (THERE) = address (HERE + 1)  Clear f  [ label ] CLRF f  0 \le f \le 31                                             | Syntax: Operands: Operation: Status Affected:                        | [ label ] CLRWDT<br>None<br>$00h \rightarrow WDT$ ;<br>$0 \rightarrow WDT$ prescaler (if assigned);<br>$1 \rightarrow \overline{TO}$ ;<br>$1 \rightarrow \overline{PD}$<br>$\overline{TO}$ , $\overline{PD}$                                                                                                                                                                                         |

| Before Instruction PC = After Instruction PC = TOS = CLRF Syntax:                                                                   | uction = address (HERE) ction = address (THERE) = address (HERE + 1)  Clear f  [ $label$ ] CLRF f $0 \le f \le 31$ $00h \rightarrow (f)$ ;                  | Syntax: Operands: Operation: Status Affected: Encoding:              | [ label ] CLRWDT  None $00h \rightarrow WDT;$ $0 \rightarrow WDT$ prescaler (if assigned); $1 \rightarrow \overline{TO};$ $1 \rightarrow \overline{PD}$ $\overline{TO}, \overline{PD}$ $0000  0000  0100$ The CLRWDT instruction resets the WDT. It also resets the prescaler, if                                                                                                                    |

| Before Instruction PC = After Instruction PC = TOS =  CLRF  Syntax: Operands: Operation:  Status Affected:                          | uction = address (HERE) ction = address (THERE) = address (HERE + 1)  Clear f  [ label ] CLRF f $0 \le f \le 31$ $00h \rightarrow (f);$ $1 \rightarrow Z$ Z | Syntax: Operands: Operation: Status Affected: Encoding:              | [ label ] CLRWDT  None $00h \rightarrow WDT;$ $0 \rightarrow WDT$ prescaler (if assigned); $1 \rightarrow \overline{TO};$ $1 \rightarrow \overline{PD}$ $\overline{TO}, \overline{PD}$ $0000  0000  0100$ The CLRWDT instruction resets the                                                                                                                                                          |

| Before Instruction PC = After Instruction PC = TOS = TOS =  CLRF  Syntax: Operands: Operands: Operation: Status Affected: Encoding: | uction = address (HERE) etion = address (THERE) = address (HERE + 1)  Clear f  [ label ] CLRF f $0 \le f \le 31$ $00h \rightarrow (f);$ $1 \rightarrow Z$ Z | Syntax: Operands: Operation: Status Affected: Encoding:              | [ label ] CLRWDT  None $00h \rightarrow WDT$ ; $0 \rightarrow WDT$ prescaler (if assigned); $1 \rightarrow \overline{10}$ ; $1 \rightarrow \overline{PD}$ $\overline{TO}$ , $\overline{PD}$ $0000  0000  0100$ The CLRWDT instruction resets the WDT. It also resets the prescaler, if the prescaler is assigned to the WDT and not Timer0. Status bits                                              |

| Before Instruction PC = After Instruction PC = TOS =  CLRF  Syntax: Operands: Operation:  Status Affected:                          | uction = address (HERE) ction = address (THERE) = address (HERE + 1)  Clear f  [ label ] CLRF f $0 \le f \le 31$ $00h \rightarrow (f);$ $1 \rightarrow Z$ Z | Syntax: Operands: Operation: Status Affected: Encoding: Description: | [ label ] CLRWDT  None $00h \rightarrow WDT$ ; $0 \rightarrow WDT$ prescaler (if assigned); $1 \rightarrow \overline{TO}$ ; $1 \rightarrow \overline{PD}$ $\overline{TO}$ , $\overline{PD}$ $0000  0000  0100$ The CLRWDT instruction resets the WDT. It also resets the prescaler, if the prescaler is assigned to the WDT and not Timer0. Status bits $\overline{TO}$ and $\overline{PD}$ are set. |

Before Instruction

After Instruction

TO

$\overline{\mathsf{PD}}$

WDT counter =

WDT counter =

WDT prescaler =

0x00

0

1

1

Before Instruction

After Instruction

Ζ

FLAG\_REG =

FLAG\_REG =

CLRF

FLAG\_REG

0x5A

0x00

1

Cycles:

Example:

### PIC16C5X

| COMF                                                 | Complement f                                                                                                                                              |                   |      |  |  |  |  |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|--|--|--|--|

| Syntax:                                              | [ label ]                                                                                                                                                 | COMF              | f,d  |  |  |  |  |

| Operands:                                            | $0 \le f \le 31$<br>$d \in [0,1]$                                                                                                                         |                   |      |  |  |  |  |

| Operation:                                           | $(\overline{f}) \rightarrow (de$                                                                                                                          | est)              |      |  |  |  |  |

| Status Affected:                                     | Z                                                                                                                                                         |                   |      |  |  |  |  |

| Encoding:                                            | 0010                                                                                                                                                      | 01df              | ffff |  |  |  |  |

| Description:                                         | The contents of register 'f' are complemented. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'. |                   |      |  |  |  |  |

| Words:                                               | 1                                                                                                                                                         |                   |      |  |  |  |  |

| Cycles:                                              | 1                                                                                                                                                         |                   |      |  |  |  |  |

| Example:                                             | COMF                                                                                                                                                      | REG1,0            |      |  |  |  |  |

| Before Instru<br>REG1<br>After Instruct<br>REG1<br>W | = 02<br>ion<br>= 02                                                                                                                                       | x13<br>x13<br>xEC |      |  |  |  |  |

| DECF                                                    | Decrement f                                                                                                                        |            |      |  |  |  |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------|------|--|--|--|

| Syntax:                                                 | [ label ]                                                                                                                          | DECF f,    | d    |  |  |  |

| Operands:                                               | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                     |            |      |  |  |  |

| Operation:                                              | $(f) - 1 \rightarrow$                                                                                                              | (dest)     |      |  |  |  |

| Status Affected:                                        | Z                                                                                                                                  |            |      |  |  |  |

| Encoding:                                               | 0000                                                                                                                               | 11df       | ffff |  |  |  |

| Description:                                            | Decrement register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'. |            |      |  |  |  |

| Words:                                                  | 1                                                                                                                                  |            |      |  |  |  |

| Cycles:                                                 | 1                                                                                                                                  |            |      |  |  |  |

| Example:                                                | DECF                                                                                                                               | CNT,       | 1    |  |  |  |

| Before Instru<br>CNT<br>Z<br>After Instruct<br>CNT<br>Z | = 0:<br>= 0<br>tion                                                                                                                | x01<br>x00 |      |  |  |  |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ label ] DECFSZ f,d                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 31$                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|                  | d ∈ [0,1]                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| Operation:       | $(f) - 1 \rightarrow d$ ; skip if result = 0                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| Encoding:        | 0010 11df ffff                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are decremented. If 'd' is 0 the result is placed in the W register. If 'd' is 1 the result is placed back in register 'f'.  If the result is 0, the next instruction, which is already fetched, is discarded and a NOP is executed instead making it a two-cycle instruction. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| Example:         | HERE DECFSZ CNT, 1                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|                  | GOTO LOOP CONTINUE •                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| Before Instru    | uction                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| PC               | = address (HERE)                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| After Instruct   |                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| CNT              | = CNT - 1;                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| if CNT<br>PC     | = 0,                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| if CNT           | = address (CONTINUE);<br>≠ 0.                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| PC               | = address (HERE+1)                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| RLF                                         | Rotate Left f through Carry                                                                                                                                                                                 |                                   |       |      |  |  |  |  |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------|------|--|--|--|--|

| Syntax:                                     | [ label                                                                                                                                                                                                     | ] RLF                             | f,c   | I    |  |  |  |  |

| Operands:                                   |                                                                                                                                                                                                             | $0 \le f \le 31$<br>$d \in [0,1]$ |       |      |  |  |  |  |

| Operation:                                  | See de                                                                                                                                                                                                      | escripti                          | on be | elow |  |  |  |  |

| Status Affected:                            | С                                                                                                                                                                                                           |                                   |       |      |  |  |  |  |

| Encoding:                                   | 0011                                                                                                                                                                                                        | 010                               | df    | ffff |  |  |  |  |

| Description:                                | The contents of register 'f' are rotated one bit to the left through the Carry Flag (STATUS<0>). If 'd' is 0 the result is placed in the W register. If 'd' is 1 the result is stored back in register 'f'. |                                   |       |      |  |  |  |  |

| Words:                                      | 1                                                                                                                                                                                                           |                                   |       |      |  |  |  |  |

| Cycles:                                     | 1                                                                                                                                                                                                           |                                   |       |      |  |  |  |  |

| Example:                                    | RLF                                                                                                                                                                                                         | REG                               | 1,0   |      |  |  |  |  |

| Before Instru<br>REG1<br>C<br>After Instruc | =                                                                                                                                                                                                           | 1110<br>0                         | 0110  | 0    |  |  |  |  |

| REG1<br>W                                   | =                                                                                                                                                                                                           | 1110<br>1100                      | 0110  | -    |  |  |  |  |

| C                                           | =                                                                                                                                                                                                           | 1                                 | 1100  | U    |  |  |  |  |

| RRF                                                                              | Rotate Right f through Carry                                                                                                                                                                                 |           |       |      |  |  |  |

|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|------|--|--|--|

| Syntax:                                                                          | [ label                                                                                                                                                                                                      | '] RF     | RF f, | d    |  |  |  |

| Operands:                                                                        | $0 \le f \le d \in [0]$                                                                                                                                                                                      |           |       |      |  |  |  |

| Operation:                                                                       | See description below                                                                                                                                                                                        |           |       |      |  |  |  |

| Status Affected:                                                                 | С                                                                                                                                                                                                            |           |       |      |  |  |  |

| Encoding:                                                                        | 0011                                                                                                                                                                                                         | . 00      | df    | ffff |  |  |  |

| Description:                                                                     | The contents of register 'f' are rotated one bit to the right through the Carry Flag (STATUS<0>). If 'd' is 0 the result is placed in the W register. If 'd' is 1 the result is placed back in register 'f'. |           |       |      |  |  |  |

| Words:                                                                           | 1                                                                                                                                                                                                            |           |       |      |  |  |  |

| Cycles:                                                                          | 1                                                                                                                                                                                                            |           |       |      |  |  |  |

| Example:                                                                         | RRF                                                                                                                                                                                                          | REC       | 31,0  |      |  |  |  |

| Before Instruction  REG1 = 1110 0110  C = 0  After Instruction  REG1 = 1110 0110 |                                                                                                                                                                                                              |           |       |      |  |  |  |

| W<br>C                                                                           | =                                                                                                                                                                                                            | 0111<br>0 | 001   | 1    |  |  |  |

| SLEEP            | Enter SLEEP Mode                                                                                                                                                                                                            |       |      |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|--|--|--|--|

| Syntax:          | [label]                                                                                                                                                                                                                     | SLEEP |      |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                        |       |      |  |  |  |  |

| Operation:       | 00h → WDT;<br>0 → WDT prescaler; if assigned<br>1 → $\overline{TO}$ ;<br>0 → $\overline{PD}$                                                                                                                                |       |      |  |  |  |  |

| Status Affected: | $\overline{TO}, \overline{PD}$                                                                                                                                                                                              |       |      |  |  |  |  |

| Encoding:        | 0000                                                                                                                                                                                                                        | 0000  | 0011 |  |  |  |  |

| Description:     | Time-out status bit (TO) is set. The power-down status bit (PD) is cleared. The WDT and its prescaler are cleared. The processor is put into SLEEP mode with the oscillator stopped. See section on SLEEP for more details. |       |      |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                           |       |      |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                           |       |      |  |  |  |  |

| Example:         | SLEEP                                                                                                                                                                                                                       |       |      |  |  |  |  |

### 12.4 DC Characteristics: PIC16C54/55/56/57-RC, XT, 10, HS, LP (Commercial) PIC16C54/55/56/57-RCI, XTI, 10I, HSI, LPI (Industrial)

| DC CH        | ARACTE | RISTICS                                                                                                                                       | Standard Operating Conditions (unless otherwise specified) Operating Temperature $0^{\circ}C \leq TA \leq +70^{\circ}C \text{ for commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \text{ for industrial}$ |                               |                                                        |                            |                                                                                                                                                                                                        |  |

|--------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No. | Symbol | Characteristic/Device                                                                                                                         | Min                                                                                                                                                                                                             | Тур†                          | Max                                                    | Units                      | Conditions                                                                                                                                                                                             |  |

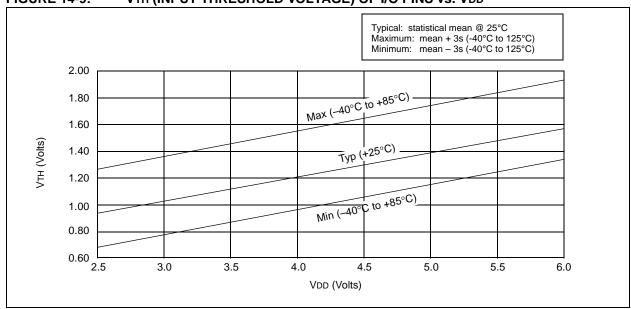

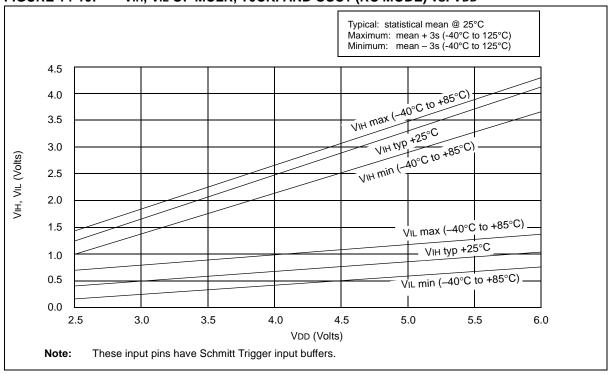

| D030         | VIL    | Input Low Voltage I/O ports MCLR (Schmitt Trigger) T0CKI (Schmitt Trigger) OSC1 (Schmitt Trigger) OSC1 (Schmitt Trigger)                      | Vss<br>Vss<br>Vss<br>Vss<br>Vss                                                                                                                                                                                 | _<br>_<br>_<br>_              | 0.2 VDD<br>0.15 VDD<br>0.15 VDD<br>0.15 VDD<br>0.3 VDD | V<br>V<br>V<br>V           | Pin at hi-impedance PIC16C5X-RC only <sup>(3)</sup> PIC16C5X-XT, 10, HS, LP                                                                                                                            |  |

| D040         | ViH    | Input High Voltage I/O ports I/O ports I/O ports MCLR (Schmitt Trigger) TOCKI (Schmitt Trigger) OSC1 (Schmitt Trigger) OSC1 (Schmitt Trigger) | 0.45 VDD<br>2.0<br>0.36 VDD<br>0.85 VDD<br>0.85 VDD<br>0.85 VDD<br>0.7 VDD                                                                                                                                      |                               | VDD<br>VDD<br>VDD<br>VDD<br>VDD<br>VDD                 | V<br>V<br>V<br>V<br>V      | For all VDD <sup>(4)</sup> 4.0V < VDD ≤ 5.5V <sup>(4)</sup> VDD > 5.5V  PIC16C5X-RC only <sup>(3)</sup> PIC16C5X-XT, 10, HS, LP                                                                        |  |

| D050         | VHYS   | Hysteresis of Schmitt<br>Trigger inputs                                                                                                       | 0.15 VDD*                                                                                                                                                                                                       | _                             | _                                                      | V                          |                                                                                                                                                                                                        |  |

| D060         | IIL    | Input Leakage Current <sup>(1,2)</sup> I/O ports  MCLR MCLR TOCKI OSC1                                                                        | -1<br>-5<br>-3<br>-3                                                                                                                                                                                            | 0.5<br>—<br>0.5<br>0.5<br>0.5 | +1<br><br>+5<br>+3<br>+3                               | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ | For Vdd $\leq$ 5.5V:<br>VSS $\leq$ VPIN $\leq$ VDD,<br>pin at hi-impedance<br>VPIN = VSS + 0.25V<br>VPIN = VDD<br>VSS $\leq$ VPIN $\leq$ VDD<br>VSS $\leq$ VPIN $\leq$ VDD,<br>PIC16C5X-XT, 10, HS, LP |  |

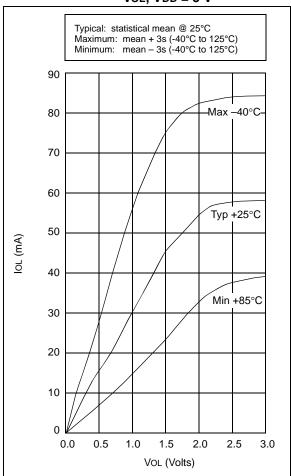

| D080         | Vol    | Output Low Voltage I/O ports OSC2/CLKOUT                                                                                                      | _                                                                                                                                                                                                               | _                             | 0.6<br>0.6                                             | V<br>V                     | IOL = 8.7 mA, VDD = 4.5V<br>IOL = 1.6 mA, VDD = 4.5V,<br>PIC16C5X-RC                                                                                                                                   |  |

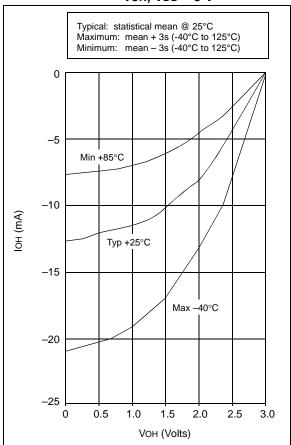

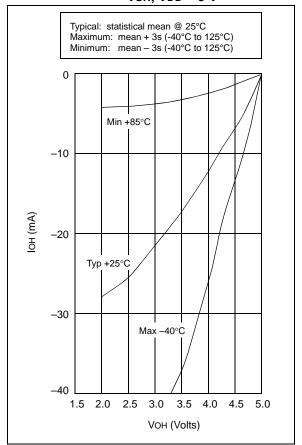

| D090         | Voн    | Output High Voltage <sup>(2)</sup> I/O ports OSC2/CLKOUT                                                                                      | VDD - 0.7<br>VDD - 0.7                                                                                                                                                                                          | _<br>_                        | _<br>_                                                 | V<br>V                     | IOH = -5.4 mA, VDD = 4.5V<br>IOH = -1.0 mA, VDD = 4.5V,<br>PIC16C5X-RC                                                                                                                                 |  |

<sup>\*</sup> These parameters are characterized but not tested.

- 2: Negative current is defined as coming out of the pin.

- **3:** For PIC16C5X-RC devices, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C5X be driven with external clock in RC mode.

- 4: The user may use the better of the two specifications.

<sup>†</sup> Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

**Note 1:** The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltage.

#### FIGURE 12-5: TIMER0 CLOCK TIMINGS - PIC16C54/55/56/57

TABLE 12-4: TIMERO CLOCK REQUIREMENTS - PIC16C54/55/56/57

| AC Ch        | Standard Operating Conditions (unless otherwise specified) Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C \text{ for commercial}$ $-40^{\circ}C \le TA \le +85^{\circ}C \text{ for industrial}$ $-40^{\circ}C \le TA \le +125^{\circ}C \text{ for extended}$ |                                                        |                              |      |     |          |                                                                |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------|------|-----|----------|----------------------------------------------------------------|

| Param<br>No. | Symbol                                                                                                                                                                                                                                                                  | Characteristic                                         | Min                          | Тур† | Max | Units    | Conditions                                                     |

| 40           | Tt0H                                                                                                                                                                                                                                                                    | TOCKI High Pulse Width - No Prescaler - With Prescaler | 0.5 Tcy + 20*<br>10*         |      |     | ns<br>ns |                                                                |

| 41           | Tt0L                                                                                                                                                                                                                                                                    | Tocki Low Pulse Width - No Prescaler - With Prescaler  | 0.5 TcY + 20*<br>10*         | _    | _   | ns<br>ns |                                                                |

| 42           | Tt0P                                                                                                                                                                                                                                                                    | T0CKI Period                                           | 20 or <u>Tcy + 40</u> *<br>N | _    | _   | ns       | Whichever is greater.<br>N = Prescale Value<br>(1, 2, 4,, 256) |

These parameters are characterized but not tested.

<sup>†</sup> Data in the Typical ("Typ") column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### 13.2 DC Characteristics: PIC16CR54A-04E, 10E, 20E (Extended)

| 1. 10 100 110 111 0 12, 102, 202 |        |                                                                              | Standard Operating Conditions (unless otherwise specified) Operating Temperature $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for extended |                   |                 |                          |                                                                                      |

|----------------------------------|--------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------|--------------------------|--------------------------------------------------------------------------------------|

| Param<br>No.                     | Symbol | Characteristic                                                               | Min                                                                                                                                                        | Тур†              | Max             | Units                    | Conditions                                                                           |

| D001                             | VDD    | Supply Voltage<br>RC, XT and LP modes<br>HS mode                             | 3.25<br>4.5                                                                                                                                                | _                 | 6.0<br>5.5      | > >                      |                                                                                      |

| D002                             | Vdr    | RAM Data Retention Voltage <sup>(1)</sup>                                    | _                                                                                                                                                          | 1.5*              | _               | V                        | Device in SLEEP mode                                                                 |

| D003                             | VPOR   | VDD Start Voltage to ensure<br>Power-on Reset                                | _                                                                                                                                                          | Vss               | _               | V                        | See Section 5.1 for details on<br>Power-on Reset                                     |

| D004                             | SVDD   | VDD Rise Rate to ensure Power-<br>on Reset                                   | 0.05*                                                                                                                                                      | _                 | _               | V/ms                     | See Section 5.1 for details on Power-on Reset                                        |

| D010                             | IDD    | Supply Current <sup>(2)</sup> RC <sup>(3)</sup> and XT modes HS mode HS mode |                                                                                                                                                            | 1.8<br>4.8<br>9.0 | 3.3<br>10<br>20 | mA<br>mA<br>mA           | Fosc = 4.0 MHz, VDD = 5.5V<br>Fosc = 10 MHz, VDD = 5.5V<br>Fosc = 16 MHz, VDD = 5.5V |

| D020                             | IPD    | Power-down Current <sup>(2)</sup>                                            | _                                                                                                                                                          | 5.0<br>0.8        | 22<br>18        | μ <b>Α</b><br>μ <b>Α</b> | VDD = 3.25V, WDT enabled<br>VDD = 3.25V, WDT disabled                                |

These parameters are characterized but not tested.

- Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- 3: Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in kΩ.

<sup>†</sup> Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

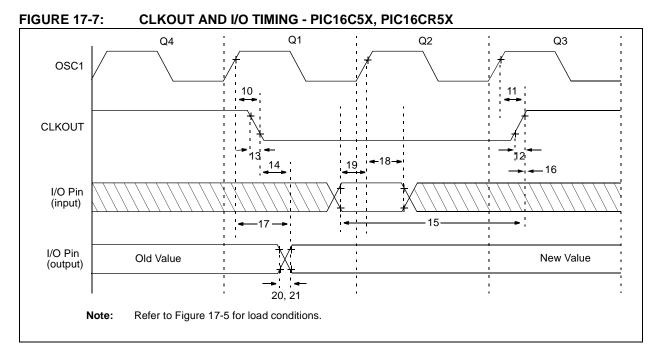

Q1 Q3 Q4 Q2 OSC1 CLKOUT <del><-</del>18→ 19 14 I/O Pin (input) I/O Pin (output) New Value Old Value 20, 21 Note: Please refer to Figure 13.1 for load conditions.

FIGURE 13-3: CLKOUT AND I/O TIMING - PIC16CR54A

TABLE 13-2: CLKOUT AND I/O TIMING REQUIREMENTS - PIC16CR54A

| AC Characteristics |          | Standard Operating Conditions (unless otherwise specified)  Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |              |      |      |       |