Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | POR, WDT                                                                    |

| Number of I/O              | 12                                                                          |

| Program Memory Size        | 768B (512 x 12)                                                             |

| Program Memory Type        | ОТР                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 25 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6.25V                                                                  |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 20-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc54a-04e-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 1-1: PIC16C5X FAMILY OF DEVICES

| Features                         | PIC16C54                            | PIC16CR54                           | PIC16C55                            | PIC16C56                            | PIC16CR56                           |

|----------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| Maximum Operation Frequency      | 40 MHz                              | 20 MHz                              | 40 MHz                              | 40 MHz                              | 20 MHz                              |

| EPROM Program Memory (x12 words) | 512                                 | _                                   | 512                                 | 1K                                  |                                     |

| ROM Program Memory (x12 words)   |                                     | 512                                 | _                                   | _                                   | 1K                                  |

| RAM Data Memory (bytes)          | 25                                  | 25                                  | 24                                  | 25                                  | 25                                  |

| Timer Module(s)                  | TMR0                                | TMR0                                | TMR0                                | TMR0                                | TMR0                                |

| I/O Pins                         | 12                                  | 12                                  | 20                                  | 12                                  | 12                                  |

| Number of Instructions           | 33                                  | 33                                  | 33                                  | 33                                  | 33                                  |

| Packages                         | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 28-pin DIP,<br>SOIC;<br>28-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP |

PIC16C58 Features **PIC16C57** PIC16CR57 PIC16CR58 Maximum Operation Frequency 20 MHz 40 MHz 40 MHz 20 MHz EPROM Program Memory (x12 words) 2K 2K \_\_\_\_ \_ ROM Program Memory (x12 words) 2K 2K \_ \_ RAM Data Memory (bytes) 72 72 73 73 Timer Module(s) TMR0 TMR0 TMR0 TMR0 I/O Pins 20 20 12 12 Number of Instructions 33 33 33 33 28-pin DIP, SOIC; 28-pin DIP, SOIC; 18-pin DIP, SOIC; 18-pin DIP, SOIC; Packages 28-pin SSOP 28-pin SSOP 20-pin SSOP 20-pin SSOP All PIC® Family devices have Power-on Reset, selectable Watchdog Timer, selectable Code Protect and high I/O current capability.

NOTES:

# 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16C5X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16C5X uses a Harvard architecture in which program and data are accessed on separate buses. This improves bandwidth over traditional von Neumann architecture where program and data are fetched on the same bus. Separating program and data memory further allows instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 12 bits wide making it possible to have all single word instructions. A 12-bit wide program memory access bus fetches a 12-bit instruction in a single cycle. A twostage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (33) execute in a single cycle except for program branches.

The PIC16C54/CR54 and PIC16C55 address 512 x 12 of program memory, the PIC16C56/CR56 address 1K x 12 of program memory, and the PIC16C57/CR57 and PIC16C58/CR58 address 2K x 12 of program memory. All program memory is internal.

The PIC16C5X can directly or indirectly address its register files and data memory. All special function registers including the program counter are mapped in the data memory. The PIC16C5X has a highly orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16C5X simple yet efficient. In addition, the learning curve is reduced significantly. The PIC16C5X device contains an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8 bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the W (working) register. The other operand is either a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow and digit borrow out bit, respectively, in subtraction. See the SUBWF and ADDWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, with the corresponding device pins described in Table 3-1 (for PIC16C54/56/58) and Table 3-2 (for PIC16C55/57).

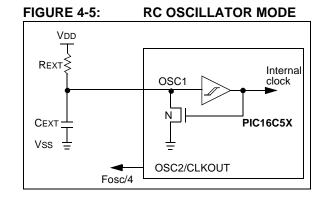

### 4.4 RC Oscillator

For timing insensitive applications, the RC device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used.

Figure 4-5 shows how the R/C combination is connected to the PIC16C5X. For REXT values below 2.2 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high REXT values (e.g., 1 M $\Omega$ ) the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend keeping REXT between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (CEXT = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

The Electrical Specifications sections show RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

Also, see the Electrical Specifications sections for variation of oscillator frequency due to VDD for given REXT/ CEXT values as well as frequency variation due to operating temperature for given R, C, and VDD values.

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin, and can be used for test purposes or to synchronize other logic.

**Note:** If you change from this device to another device, please verify oscillator characteristics in your application.

#### TABLE 5-3: RESET CONDITIONS FOR ALL REGISTERS

| Register                       | Address | Power-On Reset | MCLR or WDT Reset |

|--------------------------------|---------|----------------|-------------------|

| W                              | N/A     | XXXX XXXX      | uuuu uuuu         |

| TRIS                           | N/A     | 1111 1111      | 1111 1111         |

| OPTION                         | N/A     | 11 1111        | 11 1111           |

| INDF                           | 00h     | XXXX XXXX      | uuuu uuuu         |

| TMR0                           | 01h     | XXXX XXXX      | uuuu uuuu         |

| PCL                            | 02h     | 1111 1111      | 1111 1111         |

| STATUS                         | 03h     | 0001 1xxx      | 000q quuu         |

| FSR <sup>(1)</sup>             | 04h     | 1xxx xxxx      | luuu uuuu         |

| PORTA                          | 05h     | xxxx           | uuuu              |

| PORTB                          | 06h     | XXXX XXXX      | uuuu uuuu         |

| PORTC <sup>(2)</sup>           | 07h     | XXXX XXXX      | uuuu uuuu         |

| General Purpose Register Files | 07-7Fh  | XXXX XXXX      | սսսս սսսս         |

Legend: x = unknown u = unchanged - = unimplemented, read as '0'<math>q = see tables in Table 5-1 for possible values.

- Note 1: These values are valid for PIC16C57/CR57/CR58/CR58. For the PIC16C54/CR54/C55/C56/CR56, the value on RESET is 111x xxxx and for MCLR and WDT Reset, the value is 111u uuuu.

- **2:** General purpose register file on PIC16C54/CR54/C56/CR56/C58/CR58.

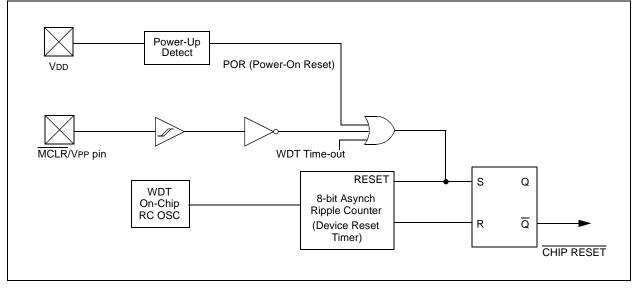

#### FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

NOTES:

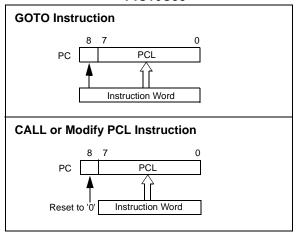

# 6.5 Program Counter

As a program instruction is executed, the Program Counter (PC) will contain the address of the next program instruction to be executed. The PC value is increased by one, every instruction cycle, unless an instruction changes the PC.

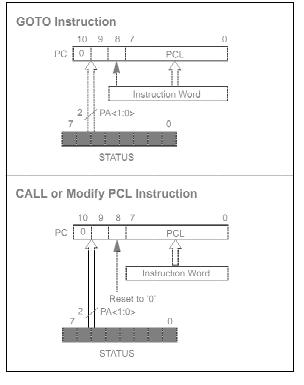

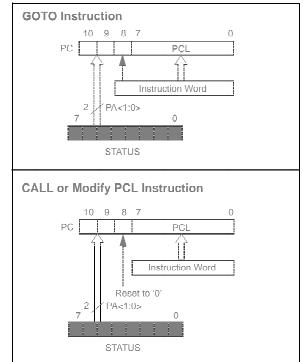

For a GOTO instruction, bits 8:0 of the PC are provided by the GOTO instruction word. The PC Latch (PCL) is mapped to PC<7:0> (Figure 6-7, Figure 6-8 and Figure 6-9).

For the PIC16C56, PIC16CR56, PIC16C57, PIC16CR57, PIC16C757, PIC16C58 and PIC16CR58, a page number must be supplied as well. Bit5 and bit6 of the STA-TUS Register provide page information to bit9 and bit10 of the PC (Figure 6-8 and Figure 6-9).

For a CALL instruction, or any instruction where the PCL is the destination, bits 7:0 of the PC again are provided by the instruction word. However, PC<8> does not come from the instruction word, but is always cleared (Figure 6-7 and Figure 6-8).

Instructions where the PCL is the destination, or modify PCL instructions, include MOVWF PCL, ADDWF PCL, and BSF PCL, 5.

For the PIC16C56, PIC16CR56, PIC16C57, PIC16CR57, PIC16C58 and PIC16CR58, a page number again must be supplied. Bit5 and bit6 of the STA-TUS Register provide page information to bit9 and bit10 of the PC (Figure 6-8 and Figure 6-9).

| Note: | Because PC<8> is cleared in the CALL           |

|-------|------------------------------------------------|

|       | instruction, or any modify PCL instruction,    |

|       | all subroutine calls or computed jumps are     |

|       | limited to the first 256 locations of any pro- |

|       | gram memory page (512 words long).             |

#### FIGURE 6-7: LOADING OF PC BRANCH INSTRUCTIONS - PIC16C54, PIC16CR54, PIC16C55

#### FIGURE 6-8:

#### LOADING OF PC BRANCH INSTRUCTIONS - PIC16C56/PIC16CR56

FIGURE 6-9:

LOADING OF PC BRANCH INSTRUCTIONS - PIC16C57/PIC16CR57, AND PIC16C58/ PIC16CR58

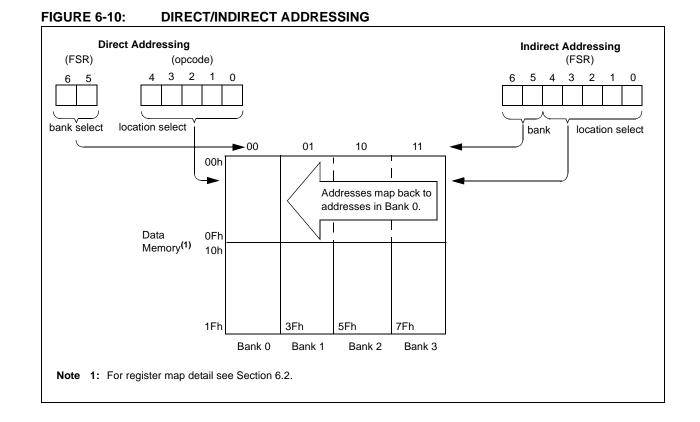

# 6.7 Indirect Data Addressing; INDF and FSR Registers

The INDF Register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR Register (FSR is a *pointer*). This is indirect addressing.

#### EXAMPLE 6-1: INDIRECT ADDRESSING

- Register file 08 contains the value 10h

- Register file 09 contains the value 0Ah

- · Load the value 08 into the FSR Register

- A read of the INDF Register will return the value of 10h

- Increment the value of the FSR Register by one (FSR = 09h)

- A read of the INDF register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF Register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 10h-1Fh using indirect addressing is shown in Example 6-2.

#### EXAMPLE 6-2:

#### HOW TO CLEAR RAM USING INDIRECT ADDRESSING

|          | MOVLW | H'10' | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | MOVWF | FSR   | ; to RAM             |

| NEXT     | CLRF  | INDF  | ;clear INDF Register |

|          | INCF  | FSR,F | ;inc pointer         |

|          | BTFSC | FSR,4 | ;all done?           |

|          | GOTO  | NEXT  | ;NO, clear next      |

| CONTINUE |       |       |                      |

|          | :     |       | ;YES, continue       |

The FSR is either a 5-bit (PIC16C54, PIC16CR54, PIC16C55, PIC16C56, PIC16CR56) or 7-bit (PIC16C57, PIC16CR57, PIC16CR58, PIC16CR58) wide register. It is used in conjunction with the INDF Register to indirectly address the data memory area.

The FSR<4:0> bits are used to select data memory addresses 00h to 1Fh.

**PIC16C54, PIC16CR54, PIC16C55, PIC16C56, PIC16CR56:** These do not use banking. FSR<6:5> bits are unimplemented and read as '1's.

**PIC16C57**, **PIC16CR57**, **PIC16C58**, **PIC16CR58**: FSR<6:5> are the bank select bits and are used to select the bank to be addressed (00 = bank 0, 01 = bank 1, 10 = bank 2, 11 = bank 3).

© 1997-2013 Microchip Technology Inc.

| BSF                                                                           | Bit Set f                                                          |                 |         |  |  |  |  |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------|---------|--|--|--|--|

| Syntax:                                                                       | [ label ]                                                          | [label] BSF f,b |         |  |  |  |  |

| Operands:                                                                     | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$ |                 |         |  |  |  |  |

| Operation:                                                                    | $1 \rightarrow (f < b >)$                                          |                 |         |  |  |  |  |

| Status Affected:                                                              | None                                                               |                 |         |  |  |  |  |

| Encoding:                                                                     | 0101                                                               | ffff            |         |  |  |  |  |

| Description:                                                                  | Bit 'b' in ı                                                       | register 'f'    | is set. |  |  |  |  |

| Words:                                                                        | 1                                                                  |                 |         |  |  |  |  |

| Cycles:                                                                       | 1                                                                  |                 |         |  |  |  |  |

| Example:                                                                      | BSF                                                                | FLAG_RE         | G, 7    |  |  |  |  |

| Before Instruction<br>FLAG_REG = 0x0A<br>After Instruction<br>FLAG REG = 0x8A |                                                                    |                 |         |  |  |  |  |

| FLAG_F                                                                        | (EG = 0)                                                           | IXOA            |         |  |  |  |  |

| BTFSC                                                  | Bit Test f, Skip if Clear                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:                                                | [label] BTFSC f,b                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Operands:                                              | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                                                                   |  |  |  |  |  |  |

| Operation:                                             | skip if $(f < b >) = 0$                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| Status Affected:                                       | None                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Encoding:                                              | 0110 bbbf ffff                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Description:                                           | If bit 'b' in register 'f' is 0 then the<br>next instruction is skipped.<br>If bit 'b' is 0 then the next instruc-<br>tion fetched during the current<br>instruction execution is discarded,<br>and a NOP is executed instead,<br>making this a 2-cycle instruction. |  |  |  |  |  |  |

| Words:                                                 | 1                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Cycles:                                                | 1(2)                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Example:                                               | HERE BTFSC FLAG,1<br>FALSE GOTO PROCESS_CODE<br>TRUE •<br>•                                                                                                                                                                                                          |  |  |  |  |  |  |

| Before Instru                                          | uction                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| PC<br>After Instruct<br>if FLAG<br>PC<br>if FLAG<br>PC | <pre>&lt;1&gt; = 0,<br/>= address (TRUE);</pre>                                                                                                                                                                                                                      |  |  |  |  |  |  |

| BTFSS                                    | Bit Test f, Skip if Set                                                                                                                                                                                                                                                   |                    |             |  |  |  |  |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------|--|--|--|--|

| Syntax:                                  | [label]                                                                                                                                                                                                                                                                   | BTFSS f            | ,b          |  |  |  |  |

| Operands:                                | $0 \le f \le 31$                                                                                                                                                                                                                                                          |                    |             |  |  |  |  |

|                                          | 0 ≤ b < 7                                                                                                                                                                                                                                                                 |                    |             |  |  |  |  |

| Operation:                               | skip if (f<                                                                                                                                                                                                                                                               | :b>) = 1           |             |  |  |  |  |

| Status Affected:                         | None                                                                                                                                                                                                                                                                      |                    |             |  |  |  |  |

| Encoding:                                | 0111                                                                                                                                                                                                                                                                      | bbbf               | ffff        |  |  |  |  |

| Description:                             | If bit 'b' in register 'f' is '1' then the<br>next instruction is skipped.<br>If bit 'b' is '1', then the next instruc-<br>tion fetched during the current<br>instruction execution, is discarded<br>and a NOP is executed instead,<br>making this a 2-cycle instruction. |                    |             |  |  |  |  |

| Words:                                   | 1                                                                                                                                                                                                                                                                         |                    |             |  |  |  |  |

| Cycles:                                  | 1(2)                                                                                                                                                                                                                                                                      |                    |             |  |  |  |  |

| Example:                                 | HERE BTFSS FLAG,1<br>FALSE GOTO PROCESS_CO<br>TRUE •<br>•                                                                                                                                                                                                                 |                    |             |  |  |  |  |

| Before Inst                              | ruction                                                                                                                                                                                                                                                                   |                    |             |  |  |  |  |

| PC<br>After Instru                       | =                                                                                                                                                                                                                                                                         | addres             | SS (HERE)   |  |  |  |  |

| After Instru<br>If FLAG<br>PC<br>if FLAG | <1> =                                                                                                                                                                                                                                                                     | 0,<br>addres<br>1, | SS (FALSE); |  |  |  |  |

| PC                                       | =                                                                                                                                                                                                                                                                         | addres             | SS (TRUE)   |  |  |  |  |

NOTES:

#### 12.5 DC Characteristics: PIC16C54/55/56/57-RCE, XTE, 10E, HSE, LPE (Extended)

| DC CHARACTERISTICS |        | Standard Operating Conditions (unless otherwise specified)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                        |      |            |        |                                                                          |

|--------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|------------|--------|--------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                                                                                       | Min                    | Тур† | Max        | Units  | Conditions                                                               |

| D030               | VIL    | Input Low Voltage                                                                                                                    |                        |      |            |        |                                                                          |

|                    |        | I/O ports                                                                                                                            | Vss                    | —    | 0.15 Vdd   | V      | Pin at hi-impedance                                                      |

|                    |        | MCLR (Schmitt Trigger)                                                                                                               | Vss                    | —    | 0.15 Vdd   | V      |                                                                          |

|                    |        | T0CKI (Schmitt Trigger)                                                                                                              | Vss                    | _    | 0.15 VDD   | V      |                                                                          |

|                    |        | OSC1 (Schmitt Trigger)                                                                                                               | Vss                    | _    | 0.15 VDD   | V      | PIC16C5X-RC only <sup>(3)</sup>                                          |

|                    |        | OSC1 (Schmitt Trigger)                                                                                                               | Vss                    | —    | 0.3 Vdd    | V      | PIC16C5X-XT, 10, HS, LP                                                  |

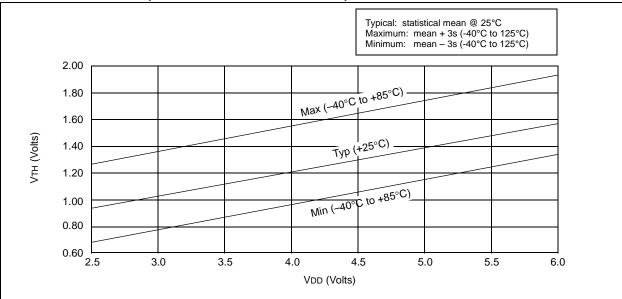

| D040               | Vih    | Input High Voltage                                                                                                                   |                        |      |            |        |                                                                          |

|                    |        | I/O ports                                                                                                                            | 0.45 Vdd               |      | Vdd        | V      | For all VDD <sup>(4)</sup>                                               |

|                    |        | I/O ports                                                                                                                            | 2.0                    | —    | Vdd        | V      | $4.0V < VDD \le 5.5V^{(4)}$                                              |

|                    |        | I/O ports                                                                                                                            | 0.36 VDD               | —    | Vdd        | V      | VDD > 5.5 V                                                              |

|                    |        | MCLR (Schmitt Trigger)                                                                                                               | 0.85 Vdd               | _    | Vdd        | V      |                                                                          |

|                    |        | T0CKI (Schmitt Trigger)                                                                                                              | 0.85 Vdd               | _    | Vdd        | V      |                                                                          |

|                    |        | OSC1 (Schmitt Trigger)                                                                                                               | 0.85 Vdd               | _    | Vdd        | V      | PIC16C5X-RC only <sup>(3)</sup>                                          |

|                    |        | OSC1 (Schmitt Trigger)                                                                                                               | 0.7 Vdd                | —    | Vdd        | V      | PIC16C5X-XT, 10, HS, LP                                                  |

| D050               | VHYS   | Hysteresis of Schmitt<br>Trigger inputs                                                                                              | 0.15 Vdd*              | _    | —          | V      |                                                                          |

| D060               | lı∟    | Input Leakage Current (1,2)                                                                                                          |                        |      |            |        | <b>For V</b> DD ≤ <b>5.5 V</b> :                                         |

|                    |        | I/O ports                                                                                                                            | -1                     | 0.5  | +1         | μA     | VSS $\leq$ VPIN $\leq$ VDD, pin at hi-impedance                          |

|                    |        | MCLR                                                                                                                                 | -5                     | _    | _          | μA     | VPIN = VSS + 0.25V                                                       |

|                    |        | MCLR                                                                                                                                 | _                      | 0.5  | +5         | μA     | VPIN = VDD                                                               |

|                    |        | тоскі                                                                                                                                | -3                     | 0.5  | +3         | μA     | $VSS \leq VPIN \leq VDD$                                                 |

|                    |        | OSC1                                                                                                                                 | -3                     | 0.5  | +3         | μA     | $VSS \le VPIN \le VDD$ ,<br>PIC16C5X-XT, 10, HS, LP                      |

| D080               | Vol    | Output Low Voltage                                                                                                                   |                        |      |            |        |                                                                          |

|                    |        | I/O ports<br>OSC2/CLKOUT                                                                                                             | —                      | _    | 0.6<br>0.6 | V<br>V | IOL = 8.7 mA, VDD = 4.5V<br>IOL = 1.6 mA, VDD = 4.5V,<br>PIC16C5X-RC     |

| D090               | Voн    | <b>Output High Voltage<sup>(2)</sup></b><br>I/O ports<br>OSC2/CLKOUT                                                                 | Vdd – 0.7<br>Vdd – 0.7 |      |            | V<br>V | IOH = -5.4  mA, VDD = 4.5V<br>IOH = -1.0  mA, VDD = 4.5V,<br>PIC16C5X-RC |

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

Note 1: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltage.

2: Negative current is defined as coming out of the pin.

3: For PIC16C5X-RC devices, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C5X be driven with external clock in RC mode.

4: The user may use the better of the two specifications.

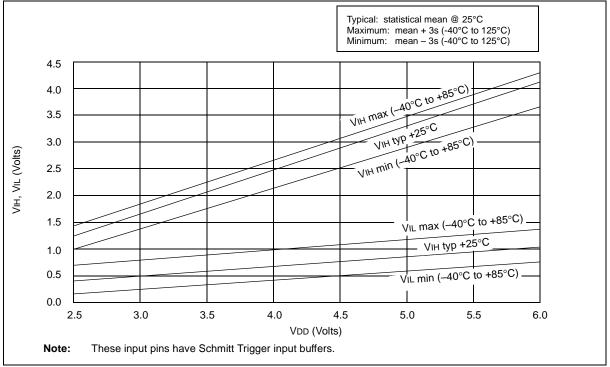

#### FIGURE 14-9: VTH (INPUT THRESHOLD VOLTAGE) OF I/O PINS vs. VDD

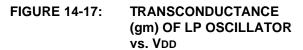

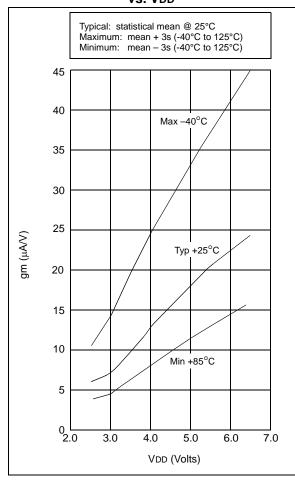

#### FIGURE 14-18:

#### TRANSCONDUCTANCE (gm) OF XT OSCILLATOR vs. VDD

### 15.2 DC Characteristics: PIC16C54A-04E, 10E, 20E (Extended) PIC16LC54A-04E (Extended)

|                                       |        | FICTULCJ                                      |            |                             | cnac         | ч)     |                                                                                         |

|---------------------------------------|--------|-----------------------------------------------|------------|-----------------------------|--------------|--------|-----------------------------------------------------------------------------------------|

| PIC16LC54A-04E<br>(Extended)          |        |                                               |            | <b>ard Ope</b><br>ting Terr |              |        | tions (unless otherwise specified) $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |

| PIC16C54A-04E, 10E, 20E<br>(Extended) |        |                                               |            | ard Ope<br>ting Terr        |              |        | tions (unless otherwise specified) $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |

| Param<br>No.                          | Symbol | Characteristic                                | Min        | Тур†                        | Max          | Units  | Conditions                                                                              |

|                                       | Vdd    | Supply Voltage                                |            |                             | •            |        |                                                                                         |

| D001                                  |        | PIC16LC54A                                    | 3.0<br>2.5 | _                           | 6.25<br>6.25 | V<br>V | XT and RC modes<br>LP mode                                                              |

| D001A                                 |        | PIC16C54A                                     | 3.5<br>4.5 |                             | 5.5<br>5.5   | V<br>V | RC and XT modes<br>HS mode                                                              |

| D002                                  | Vdr    | RAM Data Retention Voltage <sup>(1)</sup>     | —          | 1.5*                        |              | V      | Device in SLEEP mode                                                                    |

| D003                                  | VPOR   | VDD Start Voltage to ensure<br>Power-on Reset | —          | Vss                         | -            | V      | See Section 5.1 for details on<br>Power-on Reset                                        |

| D004                                  | Svdd   | VDD Rise Rate to ensure<br>Power-on Reset     | 0.05*      | _                           | _            | V/ms   | See Section 5.1 for details on<br>Power-on Reset                                        |

|                                       | IDD    | Supply Current <sup>(2)</sup>                 |            |                             |              |        |                                                                                         |

| D010                                  |        | PIC16LC54A                                    | —          | 0.5                         | 25           | mA     | Fosc = 4.0 MHz, VDD = 5.5V,<br>RC <sup>(3)</sup> and XT modes                           |

|                                       |        |                                               | —          | 11                          | 27           | μA     | Fosc = 32 kHz, VDD = 2.5V,<br>LP mode, Commercial                                       |

|                                       |        |                                               | —          | 11                          | 35           | μA     | Fosc = 32 kHz, VDD = 2.5V,<br>LP mode, Industrial                                       |

|                                       |        |                                               | _          | 11                          | 37           | μA     | Fosc = 32 kHz, VDD = 2.5V,<br>LP mode, Extended                                         |

| D010A                                 |        | PIC16C54A                                     | —          | 1.8                         | 3.3          | mA     | Fosc = 4.0 MHz, VDD = 5.5V, $RC^{(3)}$ and XT modes                                     |

|                                       |        |                                               | —          | 4.8                         | 10           | mA     | Fosc = 10 MHz, VDD = 5.5V,<br>HS mode                                                   |

|                                       |        |                                               | —          | 9.0                         | 20           | mA     | Fosc = 20 MHz, VDD = 5.5V,<br>HS mode                                                   |

Legend: Rows with standard voltage device data only are shaded for improved readability.

- \* These parameters are characterized but not tested.

- † Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, TOCKI = VDD, MCLR = VDD; WDT enabled/ disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- **3:** Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in kΩ.

#### 15.3 DC Characteristics: PIC16LV54A-02 (Commercial) PIC16LV54A-02I (Industrial)

| PIC16LV54A-02<br>PIC16LV54A-02I<br>(Commercial, Industrial) |        |                                                                                                                     | $ \begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for commercial} \\ -20^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \end{array} $ |                           |                        |                      |                                                                                                                |  |

|-------------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------|----------------------|----------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.                                                | Symbol | Characteristic                                                                                                      | Min                                                                                                                                                                                                                                                                | Тур†                      | Max                    | Units                | Conditions                                                                                                     |  |

| D001                                                        | Vdd    | Supply Voltage<br>RC and XT modes                                                                                   | 2.0                                                                                                                                                                                                                                                                | _                         | 3.8                    | V                    |                                                                                                                |  |

| D002                                                        | Vdr    | RAM Data Retention<br>Voltage <sup>(1)</sup>                                                                        | —                                                                                                                                                                                                                                                                  | 1.5*                      | —                      | V                    | Device in SLEEP mode                                                                                           |  |

| D003                                                        | VPOR   | VDD Start Voltage to ensure<br>Power-on Reset                                                                       | —                                                                                                                                                                                                                                                                  | Vss                       | —                      | V                    | See Section 5.1 for details on<br>Power-on Reset                                                               |  |

| D004                                                        | SVDD   | VDD Rise Rate to ensure<br>Power-on Reset                                                                           | 0.05*                                                                                                                                                                                                                                                              |                           | —                      | V/ms                 | See Section 5.1 for details on<br>Power-on Reset                                                               |  |

| D010                                                        | IDD    | <b>Supply Current<sup>(2)</sup></b><br>RC <sup>(3)</sup> and XT modes<br>LP mode, Commercial<br>LP mode, Industrial |                                                                                                                                                                                                                                                                    | 0.5<br>11<br>14           | —<br>27<br>35          | μA                   | Fosc = 2.0 MHz, VDD = 3.0V<br>Fosc = 32 kHz, VDD = 2.5V WDT disabled<br>Fosc = 32 kHz, VDD = 2.5V WDT disabled |  |

| D020                                                        | IPD    | <b>Power-down Current<sup>(2,4)</sup></b><br>Commercial<br>Commercial<br>Industrial<br>Industrial                   |                                                                                                                                                                                                                                                                    | 2.5<br>0.25<br>3.5<br>0.3 | 12<br>4.0<br>14<br>5.0 | μΑ<br>μΑ<br>μΑ<br>μΑ | VDD = 2.5V, WDT enabled<br>VDD = 2.5V, WDT disabled<br>VDD = 2.5V, WDT enabled<br>VDD = 2.5V, WDT disabled     |  |

These parameters are characterized but not tested.

- † Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- **Note 1:** This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to VSS, T0CKI = VDD, MCLR = VDD; WDT enabled/ disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- **3:** Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in kΩ.

- 4: The oscillator start-up time can be as much as 8 seconds for XT and LP oscillator selection on wake-up from SLEEP mode or during initial power-up.

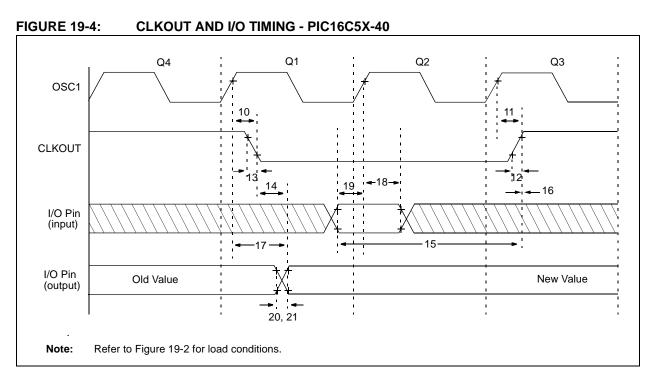

| <b>TABLE 19-2</b> : | CLKOUT AND I/O TIMING REQUIREMENTS - PIC16C5X-40 |

|---------------------|--------------------------------------------------|

|                     |                                                  |

| AC Characteristics |          | Standard Operating Conditions (unless otherwise specified)Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial |              |      |      |       |  |  |  |

|--------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------|--------------|------|------|-------|--|--|--|

| Param<br>No.       | Symbol   | Characteristic                                                                                                                      | Min          | Тур† | Max  | Units |  |  |  |

| 10                 | TosH2ckL | OSC1↑ to CLKOUT↓ <sup>(1,2)</sup>                                                                                                   | —            | 15   | 30** | ns    |  |  |  |

| 11                 | TosH2ckH | OSC1↑ to CLKOUT↑ <sup>(1,2)</sup>                                                                                                   | —            | 15   | 30** | ns    |  |  |  |

| 12                 | TckR     | CLKOUT rise time <sup>(1,2)</sup>                                                                                                   | —            | 5.0  | 15** | ns    |  |  |  |

| 13                 | TckF     | CLKOUT fall time <sup>(1,2)</sup>                                                                                                   | —            | 5.0  | 15** | ns    |  |  |  |

| 14                 | TckL2ioV | CLKOUT↓ to Port out valid <sup>(1,2)</sup>                                                                                          | —            | —    | 40** | ns    |  |  |  |

| 15                 | TioV2ckH | Port in valid before CLKOUT <sup>(1,2)</sup>                                                                                        | 0.25 TCY+30* | —    | _    | ns    |  |  |  |

| 16                 | TckH2iol | Port in hold after CLKOUT <sup>(1,2)</sup>                                                                                          | 0*           | —    | _    | ns    |  |  |  |

| 17                 | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to Port out valid <sup>(2)</sup>                                                                       | —            | —    | 100  | ns    |  |  |  |

| 18                 | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to Port input invalid<br>(I/O in hold time)                                                            | TBD          | —    | —    | ns    |  |  |  |

| 19                 | TioV2osH | Port input valid to OSC1↑<br>(I/O in setup time)                                                                                    | TBD          | —    | —    | ns    |  |  |  |

| 20                 | TioR     | Port output rise time <sup>(2)</sup>                                                                                                | —            | 10   | 25** | ns    |  |  |  |

| 21                 | TioF     | Port output fall time <sup>(2)</sup>                                                                                                | —            | 10   | 25** | ns    |  |  |  |

\* These parameters are characterized but not tested.

- \*\* These parameters are design targets and are not tested. No characterization data available at this time.

- † Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

2: Refer to Figure 19-2 for load conditions.

© 1997-2013 Microchip Technology Inc.

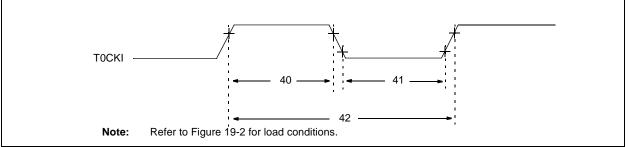

# FIGURE 19-6: TIMER0 CLOCK TIMINGS - PIC16C5X-40

#### TABLE 19-4: TIMER0 CLOCK REQUIREMENTS PIC16C5X-40

| A            | AC Charac | toristics              | Standard Operating Conditions (unless otherwise specified)Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial |      |     |       |                                                                |  |  |

|--------------|-----------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|----------------------------------------------------------------|--|--|

| Param<br>No. | Symbol    | Characteristic         | Min                                                                                                                                 | Тур† | Max | Units | Conditions                                                     |  |  |

| 40           | Tt0H      | T0CKI High Pulse Width |                                                                                                                                     |      |     |       |                                                                |  |  |

|              |           | - No Prescaler         | 0.5 Tcy + 20*                                                                                                                       | —    |     | ns    |                                                                |  |  |

|              |           | - With Prescaler       | 10*                                                                                                                                 |      | —   | ns    |                                                                |  |  |

| 41           | Tt0L      | T0CKI Low Pulse Width  |                                                                                                                                     |      |     |       |                                                                |  |  |

|              |           | - No Prescaler         | 0.5 TCY + 20*                                                                                                                       | —    |     | ns    |                                                                |  |  |

|              |           | - With Prescaler       | 10*                                                                                                                                 | _    | —   | ns    |                                                                |  |  |

| 42           | Tt0P      | T0CKI Period           | 20 or <u>Tcy + 40</u> *<br>N                                                                                                        | _    | _   | ns    | Whichever is greater.<br>N = Prescale Value<br>(1, 2, 4,, 256) |  |  |

\* These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

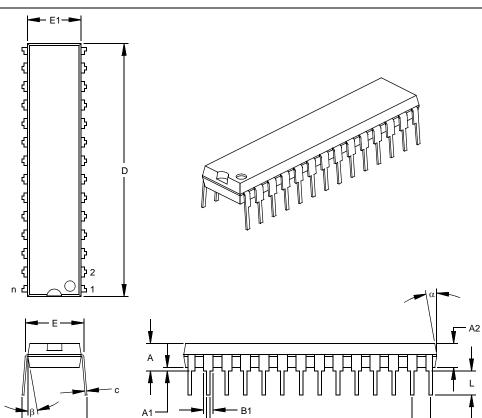

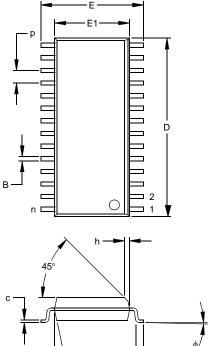

#### 28-Lead Skinny Plastic Dual In-line (SP) - 300 mil (PDIP)

в

|                            | Units     |       | INCHES* |       | Μ     | IILLIMETERS |       |

|----------------------------|-----------|-------|---------|-------|-------|-------------|-------|

| Dimensi                    | on Limits | MIN   | NOM     | MAX   | MIN   | NOM         | MAX   |

| Number of Pins             | n         |       | 28      |       |       | 28          |       |

| Pitch                      | р         |       | .100    |       |       | 2.54        |       |

| Top to Seating Plane       | А         | .140  | .150    | .160  | 3.56  | 3.81        | 4.06  |

| Molded Package Thickness   | A2        | .125  | .130    | .135  | 3.18  | 3.30        | 3.43  |

| Base to Seating Plane      | A1        | .015  |         |       | 0.38  |             |       |

| Shoulder to Shoulder Width | E         | .300  | .310    | .325  | 7.62  | 7.87        | 8.26  |

| Molded Package Width       | E1        | .275  | .285    | .295  | 6.99  | 7.24        | 7.49  |

| Overall Length             | D         | 1.345 | 1.365   | 1.385 | 34.16 | 34.67       | 35.18 |

| Tip to Seating Plane       | L         | .125  | .130    | .135  | 3.18  | 3.30        | 3.43  |

| Lead Thickness             | С         | .008  | .012    | .015  | 0.20  | 0.29        | 0.38  |

| Upper Lead Width           | B1        | .040  | .053    | .065  | 1.02  | 1.33        | 1.65  |

| Lower Lead Width           | В         | .016  | .019    | .022  | 0.41  | 0.48        | 0.56  |

| Overall Row Spacing        | èB        | .320  | .350    | .430  | 8.13  | 8.89        | 10.92 |

| Mold Draft Angle Top       | α         | 5     | 10      | 15    | 5     | 10          | 15    |

| Mold Draft Angle Bottom    | β         | 5     | 10      | 15    | 5     | 10          | 15    |

\* Controlling Parameter § Significant Characteristic

eВ

Dimension D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side.

JEDEC Equivalent: MO-095

Drawing No. C04-070

- p -

Notes:

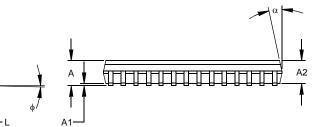

#### 28-Lead Plastic Small Outline (SO) - Wide, 300 mil (SOIC)

For the most current package drawings, please see the Microchip Packaging Specification located Note: at http://www.microchip.com/packaging

|                          | Units     | Units INCHES* |      |      | MILLIMETERS |       |       |  |

|--------------------------|-----------|---------------|------|------|-------------|-------|-------|--|

| Dimensi                  | on Limits | MIN           | NOM  | MAX  | MIN         | NOM   | MAX   |  |

| Number of Pins           | n         |               | 28   |      |             | 28    |       |  |

| Pitch                    | р         |               | .050 |      |             | 1.27  |       |  |

| Overall Height           | А         | .093          | .099 | .104 | 2.36        | 2.50  | 2.64  |  |

| Molded Package Thickness | A2        | .088          | .091 | .094 | 2.24        | 2.31  | 2.39  |  |

| Standoff §               | A1        | .004          | .008 | .012 | 0.10        | 0.20  | 0.30  |  |

| Overall Width            | E         | .394          | .407 | .420 | 10.01       | 10.34 | 10.67 |  |

| Molded Package Width     | E1        | .288          | .295 | .299 | 7.32        | 7.49  | 7.59  |  |

| Overall Length           | D         | .695          | .704 | .712 | 17.65       | 17.87 | 18.08 |  |

| Chamfer Distance         | h         | .010          | .020 | .029 | 0.25        | 0.50  | 0.74  |  |

| Foot Length              | L         | .016          | .033 | .050 | 0.41        | 0.84  | 1.27  |  |

| Foot Angle Top           | φ         | 0             | 4    | 8    | 0           | 4     | 8     |  |

| Lead Thickness           | С         | .009          | .011 | .013 | 0.23        | 0.28  | 0.33  |  |

| Lead Width               | В         | .014          | .017 | .020 | 0.36        | 0.42  | 0.51  |  |

| Mold Draft Angle Top     | α         | 0             | 12   | 15   | 0           | 12    | 15    |  |

| Mold Draft Angle Bottom  | β         | 0             | 12   | 15   | 0           | 12    | 15    |  |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-013 Drawing No. C04-052

NOTES: