Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 768B (512 x 12)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 25 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6.25V                                                                 |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 18-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc54a-04i-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

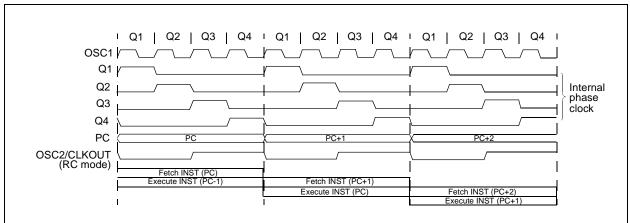

#### 3.1 **Clocking Scheme/Instruction** Cycle

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the program counter is incremented every Q1 and the instruction is fetched from program memory and latched into the instruction register in Q4. It is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 3-2 and Example 3-1.

#### 3.2 Instruction Flow/Pipelining

An Instruction Cycle consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-2: **CLOCK/INSTRUCTION CYCLE**

#### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

is "flushed" from the pipeline, while the new instruction is being fetched and then executed.

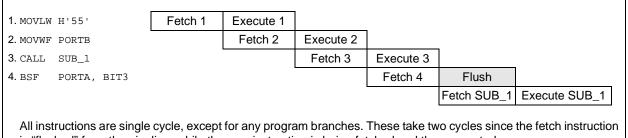

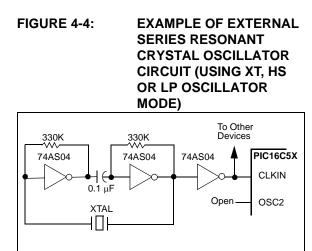

# 4.3 External Crystal Oscillator Circuit

Either a prepackaged oscillator or a simple oscillator circuit with TTL gates can be used as an external crystal oscillator circuit. Prepackaged oscillators provide a wide operating range and better stability. A welldesigned crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used: one with parallel resonance, or one with series resonance.

Figure 4-3 shows an implementation example of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This circuit could be used for external oscillator designs.

FIGURE 4-3: EXAMPLE OF EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT (USING XT, HS OR LP OSCILLATOR MODE)

Figure 4-4 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

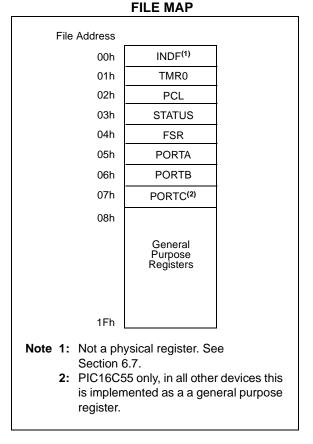

# 6.2 Data Memory Organization

Data memory is composed of registers, or bytes of RAM. Therefore, data memory for a device is specified by its register file. The register file is divided into two functional groups: Special Function Registers and General Purpose Registers.

The Special Function Registers include the TMR0 register, the Program Counter (PC), the Status Register, the I/O registers (ports) and the File Select Register (FSR). In addition, Special Purpose Registers are used to control the I/O port configuration and prescaler options.

The General Purpose Registers are used for data and control information under command of the instructions.

For the PIC16C54, PIC16CR54, PIC16C56 and PIC16CR56, the register file is composed of 7 Special Function Registers and 25 General Purpose Registers (Figure 6-4).

For the PIC16C55, the register file is composed of 8 Special Function Registers and 24 General Purpose Registers.

For the PIC16C57 and PIC16CR57, the register file is composed of 8 Special Function Registers, 24 General Purpose Registers and up to 48 additional General Purpose Registers that may be addressed using a banking scheme (Figure 6-5).

For the PIC16C58 and PIC16CR58, the register file is composed of 7 Special Function Registers, 25 General Purpose Registers and up to 48 additional General Purpose Registers that may be addressed using a banking scheme (Figure 6-6).

#### 6.2.1 GENERAL PURPOSE REGISTER FILE

The register file is accessed either directly or indirectly through the File Select Register (FSR). The FSR Register is described in Section 6.7.

#### FIGURE 6-4: PIC16C54, PIC16CR54, PIC16C55, PIC16C56, PIC16CR56 REGISTER

# 6.3 STATUS Register

This register contains the arithmetic status of the ALU, the RESET status and the page preselect bits for program memories larger than 512 words.

The STATUS Register can be the destination for any instruction, as with any other register. If the STATUS Register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not

writable. Therefore, the result of an instruction with the STATUS Register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS Register as  $000u \ u1uu$  (where u = unchanged).

It is recommended, therefore, that only BCF, BSF and MOVWF instructions be used to alter the STATUS Register because these instructions do not affect the Z, DC or C bits from the STATUS Register. For other instructions which do affect STATUS Bits, see Section 10.0, Instruction Set Summary.

# REGISTER 6-1: STATUS REGISTER (ADDRESS: 03h)

|          | R/W-0                                                                                                                                                         | R/W-0                              | R/W-0        | R-1          | R-1                        | R/W-x         | R/W-x        | R/W-x          |  |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------------|--------------|----------------------------|---------------|--------------|----------------|--|--|--|--|

|          | PA2                                                                                                                                                           | PA1                                | PA0          | TO           | PD                         | Z             | DC           | С              |  |  |  |  |

|          | bit 7                                                                                                                                                         |                                    |              |              |                            |               |              | bit 0          |  |  |  |  |

| bit 7:   | PA2: This bit                                                                                                                                                 | unused at th                       | is time.     |              |                            |               |              |                |  |  |  |  |

|          | Use of the PA2 bit as a general purpose read/write bit is not recommended, since this may affect upwa<br>compatibility with future products.                  |                                    |              |              |                            |               |              |                |  |  |  |  |

| bit 6-5: |                                                                                                                                                               |                                    |              | -            | CR56)(PIC16                |               |              | 58)            |  |  |  |  |

|          |                                                                                                                                                               |                                    |              |              | 16C57/CR57,<br>16C57/CR57, |               |              |                |  |  |  |  |

|          |                                                                                                                                                               | (400h - 5FFh                       |              |              |                            | FIC 10C30/C   | N00          |                |  |  |  |  |

|          | 11 = Page 3                                                                                                                                                   | (600h - 7FFh                       |              |              |                            |               |              |                |  |  |  |  |

|          | Each page is                                                                                                                                                  |                                    | deperal pur  | ose read/wr  | ite bits in devi           | ices which do | not use them | for program    |  |  |  |  |

|          |                                                                                                                                                               |                                    |              |              | affect upward              |               |              |                |  |  |  |  |

| bit 4:   | TO: Time-ou                                                                                                                                                   |                                    |              | ,            | •                          |               |              |                |  |  |  |  |

|          |                                                                                                                                                               | ver-up, CLRWI<br>ime-out occur     |              | , or sleep i | nstruction                 |               |              |                |  |  |  |  |

| bit 3:   | PD: Power-d                                                                                                                                                   | lown bit                           |              |              |                            |               |              |                |  |  |  |  |

|          | •                                                                                                                                                             | ver-up or by tl<br>ution of the SI |              |              |                            |               |              |                |  |  |  |  |

| bit 2:   | Z: Zero bit                                                                                                                                                   |                                    |              |              |                            |               |              |                |  |  |  |  |

|          |                                                                                                                                                               | lt of an arithm<br>It of an arithm |              |              |                            |               |              |                |  |  |  |  |

| bit 1:   | DC: Digit car                                                                                                                                                 | ry/borrow bit                      | (for ADDWF a | nd SUBWF in  | structions)                |               |              |                |  |  |  |  |

|          | ADDWF                                                                                                                                                         |                                    |              |              |                            |               |              |                |  |  |  |  |

|          | <ul> <li>1 = A carry from the 4th low order bit of the result occurred</li> <li>0 = A carry from the 4th low order bit of the result did not occur</li> </ul> |                                    |              |              |                            |               |              |                |  |  |  |  |

|          | SUBWF                                                                                                                                                         |                                    |              |              |                            |               |              |                |  |  |  |  |

|          | 1 = A borrow from the 4th low order bit of the result did not occur                                                                                           |                                    |              |              |                            |               |              |                |  |  |  |  |

|          | 0 = A borrow from the 4th low order bit of the result occurred                                                                                                |                                    |              |              |                            |               |              |                |  |  |  |  |

| bit 0:   | -                                                                                                                                                             | row bit (for AI                    |              |              | F instructions             |               | _            |                |  |  |  |  |

|          | <b>ADDWF</b><br>1 = A carry o                                                                                                                                 | ocurred                            |              | orrow did n  | ot occur                   | RRF or RLI    |              | , respectively |  |  |  |  |

|          | $\pm = \pi \operatorname{carry} 0$                                                                                                                            | locurrou                           | / · ·        |              |                            |               |              |                |  |  |  |  |

| Legena:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | 1 = bit is set   | 0 = bit is cleared        | x = bit is unknown |

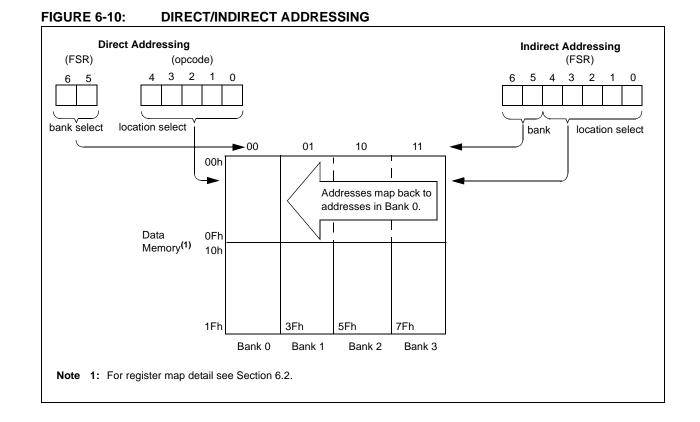

# 6.7 Indirect Data Addressing; INDF and FSR Registers

The INDF Register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR Register (FSR is a *pointer*). This is indirect addressing.

#### EXAMPLE 6-1: INDIRECT ADDRESSING

- Register file 08 contains the value 10h

- Register file 09 contains the value 0Ah

- · Load the value 08 into the FSR Register

- A read of the INDF Register will return the value of 10h

- Increment the value of the FSR Register by one (FSR = 09h)

- A read of the INDF register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF Register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 10h-1Fh using indirect addressing is shown in Example 6-2.

# EXAMPLE 6-2:

#### HOW TO CLEAR RAM USING INDIRECT ADDRESSING

|          | MOVLW | H'10' | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | MOVWF | FSR   | ; to RAM             |

| NEXT     | CLRF  | INDF  | ;clear INDF Register |

|          | INCF  | FSR,F | ;inc pointer         |

|          | BTFSC | FSR,4 | ;all done?           |

|          | GOTO  | NEXT  | ;NO, clear next      |

| CONTINUE |       |       |                      |

|          | :     |       | ;YES, continue       |

The FSR is either a 5-bit (PIC16C54, PIC16CR54, PIC16C55, PIC16C56, PIC16CR56) or 7-bit (PIC16C57, PIC16CR57, PIC16CR58, PIC16CR58) wide register. It is used in conjunction with the INDF Register to indirectly address the data memory area.

The FSR<4:0> bits are used to select data memory addresses 00h to 1Fh.

**PIC16C54, PIC16CR54, PIC16C55, PIC16C56, PIC16CR56:** These do not use banking. FSR<6:5> bits are unimplemented and read as '1's.

**PIC16C57**, **PIC16CR57**, **PIC16C58**, **PIC16CR58**: FSR<6:5> are the bank select bits and are used to select the bank to be addressed (00 = bank 0, 01 = bank 1, 10 = bank 2, 11 = bank 3).

© 1997-2013 Microchip Technology Inc.

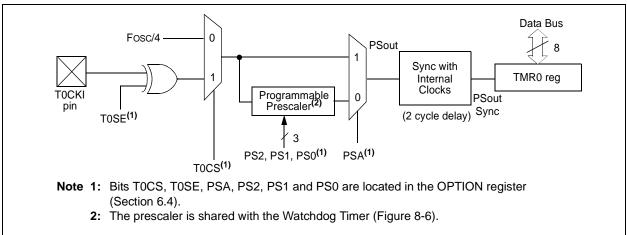

# 8.0 TIMER0 MODULE AND TMR0 REGISTER

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Edge select for external clock

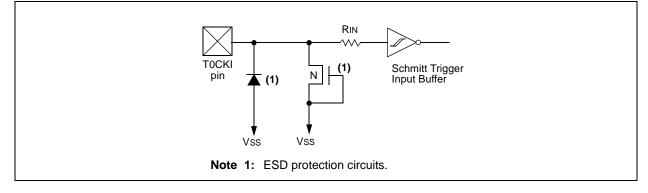

Figure 8-1 is a simplified block diagram of the Timer0 module, while Figure 8-2 shows the electrical structure of the Timer0 input.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two cycles (Figure 8-3 and Figure 8-4). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the T0CS bit (OPTION<5>). In this mode, Timer0 will increment either on every rising or falling edge of pin T0CKI. The incrementing edge is determined by the source edge select bit T0SE (OPTION<4>). Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 8.1.

Note: The prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both.

The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4,..., 1:256 are selectable. Section 8.2 details the operation of the prescaler.

A summary of registers associated with the Timer0 module is found in Table 8-1.

#### FIGURE 8-2: ELECTRICAL STRUCTURE OF TOCKI PIN

# 8.1 Using Timer0 with an External Clock

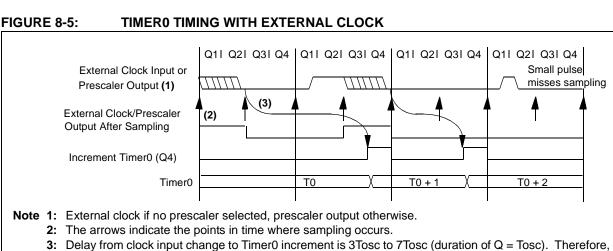

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 8.1.1 EXTERNAL CLOCK SYNCHRONIZATION

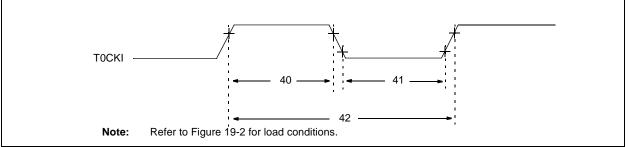

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 8-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple counter-type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

# 8.1.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 8-5 shows the delay from the external clock edge to the timer incrementing.

Belay from clock input change to Timer0 increment is 3 lose to 7 lose (duration of Q = lose). There the error in measuring the interval between two edges on Timer0 input = ± 4 Tose max.

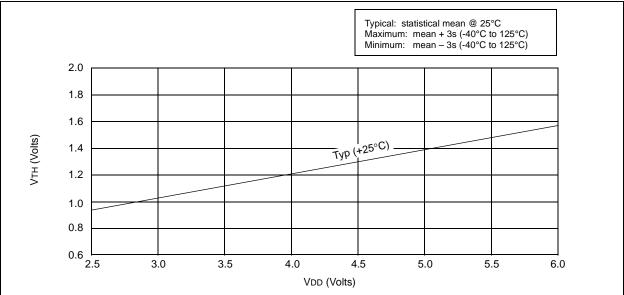

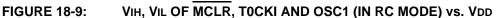

#### 12.5 DC Characteristics: PIC16C54/55/56/57-RCE, XTE, 10E, HSE, LPE (Extended)

| DC CHARACTERISTICS |        | Standard Operating Conditions (unless otherwise specified)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                        |      |            |        |                                                                          |  |

|--------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|------------|--------|--------------------------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic                                                                                                                       | Min                    | Тур† | Max        | Units  | Conditions                                                               |  |

| D030               | VIL    | Input Low Voltage                                                                                                                    |                        |      |            |        |                                                                          |  |

|                    |        | I/O ports                                                                                                                            | Vss                    | —    | 0.15 Vdd   | V      | Pin at hi-impedance                                                      |  |

|                    |        | MCLR (Schmitt Trigger)                                                                                                               | Vss                    | —    | 0.15 Vdd   | V      | -                                                                        |  |

|                    |        | T0CKI (Schmitt Trigger)                                                                                                              | Vss                    | _    | 0.15 VDD   | V      |                                                                          |  |

|                    |        | OSC1 (Schmitt Trigger)                                                                                                               | Vss                    | _    | 0.15 VDD   | V      | PIC16C5X-RC only <sup>(3)</sup>                                          |  |

|                    |        | OSC1 (Schmitt Trigger)                                                                                                               | Vss                    | —    | 0.3 Vdd    | V      | PIC16C5X-XT, 10, HS, LP                                                  |  |

| D040               | Vih    | Input High Voltage                                                                                                                   |                        |      |            |        |                                                                          |  |

|                    |        | I/O ports                                                                                                                            | 0.45 Vdd               |      | Vdd        | V      | For all VDD <sup>(4)</sup>                                               |  |

|                    |        | I/O ports                                                                                                                            | 2.0                    | —    | Vdd        | V      | $4.0V < VDD \le 5.5V^{(4)}$                                              |  |

|                    |        | I/O ports                                                                                                                            | 0.36 VDD               | —    | Vdd        | V      | VDD > 5.5 V                                                              |  |

|                    |        | MCLR (Schmitt Trigger)                                                                                                               | 0.85 Vdd               | _    | Vdd        | V      |                                                                          |  |

|                    |        | T0CKI (Schmitt Trigger)                                                                                                              | 0.85 Vdd               | _    | Vdd        | V      |                                                                          |  |

|                    |        | OSC1 (Schmitt Trigger)                                                                                                               | 0.85 Vdd               | _    | Vdd        | V      | PIC16C5X-RC only <sup>(3)</sup>                                          |  |

|                    |        | OSC1 (Schmitt Trigger)                                                                                                               | 0.7 Vdd                | —    | Vdd        | V      | PIC16C5X-XT, 10, HS, LP                                                  |  |

| D050               | VHYS   | Hysteresis of Schmitt<br>Trigger inputs                                                                                              | 0.15 Vdd*              | _    | —          | V      |                                                                          |  |

| D060               | lı∟    | Input Leakage Current (1,2)                                                                                                          |                        |      |            |        | <b>For V</b> DD ≤ <b>5.5 V</b> :                                         |  |

|                    |        | I/O ports                                                                                                                            | -1                     | 0.5  | +1         | μA     | VSS $\leq$ VPIN $\leq$ VDD, pin at hi-impedance                          |  |

|                    |        | MCLR                                                                                                                                 | -5                     | _    | _          | μA     | VPIN = VSS + 0.25V                                                       |  |

|                    |        | MCLR                                                                                                                                 | _                      | 0.5  | +5         | μA     | VPIN = VDD                                                               |  |

|                    |        | тоскі                                                                                                                                | -3                     | 0.5  | +3         | μA     | $VSS \leq VPIN \leq VDD$                                                 |  |

|                    |        | OSC1                                                                                                                                 | -3                     | 0.5  | +3         | μA     | $VSS \le VPIN \le VDD$ ,<br>PIC16C5X-XT, 10, HS, LP                      |  |

| D080               | Vol    | Output Low Voltage                                                                                                                   |                        |      |            |        |                                                                          |  |

|                    |        | I/O ports<br>OSC2/CLKOUT                                                                                                             | _                      | _    | 0.6<br>0.6 | V<br>V | IOL = 8.7 mA, VDD = 4.5V<br>IOL = 1.6 mA, VDD = 4.5V,<br>PIC16C5X-RC     |  |

| D090               | Vон    | <b>Output High Voltage<sup>(2)</sup></b><br>I/O ports<br>OSC2/CLKOUT                                                                 | Vdd – 0.7<br>Vdd – 0.7 |      |            | V<br>V | IOH = -5.4  mA, VDD = 4.5V<br>IOH = -1.0  mA, VDD = 4.5V,<br>PIC16C5X-RC |  |

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

Note 1: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltage.

2: Negative current is defined as coming out of the pin.

3: For PIC16C5X-RC devices, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C5X be driven with external clock in RC mode.

4: The user may use the better of the two specifications.

# 13.3 DC Characteristics: PIC16CR54A-04, 10, 20, PIC16LCR54A-04 (Commercial) PIC16CR54A-04I, 10I, 20I, PIC16LCR54A-04I (Industrial)

|              |        |                                                                                                                                     | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \end{array}$ |                        |                                                                     |                       |                                                                                                                                                                               |  |

|--------------|--------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No. | Symbol | Characteristic                                                                                                                      | Min                                                                                                                                                                                                                                                              | Тур†                   | Max                                                                 | Units                 | Conditions                                                                                                                                                                    |  |

| D030         | VIL    | Input Low Voltage<br>I/O ports<br>MCLR (Schmitt Trigger)<br>T0CKI (Schmitt Trigger)<br>OSC1 (Schmitt Trigger)<br>OSC1               | Vss<br>Vss<br>Vss<br>Vss<br>Vss                                                                                                                                                                                                                                  |                        | 0.2 VDD<br>0.15 VDD<br>0.15 VDD<br>0.15 VDD<br>0.15 VDD<br>0.15 VDD | V<br>V<br>V<br>V      | Pin at hi-impedance<br>RC mode only <sup>(3)</sup><br>XT, HS and LP modes                                                                                                     |  |

| D040         | VIн    | Input High Voltage<br>I/O ports<br>I/O ports<br>MCLR (Schmitt Trigger)<br>T0CKI (Schmitt Trigger)<br>OSC1 (Schmitt Trigger)<br>OSC1 | 2.0<br>0.6 VDD<br>0.85 VDD<br>0.85 VDD<br>0.85 VDD<br>0.85 VDD                                                                                                                                                                                                   |                        | VDD<br>VDD<br>VDD<br>VDD<br>VDD<br>VDD<br>VDD                       | V<br>V<br>V<br>V<br>V | VDD = 3.0V to 5.5V <sup>(4)</sup><br>Full VDD range <sup>(4)</sup><br>RC mode only <sup>(3)</sup><br>XT, HS and LP modes                                                      |  |

| D050         | VHYS   | Hysteresis of Schmitt<br>Trigger inputs                                                                                             | 0.15 VDD*                                                                                                                                                                                                                                                        | —                      | —                                                                   | V                     |                                                                                                                                                                               |  |

| D060         | lι∟    | Input Leakage Current <sup>(1,2)</sup><br>I/O ports                                                                                 | -1.0                                                                                                                                                                                                                                                             | _                      | +1.0                                                                | μA                    | For VDD $\leq$ 5.5V:<br>VSS $\leq$ VPIN $\leq$ VDD,<br>pin at hi-impedance                                                                                                    |  |

|              |        | MCLR<br>MCLR<br>TOCKI<br>OSC1                                                                                                       | -5.0<br><br>-3.0<br>-3.0                                                                                                                                                                                                                                         | —<br>0.5<br>0.5<br>0.5 | <br>+5.0<br>+3.0<br>+3.0                                            | μΑ<br>μΑ<br>μΑ        | $\label{eq:VPIN} \begin{array}{l} VPIN = VSS + 0.25V \\ VPIN = VDD \\ VSS \leq VPIN \leq VDD \\ VSS \leq VPIN \leq VDD, \\ XT,  HS  \text{and}  LP  \text{modes} \end{array}$ |  |

| D080         | Vol    | Output Low Voltage<br>I/O ports<br>OSC2/CLKOUT                                                                                      |                                                                                                                                                                                                                                                                  | _                      | 0.5<br>0.5                                                          | V<br>V                | IOL = 10  mA,  VDD = 6.0  V<br>IOL = 1.9  mA,  VDD = 6.0  V,<br>RC mode only                                                                                                  |  |

| D090         | Vон    | Output High Voltage <sup>(2)</sup><br>I/O ports<br>OSC2/CLKOUT                                                                      | Vdd - 0.5<br>Vdd - 0.5                                                                                                                                                                                                                                           | _                      |                                                                     | V<br>V                | IOH = -4.0  mA,  VDD = 6.0 V<br>IOH = -0.8  mA,  VDD = 6.0 V,<br>RC mode only                                                                                                 |  |

\* These parameters are characterized but not tested.

- † Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- **Note 1:** The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltage.

- 2: Negative current is defined as coming out of the pin.

- **3:** For the RC mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C5X be driven with external clock in RC mode.

- 4: The user may use the better of the two specifications.

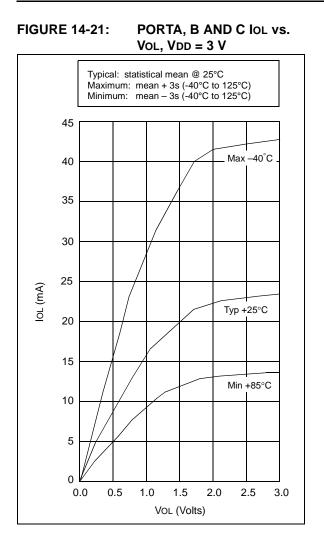

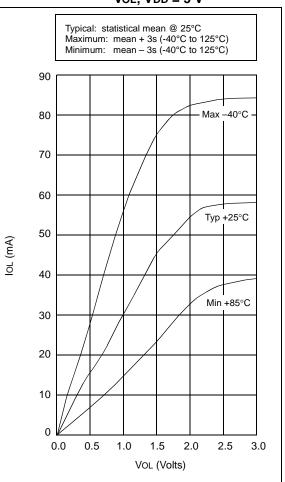

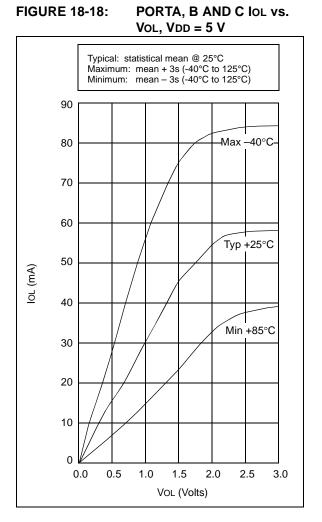

#### FIGURE 14-22: PORTA, B AND C IOL vs. VoL, VDD = 5 V

NOTES:

# 17.4 Timing Parameter Symbology and Load Conditions

The timing parameter symbols have been created with one of the following formats:

1. TppS2ppS

| 2. Tp | pS                                      |                    |

|-------|-----------------------------------------|--------------------|

| Т     |                                         |                    |

| F     | Frequency                               | T Time             |

| Lowe  | ercase letters (pp) and their meanings: |                    |

| рр    |                                         |                    |

| 2     | to                                      | mc MCLR            |

| ck    | CLKOUT                                  | osc oscillator     |

| су    | cycle time                              | os OSC1            |

| drt   | device reset timer                      | t0 T0CKI           |

| io    | I/O port                                | wdt watchdog timer |

| Uppe  | ercase letters and their meanings:      |                    |

| S     |                                         |                    |

| F     | Fall                                    | P Period           |

| н     | High                                    | R Rise             |

| T     | Invalid (Hi-impedance)                  | V Valid            |

| L     | Low                                     | Z Hi-impedance     |

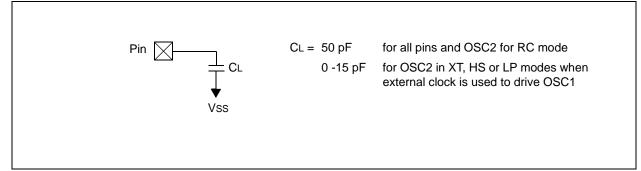

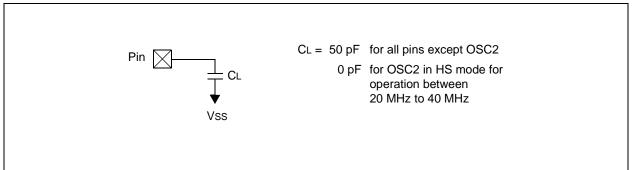

# FIGURE 17-5: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS -PIC16C54C/CR54C/C55A/C56A/CR56A/C57C/CR57C/C58B/CR58B-04, 20

© 1997-2013 Microchip Technology Inc.

# TABLE 18-2:INPUT CAPACITANCE

| Pin         | Typical Capacitance (pF) |          |  |  |  |

|-------------|--------------------------|----------|--|--|--|

| Pin         | 18L PDIP                 | 18L SOIC |  |  |  |

| RA port     | 5.0                      | 4.3      |  |  |  |

| RB port     | 5.0                      | 4.3      |  |  |  |

| MCLR        | 17.0                     | 17.0     |  |  |  |

| OSC1        | 4.0                      | 3.5      |  |  |  |

| OSC2/CLKOUT | 4.3                      | 3.5      |  |  |  |

| тоскі       | 3.2                      | 2.8      |  |  |  |

All capacitance values are typical at  $25^{\circ}$ C. A part-to-part variation of ±25% (three standard deviations) should be taken into account.

# **19.3 Timing Parameter Symbology and Load Conditions**

The timing parameter symbols have been created with one of the following formats:

1. TppS2ppS

| 2. Tp | pS                                      |                    |

|-------|-----------------------------------------|--------------------|

| Т     |                                         |                    |

| F     | Frequency                               | T Time             |

| Lowe  | ercase letters (pp) and their meanings: |                    |

| рр    |                                         |                    |

| 2     | to                                      | mc MCLR            |

| ck    | CLKOUT                                  | osc oscillator     |

| су    | cycle time                              | os OSC1            |

| drt   | device reset timer                      | t0 T0CKI           |

| io    | I/O port                                | wdt watchdog timer |

| Uppe  | ercase letters and their meanings:      |                    |

| S     |                                         |                    |

| F     | Fall                                    | P Period           |

| н     | High                                    | R Rise             |

| Ι     | Invalid (Hi-impedance)                  | V Valid            |

| L     | Low                                     | Z Hi-impedance     |

## FIGURE 19-2: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS -PIC16C54C/C55A/C56A/C57C/C58B-40

# FIGURE 19-6: TIMER0 CLOCK TIMINGS - PIC16C5X-40

# TABLE 19-4: TIMER0 CLOCK REQUIREMENTS PIC16C5X-40

| A            | AC Charac | toristics              | Standard Operating Conditions (unless otherwise specified)Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial |      |     |       |                                                                |  |  |

|--------------|-----------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|----------------------------------------------------------------|--|--|

| Param<br>No. | Symbol    | Characteristic         | Min                                                                                                                                 | Тур† | Max | Units | Conditions                                                     |  |  |

| 40           | Tt0H      | T0CKI High Pulse Width |                                                                                                                                     |      |     |       |                                                                |  |  |

|              |           | - No Prescaler         | 0.5 Tcy + 20*                                                                                                                       | —    |     | ns    |                                                                |  |  |

|              |           | - With Prescaler       | 10*                                                                                                                                 |      | —   | ns    |                                                                |  |  |

| 41           | Tt0L      | T0CKI Low Pulse Width  |                                                                                                                                     |      |     |       |                                                                |  |  |

|              |           | - No Prescaler         | 0.5 TCY + 20*                                                                                                                       | —    |     | ns    |                                                                |  |  |

|              |           | - With Prescaler       | 10*                                                                                                                                 | _    | —   | ns    |                                                                |  |  |

| 42           | Tt0P      | T0CKI Period           | 20 or <u>Tcy + 40</u> *<br>N                                                                                                        | _    | _   | ns    | Whichever is greater.<br>N = Prescale Value<br>(1, 2, 4,, 256) |  |  |

\* These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

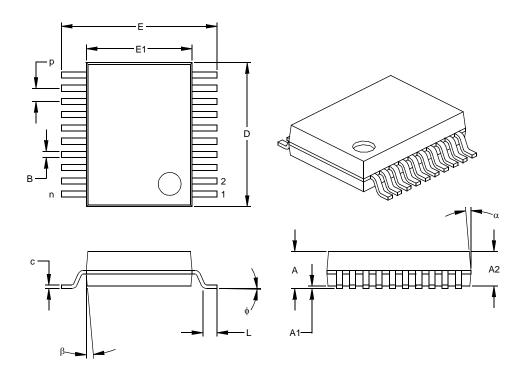

#### 20-Lead Plastic Shrink Small Outline (SS) - 209 mil, 5.30 mm (SSOP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units INCHES* |      |      |      | MILLIMETERS |        |        |  |

|--------------------------|---------------|------|------|------|-------------|--------|--------|--|

| Dimensio                 | on Limits     | MIN  | NOM  | MAX  | MIN         | NOM    | MAX    |  |

| Number of Pins           | n             |      | 20   |      |             | 20     |        |  |

| Pitch                    | р             |      | .026 |      |             | 0.65   |        |  |

| Overall Height           | Α             | .068 | .073 | .078 | 1.73        | 1.85   | 1.98   |  |

| Molded Package Thickness | A2            | .064 | .068 | .072 | 1.63        | 1.73   | 1.83   |  |

| Standoff §               | A1            | .002 | .006 | .010 | 0.05        | 0.15   | 0.25   |  |

| Overall Width            | Е             | .299 | .309 | .322 | 7.59        | 7.85   | 8.18   |  |

| Molded Package Width     | E1            | .201 | .207 | .212 | 5.11        | 5.25   | 5.38   |  |

| Overall Length           | D             | .278 | .284 | .289 | 7.06        | 7.20   | 7.34   |  |

| Foot Length              | L             | .022 | .030 | .037 | 0.56        | 0.75   | 0.94   |  |

| Lead Thickness           | С             | .004 | .007 | .010 | 0.10        | 0.18   | 0.25   |  |

| Foot Angle               | ф             | 0    | 4    | 8    | 0.00        | 101.60 | 203.20 |  |

| Lead Width               | В             | .010 | .013 | .015 | 0.25        | 0.32   | 0.38   |  |

| Mold Draft Angle Top     | α             | 0    | 5    | 10   | 0           | 5      | 10     |  |

| Mold Draft Angle Bottom  | β             | 0    | 5    | 10   | 0           | 5      | 10     |  |

\* Controlling Parameter

§ Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MO-150 Drawing No. C04-072

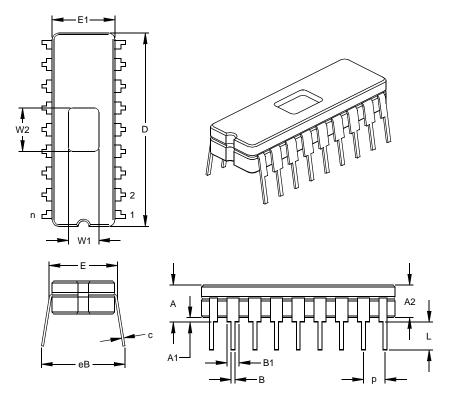

# 18-Lead Ceramic Dual In-line with Window (JW) - 300 mil (CERDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            |          | INCHES* |      | MILLIMETERS |       |       |       |

|----------------------------|----------|---------|------|-------------|-------|-------|-------|

| Dimensior                  | n Limits | MIN     | NOM  | MAX         | MIN   | NOM   | MAX   |

| Number of Pins             | n        |         | 18   |             |       | 18    |       |

| Pitch                      | р        |         | .100 |             |       | 2.54  |       |

| Top to Seating Plane       | А        | .170    | .183 | .195        | 4.32  | 4.64  | 4.95  |

| Ceramic Package Height     | A2       | .155    | .160 | .165        | 3.94  | 4.06  | 4.19  |

| Standoff                   | A1       | .015    | .023 | .030        | 0.38  | 0.57  | 0.76  |

| Shoulder to Shoulder Width | Е        | .300    | .313 | .325        | 7.62  | 7.94  | 8.26  |

| Ceramic Pkg. Width         | E1       | .285    | .290 | .295        | 7.24  | 7.37  | 7.49  |

| Overall Length             | D        | .880    | .900 | .920        | 22.35 | 22.86 | 23.37 |

| Tip to Seating Plane       | L        | .125    | .138 | .150        | 3.18  | 3.49  | 3.81  |

| Lead Thickness             | С        | .008    | .010 | .012        | 0.20  | 0.25  | 0.30  |

| Upper Lead Width           | B1       | .050    | .055 | .060        | 1.27  | 1.40  | 1.52  |

| Lower Lead Width           | В        | .016    | .019 | .021        | 0.41  | 0.47  | 0.53  |

| Overall Row Spacing §      | eB       | .345    | .385 | .425        | 8.76  | 9.78  | 10.80 |

| Window Width               | W1       | .130    | .140 | .150        | 3.30  | 3.56  | 3.81  |

| Window Length              | W2       | .190    | .200 | .210        | 4.83  | 5.08  | 5.33  |

\* Controlling Parameter § Significant Characteristic JEDEC Equivalent: MO-036

Drawing No. C04-010

# **ON-LINE SUPPORT**

Microchip provides on-line support on the Microchip World Wide Web (WWW) site.

The web site is used by Microchip as a means to make files and information easily available to customers. To view the site, the user must have access to the Internet and a web browser, such as Netscape or Microsoft Explorer. Files are also available for FTP download from our FTP site.

#### Connecting to the Microchip Internet Web Site

The Microchip web site is available by using your favorite Internet browser to attach to:

#### www.microchip.com

The file transfer site is available by using an FTP service to connect to:

#### ftp://ftp.microchip.com

The web site and file transfer site provide a variety of services. Users may download files for the latest Development Tools, Data Sheets, Application Notes, User's Guides, Articles and Sample Programs. A variety of Microchip specific business information is also available, including listings of Microchip sales offices, distributors and factory representatives. Other data available for consideration is:

- Latest Microchip Press Releases

- Technical Support Section with Frequently Asked

Questions

- Design Tips

- Device Errata

- Job Postings

- Microchip Consultant Program Member Listing

- Links to other useful web sites related to Microchip Products

- Conferences for products, Development Systems, technical information and more

- Listing of seminars and events