Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | POR, WDT                                                                     |

| Number of I/O              | 12                                                                           |

| Program Memory Size        | 768B (512 x 12)                                                              |

| Program Memory Type        | ОТР                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 25 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            | -                                                                            |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 20-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc54ct-04i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

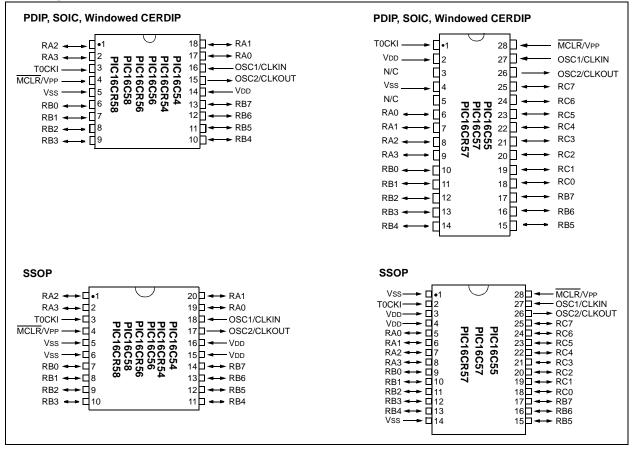

#### **Pin Diagrams**

#### **Device Differences**

| Device     | Voltage<br>Range | Oscillator<br>Selection<br>(Program) | Oscillator | Process<br>Technology<br>(Microns) | ROM<br>Equivalent | MCLR<br>Filter |

|------------|------------------|--------------------------------------|------------|------------------------------------|-------------------|----------------|

| PIC16C54   | 2.5-6.25         | Factory                              | See Note 1 | 1.2                                | PIC16CR54A        | No             |

| PIC16C54A  | 2.0-6.25         | User                                 | See Note 1 | 0.9                                | —                 | No             |

| PIC16C54C  | 2.5-5.5          | User                                 | See Note 1 | 0.7                                | PIC16CR54C        | Yes            |

| PIC16C55   | 2.5-6.25         | Factory                              | See Note 1 | 1.7                                | —                 | No             |

| PIC16C55A  | 2.5-5.5          | User                                 | See Note 1 | 0.7                                | —                 | Yes            |

| PIC16C56   | 2.5-6.25         | Factory                              | See Note 1 | 1.7                                | —                 | No             |

| PIC16C56A  | 2.5-5.5          | User                                 | See Note 1 | 0.7                                | PIC16CR56A        | Yes            |

| PIC16C57   | 2.5-6.25         | Factory                              | See Note 1 | 1.2                                | —                 | No             |

| PIC16C57C  | 2.5-5.5          | User                                 | See Note 1 | 0.7                                | PIC16CR57C        | Yes            |

| PIC16C58B  | 2.5-5.5          | User                                 | See Note 1 | 0.7                                | PIC16CR58B        | Yes            |

| PIC16CR54A | 2.5-6.25         | Factory                              | See Note 1 | 1.2                                | N/A               | Yes            |

| PIC16CR54C | 2.5-5.5          | Factory                              | See Note 1 | 0.7                                | N/A               | Yes            |

| PIC16CR56A | 2.5-5.5          | Factory                              | See Note 1 | 0.7                                | N/A               | Yes            |

| PIC16CR57C | 2.5-5.5          | Factory                              | See Note 1 | 0.7                                | N/A               | Yes            |

| PIC16CR58B | 2.5-5.5          | Factory                              | See Note 1 | 0.7                                | N/A               | Yes            |

Note 1: If you change from this device to another device, please verify oscillator characteristics in your application.

**Note:** The table shown above shows the generic names of the PIC16C5X devices. For device varieties, please refer to Section 2.0.

#### 6.4 **OPTION Register**

The OPTION Register is a 6-bit wide, write-only register which contains various control bits to configure the Timer0/WDT prescaler and Timer0.

By executing the OPTION instruction, the contents of the W Register will be transferred to the OPTION Register. A RESET sets the OPTION<5:0> bits.

#### **REGISTER 6-2: OPTION REGISTER**

| U-0   | U-0 | W-1  | W-1  | W-1 | W-1 | W-1 | W-1   |

|-------|-----|------|------|-----|-----|-----|-------|

| _     | _   | TOCS | TOSE | PSA | PS2 | PS1 | PS0   |

| bit 7 |     |      |      |     |     |     | bit 0 |

- bit 7-6: Unimplemented: Read as '0'

- bit 5: **TOCS**: Timer0 clock source select bit

- 1 = Transition on T0CKI pin

- 0 = Internal instruction cycle clock (CLKOUT)

- bit 4: **TOSE**: Timer0 source edge select bit

- 1 = Increment on high-to-low transition on T0CKI pin

- 0 = Increment on low-to-high transition on T0CKI pin

- bit 3: **PSA**: Prescaler assignment bit

- 1 = Prescaler assigned to the WDT

- 0 = Prescaler assigned to Timer0

#### bit 2-0: **PS<2:0>:** Prescaler rate select bits

| Bit Value | Timer0 Rate | WDT Rate |

|-----------|-------------|----------|

| 000       | 1:2         | 1:1      |

| 001       | 1:4         | 1:2      |

| 010       | 1:8         | 1:4      |

| 011       | 1:16        | 1:8      |

| 100       | 1:32        | 1:16     |

| 101       | 1:64        | 1:32     |

| 110       | 1 : 128     | 1:64     |

| 111       | 1:256       | 1:128    |

|           |             |          |

| Legend:           |                  |                     |                    |

|-------------------|------------------|---------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b | it, read as '0'    |

| -n = Value at POR | 1 = bit is set   | 0 = bit is cleared  | x = bit is unknown |

NOTES:

| ADDWF                                                       | Add W                                                          | and f                                      |                                                      |                    |

|-------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------|------------------------------------------------------|--------------------|

| Syntax:                                                     | [ label ] A                                                    | DDWF                                       | f,d                                                  |                    |

| Operands:                                                   | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$ |                                            |                                                      |                    |

| Operation:                                                  | (W) + (f)                                                      | $\rightarrow$ (dest)                       |                                                      |                    |

| Status Affected:                                            | C, DC, Z                                                       |                                            |                                                      |                    |

| Encoding:                                                   | 0001                                                           | 11df                                       | ffff                                                 |                    |

| Description:                                                | and regis                                                      | ster 'f'. If 'o<br>in the W<br>sult is sto | of the W r<br>d' is 0 the<br>register. I<br>red back | result<br>f 'd' is |

| Words:                                                      | 1                                                              |                                            |                                                      |                    |

| Cycles:                                                     | 1                                                              |                                            |                                                      |                    |

| Example:                                                    | ADDWF                                                          | TEMP_RE                                    | CG, 0                                                |                    |

| Before Instr<br>W<br>TEMP_I<br>After Instruc<br>W<br>TEMP_F | =<br>REG =<br>ction<br>=                                       | 0x17<br>0xC2<br>0xD9<br>0xC2               |                                                      |                    |

| ANDWF                                                      | AND W with f                                                                                                                                                                            |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                    | [label] ANDWF f,d                                                                                                                                                                       |

| Operands:                                                  | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                                          |

| Operation:                                                 | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                                                      |

| Status Affected:                                           | Z                                                                                                                                                                                       |

| Encoding:                                                  | 0001 01df ffff                                                                                                                                                                          |

| Description:                                               | The contents of the W register are<br>AND'ed with register 'f'. If 'd' is 0<br>the result is stored in the W regis-<br>ter. If 'd' is '1' the result is stored<br>back in register 'f'. |

| Words:                                                     | 1                                                                                                                                                                                       |

| Cycles:                                                    | 1                                                                                                                                                                                       |

| Example:                                                   | ANDWF TEMP_REG, 1                                                                                                                                                                       |

| Before Instru<br>W<br>TEMP_<br>After Instruc<br>W<br>TEMP_ | = 0x17<br>REG = 0xC2<br>tion<br>= 0x17                                                                                                                                                  |

| ANDLW                                        | AND literal with W                                                                                                           |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                      | [ <i>label</i> ] ANDLW k                                                                                                     |

| Operands:                                    | $0 \le k \le 255$                                                                                                            |

| Operation:                                   | (W).AND. (k) $\rightarrow$ (W)                                                                                               |

| Status Affected:                             | Z                                                                                                                            |

| Encoding:                                    | 1110 kkkk kkkk                                                                                                               |

| Description:                                 | The contents of the W register are<br>AND'ed with the eight-bit literal 'k'.<br>The result is placed in the W regis-<br>ter. |

| Words:                                       | 1                                                                                                                            |

| Cycles:                                      | 1                                                                                                                            |

| Example:                                     | ANDLW H'5F'                                                                                                                  |

| Before Instru<br>W =<br>After Instruc<br>W = | 0xA3                                                                                                                         |

| BCF                                       | Bit Clea               | r f                                                                |             |  |  |

|-------------------------------------------|------------------------|--------------------------------------------------------------------|-------------|--|--|

| Syntax:                                   | [ label ]              | [label] BCF f,b                                                    |             |  |  |

| Operands:                                 |                        | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$ |             |  |  |

| Operation:                                | $0 \rightarrow (f < b$ | >)                                                                 |             |  |  |

| Status Affected:                          | None                   |                                                                    |             |  |  |

| Encoding:                                 | 0100                   | bbbf                                                               | ffff        |  |  |

| Description:                              | Bit 'b' in             | register 'f'                                                       | is cleared. |  |  |

| Words:                                    | 1                      |                                                                    |             |  |  |

| Cycles:                                   | 1                      |                                                                    |             |  |  |

| Example:                                  | BCF                    | FLAG_RE                                                            | IG, 7       |  |  |

| Before Instru<br>FLAG_F<br>After Instruct | 0xC7                   |                                                                    |             |  |  |

| FLAG_F                                    | REG =                  | 0x47                                                               |             |  |  |

| GOTO                   | Unconditional Branch                                                                                                                                                                        |         |          |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------|

| Syntax:                | [ label ]                                                                                                                                                                                   | GOTO    | k        |

| Operands:              | $0 \le k \le 5^{-1}$                                                                                                                                                                        | 11      |          |

| Operation:             | $k \rightarrow PC < STATUS$                                                                                                                                                                 | ,       | PC<10:9> |

| Status Affected:       | None                                                                                                                                                                                        |         |          |

| Encoding:              | 101k                                                                                                                                                                                        | kkkk    | kkkk     |

| Description:           | GOTO is an unconditional branch.<br>The 9-bit immediate value is<br>loaded into PC bits <8:0>. The<br>upper bits of PC are loaded from<br>STATUS<6:5>. GOTO is a two-<br>cycle instruction. |         |          |

| Words:                 | 1                                                                                                                                                                                           |         |          |

| Cycles:                | 2                                                                                                                                                                                           |         |          |

| Example:               | GOTO THERE                                                                                                                                                                                  |         |          |

| After Instruct<br>PC = | ion<br>address                                                                                                                                                                              | G (THER | E)       |

| INCF                                                    | Increment f                                                                                                                                                          |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                 | [label] INCF f,d                                                                                                                                                     |

| Operands:                                               | $\begin{array}{l} 0 \leq f \leq 31 \\ d  \in  [0,1] \end{array}$                                                                                                     |

| Operation:                                              | (f) + 1 $\rightarrow$ (dest)                                                                                                                                         |

| Status Affected:                                        | Z                                                                                                                                                                    |

| Encoding:                                               | 0010 10df ffff                                                                                                                                                       |

| Description:                                            | The contents of register 'f' are<br>incremented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'. |

| Words:                                                  | 1                                                                                                                                                                    |

| Cycles:                                                 | 1                                                                                                                                                                    |

| Example:                                                | INCF CNT, 1                                                                                                                                                          |

| Before Instru<br>CNT<br>Z<br>After Instruct<br>CNT<br>Z | = 0xFF<br>= 0                                                                                                                                                        |

| INCFSZ                               | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                              | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                                          |

| Operands:                            | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                                                  |

| Operation:                           | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                                                                                                            |

| Status Affected:                     | None                                                                                                                                                                                                                                                                                                                                        |

| Encoding:                            | 0011 11df ffff                                                                                                                                                                                                                                                                                                                              |

| Description:                         | The contents of register 'f' are<br>incremented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'.<br>If the result is 0, then the next<br>instruction, which is already<br>fetched, is discarded and a NOP is<br>executed instead making it a two-<br>cycle instruction. |

| Words:                               | 1                                                                                                                                                                                                                                                                                                                                           |

| Cycles:                              | 1(2)                                                                                                                                                                                                                                                                                                                                        |

| Example:                             | HERE INCFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•<br>•                                                                                                                                                                                                                                                                                     |

| Before Instru<br>PC<br>After Instruc | = address (HERE)                                                                                                                                                                                                                                                                                                                            |

| CNT<br>if CNT<br>PC<br>if CNT<br>PC  | <pre>= CNT + 1;<br/>= 0,<br/>= address (CONTINUE);<br/>≠ 0,<br/>= address (HERE +1)</pre>                                                                                                                                                                                                                                                   |

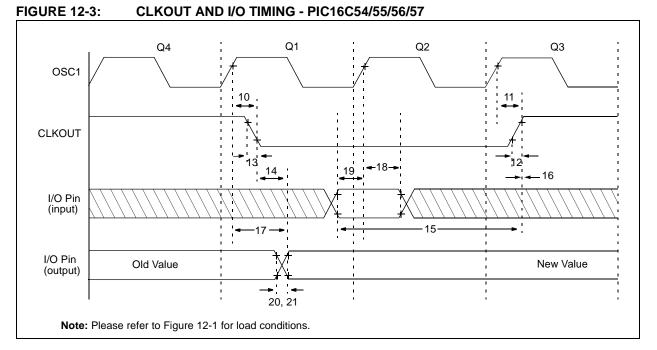

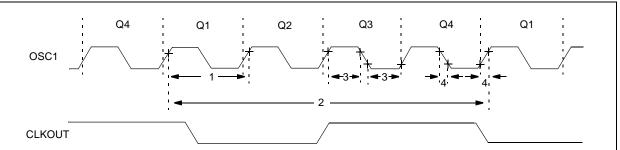

#### TABLE 12-2: CLKOUT AND I/O TIMING REQUIREMENTS - PIC16C54/55/56/57

| AC Characteristics |          | $\begin{array}{llllllllllllllllllllllllllllllllllll$                     |              |      |      |       |  |  |

|--------------------|----------|--------------------------------------------------------------------------|--------------|------|------|-------|--|--|

| Param<br>No.       | Symbol   | Characteristic                                                           | Min          | Тур† | Max  | Units |  |  |

| 10                 | TosH2ckL | OSC1↑ to CLKOUT↓ <sup>(1)</sup>                                          | —            | 15   | 30** | ns    |  |  |

| 11                 | TosH2ckH | OSC1↑ to CLKOUT↑ <sup>(1)</sup>                                          | _            | 15   | 30** | ns    |  |  |

| 12                 | TckR     | CLKOUT rise time <sup>(1)</sup>                                          |              | 5.0  | 15** | ns    |  |  |

| 13                 | TckF     | CLKOUT fall time <sup>(1)</sup>                                          | —            | 5.0  | 15** | ns    |  |  |

| 14                 | TckL2ioV | CLKOUT↓ to Port out valid <sup>(1)</sup>                                 |              |      | 40** | ns    |  |  |

| 15                 | TioV2ckH | Port in valid before CLKOUT <sup>(1)</sup>                               | 0.25 TCY+30* | _    | _    | ns    |  |  |

| 16                 | TckH2iol | Port in hold after CLKOUT <sup>(1)</sup>                                 | 0*           | _    | _    | ns    |  |  |

| 17                 | TosH2ioV | OSC1↑ (Q1 cycle) to Port out valid <sup>(2)</sup>                        | _            |      | 100* | ns    |  |  |

| 18                 | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to Port input invalid<br>(I/O in hold time) | TBD          | —    |      | ns    |  |  |

| 19                 | TioV2osH | Port input valid to OSC1↑<br>(I/O in setup time)                         | TBD          | —    | —    | ns    |  |  |

| 20                 | TioR     | Port output rise time <sup>(2)</sup>                                     | —            | 10   | 25** | ns    |  |  |

| 21                 | TioF     | Port output fall time <sup>(2)</sup>                                     | —            | 10   | 25** | ns    |  |  |

\* These parameters are characterized but not tested.

\*\* These parameters are design targets and are not tested. No characterization data available at this time.

† Data in the Typical ("Typ") column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

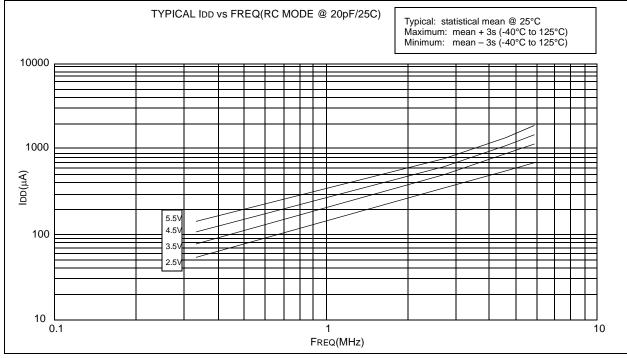

**Note 1:** Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

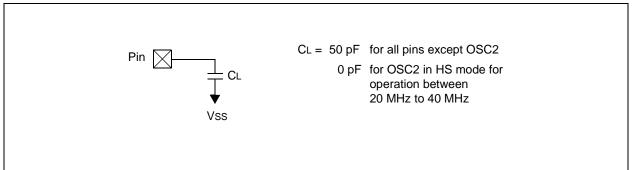

2: Please refer to Figure 12-1 for load conditions.

#### 13.4 DC Characteristics: PIC16CR54A-04E, 10E, 20E (Extended)

| DC CHARACTERISTICS |        |                                         | Standard Operating Conditions (unless otherwise specified)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |      |          |       |                                               |  |

|--------------------|--------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------|----------|-------|-----------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic                          | Min                                                                                                                                  | Тур† | Мах      | Units | Conditions                                    |  |

| D030               | VIL    | Input Low Voltage                       |                                                                                                                                      |      |          |       |                                               |  |

|                    |        | I/O ports                               | Vss                                                                                                                                  | _    | 0.15 Vdd | V     | Pin at hi-impedance                           |  |

|                    |        | MCLR (Schmitt Trigger)                  | Vss                                                                                                                                  | —    | 0.15 Vdd | V     |                                               |  |

|                    |        | T0CKI (Schmitt Trigger)                 | Vss                                                                                                                                  | —    | 0.15 VDD | V     |                                               |  |

|                    |        | OSC1 (Schmitt Trigger)                  | Vss                                                                                                                                  |      | 0.15 VDD | V     | RC mode only <sup>(3)</sup>                   |  |

|                    |        | OSC1                                    | Vss                                                                                                                                  |      | 0.3 Vdd  | V     | XT, HS and LP modes                           |  |

| D040               | Vін    | Input High Voltage                      |                                                                                                                                      |      |          |       |                                               |  |

|                    |        | I/O ports                               | 0.45 Vdd                                                                                                                             | —    | Vdd      | V     | For all VDD <sup>(4)</sup>                    |  |

|                    |        | I/O ports                               | 2.0                                                                                                                                  | —    | Vdd      | V     | $4.0V < VDD \le 5.5V^{(4)}$                   |  |

|                    |        | I/O ports                               | 0.36 VDD                                                                                                                             | —    | Vdd      | V     | VDD > 5.5V                                    |  |

|                    |        | MCLR (Schmitt Trigger)                  | 0.85 VDD                                                                                                                             | —    | Vdd      | V     |                                               |  |

|                    |        | T0CKI (Schmitt Trigger)                 | 0.85 VDD                                                                                                                             | —    | Vdd      | V     |                                               |  |

|                    |        | OSC1 (Schmitt Trigger)                  | 0.85 VDD                                                                                                                             | —    | Vdd      | V     | RC mode only <sup>(3)</sup>                   |  |

|                    |        | OSC1                                    | 0.7 Vdd                                                                                                                              |      | Vdd      | V     | XT, HS and LP modes                           |  |

| D050               | VHYS   | Hysteresis of Schmitt<br>Trigger inputs | 0.15 Vdd*                                                                                                                            | —    |          | V     |                                               |  |

| D060               | lı∟    | Input Leakage Current <sup>(1,2)</sup>  |                                                                                                                                      |      |          |       | <b>For V</b> DD ≤ <b>5.5V</b> :               |  |

|                    |        | I/O ports                               | -1.0                                                                                                                                 | 0.5  | +1.0     | μA    | $VSS \leq VPIN \leq VDD$ ,                    |  |

|                    |        |                                         |                                                                                                                                      |      |          |       | pin at hi-impedance                           |  |

|                    |        | MCLR                                    | -5.0                                                                                                                                 |      | _        | μA    | VPIN = VSS + 0.25V                            |  |

|                    |        | MCLR                                    |                                                                                                                                      | 0.5  | +5.0     | μΑ    | VPIN = VDD                                    |  |

|                    |        | TOCKI                                   | -3.0                                                                                                                                 | 0.5  | +3.0     | μΑ    | $VSS \leq VPIN \leq VDD$                      |  |

|                    |        | OSC1                                    | -3.0                                                                                                                                 | 0.5  | +3.0     | μA    | $VSS \leq VPIN \leq VDD$ ,                    |  |

|                    |        |                                         |                                                                                                                                      |      |          | •     | XT, HS and LP modes                           |  |

| D080               | Vol    | Output Low Voltage                      |                                                                                                                                      |      |          |       |                                               |  |

|                    |        | I/O ports                               | _                                                                                                                                    | _    | 0.6      | V     | IOL = 8.7 mA, VDD = 4.5V                      |  |

|                    |        | OSC2/CLKOUT                             | _                                                                                                                                    | _    | 0.6      | V     | IOL = 1.6  mA, VDD = 4.5 V,                   |  |

|                    |        |                                         |                                                                                                                                      |      |          |       | RC mode only                                  |  |

| D090               | Vон    | Output High Voltage <sup>(2)</sup>      |                                                                                                                                      |      |          |       |                                               |  |

|                    |        | I/O ports                               | Vdd - 0.7                                                                                                                            | —    | —        | V     | IOH = −5.4 mA, VDD = 4.5\                     |  |

|                    |        | OSC2/CLKOUT                             | Vdd - 0.7                                                                                                                            | —    | —        | V     | IOH = -1.0  mA,  VDD = 4.5  V<br>RC mode only |  |

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

Note 1: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltage.

**2:** Negative current is defined as coming out of the pin.

3: For the RC mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C5X be driven with external clock in RC mode.

4: The user may use the better of the two specifications.

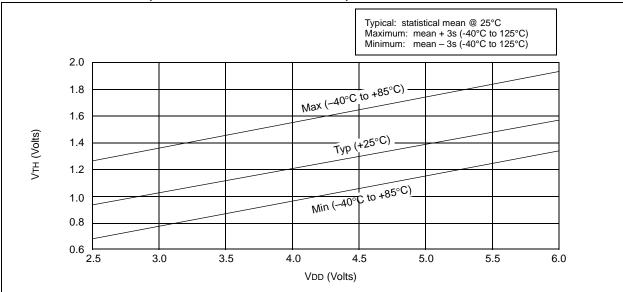

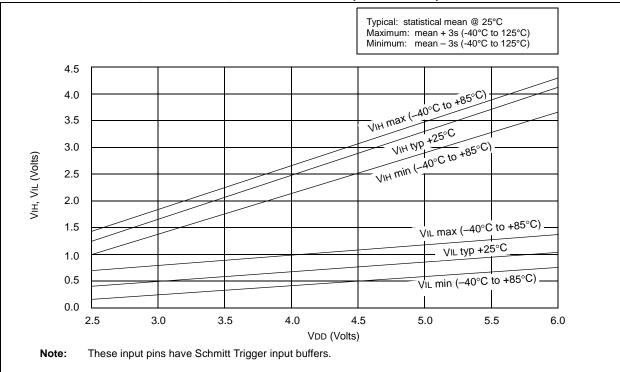

FIGURE 16-7: VTH (INPUT THRESHOLD VOLTAGE) OF I/O PINS - VDD

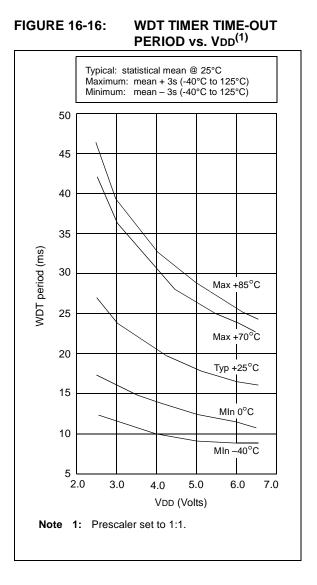

#### FIGURE 16-17: TRANSCONDUCTANCE (gm) OF HS OSCILLATOR vs. VDD

## 17.4 Timing Parameter Symbology and Load Conditions

The timing parameter symbols have been created with one of the following formats:

1. TppS2ppS

| 2. Tp | pS                                     |                    |

|-------|----------------------------------------|--------------------|

| Т     |                                        |                    |

| F     | Frequency                              | T Time             |

| Lowe  | rcase letters (pp) and their meanings: |                    |

| рр    |                                        |                    |

| 2     | to                                     | mc MCLR            |

| ck    | CLKOUT                                 | osc oscillator     |

| су    | cycle time                             | os OSC1            |

| drt   | device reset timer                     | t0 T0CKI           |

| io    | I/O port                               | wdt watchdog timer |

| Uppe  | rcase letters and their meanings:      |                    |

| S     |                                        |                    |

| F     | Fall                                   | P Period           |

| н     | High                                   | R Rise             |

| I     | Invalid (Hi-impedance)                 | V Valid            |

| L     | Low                                    | Z Hi-impedance     |

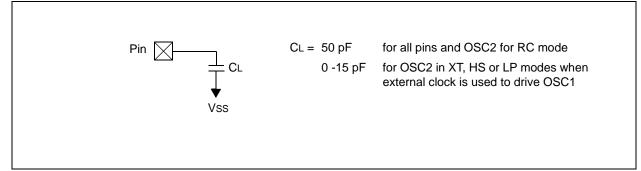

#### FIGURE 17-5: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS -PIC16C54C/CR54C/C55A/C56A/CR56A/C57C/CR57C/C58B/CR58B-04, 20

#### 17.5 Timing Diagrams and Specifications

#### FIGURE 17-6: EXTERNAL CLOCK TIMING - PIC16C5X, PIC16CR5X

#### TABLE 17-1: EXTERNAL CLOCK TIMING REQUIREMENTS - PIC16C5X, PIC16CR5X

| AC Characteristics  |      | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array}$ |      |      |       |       |                  |  |  |

|---------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-------|------------------|--|--|

| Param<br>No. Symbol |      | Characteristic                                                                                                                                                                                                                                                                                                                   | Min  | Тур† | Max   | Units | Conditions       |  |  |

|                     | Fosc | External CLKIN Frequency <sup>(1)</sup>                                                                                                                                                                                                                                                                                          | DC   | _    | 4.0   | MHz   | XT osc mode      |  |  |

|                     |      |                                                                                                                                                                                                                                                                                                                                  | DC   | —    | 4.0   | MHz   | HS osc mode (04) |  |  |

|                     |      |                                                                                                                                                                                                                                                                                                                                  | DC   | —    | 20    | MHz   | HS osc mode (20) |  |  |

|                     |      |                                                                                                                                                                                                                                                                                                                                  | DC   | —    | 200   | kHz   | LP OSC mode      |  |  |

|                     |      | Oscillator Frequency <sup>(1)</sup>                                                                                                                                                                                                                                                                                              | DC   | —    | 4.0   | MHz   | RC osc mode      |  |  |

|                     |      |                                                                                                                                                                                                                                                                                                                                  | 0.45 | —    | 4.0   | MHz   | XT osc mode      |  |  |

|                     |      |                                                                                                                                                                                                                                                                                                                                  | 4.0  | —    | 4.0   | MHz   | HS osc mode (04) |  |  |

|                     |      |                                                                                                                                                                                                                                                                                                                                  | 4.0  | —    | 20    | MHz   | HS osc mode (20) |  |  |

|                     |      |                                                                                                                                                                                                                                                                                                                                  | 5.0  | —    | 200   | kHz   | LP osc mode      |  |  |

| 1                   | Tosc | External CLKIN Period <sup>(1)</sup>                                                                                                                                                                                                                                                                                             | 250  | —    | —     | ns    | XT osc mode      |  |  |

|                     |      |                                                                                                                                                                                                                                                                                                                                  | 250  | —    | —     | ns    | HS osc mode (04) |  |  |

|                     |      |                                                                                                                                                                                                                                                                                                                                  | 50   | —    | —     | ns    | HS osc mode (20) |  |  |

|                     |      |                                                                                                                                                                                                                                                                                                                                  | 5.0  | —    | —     | μS    | LP osc mode      |  |  |

|                     |      | Oscillator Period <sup>(1)</sup>                                                                                                                                                                                                                                                                                                 | 250  | —    | —     | ns    | RC osc mode      |  |  |

|                     |      |                                                                                                                                                                                                                                                                                                                                  | 250  | —    | 2,200 | ns    | XT osc mode      |  |  |

|                     |      |                                                                                                                                                                                                                                                                                                                                  | 250  | —    | 250   | ns    | HS osc mode (04) |  |  |

|                     |      |                                                                                                                                                                                                                                                                                                                                  | 50   | —    | 250   | ns    | HS osc mode (20) |  |  |

|                     |      |                                                                                                                                                                                                                                                                                                                                  | 5.0  | —    | 200   | μS    | LP OSC mode      |  |  |

\* These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption.

When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

**2:** Instruction cycle period (TCY) equals four times the input oscillator time base period.

© 1997-2013 Microchip Technology Inc.

# PIC16C5X

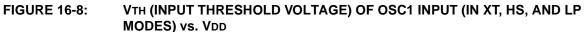

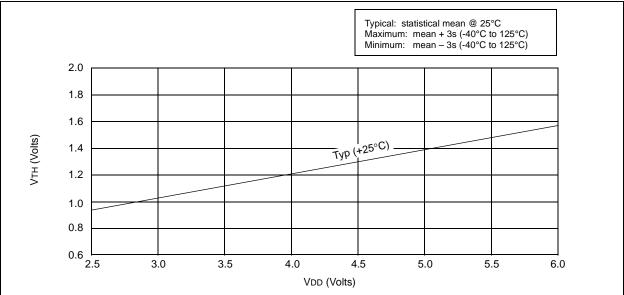

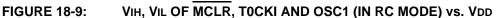

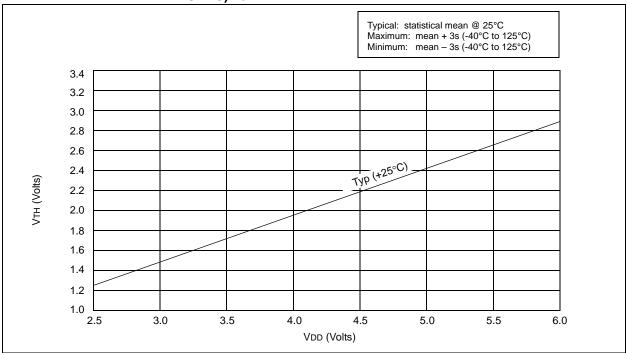

## FIGURE 18-10: VTH (INPUT THRESHOLD TRIP POINT VOLTAGE) OF OSC1 INPUT (IN XT, HS AND LP MODES) vs. VDD

## 19.0 ELECTRICAL CHARACTERISTICS - PIC16LC54C 40MHz

#### Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                                                                 | –55°C to +125°C               |

|----------------------------------------------------------------------------------------------------------------|-------------------------------|

| Storage temperature                                                                                            | –65°C to +150°C               |

| Voltage on VDD with respect to VSS                                                                             | 0 to +7.5V                    |

| Voltage on MCLR with respect to Vss                                                                            | 0 to +14V                     |

| Voltage on all other pins with respect to Vss                                                                  | –0.6V to (VDD + 0.6V)         |

| Total power dissipation <sup>(1)</sup>                                                                         | 800 mW                        |

| Max. current out of Vss pin                                                                                    | 150 mA                        |

| Max. current into Vod pin                                                                                      |                               |

| Max. current into an input pin (T0CKI only)                                                                    | ±500 μA                       |

| Input clamp current, liк (Vi <0 or Vi > VDD)                                                                   | ±20 mA                        |

| Output clamp current, IOK (VO < 0 or VO > VDD)                                                                 | ±20 mA                        |

| Max. output current sunk by any I/O pin                                                                        | 25 mA                         |

| Max. output current sourced by any I/O pin                                                                     | 20 mA                         |

| Max. output current sourced by a single I/O (Port A, B or C)                                                   | 50 mA                         |

| Max. output current sunk by a single I/O (Port A, B or C)                                                      | 50 mA                         |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) | x IOH} + $\Sigma$ (Vol x Iol) |

**†** NOTICE: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## 19.2 DC Characteristics: PIC16C54C/C55A/C56A/C57C/C58B-40 (Commercial)<sup>(1)</sup>

|              |        |                                                                                              | Standard Operating Conditions (unless otherwise specified)Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial |                               |                                        |                      |                                                                                                                                                                               |  |

|--------------|--------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No. | Symbol | Characteristic                                                                               | Min                                                                                                                                 | Тур†                          | Max                                    | Units                | Conditions                                                                                                                                                                    |  |

| D030         | VIL    | Input Low Voltage<br>I/O Ports<br>MCLR (Schmitt Trigger)<br>T0CKI (Schmitt Trigger)<br>OSC1  | Vss<br>Vss<br>Vss<br>Vss                                                                                                            |                               | 0.8<br>0.15 VDD<br>0.15 VDD<br>0.2 VDD | > > ><br>> > >       | 4.5V <vdd <math="">\leq 5.5V<br/>HS, 20 MHz <math>\leq</math> Fosc <math>\leq</math> 40 MHz</vdd>                                                                             |  |

| D040         | Viн    | Input High Voltage<br>I/O ports<br>MCLR (Schmitt Trigger)<br>T0CKI (Schmitt Trigger)<br>OSC1 | 2.0<br>0.85 Vdd<br>0.85 Vdd<br>0.85 Vdd<br>0.8 Vdd                                                                                  |                               | Vdd<br>Vdd<br>Vdd<br>Vdd               | V<br>V<br>V<br>V     | $4.5V < VDD \le 5.5V$<br>HS, 20 MHz $\le$ Fosc $\le$ 40 MHz                                                                                                                   |  |

| D050         | VHYS   | Hysteresis of Schmitt<br>Trigger inputs                                                      | 0.15 Vdd*                                                                                                                           | _                             | _                                      | V                    |                                                                                                                                                                               |  |

| D060         | lı∟    | Input Leakage Current <sup>(2,3)</sup><br>I/O ports<br>MCLR<br>MCLR<br>T0CKI<br>OSC1         | -1.0<br>-5.0<br><br>-3.0<br>-3.0                                                                                                    | 0.5<br>—<br>0.5<br>0.5<br>0.5 | +1.0<br>+5.0<br>+3.0<br>+3.0<br>—      | μΑ<br>μΑ<br>μΑ<br>μΑ | For VDD $\leq$ 5.5V:<br>VSS $\leq$ VPIN $\leq$ VDD,<br>pin at hi-impedance<br>VPIN = VSS +0.25V<br>VPIN = VDD<br>VSS $\leq$ VPIN $\leq$ VDD<br>VSS $\leq$ VPIN $\leq$ VDD, HS |  |

| D080         | Vol    | Output Low Voltage<br>I/O ports                                                              |                                                                                                                                     | _                             | 0.6                                    | V                    | Iol = 8.7 mA, Vdd = 4.5V                                                                                                                                                      |  |

| D090         | Vон    | <b>Output High Voltage<sup>(3)</sup></b><br>I/O ports                                        | Vdd - 0.7                                                                                                                           | _                             | _                                      | V                    | Іон = -5.4 mA, Vdd = 4.5V                                                                                                                                                     |  |

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

**Note 1:** Device operation between 20 MHz to 40 MHz requires the following: VDD between 4.5V to 5.5V, OSC1 pin externally driven, OSC2 pin not connected and HS oscillator mode and commercial temperatures. For operation between DC and 20 MHz, See Section 17.3.

2: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltage.

**3:** Negative current is defined as coming out of the pin.

## **19.3 Timing Parameter Symbology and Load Conditions**

The timing parameter symbols have been created with one of the following formats:

1. TppS2ppS

| 2. Tp | pS                                      |                    |

|-------|-----------------------------------------|--------------------|

| Т     |                                         |                    |

| F     | Frequency                               | T Time             |

| Lowe  | ercase letters (pp) and their meanings: |                    |

| рр    |                                         |                    |

| 2     | to                                      | mc MCLR            |

| ck    | CLKOUT                                  | osc oscillator     |

| су    | cycle time                              | os OSC1            |

| drt   | device reset timer                      | t0 T0CKI           |

| io    | I/O port                                | wdt watchdog timer |

| Uppe  | ercase letters and their meanings:      |                    |

| S     |                                         |                    |

| F     | Fall                                    | P Period           |

| н     | High                                    | R Rise             |

| Ι     | Invalid (Hi-impedance)                  | V Valid            |

| L     | Low                                     | Z Hi-impedance     |

#### FIGURE 19-2: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS -PIC16C54C/C55A/C56A/C57C/C58B-40

#### TABLE 20-1: INPUT CAPACITANCE

| Pin         | Typical Capacitance (pF) |          |  |  |  |

|-------------|--------------------------|----------|--|--|--|

| FIII        | 18L PDIP                 | 18L SOIC |  |  |  |

| RA port     | 5.0                      | 4.3      |  |  |  |

| RB port     | 5.0                      | 4.3      |  |  |  |

| MCLR        | 17.0                     | 17.0     |  |  |  |

| OSC1        | 4.0                      | 3.5      |  |  |  |

| OSC2/CLKOUT | 4.3                      | 3.5      |  |  |  |

| тоскі       | 3.2                      | 2.8      |  |  |  |

All capacitance values are typical at  $25^{\circ}$ C. A part-to-part variation of ±25% (three standard deviations) should be taken into account.

## 21.0 PACKAGING INFORMATION

### 21.1 Package Marketing Information

#### 18-Lead PDIP

#### 28-Lead Skinny PDIP (.300")

#### 28-Lead PDIP (.600")

#### 18-Lead SOIC

#### 28-Lead SOIC

#### 20-Lead SSOP

#### 28-Lead SSOP

#### Example

#### Example

### Example

### Example

#### Example

#### Example

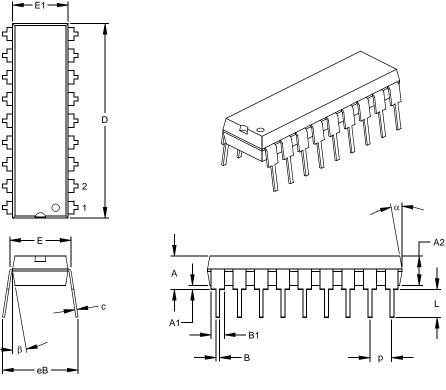

#### 18-Lead Plastic Dual In-line (P) – 300 mil (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units | INCHES* |      |      | MILLIMETERS |       |       |  |

|----------------------------|-------|---------|------|------|-------------|-------|-------|--|

| Dimension Limits           |       | MIN     | NOM  | MAX  | MIN         | NOM   | MAX   |  |

| Number of Pins             | n     |         | 18   |      |             | 18    |       |  |

| Pitch                      | р     |         | .100 |      |             | 2.54  |       |  |

| Top to Seating Plane       | Α     | .140    | .155 | .170 | 3.56        | 3.94  | 4.32  |  |

| Molded Package Thickness   | A2    | .115    | .130 | .145 | 2.92        | 3.30  | 3.68  |  |

| Base to Seating Plane      | A1    | .015    |      |      | 0.38        |       |       |  |

| Shoulder to Shoulder Width | Е     | .300    | .313 | .325 | 7.62        | 7.94  | 8.26  |  |

| Molded Package Width       | E1    | .240    | .250 | .260 | 6.10        | 6.35  | 6.60  |  |

| Overall Length             | D     | .890    | .898 | .905 | 22.61       | 22.80 | 22.99 |  |

| Tip to Seating Plane       | L     | .125    | .130 | .135 | 3.18        | 3.30  | 3.43  |  |

| Lead Thickness             | С     | .008    | .012 | .015 | 0.20        | 0.29  | 0.38  |  |

| Upper Lead Width           | B1    | .045    | .058 | .070 | 1.14        | 1.46  | 1.78  |  |

| Lower Lead Width           | В     | .014    | .018 | .022 | 0.36        | 0.46  | 0.56  |  |

| Overall Row Spacing §      | eB    | .310    | .370 | .430 | 7.87        | 9.40  | 10.92 |  |

| Mold Draft Angle Top       | α     | 5       | 10   | 15   | 5           | 10    | 15    |  |

| Mold Draft Angle Bottom    | β     | 5       | 10   | 15   | 5           | 10    | 15    |  |

\* Controlling Parameter § Significant Characteristic

Notes:

n

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-001 Drawing No. C04-007