Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc55a-04-p |

|----------------------------|---------------------------------------------------------------------------|

| Supplier Device Package    | 28-PDIP                                                                   |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                                  |

| Mounting Type              | Through Hole                                                              |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Oscillator Type            | External                                                                  |

| Data Converters            | -                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                               |

| RAM Size                   | 25 x 8                                                                    |

| EEPROM Size                | -                                                                         |

| Program Memory Type        | OTP                                                                       |

| Program Memory Size        | 768B (512 x 12)                                                           |

| Number of I/O              | 20                                                                        |

| Peripherals                | POR, WDT                                                                  |

| Connectivity               | -                                                                         |

| Speed                      | 4MHz                                                                      |

| Core Size                  | 8-Bit                                                                     |

| Core Processor             | PIC                                                                       |

| Product Status             | Active                                                                    |

| Details                    |                                                                           |

# 4.3 External Crystal Oscillator Circuit

Either a prepackaged oscillator or a simple oscillator circuit with TTL gates can be used as an external crystal oscillator circuit. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used: one with parallel resonance, or one with series resonance.

Figure 4-3 shows an implementation example of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This circuit could be used for external oscillator designs.

FIGURE 4-3: EXAMPLE OF EXTERNAL PARALLEL RESONANT

CRYSTAL OSCILLATOR

CIRCUIT (USING XT, HS

OR LP OSCILLATOR

MODE)

+5V To Other Devices

10K 4.7K 74AS04 PIC16C5X

74AS04 Open OSC2

XTAL

20 pF = 20 pF

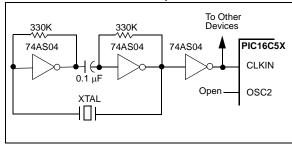

Figure 4-4 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift in a series resonant oscillator circuit. The 330  $k\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

FIGURE 4-4:

EXAMPLE OF EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT (USING XT, HS OR LP OSCILLATOR MODE)

# 5.2 Device Reset Timer (DRT)

The Device Reset Timer (DRT) provides an 18 ms nominal time-out on RESET regardless of Oscillator mode used. The DRT operates on an internal RC oscillator. The processor is kept in RESET as long as the DRT is active. The DRT delay allows VDD to rise above VDD min., and for the oscillator to stabilize.

Oscillator circuits based on crystals or ceramic resonators require a certain time after power-up to establish a stable oscillation. The on-chip DRT keeps the device in a RESET condition for approximately 18 ms after the voltage on the MCLR/VPP pin has reached a logic high (VIH) level. Thus, external RC networks connected to the MCLR input are not required in most cases, allowing for savings in cost-sensitive and/or space restricted applications.

The Device Reset time delay will vary from chip to chip due to VDD, temperature, and process variation. See AC parameters for details.

The DRT will also be triggered upon a Watchdog Timer time-out. This is particularly important for applications using the WDT to wake the PIC16C5X from SLEEP mode automatically.

# 5.3 Reset on Brown-Out

A brown-out is a condition where device power (VDD) dips below its minimum value, but not to zero, and then recovers. The device should be RESET in the event of a brown-out.

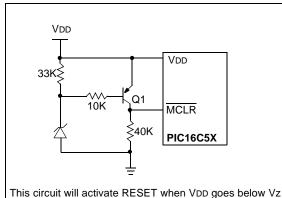

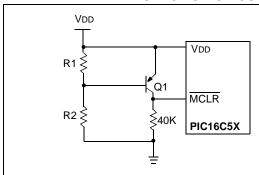

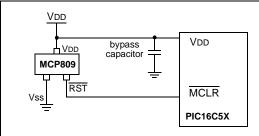

To RESET PIC16C5X devices when a brown-out occurs, external brown-out protection circuits may be built, as shown in Figure 5-6, Figure 5-7 and Figure 5-8.

FIGURE 5-6: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

# FIGURE 5-7: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

This brown-out circuit is less expensive, although less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

# FIGURE 5-8: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 3

This brown-out protection circuit employs Microchip Technology's MCP809 microcontroller supervisor. The MCP8XX and MCP1XX families of supervisors provide push-pull and open collector outputs with both "active high and active low" RESET pins. There are 7 different trip point selections to accommodate 5V and 3V systems.

+ 0.7V (where Vz = Zener voltage).

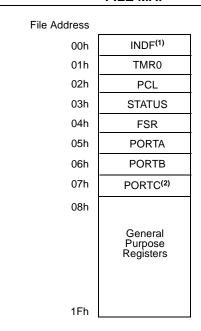

# 6.2 Data Memory Organization

Data memory is composed of registers, or bytes of RAM. Therefore, data memory for a device is specified by its register file. The register file is divided into two functional groups: Special Function Registers and General Purpose Registers.

The Special Function Registers include the TMR0 register, the Program Counter (PC), the Status Register, the I/O registers (ports) and the File Select Register (FSR). In addition, Special Purpose Registers are used to control the I/O port configuration and prescaler options.

The General Purpose Registers are used for data and control information under command of the instructions.

For the PIC16C54, PIC16CR54, PIC16C56 and PIC16CR56, the register file is composed of 7 Special Function Registers and 25 General Purpose Registers (Figure 6-4).

For the PIC16C55, the register file is composed of 8 Special Function Registers and 24 General Purpose Registers.

For the PIC16C57 and PIC16CR57, the register file is composed of 8 Special Function Registers, 24 General Purpose Registers and up to 48 additional General Purpose Registers that may be addressed using a banking scheme (Figure 6-5).

For the PIC16C58 and PIC16CR58, the register file is composed of 7 Special Function Registers, 25 General Purpose Registers and up to 48 additional General Purpose Registers that may be addressed using a banking scheme (Figure 6-6).

# 6.2.1 GENERAL PURPOSE REGISTER FILE

The register file is accessed either directly or indirectly through the File Select Register (FSR). The FSR Register is described in Section 6.7.

FIGURE 6-4: PIC16C54, PIC16CR54, PIC16C55, PIC16C56, PIC16CR56 REGISTER FILE MAP

- **Note 1:** Not a physical register. See Section 6.7.

- **2:** PIC16C55 only, in all other devices this is implemented as a general purpose register.

### 6.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral functions to control the operation of the device (Table 6-1).

The Special Registers can be classified into two sets. The Special Function Registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section for each peripheral feature.

TABLE 6-1: SPECIAL FUNCTION REGISTER SUMMARY

| Address            | Name   | Bit 7    | Bit 6       | Bit 5       | Bit 4     | Bit 3     | Bit 2     | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Details<br>on Page |

|--------------------|--------|----------|-------------|-------------|-----------|-----------|-----------|-------|-------|-------------------------------|--------------------|

| N/A                | TRIS   | I/O Cont | rol Regis   | ters (TRIS  | SA, TRIS  |           | 1111 1111 | 35    |       |                               |                    |

| N/A                | OPTION | Contains | s control b | oits to con | caler     | 11 1111   | 30        |       |       |                               |                    |

| 00h                | INDF   | Uses co  | ntents of   | FSR to ac   | egister)  | XXXX XXXX | 32        |       |       |                               |                    |

| 01h                | TMR0   | Timer0 N | Module R    | egister     |           | XXXX XXXX | 38        |       |       |                               |                    |

| 02h <sup>(1)</sup> | PCL    | Low ord  | er 8 bits c | of PC       |           |           |           |       |       | 1111 1111                     | 31                 |

| 03h                | STATUS | PA2      | PA1         | PA0         | TO        | PD        | Z         | DC    | С     | 0001 1xxx                     | 29                 |

| 04h                | FSR    | Indirect | data mem    | ory addre   | ess point | er        |           |       | I.    | 1xxx xxxx <sup>(3)</sup>      | 32                 |

| 05h                | PORTA  | _        | _           | _           | _         | RA3       | RA2       | RA1   | RA0   | XXXX                          | 35                 |

| 06h                | PORTB  | RB7      | RB6         | RB5         | RB4       | RB3       | RB2       | RB1   | RB0   | XXXX XXXX                     | 35                 |

| 07h <sup>(2)</sup> | PORTC  | RC7      | RC6         | RC5         | RC4       | RC3       | RC2       | RC1   | RC0   | xxxx xxxx                     | 35                 |

Legend: x = unknown, u = unchanged, -= unimplemented, read as '0' (if applicable). Shaded cells = unimplemented or unused

**Note** 1: The upper byte of the Program Counter is not directly accessible. See Section 6.5 for an explanation of how to access these bits.

<sup>2:</sup> File address 07h is a General Purpose Register on the PIC16C54, PIC16CR54, PIC16C56, PIC16CR56, PIC16C58 and PIC16CR58.

<sup>3:</sup> These values are valid for PIC16C57/CR57/C58/CR58. For the PIC16C54/CR54/C55/C56/CR56, the value on RESET is 111x xxxx and for MCLR and WDT Reset, the value is 111u uuuu.

# **7.0 I/O PORTS**

As with any other register, the I/O Registers can be written and read under program control. However, read instructions (e.g., MOVF PORTB, W) always read the I/O pins independent of the pin's input/output modes. On RESET, all I/O ports are defined as input (inputs are at hi-impedance) since the I/O control registers (TRISA, TRISB, TRISC) are all set.

### 7.1 PORTA

PORTA is a 4-bit I/O Register. Only the low order 4 bits are used (RA<3:0>). Bits 7-4 are unimplemented and read as '0's.

### 7.2 PORTB

PORTB is an 8-bit I/O Register (PORTB<7:0>).

# 7.3 PORTC

PORTC is an 8-bit I/O Register for PIC16C55, PIC16C57 and PIC16CR57.

PORTC is a General Purpose Register for PIC16C54, PIC16CR54, PIC16C56, PIC16CR56, PIC16C58 and PIC16CR58.

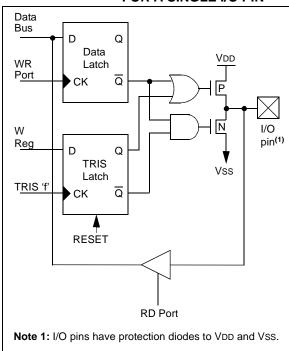

# 7.4 TRIS Registers

The Output Driver Control Registers are loaded with the contents of the W Register by executing the TRIS f instruction. A '1' from a TRIS Register bit puts the corresponding output driver in a hi-impedance (input) mode. A '0' puts the contents of the output data latch on the selected pins, enabling the output buffer.

Note: A read of the ports reads the pins, not the output data latches. That is, if an output driver on a pin is enabled and driven high, but the external system is holding it low, a read of the port will indicate that the pin is low.

The TRIS Registers are "write-only" and are set (output drivers disabled) upon RESET.

# 7.5 I/O Interfacing

The equivalent circuit for an I/O port pin is shown in Figure 7-1. All ports may be used for both input and output operation. For input operations these ports are non-latching. Any input must be present until read by an input instruction (e.g., MOVF PORTB, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit (in TRISA, TRISB, TRISC) must be cleared (= 0). For use as an input, the corresponding TRIS bit must be set. Any I/O pin can be programmed individually as input or output.

FIGURE 7-1: EQUIVALENT CIRCUIT FOR A SINGLE I/O PIN

TABLE 7-1: SUMMARY OF PORT REGISTERS

| Address | Name  | Bit 7 | Bit 6                                       | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on MCLR and WDT Reset |

|---------|-------|-------|---------------------------------------------|-------|-------|-------|-------|-------|-------|-------------------------------|-----------------------------|

| N/A     | TRIS  |       | I/O Control Registers (TRISA, TRISB, TRISC) |       |       |       |       |       |       |                               | 1111 1111                   |

| 05h     | PORTA | _     | _                                           | _     | _     | RA3   | RA2   | RA1   | RA0   | xxxx                          | uuuu                        |

| 06h     | PORTB | RB7   | RB6                                         | RB5   | RB4   | RB3   | RB2   | RB1   | RB0   | xxxx xxxx                     | uuuu uuuu                   |

| 07h     | PORTC | RC7   | RC6                                         | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   | xxxx xxxx                     | uuuu uuuu                   |

Legend: x = unknown, u = unchanged, — = unimplemented, read as '0', Shaded cells = unimplemented, read as '0'

# 7.6 I/O Programming Considerations

### 7.6.1 BI-DIRECTIONAL I/O PORTS

Some instructions operate internally as read followed by write operations. The BCF and BSF instructions, for example, read the entire port into the CPU, execute the bit operation and re-write the result. Caution must be used when these instructions are applied to a port where one or more pins are used as input/outputs. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU, bit5 to be set and the PORTB value to be written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (say bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the Input mode, no problem occurs. However, if bit0 is switched into Output mode later on, the content of the data latch may now be unknown.

Example 7-1 shows the effect of two sequential readmodify-write instructions (e.g., BCF, BSF, etc.) on an I/O port.

A pin actively outputting a high or a low should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

# EXAMPLE 7-1: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

```

; Initial PORT Settings

; PORTB<7:4> Inputs

; PORTB<3:0> Outputs

;PORTB<7:6> have external pull-ups and are

; not connected to other circuitry

PORT latch PORT pins

BCF

PORTB, 7

;01pp pppp

11pp pppp

BCF

PORTB. 6

;10pp pppp

11pp pppp

MOVLW H'3F'

;

TRIS

PORTB

;10pp pppp

10pp pppp

; Note that the user may have expected the pin

; values to be 00pp pppp. The 2nd BCF caused

```

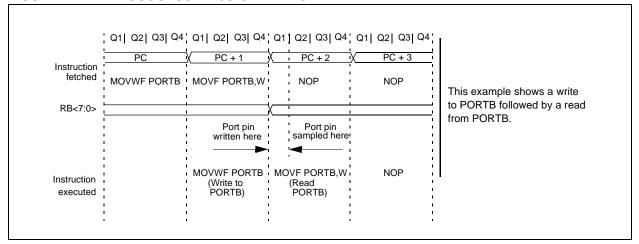

# 7.6.2 SUCCESSIVE OPERATIONS ON I/O PORTS

; RB7 to be latched as the pin value (High).

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 7-2). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should allow the pin voltage to stabilize (load dependent) before the next instruction, which causes that file to be read into the CPU, is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

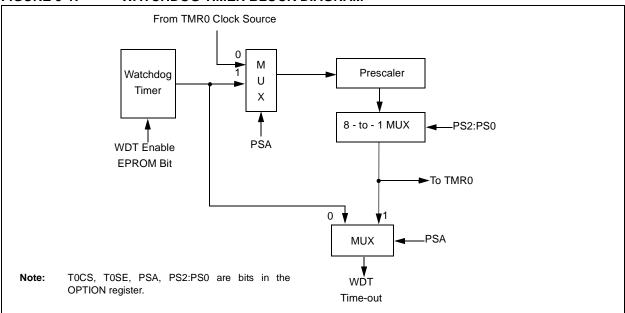

# 9.2 Watchdog Timer (WDT)

The Watchdog Timer (WDT) is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins have been stopped, for example, by execution of a SLEEP instruction. During normal operation or SLEEP, a WDT Reset or Wake-up Reset generates a device RESET.

The TO bit (STATUS<4>) will be cleared upon a Watchdog Timer Reset (Section 6.3).

The WDT can be permanently disabled by programming the configuration bit WDTE as a '0' (Section 9.1). Refer to the PIC16C5X Programming Specifications (Literature Number DS30190) to determine how to access the configuration word.

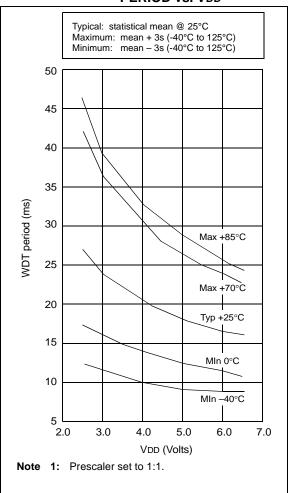

### 9.2.1 WDT PERIOD

An 8-bit counter is available as a prescaler for the Timer0 module (Section 8.2), or as a postscaler for the Watchdog Timer (WDT), respectively. For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that the prescaler may be used by either the Timer0 module or the WDT, but not

both. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the WDT, and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine prescaler assignment and prescale ratio (Section 6.4).

The WDT has a nominal time-out period of 18 ms (with no prescaler). If a longer time-out period is desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT (under software control) by writing to the OPTION register. Thus, time-out a period of a nominal 2.3 seconds can be realized. These periods vary with temperature, VDD and part-to-part process variations (see Device Characterization).

Under worst case conditions (VDD = Min., Temperature = Max., WDT prescaler = 1:128), it may take several seconds before a WDT time-out occurs.

# 9.2.2 WDT PROGRAMMING CONSIDERATIONS

The CLRWDT instruction clears the WDT and the prescaler, if assigned to the WDT, and prevents it from timing out and generating a device RESET.

The SLEEP instruction RESETS the WDT and the prescaler, if assigned to the WDT. This gives the maximum SLEEP time before a WDT Wake-up Reset.

FIGURE 9-1: WATCHDOG TIMER BLOCK DIAGRAM

TABLE 9-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE WATCHDOG TIMER

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on MCLR and WDT Reset |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------------------|-----------------------------|

| N/A     | OPTION |       | 1     | Tosc  | Tose  | PSA   | PS2   | PS1   | PS0   | 11 1111                       | 11 1111                     |

Legend: u = unchanged, - = unimplemented, read as '0'. Shaded cells not used by Watchdog Timer.

# 11.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB® IDE Software

- · Assemblers/Compilers/Linkers

- MPASM™ Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK™ Object Linker/ MPLIB™ Object Librarian

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- ICEPIC™ In-Circuit Emulator

- · In-Circuit Debugger

- MPLAB ICD

- · Device Programmers

- PRO MATE® II Universal Device Programmer

- PICSTART® Plus Entry-Level Development Programmer

- · Low Cost Demonstration Boards

- PICDEM™ 1 Demonstration Board

- PICDEM 2 Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 17 Demonstration Board

- KEELOQ® Demonstration Board

# 11.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. The MPLAB IDE is a Windows®-based application that contains:

- · An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- · A full-featured editor

- · A project manager

- Customizable toolbar and key mapping

- · A status bar

- · On-line help

The MPLAB IDE allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- · Debug using:

- source files

- absolute listing file

- machine code

The ability to use MPLAB IDE with multiple debugging tools allows users to easily switch from the cost-effective simulator to a full-featured emulator with minimal retraining.

### 11.2 MPASM Assembler

The MPASM assembler is a full-featured universal macro assembler for all PIC MCUs.

The MPASM assembler has a command line interface and a Windows shell. It can be used as a stand-alone application on a Windows 3.x or greater system, or it can be used through MPLAB IDE. The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file that contains source lines and generated machine code, and a COD file for debugging.

The MPASM assembler features include:

- · Integration into MPLAB IDE projects.

- User-defined macros to streamline assembly code.

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process.

# 11.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI 'C' compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

# 12.6 Timing Parameter Symbology and Load Conditions

The timing parameter symbols have been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| T                                          |                |

|--------------------------------------------|----------------|

| F Frequency                                | T Time         |

| Lowercase letters (pp) and their meanings: |                |

| рр                                         |                |

| 2 to                                       | mc MCLR        |

| ck CLKOUT                                  | osc oscillator |

| cy cycle time                              | os OSC1        |

t0 T0CKI

wdt watchdog timer

Uppercase letters and their meanings:

drt device reset timer

io I/O port

| OPP | stoadd tottord arra trion trioarmigo. |   |              |

|-----|---------------------------------------|---|--------------|

| S   |                                       |   |              |

| F   | Fall                                  | Р | Period       |

| Н   | High                                  | R | Rise         |

| I   | Invalid (Hi-impedance)                | V | Valid        |

| L   | Low                                   | Z | Hi-impedance |

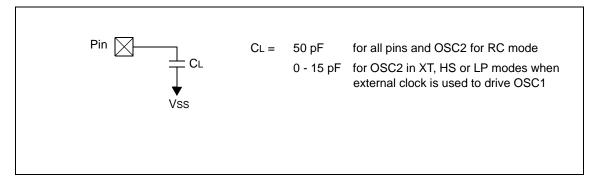

# FIGURE 12-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS - PIC16C54/55/56/57

TABLE 12-1: EXTERNAL CLOCK TIMING REQUIREMENTS - PIC16C54/55/56/57

AC Characteristics Standard Operating Conditions (unless otherwise specified)

Operating Temperature  $0^{\circ}\text{C} \le \text{TA} \le +70^{\circ}\text{C}$  for commercial  $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$  for industrial  $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$  for extended

| Param<br>No. | Symbol | Characteristic                        | Min  | Typ†   | Max    | Units | Conditions             |

|--------------|--------|---------------------------------------|------|--------|--------|-------|------------------------|

| 1            | Tosc   | External CLKIN Period <sup>(1)</sup>  | 250  | _      | _      | ns    | XT osc mode            |

|              |        |                                       | 100  | _      | _      | ns    | 10 MHz mode            |

|              |        |                                       | 50   | _      | _      | ns    | HS osc mode (Comm/Ind) |

|              |        |                                       | 62.5 | _      | _      | ns    | HS osc mode (Ext)      |

|              |        |                                       | 25   | _      | _      | μS    | LP osc mode            |

|              |        | Oscillator Period <sup>(1)</sup>      | 250  | _      | _      | ns    | RC osc mode            |

|              |        |                                       | 250  | _      | 10,000 | ns    | XT osc mode            |

|              |        |                                       | 100  | _      | 250    | ns    | 10 MHz mode            |

|              |        |                                       | 50   | _      | 250    | ns    | HS osc mode (Comm/Ind) |

|              |        |                                       | 62.5 | _      | 250    | ns    | HS osc mode (Ext)      |

|              |        |                                       | 25   | _      | _      | μS    | LP osc mode            |

| 2            | Tcy    | Instruction Cycle Time <sup>(2)</sup> | _    | 4/Fosc | _      | _     |                        |

| 3            | TosL,  | Clock in (OSC1) Low or High           | 85*  | _      | _      | ns    | XT oscillator          |

|              | TosH   | Time                                  | 20*  | _      | _      | ns    | HS oscillator          |

|              |        |                                       | 2.0* | _      | _      | μS    | LP oscillator          |

| 4            | TosR,  | Clock in (OSC1) Rise or Fall          | _    | _      | 25*    | ns    | XT oscillator          |

|              | TosF   | Time                                  | _    | _      | 25*    | ns    | HS oscillator          |

|              |        |                                       | _    | _      | 50*    | ns    | LP oscillator          |

<sup>\*</sup> These parameters are characterized but not tested.

**Note 1:** All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

2: Instruction cycle period (TcY) equals four times the input oscillator time base period.

<sup>†</sup> Data in the Typical ("Typ") column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# 13.1 DC Characteristics: PIC16CR54A-04, 10, 20, PIC16LCR54A-04 (Commercial) PIC16CR54A-04I, 10I, 20I, PIC16LCR54A-04I (Industrial)

| PIC16LC      | PIC16LCR54A-04<br>PIC16LCR54A-04I<br>(Commercial, Industrial)                 |                                   |                  |                                 | Standard Operating Conditions (unless otherwise specified Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                            |                                                                                                                                        |  |  |  |  |

|--------------|-------------------------------------------------------------------------------|-----------------------------------|------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PIC16CR      | PIC16CR54A-04, 10, 20<br>PIC16CR54A-04I, 10I, 20I<br>(Commercial, Industrial) |                                   |                  |                                 |                                                                                                                                                                                           |                            |                                                                                                                                        |  |  |  |  |

| Param<br>No. | Symbol                                                                        | Characteristic/Device             | Min              | Тур†                            | Max                                                                                                                                                                                       | Units                      | Conditions                                                                                                                             |  |  |  |  |

|              | IPD                                                                           | Power-down Current <sup>(2)</sup> |                  |                                 |                                                                                                                                                                                           |                            |                                                                                                                                        |  |  |  |  |

| D006         |                                                                               | PIC16LCR54A-Commercial            | _<br>_<br>_      | 1.0<br>2.0<br>3.0<br>5.0        | 6.0<br>8.0*<br>15<br>25                                                                                                                                                                   | μΑ<br>μΑ<br>μΑ<br>μΑ       | VDD = 2.5V, WDT disabled<br>VDD = 4.0V, WDT disabled<br>VDD = 6.0V, WDT disabled<br>VDD = 6.0V, WDT enabled                            |  |  |  |  |

| D006A        |                                                                               | PIC16CR54A-Commercial             | _<br>_<br>_<br>_ | 1.0<br>2.0<br>3.0<br>5.0        | 6.0<br>8.0*<br>15<br>25                                                                                                                                                                   | μΑ<br>μΑ<br>μΑ<br>μΑ       | VDD = 2.5V, WDT disabled<br>VDD = 4.0V, WDT disabled<br>VDD = 6.0V, WDT disabled<br>VDD = 6.0V, WDT enabled                            |  |  |  |  |

| D007         |                                                                               | PIC16LCR54A-Industrial            |                  | 1.0<br>2.0<br>3.0<br>3.0<br>5.0 | 8.0<br>10*<br>20*<br>18<br>45                                                                                                                                                             | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ | VDD = 2.5V, WDT disabled<br>VDD = 4.0V, WDT disabled<br>VDD = 4.0V, WDT enabled<br>VDD = 6.0V, WDT disabled<br>VDD = 6.0V, WDT enabled |  |  |  |  |

| D007A        |                                                                               | PIC16CR54A-Industrial             | _<br>_<br>_<br>_ | 1.0<br>2.0<br>3.0<br>3.0<br>5.0 | 8.0<br>10*<br>20*<br>18<br>45                                                                                                                                                             | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ | VDD = 2.5V, WDT disabled<br>VDD = 4.0V, WDT disabled<br>VDD = 4.0V, WDT enabled<br>VDD = 6.0V, WDT disabled<br>VDD = 6.0V, WDT enabled |  |  |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

- Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- 3: Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in  $k\Omega$ .

TABLE 13-1: EXTERNAL CLOCK TIMING REQUIREMENTS - PIC16CR54A

AC Characteristics Standard Operating Conditions (unless otherwise specified)

Operating Temperature  $0^{\circ}\text{C} \leq \text{Ta} \leq +70^{\circ}\text{C}$  for commercial  $-40^{\circ}\text{C} \leq \text{Ta} \leq +85^{\circ}\text{C}$  for industrial  $-40^{\circ}\text{C} \leq \text{Ta} \leq +125^{\circ}\text{C}$  for extended

| Param<br>No. | Symbol     | Characteristic                        | Min  | Тур†   | Max    | Units | Conditions       |

|--------------|------------|---------------------------------------|------|--------|--------|-------|------------------|

| 1            | Tosc       | External CLKIN Period <sup>(1)</sup>  | 250  |        | _      | ns    | XT osc mode      |

|              |            |                                       | 250  | _      | _      | ns    | HS osc mode (04) |

|              |            |                                       | 100  | _      | _      | ns    | HS osc mode (10) |

|              |            |                                       | 50   | _      | _      | ns    | HS osc mode (20) |

|              |            |                                       | 5.0  | _      | _      | μS    | LP osc mode      |

|              |            | Oscillator Period <sup>(1)</sup>      | 250  | _      | _      | ns    | RC osc mode      |

|              |            |                                       | 250  | _      | 10,000 | ns    | XT osc mode      |

|              |            |                                       | 250  | _      | 250    | ns    | HS osc mode (04) |

|              |            |                                       | 100  | _      | 250    | ns    | HS osc mode (10) |

|              |            |                                       | 50   | _      | 250    | ns    | HS osc mode (20) |

|              |            |                                       | 5.0  | _      | 200    | μS    | LP osc mode      |

| 2            | Tcy        | Instruction Cycle Time <sup>(2)</sup> | _    | 4/Fosc | _      | _     |                  |

| 3            | TosL, TosH | Clock in (OSC1) Low or High           | 50*  | _      | _      | ns    | XT oscillator    |

|              |            | Time                                  | 20*  | _      | _      | ns    | HS oscillator    |

|              |            |                                       | 2.0* | _      | _      | μS    | LP oscillator    |

| 4            | TosR, TosF | Clock in (OSC1) Rise or Fall          | _    | _      | 25*    | ns    | XT oscillator    |

|              |            | Time                                  | _    | _      | 25*    | ns    | HS oscillator    |

|              |            |                                       |      |        | 50*    | ns    | LP oscillator    |

- \* These parameters are characterized but not tested.

- † Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- **Note 1:** All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

- 2: Instruction cycle period (TCY) equals four times the input oscillator time base period.

FIGURE 14-15: WDT TIMER TIME-OUT PERIOD vs. VDD<sup>(1)</sup>

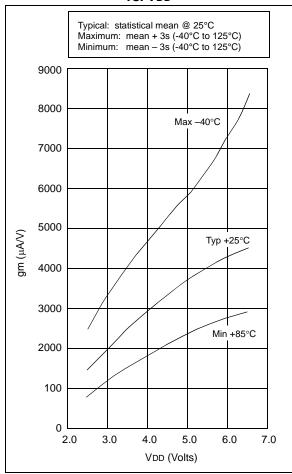

FIGURE 14-16: TRANSCONDUCTANCE (gm) OF HS OSCILLATOR vs. VDD

# 15.0 ELECTRICAL CHARACTERISTICS - PIC16C54A

Absolute Maximum Ratings(†) Storage temperature ——65°C to +150°C Voltage on all other pins with respect to Vss ......—0.6V to (VDD + 0.6V) Total power dissipation<sup>(1)</sup>......800 mW Max. current into an input pin (T0CKI only) ......±500 μA Input clamp current, IK (VI < 0 or VI > VDD)......±20 mA Output clamp current, IOK (VO < 0 or VO > VDD) ......±20 mA

Note 1: Power dissipation is calculated as follows: Pdis = VDD x {IDD -  $\Sigma$  IOH} +  $\Sigma$  {(VDD-VOH) x IOH} +  $\Sigma$ (VOL x IOL)

† NOTICE: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# 15.6 Timing Diagrams and Specifications

**AC Characteristics**

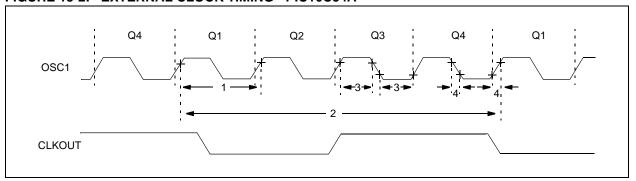

# FIGURE 15-2: EXTERNAL CLOCK TIMING - PIC16C54A

TABLE 15-1: EXTERNAL CLOCK TIMING REQUIREMENTS - PIC16C54A

Standard Operating Conditions (unless otherwise specified)

Operating Temperature  $0^{\circ}C \le TA \le +70^{\circ}C$  for commercial  $-40^{\circ}C \le TA \le +85^{\circ}C$  for industrial

-20°C  $\leq$  TA  $\leq$  +85°C for industrial - PIC16LV54A-02I

$-40^{\circ}$ C  $\leq$  TA  $\leq$  +125 $^{\circ}$ C for extended

**Param Symbol** Characteristic Min Max Units Conditions Typ† No. External CLKIN Fre-Fosc DC MHz XT osc mode 4.0 quency<sup>(1)</sup> XT osc mode (PIC16LV54A) DC 2.0 MHz MHz HS osc mode (04) DC 4.0 DC 10 MHz HS osc mode (10) DC 20 MHz HS osc mode (20) DC 200 kHz LP osc mode Oscillator Frequency<sup>(1)</sup> DC MHz RC osc mode 4.0 DC 2.0 MHz RC osc mode (PIC16LV54A) 0.1 4.0 MHz XT osc mode MHz XT osc mode (PIC16LV54A) 2.0 0.1 4.0 MHz HS osc mode (04) 4.0 4.0 10 MHz HS osc mode (10) 20 MHz HS osc mode (20) 4.0 200 LP osc mode 5.0 kHz

**Note 1:** All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption.

When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

2: Instruction cycle period (TcY) equals four times the input oscillator time base period.

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

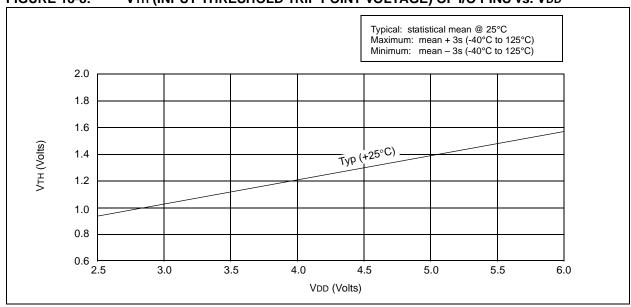

FIGURE 18-8: VTH (INPUT THRESHOLD TRIP POINT VOLTAGE) OF I/O PINS vs. VDD

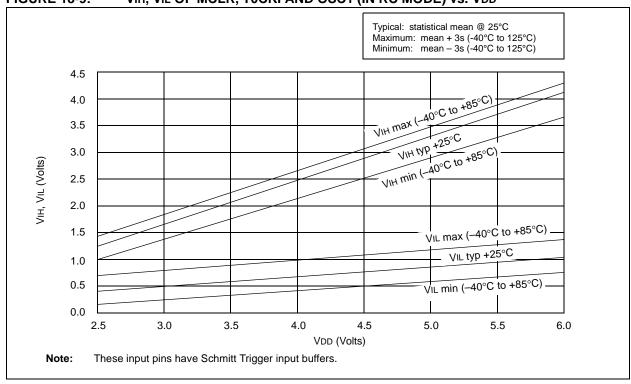

FIGURE 18-9: VIH, VIL OF MCLR, TOCKI AND OSC1 (IN RC MODE) vs. VDD

# 19.2 DC Characteristics: PIC16C54C/C55A/C56A/C57C/C58B-40 (Commercial)<sup>(1)</sup>

| DC CH        | ARACTER | RISTICS                                                                          | Standard Ope<br>Operating Tem          |                   |                                        |                      | ss otherwise specified)<br>0°C for commercial                                    |

|--------------|---------|----------------------------------------------------------------------------------|----------------------------------------|-------------------|----------------------------------------|----------------------|----------------------------------------------------------------------------------|

| Param<br>No. | Symbol  | Characteristic                                                                   | Min                                    | Тур†              | Max                                    | Units                | Conditions                                                                       |

| D030         | VIL     | Input Low Voltage I/O Ports MCLR (Schmitt Trigger) T0CKI (Schmitt Trigger) OSC1  | Vss<br>Vss<br>Vss<br>Vss               | _<br>_<br>_       | 0.8<br>0.15 VDD<br>0.15 VDD<br>0.2 VDD | V<br>V<br>V          | $4.5V < VDD \le 5.5V$<br>HS, 20 MHz $\le$ FOSC $\le$ 40 MHz                      |

| D040         | ViH     | Input High Voltage I/O ports MCLR (Schmitt Trigger) T0CKI (Schmitt Trigger) OSC1 | 2.0<br>0.85 Vdd<br>0.85 Vdd<br>0.8 Vdd | _<br>_<br>_<br>_  | VDD<br>VDD<br>VDD<br>VDD               | V<br>V<br>V          | 4.5V < VDD ≤ 5.5V<br>HS, 20 MHz ≤ FOSC ≤ 40 MHz                                  |

| D050         | VHYS    | Hysteresis of Schmitt<br>Trigger inputs                                          | 0.15 VDD*                              | _                 | _                                      | V                    |                                                                                  |

| D060         | lıL     | Input Leakage Current <sup>(2,3)</sup> I/O ports MCLR                            | -1.0<br>-5.0                           | 0.5               | +1.0<br>+5.0                           | μA<br>μA             | For VDD ≤ 5.5V:<br>VSS ≤ VPIN ≤ VDD,<br>pin at hi-impedance<br>VPIN = VSS +0.25V |

|              |         | MCLR<br>TOCKI<br>OSC1                                                            | -3.0<br>-3.0<br>-3.0                   | 0.5<br>0.5<br>0.5 | +3.0<br>+3.0<br>+3.0                   | μΑ<br>μΑ<br>μΑ<br>μΑ | VPIN = VSS +0.25V<br>VPIN = VDD<br>VSS ≤ VPIN ≤ VDD<br>VSS ≤ VPIN ≤ VDD, HS      |

| D080         | Vol     | Output Low Voltage I/O ports                                                     | _                                      | _                 | 0.6                                    | V                    | IOL = 8.7 mA, VDD = 4.5V                                                         |

| D090         | Voн     | Output High Voltage <sup>(3)</sup> I/O ports                                     | VDD - 0.7                              | _                 | _                                      | V                    | IOH = -5.4 mA, VDD = 4.5V                                                        |

<sup>\*</sup> These parameters are characterized but not tested.

- **Note 1:** Device operation between 20 MHz to 40 MHz requires the following: VDD between 4.5V to 5.5V, OSC1 pin externally driven, OSC2 pin not connected and HS oscillator mode and commercial temperatures. For operation between DC and 20 MHz, See Section 17.3.

- 2: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltage.

- 3: Negative current is defined as coming out of the pin.

<sup>†</sup> Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

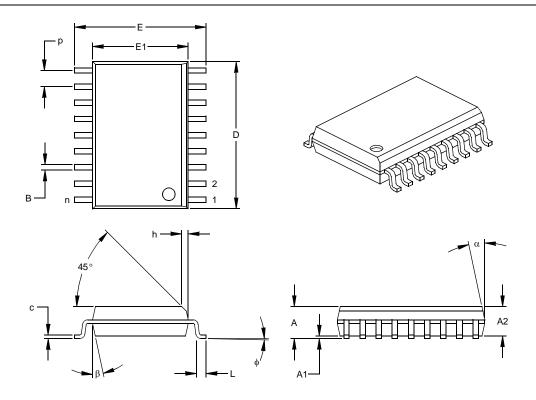

# 18-Lead Plastic Small Outline (SO) - Wide, 300 mil (SOIC)

For the most current package drawings, please see the Microchip Packaging Specification located Note: at http://www.microchip.com/packaging

|                          | Units |      | INCHES* |      | MILLIMETERS |       |       |

|--------------------------|-------|------|---------|------|-------------|-------|-------|

| Dimension                | MIN   | NOM  | MAX     | MIN  | NOM         | MAX   |       |

| Number of Pins           | n     |      | 18      |      |             | 18    |       |

| Pitch                    | р     |      | .050    |      |             | 1.27  |       |

| Overall Height           | Α     | .093 | .099    | .104 | 2.36        | 2.50  | 2.64  |

| Molded Package Thickness | A2    | .088 | .091    | .094 | 2.24        | 2.31  | 2.39  |

| Standoff §               | A1    | .004 | .008    | .012 | 0.10        | 0.20  | 0.30  |

| Overall Width            | Е     | .394 | .407    | .420 | 10.01       | 10.34 | 10.67 |

| Molded Package Width     | E1    | .291 | .295    | .299 | 7.39        | 7.49  | 7.59  |

| Overall Length           | D     | .446 | .454    | .462 | 11.33       | 11.53 | 11.73 |

| Chamfer Distance         | h     | .010 | .020    | .029 | 0.25        | 0.50  | 0.74  |

| Foot Length              | L     | .016 | .033    | .050 | 0.41        | 0.84  | 1.27  |

| Foot Angle               | ф     | 0    | 4       | 8    | 0           | 4     | 8     |

| Lead Thickness           | С     | .009 | .011    | .012 | 0.23        | 0.27  | 0.30  |

| Lead Width               | В     | .014 | .017    | .020 | 0.36        | 0.42  | 0.51  |

| Mold Draft Angle Top     | α     | 0    | 12      | 15   | 0           | 12    | 15    |

| Mold Draft Angle Bottom  | β     | 0    | 12      | 15   | 0           | 12    | 15    |

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side. JEDEC Equivalent: MS-013 Drawing No. C04-051

<sup>\*</sup> Controlling Parameter § Significant Characteristic

### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949

### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. & KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 1997-2013, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 9781620769355

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.