Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 20                                                                         |

| Program Memory Size        | 768B (512 x 12)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 25 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc55a-04-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

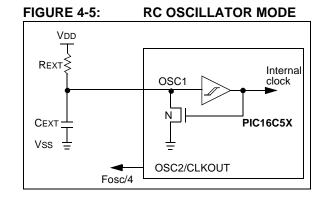

#### 4.4 RC Oscillator

For timing insensitive applications, the RC device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used.

Figure 4-5 shows how the R/C combination is connected to the PIC16C5X. For REXT values below 2.2 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high REXT values (e.g., 1 M $\Omega$ ) the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend keeping REXT between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (CEXT = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

The Electrical Specifications sections show RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

Also, see the Electrical Specifications sections for variation of oscillator frequency due to VDD for given REXT/ CEXT values as well as frequency variation due to operating temperature for given R, C, and VDD values.

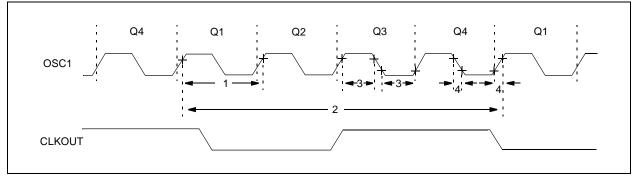

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin, and can be used for test purposes or to synchronize other logic.

**Note:** If you change from this device to another device, please verify oscillator characteristics in your application.

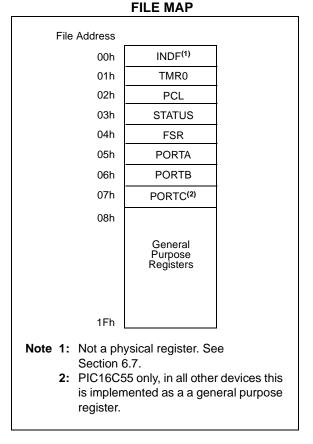

#### 6.2 Data Memory Organization

Data memory is composed of registers, or bytes of RAM. Therefore, data memory for a device is specified by its register file. The register file is divided into two functional groups: Special Function Registers and General Purpose Registers.

The Special Function Registers include the TMR0 register, the Program Counter (PC), the Status Register, the I/O registers (ports) and the File Select Register (FSR). In addition, Special Purpose Registers are used to control the I/O port configuration and prescaler options.

The General Purpose Registers are used for data and control information under command of the instructions.

For the PIC16C54, PIC16CR54, PIC16C56 and PIC16CR56, the register file is composed of 7 Special Function Registers and 25 General Purpose Registers (Figure 6-4).

For the PIC16C55, the register file is composed of 8 Special Function Registers and 24 General Purpose Registers.

For the PIC16C57 and PIC16CR57, the register file is composed of 8 Special Function Registers, 24 General Purpose Registers and up to 48 additional General Purpose Registers that may be addressed using a banking scheme (Figure 6-5).

For the PIC16C58 and PIC16CR58, the register file is composed of 7 Special Function Registers, 25 General Purpose Registers and up to 48 additional General Purpose Registers that may be addressed using a banking scheme (Figure 6-6).

#### 6.2.1 GENERAL PURPOSE REGISTER FILE

The register file is accessed either directly or indirectly through the File Select Register (FSR). The FSR Register is described in Section 6.7.

#### FIGURE 6-4: PIC16C54, PIC16CR54, PIC16C55, PIC16C56, PIC16CR56 REGISTER

| Mnemonic,        |         | Description                  | Cycles           | 12-1 | Bit Opc | ode  | Status   | Notoo |

|------------------|---------|------------------------------|------------------|------|---------|------|----------|-------|

| Opera            | nds     | Description                  |                  | MSb  |         | LSb  | Affected | Notes |

| ADDWF            | f,d     | Add W and f                  | 1                | 0001 | 11df    | ffff | C,DC,Z   | 1,2,4 |

| ANDWF            | f,d     | AND W with f                 | 1                | 0001 | 01df    | ffff | Z        | 2,4   |

| CLRF             | f       | Clear f                      | 1                | 0000 | 011f    | ffff | Z        | 4     |

| CLRW             | -       | Clear W                      | 1                | 0000 | 0100    | 0000 | Z        |       |

| COMF             | f, d    | Complement f                 | 1                | 0010 | 01df    | ffff | Z        |       |

| DECF             | f, d    | Decrement f                  | 1                | 0000 | 11df    | ffff | Z        | 2,4   |

| DECFSZ           | f, d    | Decrement f, Skip if 0       | 1 <sup>(2)</sup> | 0010 | 11df    | ffff | None     | 2,4   |

| INCF             | f, d    | Increment f                  | 1                | 0010 | 10df    | ffff | Z        | 2,4   |

| INCFSZ           | f, d    | Increment f, Skip if 0       | 1 <sup>(2)</sup> | 0011 | 11df    | ffff | None     | 2,4   |

| IORWF            | f, d    | Inclusive OR W with f        | 1                | 0001 | 00df    | ffff | Z        | 2,4   |

| MOVF             | f, d    | Move f                       | 1                | 0010 | 00df    | ffff | Z        | 2,4   |

| MOVWF            | f       | Move W to f                  | 1                | 0000 | 001f    | ffff | None     | 1,4   |

| NOP              | -       | No Operation                 | 1                | 0000 | 0000    | 0000 | None     |       |

| RLF              | f, d    | Rotate left f through Carry  | 1                | 0011 | 01df    | ffff | С        | 2,4   |

| RRF              | f, d    | Rotate right f through Carry | 1                | 0011 | 00df    | ffff | С        | 2,4   |

| SUBWF            | f, d    | Subtract W from f            | 1                | 0000 | 10df    | ffff | C,DC,Z   | 1,2,4 |

| SWAPF            | f, d    | Swap f                       | 1                | 0011 | 10df    | ffff | None     | 2,4   |

| XORWF            | f, d    | Exclusive OR W with f        | 1                | 0001 | 10df    | ffff | Z        | 2,4   |

| <b>BIT-ORIEN</b> | TED FIL | E REGISTER OPERATIONS        | •                |      |         |      |          |       |

| BCF              | f, b    | Bit Clear f                  | 1                | 0100 | bbbf    | ffff | None     | 2,4   |

| BSF              | f, b    | Bit Set f                    | 1                | 0101 | bbbf    | ffff | None     | 2,4   |

| BTFSC            | f, b    | Bit Test f, Skip if Clear    | 1 (2)            | 0110 | bbbf    | ffff | None     |       |

| BTFSS            | f, b    | Bit Test f, Skip if Set      | 1 (2)            | 0111 | bbbf    | ffff | None     |       |

| LITERAL A        | ND CON  | ITROL OPERATIONS             | •                |      |         |      |          |       |

| ANDLW            | k       | AND literal with W           | 1                | 1110 | kkkk    | kkkk | Z        |       |

| CALL             | k       | Call subroutine              | 2                | 1001 | kkkk    | kkkk | None     | 1     |

| CLRWDT           | k       | Clear Watchdog Timer         | 1                | 0000 | 0000    | 0100 | TO, PD   |       |

| GOTO             | k       | Unconditional branch         | 2                | 101k | kkkk    | kkkk | None     |       |

| IORLW            | k       | Inclusive OR Literal with W  | 1                | 1101 | kkkk    | kkkk | Z        |       |

| MOVLW            | k       | Move Literal to W            | 1                | 1100 | kkkk    | kkkk | None     |       |

| OPTION           | k       | Load OPTION register         | 1                | 0000 | 0000    | 0010 | None     |       |

| RETLW            | k       | Return, place Literal in W   | 2                | 1000 | kkkk    | kkkk | None     |       |

| SLEEP            | _       | Go into standby mode         | 1                | 0000 | 0000    | 0011 | TO, PD   |       |

| TRIS             | f       | Load TRIS register           | 1                | 0000 | 0000    | Offf | None     | 3     |

| XORLW            | k       | Exclusive OR Literal to W    | 1                | 1111 | kkkk    | kkkk | Z        |       |

#### TABLE 10-2: INSTRUCTION SET SUMMARY

**Note 1:** The 9th bit of the program counter will be forced to a '0' by any instruction that writes to the PC except for GOTO (see Section 6.5 for more on program counter).

2: When an I/O register is modified as a function of itself (e.g. MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

**3:** The instruction TRIS f, where f = 5, 6 or 7 causes the contents of the W register to be written to the tristate latches of PORTA, B or C respectively. A '1' forces the pin to a hi-impedance state and disables the output buffers.

**4:** If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared (if assigned to TMR0).

## 12.0 ELECTRICAL CHARACTERISTICS - PIC16C54A

#### Absolute Maximum Ratings<sup>(†)</sup>

| Ambient Temperature under bias                                   | –55°C to +125°C      |

|------------------------------------------------------------------|----------------------|

| Storage Temperature                                              | 65°C to +150°C       |

| Voltage on VDD with respect to VSS                               | 0V to +7.5V          |

| Voltage on MCLR with respect to Vss <sup>(1)</sup>               | 0V to +14V           |

| Voltage on all other pins with respect to Vss                    | 0.6V to (VDD + 0.6V) |

| Total power dissipation <sup>(2)</sup>                           | 800 mW               |

| Max. current out of Vss pin                                      | 150 mA               |

| Max. current into Vod pin                                        | 100 mA               |

| Max. current into an input pin (T0CKI only)                      | ±500 μA              |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                     | ±20 mA               |

| Output clamp current, IOK (VO < 0 or VO > VDD)                   | ±20 mA               |

| Max. output current sunk by any I/O pin                          | 25 mA                |

| Max. output current sourced by any I/O pin                       | 20 mA                |

| Max. output current sourced by a single I/O port (PORTA, B or C) | 40 mA                |

| Max. output current sunk by a single I/O port (PORTA, B or C)    | 50 mA                |

|                                                                  |                      |

- **Note 1:** Voltage spikes below Vss at the  $\overline{\text{MCLR}}$  pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50 to 100  $\Omega$  should be used when applying a "low" level to the  $\overline{\text{MCLR}}$  pin rather than pulling this pin directly to Vss.

- 2: Power Dissipation is calculated as follows: Pdis = VDD x {IDD  $\Sigma$  IOH} +  $\Sigma$  {(VDD VOH) x IOH} +  $\Sigma$ (VOL x IOL)

† NOTICE: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### 12.7 Timing Diagrams and Specifications

#### FIGURE 12-2: EXTERNAL CLOCK TIMING - PIC16C54/55/56/57

#### TABLE 12-1: EXTERNAL CLOCK TIMING REQUIREMENTS - PIC16C54/55/56/57

| AC Characteristics |        | -4(                                     | )°C ≤ 1<br>)°C ≤ 1 | nless otł<br>Ā ≤ +70°<br>Ā ≤ +85°<br>Ā ≤ +125 | C for cor<br>C for ind | nmercia<br>ustrial | ·                      |

|--------------------|--------|-----------------------------------------|--------------------|-----------------------------------------------|------------------------|--------------------|------------------------|

| Param<br>No.       | Symbol | Characteristic                          | Min                | Тур†                                          | Max                    | Units              | Conditions             |

| 1A                 | Fosc   | External CLKIN Frequency <sup>(1)</sup> | DC                 |                                               | 4.0                    | MHz                | XT OSC mode            |

|                    |        |                                         | DC                 | —                                             | 10                     | MHz                | 10 MHz mode            |

|                    |        |                                         | DC                 | _                                             | 20                     | MHz                | HS osc mode (Comm/Ind) |

|                    |        |                                         | DC                 | _                                             | 16                     | MHz                | HS osc mode (Ext)      |

|                    |        |                                         | DC                 | —                                             | 40                     | kHz                | LP osc mode            |

|                    |        | Oscillator Frequency <sup>(1)</sup>     | DC                 | _                                             | 4.0                    | MHz                | RC osc mode            |

|                    |        |                                         | 0.1                | _                                             | 4.0                    | MHz                | XT OSC mode            |

|                    |        |                                         | 4.0                | _                                             | 10                     | MHz                | 10 MHz mode            |

|                    |        |                                         | 4.0                | —                                             | 20                     | MHz                | HS OSC mode (Comm/Ind) |

|                    |        |                                         | 4.0                | _                                             | 16                     | MHz                | HS osc mode (Ext)      |

|                    |        |                                         | DC                 | —                                             | 40                     | kHz                | LP osc mode            |

\* These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

**2:** Instruction cycle period (TCY) equals four times the input oscillator time base period.

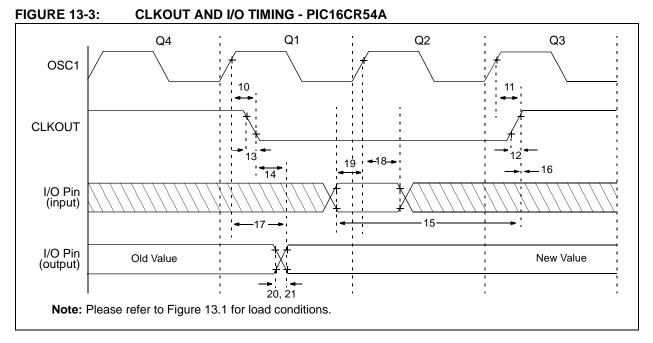

#### TABLE 13-2: CLKOUT AND I/O TIMING REQUIREMENTS - PIC16CR54A

| AC Chara     | acteristics | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array}$ |              |      |      |       |  |  |

|--------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|------|-------|--|--|

| Param<br>No. | Symbol      | Characteristic                                                                                                                                                                                                                                                                                                                   | Min          | Тур† | Max  | Units |  |  |

| 10           | TosH2ckL    | OSC1↑ to CLKOUT↓ <sup>(1)</sup>                                                                                                                                                                                                                                                                                                  | —            | 15   | 30** | ns    |  |  |

| 11           | TosH2ckH    | OSC1↑ to CLKOUT↑ <sup>(1)</sup>                                                                                                                                                                                                                                                                                                  | —            | 15   | 30** | ns    |  |  |

| 12           | TckR        | CLKOUT rise time <sup>(1)</sup>                                                                                                                                                                                                                                                                                                  | —            | 5.0  | 15** | ns    |  |  |

| 13           | TckF        | CLKOUT fall time <sup>(1)</sup>                                                                                                                                                                                                                                                                                                  | —            | 5.0  | 15** | ns    |  |  |

| 14           | TckL2ioV    | CLKOUT↓ to Port out valid <sup>(1)</sup>                                                                                                                                                                                                                                                                                         | —            | —    | 40** | ns    |  |  |

| 15           | TioV2ckH    | Port in valid before CLKOUT <sup>(1)</sup>                                                                                                                                                                                                                                                                                       | 0.25 TCY+30* | —    |      | ns    |  |  |

| 16           | TckH2iol    | Port in hold after CLKOUT <sup>(1)</sup>                                                                                                                                                                                                                                                                                         | 0*           | —    |      | ns    |  |  |

| 17           | TosH2ioV    | OSC1↑ (Q1 cycle) to Port out valid <sup>(2)</sup>                                                                                                                                                                                                                                                                                | —            | —    | 100* | ns    |  |  |

| 18           | TosH2iol    | OSC1 <sup>↑</sup> (Q2 cycle) to Port input invalid (I/O in hold time)                                                                                                                                                                                                                                                            | TBD          | —    | —    | ns    |  |  |

| 19           | TioV2osH    | Port input valid to OSC1↑<br>(I/O in setup time)                                                                                                                                                                                                                                                                                 | TBD          | —    | —    | ns    |  |  |

| 20           | TioR        | Port output rise time <sup>(2)</sup>                                                                                                                                                                                                                                                                                             | _            | 10   | 25** | ns    |  |  |

| 21           | TioF        | Port output fall time <sup>(2)</sup>                                                                                                                                                                                                                                                                                             | _            | 10   | 25** | ns    |  |  |

\* These parameters are characterized but not tested.

- \*\* These parameters are design targets and are not tested. No characterization data available at this time.

- † Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

**Note 1:** Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

2: Please refer to Figure 13.1 for load conditions.

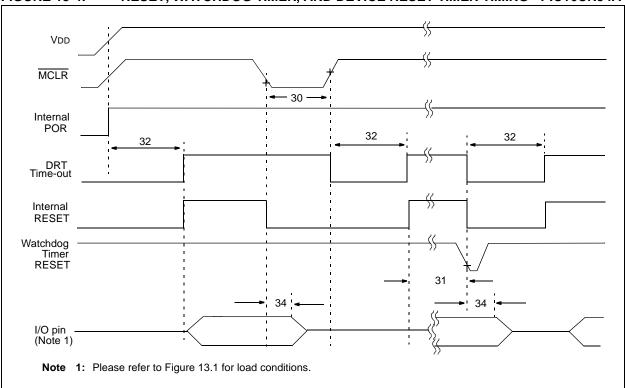

#### FIGURE 13-4: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING - PIC16CR54A

#### TABLE 13-3: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER - PIC16CR54A

| AC Chara     | cteristics | Standard Operating Conditions (uOperating Temperature $0^{\circ}C \leq$ $-40^{\circ}C \leq$ $-40^{\circ}C \leq$ | TA ≤ +7<br>TA ≤ +8                         | 0°C for<br>5°C for | comme<br>industria | rcial<br>al |                   |  |  |

|--------------|------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------|--------------------|-------------|-------------------|--|--|

| Param<br>No. | Symbol     | Characteristic                                                                                                  | Characteristic Min Typ† Max Units Conditio |                    |                    |             |                   |  |  |

| 30           | TmcL       | MCLR Pulse Width (low)                                                                                          | 1.0*                                       |                    |                    | μS          | VDD = 5.0V        |  |  |

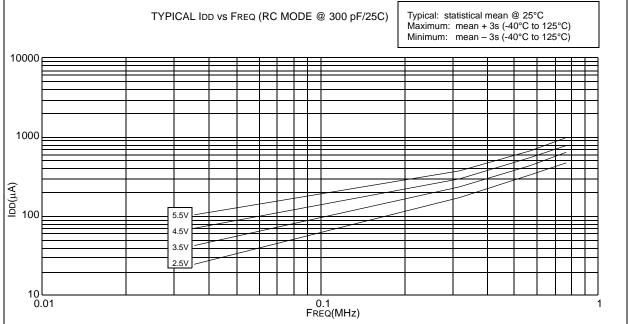

| 31           | Twdt       | Watchdog Timer Time-out Period<br>(No Prescaler)                                                                | 7.0*                                       | 18*                | 40*                | ms          | VDD = 5.0V (Comm) |  |  |

| 32           | Tdrt       | Device Reset Timer Period                                                                                       | 7.0*                                       | 18*                | 30*                | ms          | VDD = 5.0V (Comm) |  |  |

| 34           | Tioz       | I/O Hi-impedance from MCLR Low                                                                                  | _                                          | _                  | 1.0*               | μS          |                   |  |  |

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

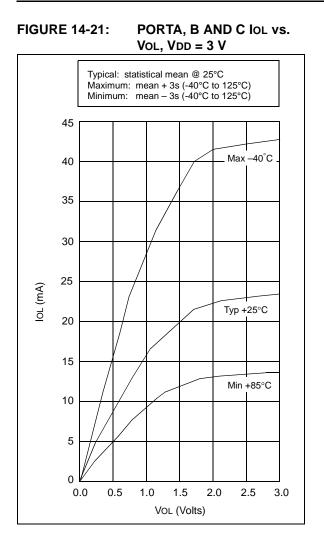

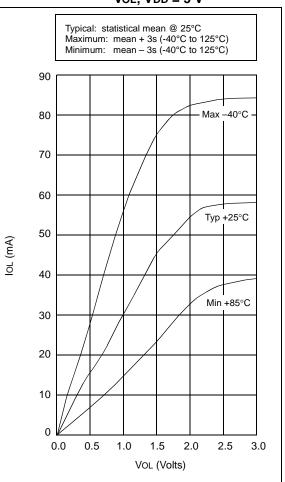

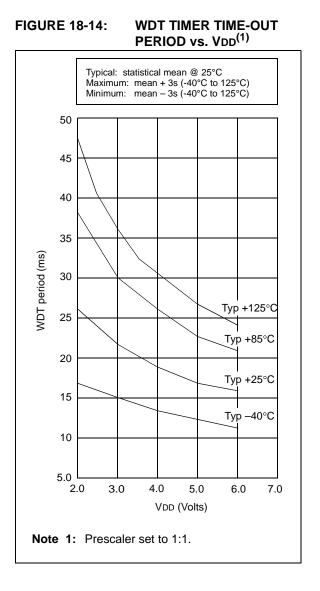

#### FIGURE 14-22: PORTA, B AND C IOL vs. VoL, VDD = 5 V

# PIC16C5X

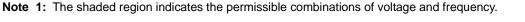

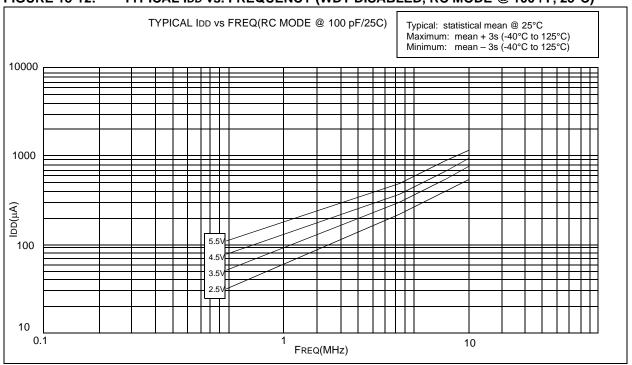

**2:** The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

2: The maximum rated speed of the part limits the permissible combinations of voltage and frequency.

Please reference the Product Identification System section for the maximum rated speed of the parts.

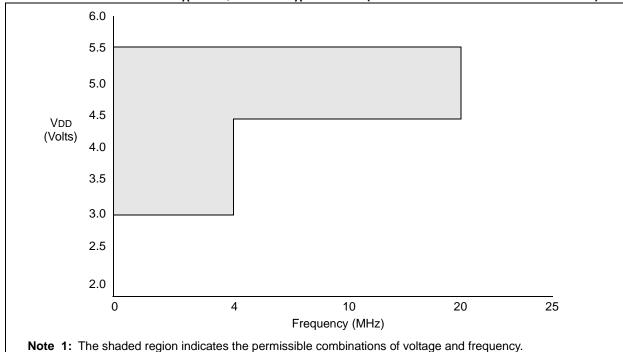

#### **FIGURE 17-9:** TIMER0 CLOCK TIMINGS - PIC16C5X, PIC16CR5X

#### **TABLE 17-4:** TIMER0 CLOCK REQUIREMENTS - PIC16C5X, PIC16CR5X

| ļ            | AC Chara | Standard Operatin<br>Operating Temperat  |                              | TA ≤ +7<br>TA ≤ +8 | 0°C fo<br>5°C fo | r comm<br>r indust | ercial<br>rial                                                 |

|--------------|----------|------------------------------------------|------------------------------|--------------------|------------------|--------------------|----------------------------------------------------------------|

| Param<br>No. | Symbol   | Characteristic                           | Min                          | Тур†               | Max              | Units              | Conditions                                                     |

| 40           | Tt0H     | T0CKI High Pulse Width<br>- No Prescaler | 0.5 Tcy + 20*                | _                  | _                | ns                 |                                                                |

|              |          | - With Prescaler                         | 10*                          | —                  | —                | ns                 |                                                                |

| 41           | TtOL     | T0CKI Low Pulse Width<br>- No Prescaler  | 0.5 Tcy + 20*                | _                  | _                | ns                 |                                                                |

|              |          | - With Prescaler                         | 10*                          | —                  | _                | ns                 |                                                                |

| 42           | Tt0P     | T0CKI Period                             | 20 or <u>Tcy + 40</u> *<br>N |                    | _                | ns                 | Whichever is greater.<br>N = Prescale Value<br>(1, 2, 4,, 256) |

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

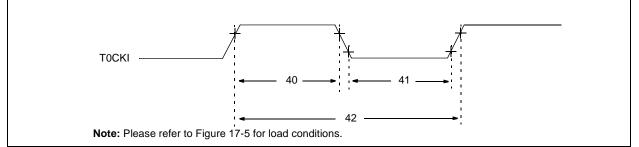

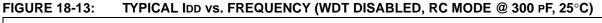

#### FIGURE 18-12: TYPICAL IDD vs. FREQUENCY (WDT DISABLED, RC MODE @ 100 PF, 25°C)

# PIC16C5X

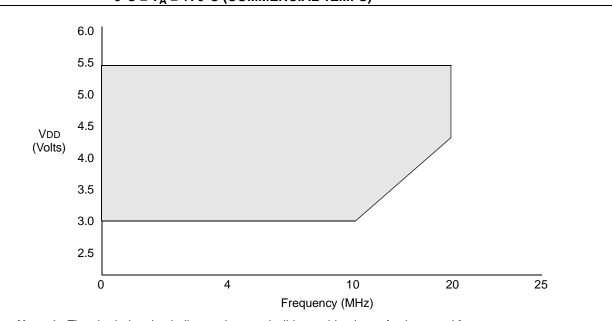

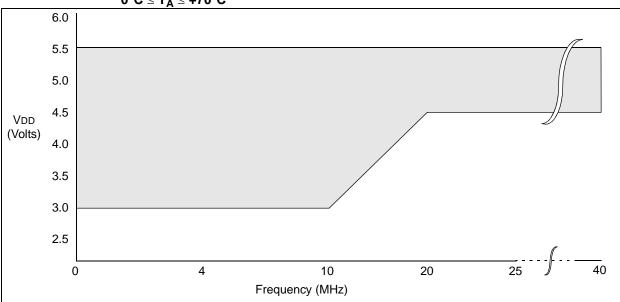

FIGURE 19-1: PIC16C54C/C55A/C56A/C57C/C58B-40 VOLTAGE-FREQUENCY GRAPH,  $0^{\circ}C \le T_A \le +70^{\circ}C$

- **2:** The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

- **3:** Operation between 20 to 40 MHz requires the following:

- VDD between 4.5V. and 5.5V

- OSC1 externally driven

- OSC2 not connected

- HS mode

- Commercial temperatures

Devices qualified for 40 MHz operation have -40 designation (ex: PIC16C54C-40/P).

4: For operation between DC and 20 MHz, see Section 17.1.

## 19.2 DC Characteristics: PIC16C54C/C55A/C56A/C57C/C58B-40 (Commercial)<sup>(1)</sup>

| DC CH        | ARACTER | RISTICS                                                                                      | Standard Operating Conditions (unless otherwise specified)Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial |                               |                                        |                            |                                                                                                                                                                               |  |

|--------------|---------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No. | Symbol  | Characteristic                                                                               | Min                                                                                                                                 | Тур†                          | Max                                    | Units                      | Conditions                                                                                                                                                                    |  |

| D030         | VIL     | Input Low Voltage<br>I/O Ports<br>MCLR (Schmitt Trigger)<br>T0CKI (Schmitt Trigger)<br>OSC1  | Vss<br>Vss<br>Vss<br>Vss                                                                                                            |                               | 0.8<br>0.15 VDD<br>0.15 VDD<br>0.2 VDD | > > > >                    | 4.5V <vdd <math="">\leq 5.5V<br/>HS, 20 MHz <math>\leq</math> Fosc <math>\leq</math> 40 MHz</vdd>                                                                             |  |

| D040         | Viн     | Input High Voltage<br>I/O ports<br>MCLR (Schmitt Trigger)<br>T0CKI (Schmitt Trigger)<br>OSC1 | 2.0<br>0.85 Vdd<br>0.85 Vdd<br>0.85 Vdd<br>0.8 Vdd                                                                                  |                               | Vdd<br>Vdd<br>Vdd<br>Vdd               | V<br>V<br>V<br>V           | $4.5V < VDD \le 5.5V$<br>HS, 20 MHz $\le$ Fosc $\le$ 40 MHz                                                                                                                   |  |

| D050         | VHYS    | Hysteresis of Schmitt<br>Trigger inputs                                                      | 0.15 Vdd*                                                                                                                           | —                             | _                                      | V                          |                                                                                                                                                                               |  |

| D060         | lı∟     | Input Leakage Current <sup>(2,3)</sup><br>I/O ports<br>MCLR<br>MCLR<br>T0CKI<br>OSC1         | -1.0<br>-5.0<br><br>-3.0<br>-3.0                                                                                                    | 0.5<br>—<br>0.5<br>0.5<br>0.5 | +1.0<br>+5.0<br>+3.0<br>+3.0<br>—      | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ | For VDD $\leq$ 5.5V:<br>VSS $\leq$ VPIN $\leq$ VDD,<br>pin at hi-impedance<br>VPIN = VSS +0.25V<br>VPIN = VDD<br>VSS $\leq$ VPIN $\leq$ VDD<br>VSS $\leq$ VPIN $\leq$ VDD, HS |  |

| D080         | Vol     | Output Low Voltage<br>I/O ports                                                              |                                                                                                                                     | _                             | 0.6                                    | V                          | Iol = 8.7 mA, Vdd = 4.5V                                                                                                                                                      |  |

| D090         | Vон     | <b>Output High Voltage<sup>(3)</sup></b><br>I/O ports                                        | Vdd - 0.7                                                                                                                           | _                             | _                                      | V                          | Іон = -5.4 mA, Vdd = 4.5V                                                                                                                                                     |  |

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

**Note 1:** Device operation between 20 MHz to 40 MHz requires the following: VDD between 4.5V to 5.5V, OSC1 pin externally driven, OSC2 pin not connected and HS oscillator mode and commercial temperatures. For operation between DC and 20 MHz, See Section 17.3.

2: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltage.

**3:** Negative current is defined as coming out of the pin.

### Package Marking Information (Cont'd)

18-Lead CERDIP Windowed

|  | XXXXXXXX<br>XXXXXXXX<br>YYWWNNN |

|--|---------------------------------|

|--|---------------------------------|

#### 28-Lead CERDIP Windowed

Example

#### Example

| Lege | end: XX?<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | <ul> <li>Customer-specific information<br/>Year code (last digit of calendar year)<br/>Year code (last 2 digits of calendar year)<br/>Week code (week of January 1 is week '01')<br/>Alphanumeric traceability code<br/>Pb-free JEDEC designator for Matte Tin (Sn)<br/>This package is Pb-free. The Pb-free JEDEC designator (e3)<br/>can be found on the outer packaging for this package.</li> </ul> |

|------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note | be carr                                     | vent the full Microchip part number cannot be marked on one line, it will ied over to the next line, thus limiting the number of available ers for customer-specific information.                                                                                                                                                                                                                       |

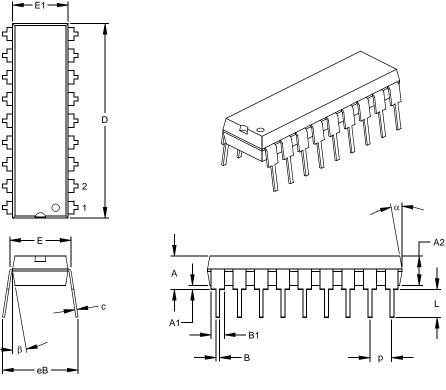

#### 18-Lead Plastic Dual In-line (P) – 300 mil (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units INCHES*    |      |      |      | N     | IILLIMETERS | 5     |

|----------------------------|------------------|------|------|------|-------|-------------|-------|

| Dimensio                   | Dimension Limits |      |      | MAX  | MIN   | NOM         | MAX   |

| Number of Pins             | n                |      | 18   |      |       | 18          |       |

| Pitch                      | р                |      | .100 |      |       | 2.54        |       |

| Top to Seating Plane       | Α                | .140 | .155 | .170 | 3.56  | 3.94        | 4.32  |

| Molded Package Thickness   | A2               | .115 | .130 | .145 | 2.92  | 3.30        | 3.68  |

| Base to Seating Plane      | A1               | .015 |      |      | 0.38  |             |       |

| Shoulder to Shoulder Width | Е                | .300 | .313 | .325 | 7.62  | 7.94        | 8.26  |

| Molded Package Width       | E1               | .240 | .250 | .260 | 6.10  | 6.35        | 6.60  |

| Overall Length             | D                | .890 | .898 | .905 | 22.61 | 22.80       | 22.99 |

| Tip to Seating Plane       | L                | .125 | .130 | .135 | 3.18  | 3.30        | 3.43  |

| Lead Thickness             | С                | .008 | .012 | .015 | 0.20  | 0.29        | 0.38  |

| Upper Lead Width           | B1               | .045 | .058 | .070 | 1.14  | 1.46        | 1.78  |

| Lower Lead Width           | В                | .014 | .018 | .022 | 0.36  | 0.46        | 0.56  |

| Overall Row Spacing §      | eB               | .310 | .370 | .430 | 7.87  | 9.40        | 10.92 |

| Mold Draft Angle Top       | α                | 5    | 10   | 15   | 5     | 10          | 15    |

| Mold Draft Angle Bottom    | β                | 5    | 10   | 15   | 5     | 10          | 15    |

\* Controlling Parameter § Significant Characteristic

Notes:

n

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-001 Drawing No. C04-007

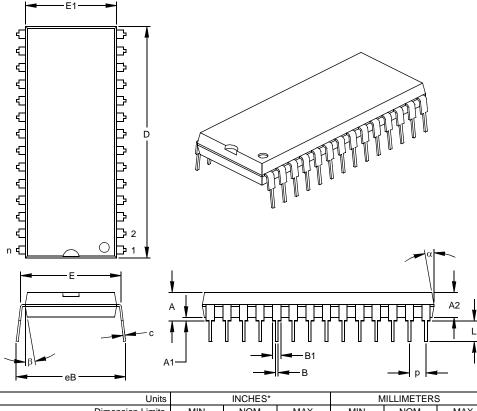

### 28-Lead Plastic Dual In-line (P) - 600 mil (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units        |       | INCHES* | MILLIMETERS |       |       |       |

|----------------------------|--------------|-------|---------|-------------|-------|-------|-------|

| Dimer                      | ision Limits | MIN   | NOM     | MAX         | MIN   | NOM   | MAX   |

| Number of Pins             | n            |       | 28      |             |       | 28    |       |

| Pitch                      | р            |       | .100    |             |       | 2.54  |       |

| Top to Seating Plane       | А            | .160  | .175    | .190        | 4.06  | 4.45  | 4.83  |

| Molded Package Thickness   | A2           | .140  | .150    | .160        | 3.56  | 3.81  | 4.06  |

| Base to Seating Plane      | A1           | .015  |         |             | 0.38  |       |       |

| Shoulder to Shoulder Width | E            | .595  | .600    | .625        | 15.11 | 15.24 | 15.88 |

| Molded Package Width       | E1           | .505  | .545    | .560        | 12.83 | 13.84 | 14.22 |

| Overall Length             | D            | 1.395 | 1.430   | 1.465       | 35.43 | 36.32 | 37.21 |

| Tip to Seating Plane       | L            | .120  | .130    | .135        | 3.05  | 3.30  | 3.43  |

| Lead Thickness             | С            | .008  | .012    | .015        | 0.20  | 0.29  | 0.38  |

| Upper Lead Width           | B1           | .030  | .050    | .070        | 0.76  | 1.27  | 1.78  |

| Lower Lead Width           | В            | .014  | .018    | .022        | 0.36  | 0.46  | 0.56  |

| Overall Row Spacing        | § eB         | .620  | .650    | .680        | 15.75 | 16.51 | 17.27 |

| Mold Draft Angle Top       | α            | 5     | 10      | 15          | 5     | 10    | 15    |

| Mold Draft Angle Bottom    | β            | 5     | 10      | 15          | 5     | 10    | 15    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

JEDEC Equivalent: MO-011 Drawing No. C04-079

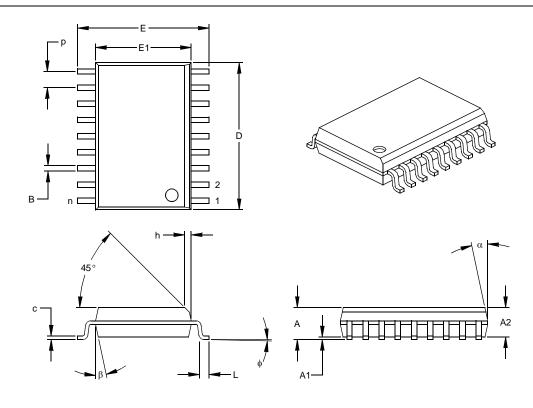

#### 18-Lead Plastic Small Outline (SO) - Wide, 300 mil (SOIC)

For the most current package drawings, please see the Microchip Packaging Specification located Note: at http://www.microchip.com/packaging

|                          | Units     | INCHES* |      |      | MILLIMETERS |       |       |

|--------------------------|-----------|---------|------|------|-------------|-------|-------|

| Dimensi                  | on Limits | MIN     | NOM  | MAX  | MIN         | NOM   | MAX   |

| Number of Pins           | n         |         | 18   |      |             | 18    |       |

| Pitch                    | р         |         | .050 |      |             | 1.27  |       |

| Overall Height           | А         | .093    | .099 | .104 | 2.36        | 2.50  | 2.64  |

| Molded Package Thickness | A2        | .088    | .091 | .094 | 2.24        | 2.31  | 2.39  |

| Standoff §               | A1        | .004    | .008 | .012 | 0.10        | 0.20  | 0.30  |

| Overall Width            | E         | .394    | .407 | .420 | 10.01       | 10.34 | 10.67 |

| Molded Package Width     | E1        | .291    | .295 | .299 | 7.39        | 7.49  | 7.59  |

| Overall Length           | D         | .446    | .454 | .462 | 11.33       | 11.53 | 11.73 |

| Chamfer Distance         | h         | .010    | .020 | .029 | 0.25        | 0.50  | 0.74  |

| Foot Length              | L         | .016    | .033 | .050 | 0.41        | 0.84  | 1.27  |

| Foot Angle               | φ         | 0       | 4    | 8    | 0           | 4     | 8     |

| Lead Thickness           | С         | .009    | .011 | .012 | 0.23        | 0.27  | 0.30  |

| Lead Width               | В         | .014    | .017 | .020 | 0.36        | 0.42  | 0.51  |

| Mold Draft Angle Top     | α         | 0       | 12   | 15   | 0           | 12    | 15    |

| Mold Draft Angle Bottom  | β         | 0       | 12   | 15   | 0           | 12    | 15    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-013 Drawing No. C04-051

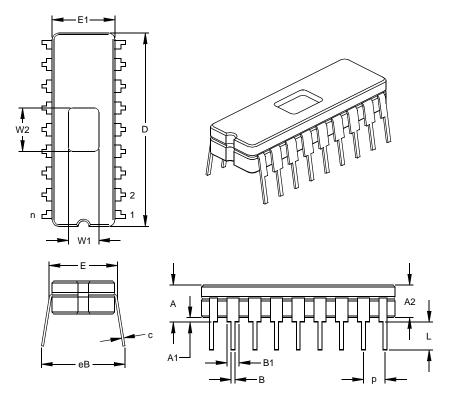

### 18-Lead Ceramic Dual In-line with Window (JW) - 300 mil (CERDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units INCHES* |      |      | MILLIMETERS |       |       |       |

|----------------------------|---------------|------|------|-------------|-------|-------|-------|

| Dimensior                  | n Limits      | MIN  | NOM  | MAX         | MIN   | NOM   | MAX   |

| Number of Pins             | n             |      | 18   |             |       | 18    |       |

| Pitch                      | р             |      | .100 |             |       | 2.54  |       |

| Top to Seating Plane       | А             | .170 | .183 | .195        | 4.32  | 4.64  | 4.95  |

| Ceramic Package Height     | A2            | .155 | .160 | .165        | 3.94  | 4.06  | 4.19  |

| Standoff                   | A1            | .015 | .023 | .030        | 0.38  | 0.57  | 0.76  |

| Shoulder to Shoulder Width | Е             | .300 | .313 | .325        | 7.62  | 7.94  | 8.26  |

| Ceramic Pkg. Width         | E1            | .285 | .290 | .295        | 7.24  | 7.37  | 7.49  |

| Overall Length             | D             | .880 | .900 | .920        | 22.35 | 22.86 | 23.37 |

| Tip to Seating Plane       | L             | .125 | .138 | .150        | 3.18  | 3.49  | 3.81  |

| Lead Thickness             | С             | .008 | .010 | .012        | 0.20  | 0.25  | 0.30  |

| Upper Lead Width           | B1            | .050 | .055 | .060        | 1.27  | 1.40  | 1.52  |

| Lower Lead Width           | В             | .016 | .019 | .021        | 0.41  | 0.47  | 0.53  |

| Overall Row Spacing §      | eВ            | .345 | .385 | .425        | 8.76  | 9.78  | 10.80 |

| Window Width               | W1            | .130 | .140 | .150        | 3.30  | 3.56  | 3.81  |

| Window Length              | W2            | .190 | .200 | .210        | 4.83  | 5.08  | 5.33  |

\* Controlling Parameter § Significant Characteristic JEDEC Equivalent: MO-036

Drawing No. C04-010

NOTES: