#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 1.5KB (1K x 12)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 25 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 18-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc56a-04i-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16C5X

### 8-Bit EPROM/ROM-Based CMOS Microcontrollers

#### 1.0 GENERAL DESCRIPTION

The PIC16C5X from Microchip Technology is a family of low cost, high performance, 8-bit fully static, EPROM/ROM-based CMOS microcontrollers. It employs a RISC architecture with only 33 single word/ single cycle instructions. All instructions are single cycle except for program branches which take two cycles. The PIC16C5X delivers performance in an order of magnitude higher than its competitors in the same price category. The 12-bit wide instructions are highly symmetrical resulting in 2:1 code compression over other 8-bit microcontrollers in its class. The easy to use and easy to remember instruction set reduces development time significantly.

The PIC16C5X products are equipped with special features that reduce system cost and power requirements. The Power-on Reset (POR) and Device Reset Timer (DRT) eliminate the need for external RESET circuitry. There are four oscillator configurations to choose from, including the power saving LP (Low Power) oscillator and cost saving RC oscillator. Power saving SLEEP mode, Watchdog Timer and Code Protection features improve system cost, power and reliability.

The UV erasable CERDIP packaged versions are ideal for code development, while the cost effective One Time Programmable (OTP) versions are suitable for production in any volume. The customer can take full advantage of Microchip's price leadership in OTP microcontrollers, while benefiting from the OTP's flexibility.

The PIC16C5X products are supported by a full featured macro assembler, a software simulator, an in-circuit emulator, a low cost development programmer and a full featured programmer. All the tools are supported on IBM<sup>®</sup> PC and compatible machines.

#### 1.1 Applications

The PIC16C5X series fits perfectly in applications ranging from high speed automotive and appliance motor control to low power remote transmitters/receivers, pointing devices and telecom processors. The EPROM technology makes customizing application programs (transmitter codes, motor speeds, receiver frequencies, etc.) extremely fast and convenient. The small footprint packages, for through hole or surface mounting, make this microcontroller series perfect for applications with space limitations. Low cost, low power, high performance ease of use and I/O flexibility make the PIC16C5X series very versatile even in areas where no microcontroller use has been considered before (e.g., timer functions, replacement of "glue" logic in larger systems, co-processor applications).

#### 5.1 Power-On Reset (POR)

The PIC16C5X family incorporates on-chip Power-On Reset (POR) circuitry which provides an internal chip RESET for most power-up situations. To use this feature, the user merely ties the MCLR/VPP pin to VDD. A simplified block diagram of the on-chip Power-On Reset circuit is shown in Figure 5-1.

The Power-On Reset circuit and the Device Reset Timer (Section 5.2) circuit are closely related. On power-up, the RESET latch is set and the DRT is <u>RESET</u>. The DRT timer begins counting once it detects MCLR to be high. After the time-out period, which is typically 18 ms, it will RESET the reset latch and thus end the on-chip RESET signal.

A power-up example where MCLR is not tied to VDD is shown in Figure 5-3. VDD is allowed to rise and stabilize before bringing MCLR high. The chip will actually come out of reset TDRT msec after MCLR goes high.

In Figure 5-4, the on-chip Power-On Reset feature is being used (MCLR and VDD are tied together). The VDD is stable before the start-up timer times out and there is no problem in getting a proper RESET. However, Figure 5-5 depicts a problem situation where VDD rises too slowly. The time between when the DRT senses a high on the MCLR/VPP pin, and when the MCLR/VPP pin (and VDD) actually reach their full value, is too long. In this situation, when the start-up timer times out, VDD has not reached the VDD (min) value and the chip is, therefore, not guaranteed to function correctly. For such situations, we recommend that external RC circuits be used to achieve longer POR delay times (Figure 5-2).

Note: When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met.

For more information on PIC16C5X POR, see *Power-Up Considerations* - AN522 in the <u>Embedded Control Handbook</u>.

The POR circuit does not produce an internal RESET when VDD declines.

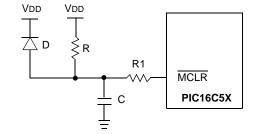

#### FIGURE 5-2:

#### EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- External Power-On Reset circuit is required only if VDD power-up is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- R < 40 kΩ is recommended to make sure that voltage drop across R does not violate the device electrical specification.

- R1 =  $100\Omega$  to 1 k $\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C in the event of  $\overline{MCLR}$  pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

#### 6.0 MEMORY ORGANIZATION

PIC16C5X memory is organized into program memory and data memory. For devices with more than 512 bytes of program memory, a paging scheme is used. Program memory pages are accessed using one or two STATUS Register bits. For devices with a data memory register file of more than 32 registers, a banking scheme is used. Data memory banks are accessed using the File Selection Register (FSR).

#### 6.1 Program Memory Organization

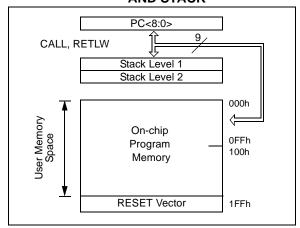

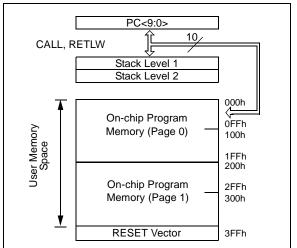

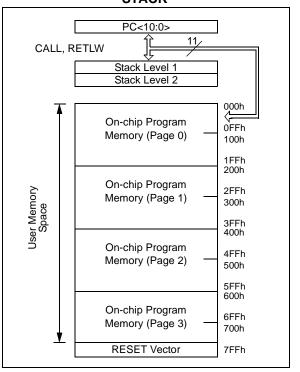

The PIC16C54, PIC16CR54 and PIC16C55 have a 9bit Program Counter (PC) capable of addressing a 512 x 12 program memory space (Figure 6-1). The PIC16C56 and PIC16CR56 have a 10-bit Program Counter (PC) capable of addressing a 1K x 12 program memory space (Figure 6-2). The PIC16CR57, PIC16C58 and PIC16CR58 have an 11-bit Program Counter capable of addressing a 2K x 12 program memory space (Figure 6-3). Accessing a location above the physically implemented address will cause a wraparound.

A NOP at the RESET vector location will cause a restart at location 000h. The RESET vector for the PIC16C54, PIC16CR54 and PIC16C55 is at 1FFh. The RESET vector for the PIC16C56 and PIC16CR56 is at 3FFh. The RESET vector for the PIC16C57, PIC16CR57, PIC16C58, and PIC16CR58 is at 7FFh. See Section 6.5 for additional information using CALL and GOTO instructions.

#### FIGURE 6-1: PIC16C54/CR54/C55 PROGRAM MEMORY MAP AND STACK

#### FIGURE 6-2:

#### PIC16C56/CR56 PROGRAM MEMORY MAP AND STACK

FIGURE 6-3:

PIC16C57/CR57/C58/ CR58 PROGRAM MEMORY MAP AND STACK

#### 6.3 STATUS Register

This register contains the arithmetic status of the ALU, the RESET status and the page preselect bits for program memories larger than 512 words.

The STATUS Register can be the destination for any instruction, as with any other register. If the STATUS Register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not

writable. Therefore, the result of an instruction with the STATUS Register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS Register as  $000u \ u1uu$  (where u = unchanged).

It is recommended, therefore, that only BCF, BSF and MOVWF instructions be used to alter the STATUS Register because these instructions do not affect the Z, DC or C bits from the STATUS Register. For other instructions which do affect STATUS Bits, see Section 10.0, Instruction Set Summary.

#### REGISTER 6-1: STATUS REGISTER (ADDRESS: 03h)

|          | R/W-0                                                                                                                                                         | R/W-0                              | R/W-0        | R-1          | R-1                        | R/W-x         | R/W-x          | R/W-x          |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------------|--------------|----------------------------|---------------|----------------|----------------|--|--|

|          | PA2                                                                                                                                                           | PA1                                | PA0          | TO           | PD                         | Z             | DC             | С              |  |  |

|          | bit 7                                                                                                                                                         |                                    |              |              |                            |               |                | bit 0          |  |  |

| bit 7:   | PA2: This bit                                                                                                                                                 | unused at th                       | is time.     |              |                            |               |                |                |  |  |

|          |                                                                                                                                                               | A2 bit as a ge<br>with future pr   |              | e read/write | bit is not recor           | mmended, sir  | nce this may a | affect upward  |  |  |

| bit 6-5: |                                                                                                                                                               |                                    |              | -            | CR56)(PIC16                |               |                | 58)            |  |  |

|          |                                                                                                                                                               |                                    |              |              | 16C57/CR57,<br>16C57/CR57, |               |                |                |  |  |

|          |                                                                                                                                                               | (400h - 5FFh                       |              |              |                            | FIC 10C30/C   | N00            |                |  |  |

|          | 11 = Page 3                                                                                                                                                   | (600h - 7FFh                       | •            |              |                            |               |                |                |  |  |

|          | Each page is                                                                                                                                                  |                                    | deperal pur  | ose read/wr  | ite bits in devi           | ices which do | not use them   | for program    |  |  |

|          |                                                                                                                                                               |                                    |              |              | affect upward              |               |                |                |  |  |

| bit 4:   | TO: Time-ou                                                                                                                                                   |                                    |              | ,            | •                          |               |                |                |  |  |

|          |                                                                                                                                                               | ver-up, CLRWI<br>ime-out occur     |              | , or sleep i | nstruction                 |               |                |                |  |  |

| bit 3:   | PD: Power-d                                                                                                                                                   | lown bit                           |              |              |                            |               |                |                |  |  |

|          | •                                                                                                                                                             | ver-up or by tl<br>ution of the SI |              |              |                            |               |                |                |  |  |

| bit 2:   | Z: Zero bit                                                                                                                                                   |                                    |              |              |                            |               |                |                |  |  |

|          |                                                                                                                                                               | lt of an arithm<br>It of an arithm |              |              |                            |               |                |                |  |  |

| bit 1:   | DC: Digit car                                                                                                                                                 | ry/borrow bit                      | (for ADDWF a | nd SUBWF in  | structions)                |               |                |                |  |  |

|          | ADDWF                                                                                                                                                         |                                    |              |              |                            |               |                |                |  |  |

|          | <ul> <li>1 = A carry from the 4th low order bit of the result occurred</li> <li>0 = A carry from the 4th low order bit of the result did not occur</li> </ul> |                                    |              |              |                            |               |                |                |  |  |

|          | SUBWF                                                                                                                                                         |                                    |              |              |                            |               |                |                |  |  |

|          |                                                                                                                                                               |                                    |              |              | did not occur              |               |                |                |  |  |

|          | 0 = A borrow from the 4th low order bit of the result occurred                                                                                                |                                    |              |              |                            |               |                |                |  |  |

| bit 0:   | •                                                                                                                                                             | row bit (for AI                    |              |              | F instructions             |               | _              |                |  |  |

|          | <b>ADDWF</b><br>1 = A carry o                                                                                                                                 | ocurred                            |              | orrow did n  | ot occur                   | RRF or RLI    |                | , respectively |  |  |

|          | $\pm = \pi \operatorname{carry} 0$                                                                                                                            | locurrou                           | / · ·        |              |                            |               |                |                |  |  |

| Legena:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | 1 = bit is set   | 0 = bit is cleared        | x = bit is unknown |

#### 9.3 Power-Down Mode (SLEEP)

A device may be powered down (SLEEP) and later powered up (Wake-up from SLEEP).

#### 9.3.1 SLEEP

The Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the TO bit (STATUS<4>) is set, the PD bit (STATUS<3>) is cleared and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, driving low, or hi-impedance).

It should be noted that a RESET generated by a WDT time-out does not drive the MCLR/VPP pin low.

For lowest current consumption while powered down, the T0CKI input should be at VDD or Vss and the  $\overline{\text{MCLR}}/\text{VPP}$  pin must be at a logic high level ( $\overline{\text{MCLR}} = \text{VIH}$ ).

#### 9.3.2 WAKE-UP FROM SLEEP

The device can wake up from SLEEP through one of the following events:

- 1. An external RESET input on MCLR/VPP pin.

- 2. A Watchdog Timer Time-out Reset (if WDT was enabled).

Both of these events cause a device RESET. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits can be used to determine the cause of device RESET. The  $\overline{\text{TO}}$  bit is cleared if a WDT timeout occurred (and caused wake-up). The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked.

The WDT is cleared when the device wakes from SLEEP, regardless of the wake-up source.

#### 9.4 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip does not recommend code pro- |

|-------|----------------------------------------|

|       | tecting windowed devices.              |

#### 9.5 ID Locations

Four memory locations are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify.

Use only the lower 4 bits of the ID locations and always program the upper 8 bits as '1's.

**Note:** Microchip will assign a unique pattern number for QTP and SQTP requests and for ROM devices. This pattern number will be unique and traceable to the submitted code.

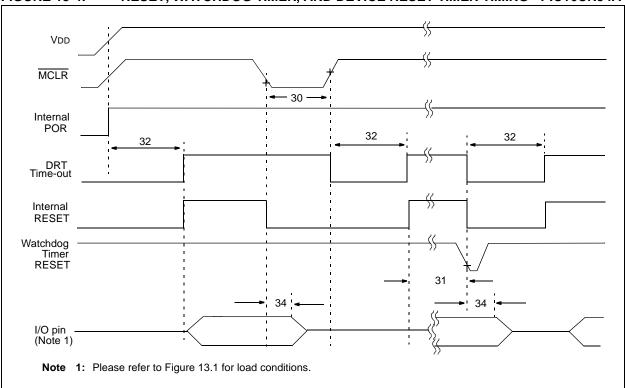

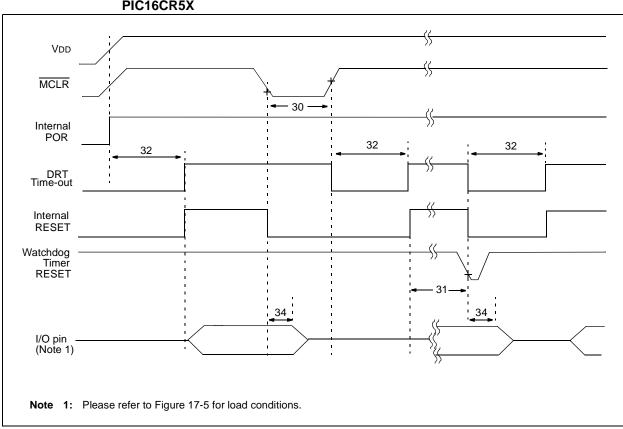

#### FIGURE 13-4: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING - PIC16CR54A

#### TABLE 13-3: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER - PIC16CR54A

| AC Chara     | cteristics | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array}$ |      |      |      |       |                   |  |

|--------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|-------------------|--|

| Param<br>No. | Symbol     | Characteristic                                                                                                                                                                                                                                                                                                                   | Min  | Тур† | Max  | Units | Conditions        |  |

| 30           | TmcL       | MCLR Pulse Width (low)                                                                                                                                                                                                                                                                                                           | 1.0* |      |      | μS    | VDD = 5.0V        |  |

| 31           | Twdt       | Watchdog Timer Time-out Period<br>(No Prescaler)                                                                                                                                                                                                                                                                                 | 7.0* | 18*  | 40*  | ms    | VDD = 5.0V (Comm) |  |

| 32           | Tdrt       | Device Reset Timer Period                                                                                                                                                                                                                                                                                                        | 7.0* | 18*  | 30*  | ms    | VDD = 5.0V (Comm) |  |

| 34           | Tioz       | I/O Hi-impedance from MCLR Low                                                                                                                                                                                                                                                                                                   | _    | _    | 1.0* | μS    |                   |  |

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

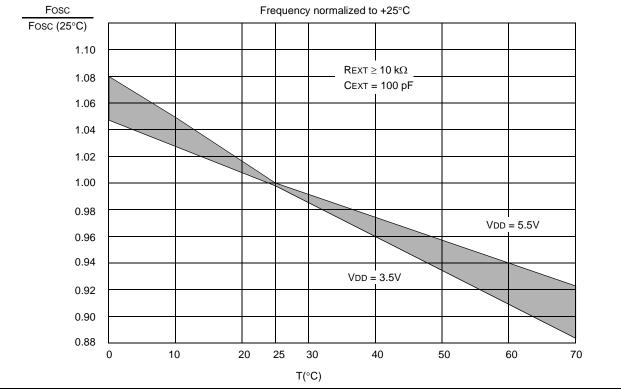

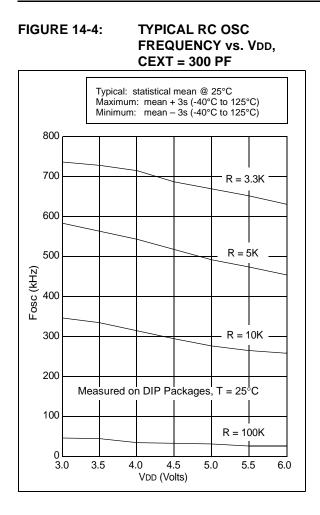

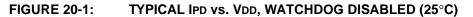

#### 14.0 DEVICE CHARACTERIZATION - PIC16C54A

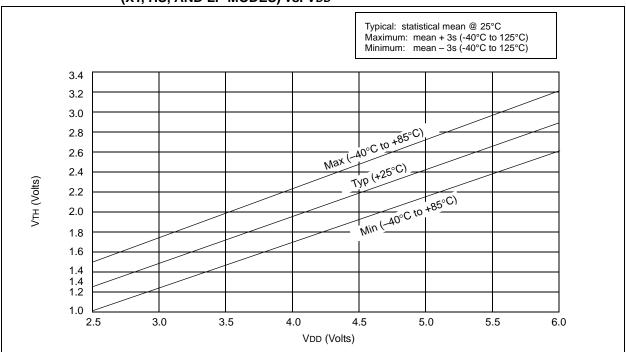

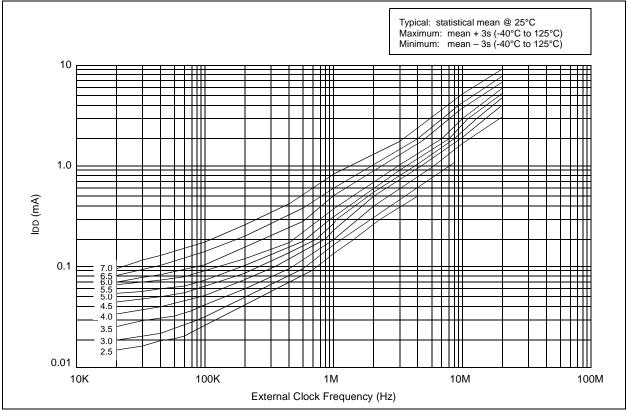

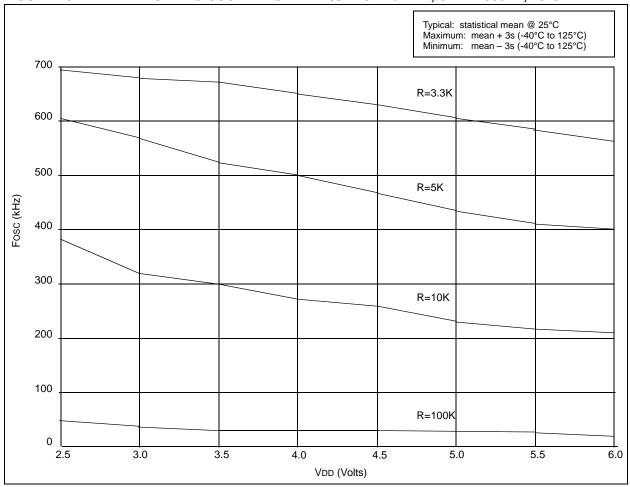

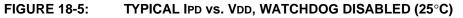

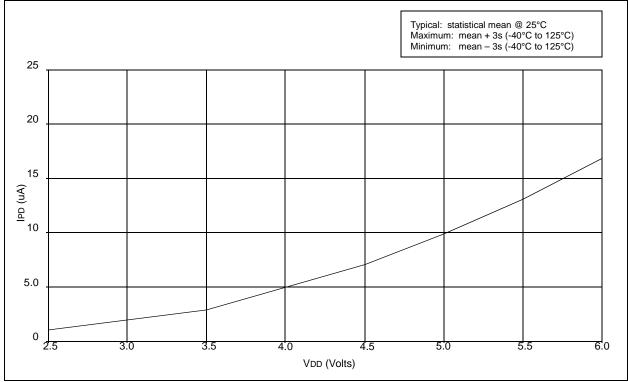

The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

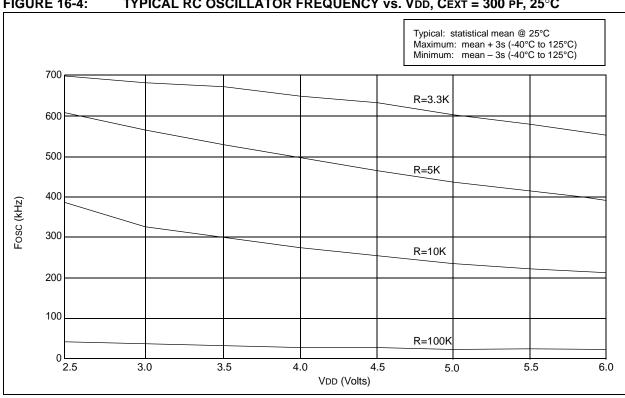

#### TABLE 14-1: RC OSCILLATOR FREQUENCIES

| Сехт   | Rext | Ave<br>Fosc @ |       |

|--------|------|---------------|-------|

| 20 pF  | 3.3K | 5 MHz         | ± 27% |

|        | 5K   | 3.8 MHz       | ± 21% |

|        | 10K  | 2.2 MHz       | ± 21% |

|        | 100K | 262 kHz       | ± 31% |

| 100 pF | 3.3K | 1.6 MHz       | ± 13% |

|        | 5K   | 1.2 MHz       | ± 13% |

|        | 10K  | 684 kHz       | ± 18% |

|        | 100K | 71 kHz        | ± 25% |

| 300 pF | 3.3K | 660 kHz       | ± 10% |

|        | 5.0K | 484 kHz       | ± 14% |

|        | 10K  | 267 kHz       | ± 15% |

|        | 100K | 29 kHz        | ± 19% |

The frequencies are measured on DIP packages.

The percentage variation indicated here is part-to-part variation due to normal process distribution. The variation indicated is  $\pm 3$  standard deviations from the average value for VDD = 5V.

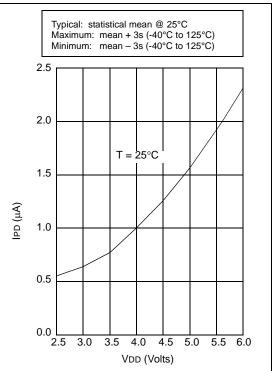

#### FIGURE 14-5: TYPICAL IPD vs. VDD, WATCHDOG DISABLED

# PIC16C5X

#### **FIGURE 16-4:** TYPICAL RC OSCILLATOR FREQUENCY vs. VDD, CEXT = 300 PF, 25°C

# PIC16C5X

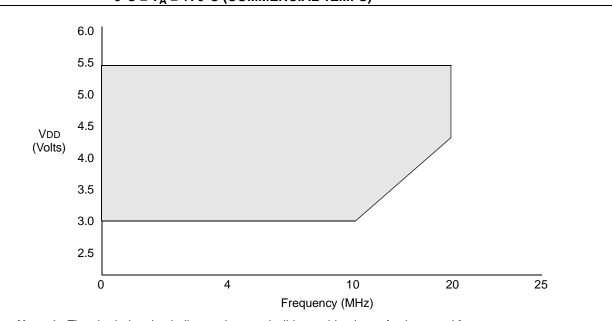

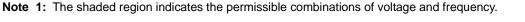

**2:** The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

2: The maximum rated speed of the part limits the permissible combinations of voltage and frequency.

Please reference the Product Identification System section for the maximum rated speed of the parts.

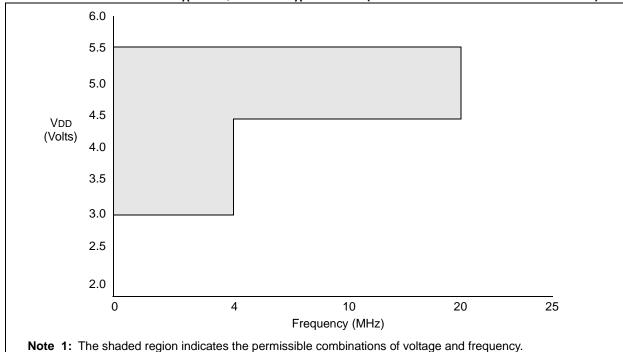

|             | ALVAUT AND VA TIMINA DEALUDENENTA DIALAASY DIALAADSY     |

|-------------|----------------------------------------------------------|

| IABLE 17-2: | CLKOUT AND I/O TIMING REQUIREMENTS - PIC16C5X, PIC16CR5X |

| AC Chara     | acteristics | $ \begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array} $ |              |      |      |       |  |  |  |

|--------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|------|-------|--|--|--|

| Param<br>No. | Symbol      | Characteristic                                                                                                                                                                                                                                                                                                                     | Min          | Тур† | Max  | Units |  |  |  |

| 10           | TosH2ckL    | OSC1↑ to CLKOUT↓ <sup>(1)</sup>                                                                                                                                                                                                                                                                                                    | _            | 15   | 30** | ns    |  |  |  |

| 11           | TosH2ckH    | OSC1↑ to CLKOUT↑ <sup>(1)</sup>                                                                                                                                                                                                                                                                                                    | _            | 15   | 30** | ns    |  |  |  |

| 12           | TckR        | CLKOUT rise time <sup>(1)</sup>                                                                                                                                                                                                                                                                                                    | —            | 5.0  | 15** | ns    |  |  |  |

| 13           | TckF        | CLKOUT fall time <sup>(1)</sup>                                                                                                                                                                                                                                                                                                    | —            | 5.0  | 15** | ns    |  |  |  |

| 14           | TckL2ioV    | CLKOUT↓ to Port out valid <sup>(1)</sup>                                                                                                                                                                                                                                                                                           | —            | —    | 40** | ns    |  |  |  |

| 15           | TioV2ckH    | Port in valid before CLKOUT <sup>(1)</sup>                                                                                                                                                                                                                                                                                         | 0.25 TCY+30* | —    | _    | ns    |  |  |  |

| 16           | TckH2iol    | Port in hold after CLKOUT <sup>(1)</sup>                                                                                                                                                                                                                                                                                           | 0*           | —    | _    | ns    |  |  |  |

| 17           | TosH2ioV    | OSC1 <sup>↑</sup> (Q1 cycle) to Port out valid <sup>(2)</sup>                                                                                                                                                                                                                                                                      | —            | —    | 100* | ns    |  |  |  |

| 18           | TosH2iol    | OSC1↑ (Q2 cycle) to Port input invalid<br>(I/O in hold time)                                                                                                                                                                                                                                                                       | TBD          | —    | _    | ns    |  |  |  |

| 19           | TioV2osH    | Port input valid to OSC1↑<br>(I/O in setup time)                                                                                                                                                                                                                                                                                   | TBD          | —    | —    | ns    |  |  |  |

| 20           | TioR        | Port output rise time <sup>(2)</sup>                                                                                                                                                                                                                                                                                               | _            | 10   | 25** | ns    |  |  |  |

| 21           | TioF        | Port output fall time <sup>(2)</sup>                                                                                                                                                                                                                                                                                               | —            | 10   | 25** | ns    |  |  |  |

\* These parameters are characterized but not tested.

\*\* These parameters are design targets and are not tested. No characterization data available at this time.

† Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

**2:** Refer to Figure 17-5 for load conditions.

### FIGURE 17-8: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING - PIC16C5X, PIC16CR5X

#### TABLE 17-3: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER - PIC16C5X, PIC16CR5X

| AC Charac    | teristics | $ \begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \\ \end{array} $ |       |      |       |       |                   |  |

|--------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-------|-------------------|--|

| Param<br>No. | Symbol    | Characteristic                                                                                                                                                                                                                                                                                                                        | Min   | Тур† | Мах   | Units | Conditions        |  |

| 30           | TmcL      | MCLR Pulse Width (low)                                                                                                                                                                                                                                                                                                                | 1000* |      | _     | ns    | VDD = 5.0V        |  |

| 31           | Twdt      | Watchdog Timer Time-out Period<br>(No Prescaler)                                                                                                                                                                                                                                                                                      | 9.0*  | 18*  | 30*   | ms    | VDD = 5.0V (Comm) |  |

| 32           | Tdrt      | Device Reset Timer Period                                                                                                                                                                                                                                                                                                             | 9.0*  | 18*  | 30*   | ms    | VDD = 5.0V (Comm) |  |

| 34           | Tioz      | I/O Hi-impedance from MCLR Low                                                                                                                                                                                                                                                                                                        | 100*  | 300* | 1000* | ns    |                   |  |

\* These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

© 1997-2013 Microchip Technology Inc.

FIGURE 18-4: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD, CEXT = 300 PF, 25°C

© 1997-2013 Microchip Technology Inc.

#### **19.3 Timing Parameter Symbology and Load Conditions**

The timing parameter symbols have been created with one of the following formats:

1. TppS2ppS

| 2. Tp | pS                                      |                    |

|-------|-----------------------------------------|--------------------|

| Т     |                                         |                    |

| F     | Frequency                               | T Time             |

| Lowe  | ercase letters (pp) and their meanings: |                    |

| рр    |                                         |                    |

| 2     | to                                      | mc MCLR            |

| ck    | CLKOUT                                  | osc oscillator     |

| су    | cycle time                              | os OSC1            |

| drt   | device reset timer                      | t0 T0CKI           |

| io    | I/O port                                | wdt watchdog timer |

| Uppe  | ercase letters and their meanings:      |                    |

| S     |                                         |                    |

| F     | Fall                                    | P Period           |

| н     | High                                    | R Rise             |

| Ι     | Invalid (Hi-impedance)                  | V Valid            |

| L     | Low                                     | Z Hi-impedance     |

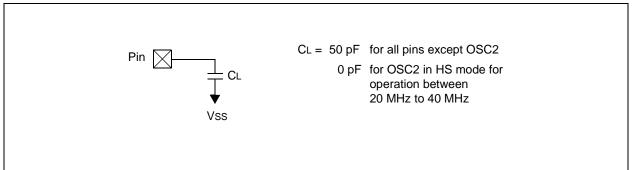

#### FIGURE 19-2: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS -PIC16C54C/C55A/C56A/C57C/C58B-40

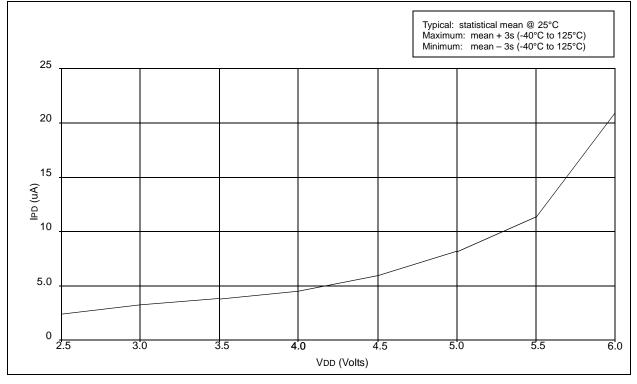

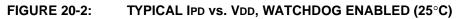

#### 20.0 DEVICE CHARACTERIZATION - PIC16LC54C 40MHz

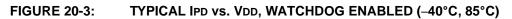

The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

© 1997-2013 Microchip Technology Inc.

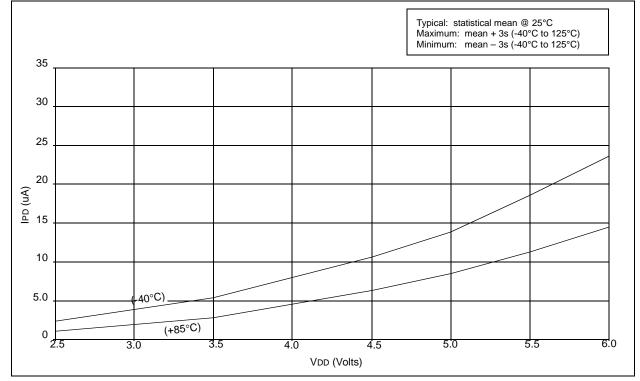

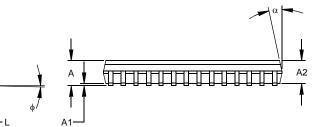

#### 28-Lead Plastic Small Outline (SO) - Wide, 300 mil (SOIC)

For the most current package drawings, please see the Microchip Packaging Specification located Note: at http://www.microchip.com/packaging

|                          | Units     |      | INCHES* |      | MILLIMETERS |       |       |

|--------------------------|-----------|------|---------|------|-------------|-------|-------|

| Dimensi                  | on Limits | MIN  | NOM     | MAX  | MIN         | NOM   | MAX   |

| Number of Pins           | n         |      | 28      |      |             | 28    |       |

| Pitch                    | р         |      | .050    |      |             | 1.27  |       |

| Overall Height           | А         | .093 | .099    | .104 | 2.36        | 2.50  | 2.64  |

| Molded Package Thickness | A2        | .088 | .091    | .094 | 2.24        | 2.31  | 2.39  |

| Standoff §               | A1        | .004 | .008    | .012 | 0.10        | 0.20  | 0.30  |

| Overall Width            | E         | .394 | .407    | .420 | 10.01       | 10.34 | 10.67 |

| Molded Package Width     | E1        | .288 | .295    | .299 | 7.32        | 7.49  | 7.59  |

| Overall Length           | D         | .695 | .704    | .712 | 17.65       | 17.87 | 18.08 |

| Chamfer Distance         | h         | .010 | .020    | .029 | 0.25        | 0.50  | 0.74  |

| Foot Length              | L         | .016 | .033    | .050 | 0.41        | 0.84  | 1.27  |

| Foot Angle Top           | φ         | 0    | 4       | 8    | 0           | 4     | 8     |

| Lead Thickness           | С         | .009 | .011    | .013 | 0.23        | 0.28  | 0.33  |

| Lead Width               | В         | .014 | .017    | .020 | 0.36        | 0.42  | 0.51  |

| Mold Draft Angle Top     | α         | 0    | 12      | 15   | 0           | 12    | 15    |

| Mold Draft Angle Bottom  | β         | 0    | 12      | 15   | 0           | 12    | 15    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-013 Drawing No. C04-052

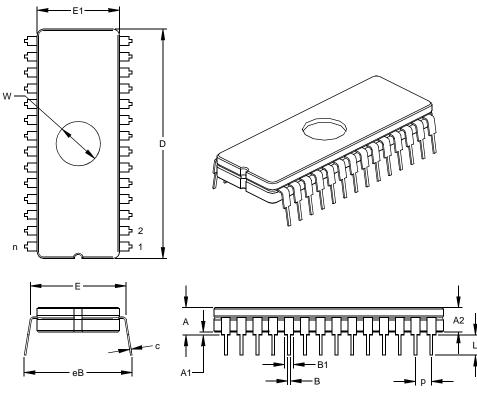

#### 28-Lead Ceramic Dual In-line with Window (JW) - 600 mil (CERDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | INCHES* |       |       | MILLIMETERS |       |       |       |

|----------------------------|---------|-------|-------|-------------|-------|-------|-------|

| Dimensior                  | Limits  | MIN   | NOM   | MAX         | MIN   | NOM   | MAX   |

| Number of Pins             | n       |       | 28    |             |       | 28    |       |

| Pitch                      | р       |       | .100  |             |       | 2.54  |       |

| Top to Seating Plane       | Α       | .195  | .210  | .225        | 4.95  | 5.33  | 5.72  |

| Ceramic Package Height     | A2      | .155  | .160  | .165        | 3.94  | 4.06  | 4.19  |

| Standoff                   | A1      | .015  | .038  | .060        | 0.38  | 0.95  | 1.52  |

| Shoulder to Shoulder Width | Е       | .595  | .600  | .625        | 15.11 | 15.24 | 15.88 |

| Ceramic Pkg. Width         | E1      | .514  | .520  | .526        | 13.06 | 13.21 | 13.36 |

| Overall Length             | D       | 1.430 | 1.460 | 1.490       | 36.32 | 37.08 | 37.85 |

| Tip to Seating Plane       | L       | .125  | .138  | .150        | 3.18  | 3.49  | 3.81  |

| Lead Thickness             | С       | .008  | .010  | .012        | 0.20  | 0.25  | 0.30  |

| Upper Lead Width           | B1      | .050  | .058  | .065        | 1.27  | 1.46  | 1.65  |

| Lower Lead Width           | В       | .016  | .020  | .023        | 0.41  | 0.51  | 0.58  |

| Overall Row Spacing §      | eB      | .610  | .660  | .710        | 15.49 | 16.76 | 18.03 |

| Window Diameter            | W       | .270  | .280  | .290        | 6.86  | 7.11  | 7.37  |

Sontolling Parameter

Significant Characteristic

JEDEC Equivalent: MO-103

Drawing No. C04-013

#### **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.                            | - <u>xx</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Ť                                                                                                                          | <u>/xx</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <u>xxx</u> | Exa                          | nples                                                                                     | S:                                                                                                                                                                                                                                                           |  |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Device                              | Frequency<br>Range/OSC<br>Type           PIC16C54           PIC16C54A           PIC16C54C           PIC16C55A           PIC16C55A           PIC16C55A           PIC16C56A           PIC16C57C           PIC16C57C           PIC16C58B           PIC16C58B                                                                                                                                                                                                                                                                                                                                                        | Temperature<br>Range                                                                                                       | $\begin{array}{c} (2) \\ (1) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\ (2) \\$ | Pattern    | a)<br>b)<br>c)<br>d)<br>Note | PDIP<br>QTP<br>PIC10<br>packa<br>PIC10<br>cial te<br>dard<br>PIC1<br>temp<br>MHz,<br>#123 | <ol> <li>C = normal voltage range<br/>LC = extended</li> </ol>                                                                                                                                                                                               |  |

| Frequency Range/<br>Oscillator Type | <ul> <li>RC Resistor Capacitor</li> <li>LP Low Power Crystal</li> <li>XT Standard Crystal/Resonator</li> <li>High Speed Crystal</li> <li>200 KHz (LP) or 2 MHz (XT and RC)</li> <li>400 KHz (LP) or 4 MHz (XT and RC)</li> <li>10 MHz (HS only)</li> <li>20 20 MHz (HS only)</li> <li>40 MHz (HS only)</li> <li>40 MHz (HS only)</li> <li>b<sup>(4)</sup> No oscillator type for JW packages<sup>(3)</sup></li> <li>*RC/LP/XT/HS are for 16C54/55/56/57 devices only</li> <li>-04/10/20 options are available for all other devices</li> <li>-40 is available for 16C54/C55A/56A/57C/58B devices only</li> </ul> |                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |                              | 3:                                                                                        | T = in tape and reel - SOIC and SSOP<br>packages only<br>JW Devices are UV erasable and can be<br>programmed to any device configura-<br>tion. JW Devices meet the electrical<br>requirements of each oscillator type,<br>including LC devices.<br>b = Blank |  |

| Temperature Range                   | $b^{(4)} = 0^{\circ}C$<br>$I = -40^{\circ}C$<br>$E = -40^{\circ}C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | to +85°C                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |                              |                                                                                           |                                                                                                                                                                                                                                                              |  |

| Package                             | JW = 28-pin<br>DIP <sup>(3)</sup><br>P = 28-pin<br>SO = 300 m<br>SS = 209 m<br>SP = 28-pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Waffle Pack<br>600 mil/18-pin 300<br>600 mil/18-pin 300<br>il SOIC<br>il SSOP<br>300 mil Skinny PE<br>for additional packa | ) mil PDIP<br>DIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |                              |                                                                                           |                                                                                                                                                                                                                                                              |  |

| Pattern                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I code (factory spe<br>lank for OTP and V                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |                              |                                                                                           |                                                                                                                                                                                                                                                              |  |

#### Sales and Support

#### **Data Sheets**

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

1. Your local Microchip sales office

2. The Microchip Worldwide Site (www.microchip.com)