Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

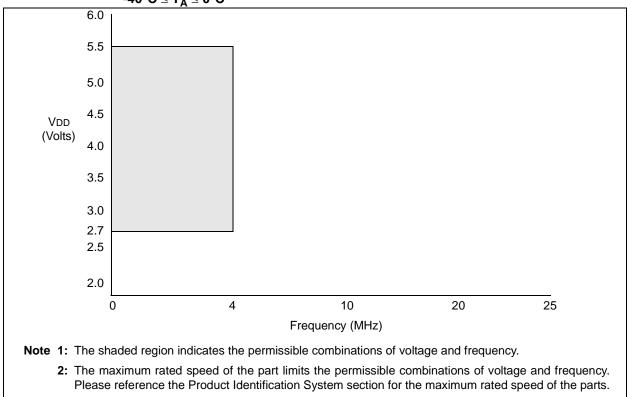

| Speed                      | 4MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | POR, WDT                                                                     |

| Number of I/O              | 12                                                                           |

| Program Memory Size        | 1.5KB (1K x 12)                                                              |

| Program Memory Type        | ОТР                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 25 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            | -                                                                            |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 20-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc56at-04i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16C5X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16C5X uses a Harvard architecture in which program and data are accessed on separate buses. This improves bandwidth over traditional von Neumann architecture where program and data are fetched on the same bus. Separating program and data memory further allows instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 12 bits wide making it possible to have all single word instructions. A 12-bit wide program memory access bus fetches a 12-bit instruction in a single cycle. A twostage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (33) execute in a single cycle except for program branches.

The PIC16C54/CR54 and PIC16C55 address 512 x 12 of program memory, the PIC16C56/CR56 address 1K x 12 of program memory, and the PIC16C57/CR57 and PIC16C58/CR58 address 2K x 12 of program memory. All program memory is internal.

The PIC16C5X can directly or indirectly address its register files and data memory. All special function registers including the program counter are mapped in the data memory. The PIC16C5X has a highly orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16C5X simple yet efficient. In addition, the learning curve is reduced significantly. The PIC16C5X device contains an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8 bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the W (working) register. The other operand is either a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow and digit borrow out bit, respectively, in subtraction. See the SUBWF and ADDWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, with the corresponding device pins described in Table 3-1 (for PIC16C54/56/58) and Table 3-2 (for PIC16C55/57).

| Pin Name    | Pi  | Pin Numb |      | Pin  | Buffer | Description                                                                                                                                                                                                       |

|-------------|-----|----------|------|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name    | DIP | SOIC     | SSOP | Туре | Туре   | Description                                                                                                                                                                                                       |

| RA0         | 6   | 6        | 5    | I/O  | TTL    | Bi-directional I/O port                                                                                                                                                                                           |

| RA1         | 7   | 7        | 6    | I/O  | TTL    |                                                                                                                                                                                                                   |

| RA2         | 8   | 8        | 7    | I/O  | TTL    |                                                                                                                                                                                                                   |

| RA3         | 9   | 9        | 8    | I/O  | TTL    |                                                                                                                                                                                                                   |

| RB0         | 10  | 10       | 9    | I/O  | TTL    | Bi-directional I/O port                                                                                                                                                                                           |

| RB1         | 11  | 11       | 10   | I/O  | TTL    |                                                                                                                                                                                                                   |

| RB2         | 12  | 12       | 11   | I/O  | TTL    |                                                                                                                                                                                                                   |

| RB3         | 13  | 13       | 12   | I/O  | TTL    |                                                                                                                                                                                                                   |

| RB4         | 14  | 14       | 13   | I/O  | TTL    |                                                                                                                                                                                                                   |

| RB5         | 15  | 15       | 15   | I/O  | TTL    |                                                                                                                                                                                                                   |

| RB6         | 16  | 16       | 16   | I/O  | TTL    |                                                                                                                                                                                                                   |

| RB7         | 17  | 17       | 17   | I/O  | TTL    |                                                                                                                                                                                                                   |

| RC0         | 18  | 18       | 18   | I/O  | TTL    | Bi-directional I/O port                                                                                                                                                                                           |

| RC1         | 19  | 19       | 19   | I/O  | TTL    |                                                                                                                                                                                                                   |

| RC2         | 20  | 20       | 20   | I/O  | TTL    |                                                                                                                                                                                                                   |

| RC3         | 21  | 21       | 21   | I/O  | TTL    |                                                                                                                                                                                                                   |

| RC4         | 22  | 22       | 22   | I/O  | TTL    |                                                                                                                                                                                                                   |

| RC5         | 23  | 23       | 23   | I/O  | TTL    |                                                                                                                                                                                                                   |

| RC6         | 24  | 24       | 24   | I/O  | TTL    |                                                                                                                                                                                                                   |

| RC7         | 25  | 25       | 25   | I/O  | TTL    |                                                                                                                                                                                                                   |

| TOCKI       | 1   | 1        | 2    | Ι    | ST     | Clock input to Timer0. Must be tied to Vss or VDD, if not in use, to reduce current consumption.                                                                                                                  |

| MCLR        | 28  | 28       | 28   | I    | ST     | Master clear (RESET) input. This pin is an active low RESET to the device.                                                                                                                                        |

| OSC1/CLKIN  | 27  | 27       | 27   | I    | ST     | Oscillator crystal input/external clock source input.                                                                                                                                                             |

| OSC2/CLKOUT | 26  | 26       | 26   | 0    | _      | Oscillator crystal output. Connects to crystal or resonator<br>in crystal Oscillator mode. In RC mode, OSC2 pin outputs<br>CLKOUT which has 1/4 the frequency of OSC1, and<br>denotes the instruction cycle rate. |

| Vdd         | 2   | 2        | 3,4  | Р    | _      | Positive supply for logic and I/O pins.                                                                                                                                                                           |

| Vss         | 4   | 4        | 1,14 | Р    |        | Ground reference for logic and I/O pins.                                                                                                                                                                          |

| N/C         | 3,5 | 3,5      |      | _    |        | Unused, do not connect.                                                                                                                                                                                           |

#### TABLE 3-2: PINOUT DESCRIPTION - PIC16C55, PIC16C57, PIC16CR57

Legend: I = input, O = output, I/O = input/output, P = power, — = Not Used, TTL = TTL input, ST = Schmitt Trigger input

NOTES:

#### TABLE 5-3: RESET CONDITIONS FOR ALL REGISTERS

| Register                       | Address | Power-On Reset | MCLR or WDT Reset |

|--------------------------------|---------|----------------|-------------------|

| W                              | N/A     | XXXX XXXX      | uuuu uuuu         |

| TRIS                           | N/A     | 1111 1111      | 1111 1111         |

| OPTION                         | N/A     | 11 1111        | 11 1111           |

| INDF                           | 00h     | XXXX XXXX      | uuuu uuuu         |

| TMR0                           | 01h     | XXXX XXXX      | uuuu uuuu         |

| PCL                            | 02h     | 1111 1111      | 1111 1111         |

| STATUS                         | 03h     | 0001 1xxx      | 000q quuu         |

| FSR <sup>(1)</sup>             | 04h     | 1xxx xxxx      | luuu uuuu         |

| PORTA                          | 05h     | xxxx           | uuuu              |

| PORTB                          | 06h     | XXXX XXXX      | uuuu uuuu         |

| PORTC <sup>(2)</sup>           | 07h     | XXXX XXXX      | uuuu uuuu         |

| General Purpose Register Files | 07-7Fh  | XXXX XXXX      | սսսս սսսս         |

Legend: x = unknown u = unchanged - = unimplemented, read as '0'<math>q = see tables in Table 5-1 for possible values.

- Note 1: These values are valid for PIC16C57/CR57/CR58/CR58. For the PIC16C54/CR54/C55/C56/CR56, the value on RESET is 111x xxxx and for MCLR and WDT Reset, the value is 111u uuuu.

- **2:** General purpose register file on PIC16C54/CR54/C56/CR56/C58/CR58.

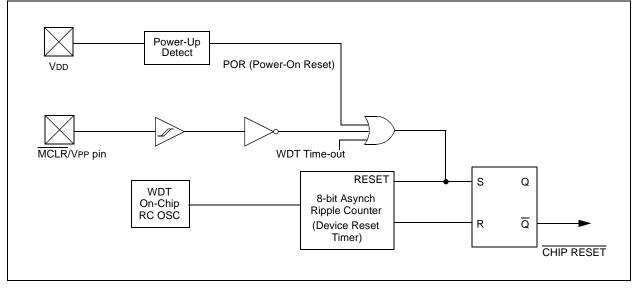

#### FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

NOTES:

| ADDWF                                                       | Add W                                                          | and f                                      |                                                      |                    |

|-------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------|------------------------------------------------------|--------------------|

| Syntax:                                                     | [ label ] A                                                    | DDWF                                       | f,d                                                  |                    |

| Operands:                                                   | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$ |                                            |                                                      |                    |

| Operation:                                                  | (W) + (f)                                                      | $\rightarrow$ (dest)                       |                                                      |                    |

| Status Affected:                                            | C, DC, Z                                                       |                                            |                                                      |                    |

| Encoding:                                                   | 0001                                                           | 11df                                       | ffff                                                 |                    |

| Description:                                                | and regis                                                      | ster 'f'. If 'd<br>in the W<br>sult is sto | of the W r<br>d' is 0 the<br>register. I<br>red back | result<br>f 'd' is |

| Words:                                                      | 1                                                              |                                            |                                                      |                    |

| Cycles:                                                     | 1                                                              |                                            |                                                      |                    |

| Example:                                                    | ADDWF                                                          | TEMP_RE                                    | G, 0                                                 |                    |

| Before Instr<br>W<br>TEMP_I<br>After Instruc<br>W<br>TEMP_F | =<br>REG =<br>ction<br>=                                       | 0x17<br>0xC2<br>0xD9<br>0xC2               |                                                      |                    |

| ANDWF                                                      | AND W with f                                                                                                                                                                            |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                    | [label] ANDWF f,d                                                                                                                                                                       |

| Operands:                                                  | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                                          |

| Operation:                                                 | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                                                      |

| Status Affected:                                           | Z                                                                                                                                                                                       |

| Encoding:                                                  | 0001 01df ffff                                                                                                                                                                          |

| Description:                                               | The contents of the W register are<br>AND'ed with register 'f'. If 'd' is 0<br>the result is stored in the W regis-<br>ter. If 'd' is '1' the result is stored<br>back in register 'f'. |

| Words:                                                     | 1                                                                                                                                                                                       |

| Cycles:                                                    | 1                                                                                                                                                                                       |

| Example:                                                   | ANDWF TEMP_REG, 1                                                                                                                                                                       |

| Before Instru<br>W<br>TEMP_<br>After Instruc<br>W<br>TEMP_ | = 0x17<br>REG = 0xC2<br>tion<br>= 0x17                                                                                                                                                  |

| ANDLW                                                           | AND literal with W                                                                                                           |  |  |  |

|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                                                         | [ <i>label</i> ] ANDLW k                                                                                                     |  |  |  |

| Operands:                                                       | $0 \le k \le 255$                                                                                                            |  |  |  |

| Operation:                                                      | (W).AND. (k) $\rightarrow$ (W)                                                                                               |  |  |  |

| Status Affected:                                                | Z                                                                                                                            |  |  |  |

| Encoding:                                                       | 1110 kkkk kkkk                                                                                                               |  |  |  |

| Description:                                                    | The contents of the W register are<br>AND'ed with the eight-bit literal 'k'.<br>The result is placed in the W regis-<br>ter. |  |  |  |

| Words:                                                          | 1                                                                                                                            |  |  |  |

| Cycles:                                                         | 1                                                                                                                            |  |  |  |

| Example:                                                        | ANDLW H'5F'                                                                                                                  |  |  |  |

| Before Instruction<br>W = 0xA3<br>After Instruction<br>W = 0x03 |                                                                                                                              |  |  |  |

| BCF                                       | Bit Clea                                                           | r f                       |             |  |  |  |

|-------------------------------------------|--------------------------------------------------------------------|---------------------------|-------------|--|--|--|

| Syntax:                                   | [label] BCF f,b                                                    |                           |             |  |  |  |

| Operands:                                 | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$ |                           |             |  |  |  |

| Operation:                                | $0 \rightarrow (f < b$                                             | $0 \rightarrow (f < b >)$ |             |  |  |  |

| Status Affected:                          | None                                                               |                           |             |  |  |  |

| Encoding:                                 | 0100                                                               | bbbf                      | ffff        |  |  |  |

| Description:                              | Bit 'b' in                                                         | register 'f'              | is cleared. |  |  |  |

| Words:                                    | 1                                                                  |                           |             |  |  |  |

| Cycles:                                   | 1                                                                  |                           |             |  |  |  |

| Example:                                  | BCF                                                                | FLAG_RE                   | IG, 7       |  |  |  |

| Before Instru<br>FLAG_F<br>After Instruct | REG =                                                              | 0xC7                      |             |  |  |  |

| FLAG_F                                    | REG =                                                              | 0x47                      |             |  |  |  |

| RLF                                          | Rotate Left f through Carry                                                                                                                                                                                                   |  |  |  |  |  |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                                      | [ <i>label</i> ] RLF f,d                                                                                                                                                                                                      |  |  |  |  |  |

| Operands:                                    | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                                    |  |  |  |  |  |

| Operation:                                   | See description below                                                                                                                                                                                                         |  |  |  |  |  |

| Status Affected:                             | С                                                                                                                                                                                                                             |  |  |  |  |  |

| Encoding:                                    | 0011 01df ffff                                                                                                                                                                                                                |  |  |  |  |  |

| Description:                                 | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry Flag (STATUS<0>). If 'd'<br>is 0 the result is placed in the W<br>register. If 'd' is 1 the result is<br>stored back in<br>register 'f'. |  |  |  |  |  |

| Words:                                       | 1                                                                                                                                                                                                                             |  |  |  |  |  |

| Cycles:                                      | 1                                                                                                                                                                                                                             |  |  |  |  |  |

| Example:                                     | RLF REG1,0                                                                                                                                                                                                                    |  |  |  |  |  |

| Before Instru<br>REG1<br>C<br>After Instruct | = 1110 0110<br>= 0<br>tion                                                                                                                                                                                                    |  |  |  |  |  |

| REG1<br>W<br>C                               | = 1110 0110<br>= 1100 1100<br>= 1                                                                                                                                                                                             |  |  |  |  |  |

| RRF                                          | Rotate Right f through Carry                                                                                                                                                                                                   |  |  |  |  |  |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                                      | [ <i>label</i> ] RRF f,d                                                                                                                                                                                                       |  |  |  |  |  |

| Operands:                                    | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                                                                                 |  |  |  |  |  |

| Operation:                                   | See description below                                                                                                                                                                                                          |  |  |  |  |  |

| Status Affected:                             | С                                                                                                                                                                                                                              |  |  |  |  |  |

| Encoding:                                    | 0011 00df ffff                                                                                                                                                                                                                 |  |  |  |  |  |

| Description:                                 | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag (STATUS<0>). If 'd'<br>is 0 the result is placed in the W<br>register. If 'd' is 1 the result is<br>placed back in<br>register 'f'. |  |  |  |  |  |

| Words:                                       | 1                                                                                                                                                                                                                              |  |  |  |  |  |

| Cycles:                                      | 1                                                                                                                                                                                                                              |  |  |  |  |  |

| Example:                                     | RRF REG1,0                                                                                                                                                                                                                     |  |  |  |  |  |

| Before Instru<br>REG1<br>C<br>After Instruct | $= 1110 0110 \\ = 0$                                                                                                                                                                                                           |  |  |  |  |  |

| REG1<br>W<br>C                               | = 1110 0110<br>= 0111 0011<br>= 0                                                                                                                                                                                              |  |  |  |  |  |

| SLEEP            | Enter SLEEP Mode                                                                                                                                                                                                                                   |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SLEEP                                                                                                                                                                                                                             |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                                               |  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT; \\ 0 \rightarrow WDT \text{ prescaler; if assigned} \\ 1 \rightarrow \overline{TO}; \\ 0 \rightarrow \overline{PD} \end{array}$                                                                             |  |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                                                                                                             |  |  |  |  |

| Encoding:        | 0000 0000 0011                                                                                                                                                                                                                                     |  |  |  |  |

| Description:     | Time-out status bit (TO) is set. The<br>power-down status bit (PD) is<br>cleared. The WDT and its pres-<br>caler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped.<br>See section on SLEEP for more<br>details. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                  |  |  |  |  |

| Example:         | SLEEP                                                                                                                                                                                                                                              |  |  |  |  |

| XORLW                                                           | Exclusive OR literal with W   |            |                                           |           |  |

|-----------------------------------------------------------------|-------------------------------|------------|-------------------------------------------|-----------|--|

| Syntax:                                                         | [label]                       | XORLW      | k                                         |           |  |

| Operands:                                                       | $0 \le k \le 255$             |            |                                           |           |  |

| Operation:                                                      | (W) .XOR. $k \rightarrow (W)$ |            |                                           |           |  |

| Status Affected:                                                | Z                             |            |                                           |           |  |

| Encoding:                                                       | 1111                          | kkkk       | kkkk                                      |           |  |

| Description:                                                    | XOR'ed                        | with the e | e W regis<br>eight bit lit<br>ed in the V | eral 'k'. |  |

| Words:                                                          | 1                             |            |                                           |           |  |

| Cycles:                                                         | 1                             |            |                                           |           |  |

| Example:                                                        | XORLW                         | 0xAF       |                                           |           |  |

| Before Instruction<br>W = 0xB5<br>After Instruction<br>W = 0x1A |                               |            |                                           |           |  |

| Exclusive OR W with f                                                                                                                                        | Exclusive OR W with f               |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--|--|--|--|

| [ label ] XORWF f,d                                                                                                                                          | -                                   |  |  |  |  |

| $\begin{array}{l} 0 \leq f \leq 31 \\ d  \in  [0,1] \end{array}$                                                                                             |                                     |  |  |  |  |

| (W) .XOR. (f) $\rightarrow$ (dest)                                                                                                                           |                                     |  |  |  |  |

| ted: Z                                                                                                                                                       |                                     |  |  |  |  |

| 0001 10df ffff                                                                                                                                               |                                     |  |  |  |  |

| W register with register 'f'. If 'd' is 0<br>the result is stored in the W regis-<br>ter. If 'd' is 1 the result is stored<br>back in register 'f'.          |                                     |  |  |  |  |

| 1                                                                                                                                                            |                                     |  |  |  |  |

| 1                                                                                                                                                            |                                     |  |  |  |  |

| XORWF REG,1                                                                                                                                                  |                                     |  |  |  |  |

| Instruction<br>G = 0xAF<br>= 0xB5<br>struction<br>G = 0x1A<br>= 0xB5                                                                                         |                                     |  |  |  |  |

| the result is stored in t<br>ter. If 'd' is 1 the result<br>back in register 'f'.<br>1<br>1<br>XORWF REG, 1<br>nstruction<br>G = 0xAF<br>= 0xB5<br>struction | er 'f'. If 'd' is 0<br>the W regis- |  |  |  |  |

### 11.13 PICDEM 3 Low Cost PIC16CXXX Demonstration Board

The PICDEM 3 demonstration board is a simple demonstration board that supports the PIC16C923 and PIC16C924 in the PLCC package. It will also support future 44-pin PLCC microcontrollers with an LCD Module. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 3 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer with an adapter socket, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 3 demonstration board to test firmware. A prototype area has been provided to the user for adding hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a thermistor and separate headers for connection to an external LCD module and a keypad. Also provided on the PICDEM 3 demonstration board is a LCD panel, with 4 commons and 12 segments, that is capable of displaying time, temperature and day of the week. The PICDEM 3 demonstration board provides an additional RS-232 interface and Windows software for showing the demultiplexed LCD signals on a PC. A simple serial interface allows the user to construct a hardware demultiplexer for the LCD signals.

#### 11.14 PICDEM 17 Demonstration Board

The PICDEM 17 demonstration board is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756A, PIC17C762 and PIC17C766. All necessary hardware is included to run basic demo programs, which are supplied on a 3.5-inch disk. A programmed sample is included and the user may erase it and program it with the other sample programs using the PRO MATE II device programmer, or the PICSTART Plus development programmer, and easily debug and test the sample code. In addition, the PICDEM 17 demonstration board supports downloading of programs to and executing out of external FLASH memory on board. The PICDEM 17 demonstration board is also usable with the MPLAB ICE in-circuit emulator, or the PICMASTER emulator and all of the sample programs can be run and modified using either emulator. Additionally, a generous prototype area is available for user hardware.

#### 11.15 KEELOQ Evaluation and Programming Tools

KEELOQ evaluation and programming tools support Microchip's HCS Secure Data Products. The HCS evaluation kit includes a LCD display to show changing codes, a decoder to decode transmissions and a programming interface to program test transmitters.

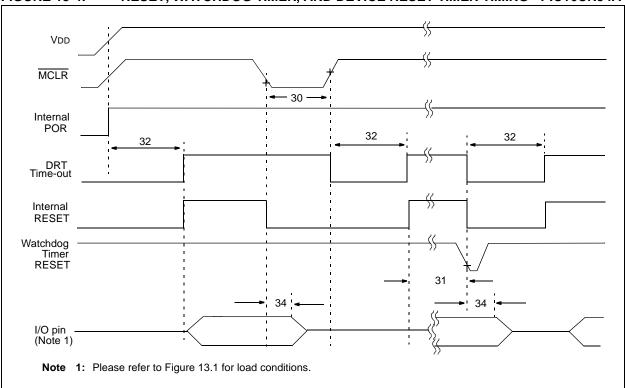

#### FIGURE 13-4: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING - PIC16CR54A

#### TABLE 13-3: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER - PIC16CR54A

| AC Chara     | cteristics | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^\circ C \leq TA \leq +70^\circ C \mbox{ for commercial} \\ -40^\circ C \leq TA \leq +85^\circ C \mbox{ for industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for extended} \end{array}$ |      |      |      |       |                   |  |  |

|--------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|-------------------|--|--|

| Param<br>No. | Symbol     | Characteristic                                                                                                                                                                                                                                                                                                             | Min  | Тур† | Max  | Units | Conditions        |  |  |

| 30           | TmcL       | MCLR Pulse Width (low)                                                                                                                                                                                                                                                                                                     | 1.0* |      |      | μS    | VDD = 5.0V        |  |  |

| 31           | Twdt       | Watchdog Timer Time-out Period<br>(No Prescaler)                                                                                                                                                                                                                                                                           | 7.0* | 18*  | 40*  | ms    | VDD = 5.0V (Comm) |  |  |

| 32           | Tdrt       | Device Reset Timer Period                                                                                                                                                                                                                                                                                                  | 7.0* | 18*  | 30*  | ms    | VDD = 5.0V (Comm) |  |  |

| 34           | Tioz       | I/O Hi-impedance from MCLR Low                                                                                                                                                                                                                                                                                             | _    | _    | 1.0* | μS    |                   |  |  |

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# 15.5 Timing Parameter Symbology and Load Conditions

The timing parameter symbols have been created with one of the following formats:

1. TppS2ppS

| oS                                    |                                                                                                                                                                                    |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                       |                                                                                                                                                                                    |

|                                       |                                                                                                                                                                                    |

| Frequency                             | T Time                                                                                                                                                                             |

| case letters (pp) and their meanings: |                                                                                                                                                                                    |

|                                       |                                                                                                                                                                                    |

| to                                    | mc MCLR                                                                                                                                                                            |

| CLKOUT                                | osc oscillator                                                                                                                                                                     |

| cycle time                            | os OSC1                                                                                                                                                                            |

| device reset timer                    | t0 T0CKI                                                                                                                                                                           |

| I/O port                              | wdt watchdog timer                                                                                                                                                                 |

| case letters and their meanings:      |                                                                                                                                                                                    |

|                                       |                                                                                                                                                                                    |

| Fall                                  | P Period                                                                                                                                                                           |

| High                                  | R Rise                                                                                                                                                                             |

| Invalid (Hi-impedance)                | V Valid                                                                                                                                                                            |

| Low                                   | Z Hi-impedance                                                                                                                                                                     |

|                                       | case letters (pp) and their meanings:<br>o<br>CLKOUT<br>cycle time<br>device reset timer<br>I/O port<br>case letters and their meanings:<br>Fall<br>High<br>Invalid (Hi-impedance) |

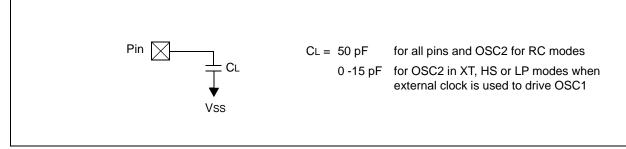

### FIGURE 15-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS - PIC16C54A

## **15.6** Timing Diagrams and Specifications

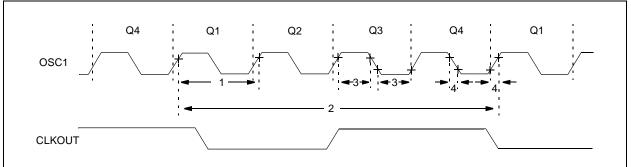

#### FIGURE 15-2: EXTERNAL CLOCK TIMING - PIC16C54A

| TABLE 15-1: EXTERNAL CLOCK TIMING REQUIREMENTS - PIC16C54A |

|------------------------------------------------------------|

|------------------------------------------------------------|

| AC Chara     | cteristics | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |            |   |     |     |                          |  |  |

|--------------|------------|------------------------------------------------------|------------|---|-----|-----|--------------------------|--|--|

| Param<br>No. | Symbol     | Characteristic                                       | Conditions |   |     |     |                          |  |  |

|              | Fosc       | External CLKIN Fre-                                  | DC         | _ | 4.0 | MHz | XT OSC mode              |  |  |

|              |            | quency <sup>(1)</sup>                                | DC         | — | 2.0 | MHz | XT osc mode (PIC16LV54A) |  |  |

|              |            |                                                      | DC         | — | 4.0 | MHz | HS osc mode (04)         |  |  |

|              |            |                                                      | DC         | — | 10  | MHz | HS osc mode (10)         |  |  |

|              |            |                                                      | DC         | — | 20  | MHz | HS osc mode (20)         |  |  |

|              |            |                                                      | DC         | — | 200 | kHz | LP OSC mode              |  |  |

|              |            | Oscillator Frequency <sup>(1)</sup>                  | DC         |   | 4.0 | MHz | RC osc mode              |  |  |

|              |            |                                                      | DC         | — | 2.0 | MHz | RC osc mode (PIC16LV54A) |  |  |

|              |            |                                                      | 0.1        | — | 4.0 | MHz | XT OSC mode              |  |  |

|              |            |                                                      | 0.1        | — | 2.0 | MHz | XT osc mode (PIC16LV54A) |  |  |

|              |            |                                                      | 4.0        | — | 4.0 | MHz | HS osc mode (04)         |  |  |

|              |            |                                                      | 4.0        | — | 10  | MHz | HS osc mode (10)         |  |  |

|              |            |                                                      | 4.0        | — | 20  | MHz | HS osc mode (20)         |  |  |

|              |            |                                                      | 5.0        | — | 200 | kHz | LP osc mode              |  |  |

\* These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- Note 1: All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

- Instruction cycle period (TcY) equals four times the input oscillator time base period.

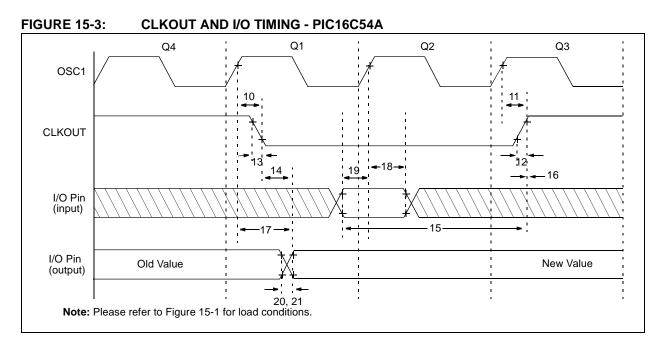

#### TABLE 15-2: CLKOUT AND I/O TIMING REQUIREMENTS - PIC16C54A

| AC Chara     | octeristics | $\begin{array}{llllllllllllllllllllllllllllllllllll$                  | $\begin{array}{l} \mbox{mdard Operating Conditions (unless otherwise specified)} \\ \mbox{erating Temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \ \ \mbox{for commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \ \ \mbox{for industrial} \\ -20^{\circ}C \leq TA \leq +85^{\circ}C \ \ \mbox{for industrial} - PIC16LV54A-02I \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \ \ \mbox{for extended} \end{array}$ |      |      |       |  |  |

|--------------|-------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|--|--|

| Param<br>No. | Symbol      | Characteristic                                                        | Min                                                                                                                                                                                                                                                                                                                                                                                                                      | Тур† | Мах  | Units |  |  |

| 10           | TosH2ckL    | OSC1↑ to CLKOUT↓ <sup>(1)</sup>                                       | —                                                                                                                                                                                                                                                                                                                                                                                                                        | 15   | 30** | ns    |  |  |

| 11           | TosH2ckH    | OSC1↑ to CLKOUT↑ <sup>(1)</sup>                                       | —                                                                                                                                                                                                                                                                                                                                                                                                                        | 15   | 30** | ns    |  |  |

| 12           | TckR        | CLKOUT rise time <sup>(1)</sup>                                       | —                                                                                                                                                                                                                                                                                                                                                                                                                        | 5.0  | 15** | ns    |  |  |

| 13           | TckF        | CLKOUT fall time <sup>(1)</sup>                                       | —                                                                                                                                                                                                                                                                                                                                                                                                                        | 5.0  | 15** | ns    |  |  |

| 14           | TckL2ioV    | CLKOUT↓ to Port out valid <sup>(1)</sup>                              | —                                                                                                                                                                                                                                                                                                                                                                                                                        | —    | 40** | ns    |  |  |

| 15           | TioV2ckH    | Port in valid before CLKOUT <sup>(1)</sup>                            | 0.25 TCY+30*                                                                                                                                                                                                                                                                                                                                                                                                             | —    | —    | ns    |  |  |

| 16           | TckH2iol    | Port in hold after CLKOUT <sup>(1)</sup>                              | 0*                                                                                                                                                                                                                                                                                                                                                                                                                       | —    | —    | ns    |  |  |

| 17           | TosH2ioV    | OSC1↑ (Q1 cycle) to Port out valid <sup>(2)</sup>                     | —                                                                                                                                                                                                                                                                                                                                                                                                                        | —    | 100* | ns    |  |  |

| 18           | TosH2iol    | OSC1 <sup>↑</sup> (Q2 cycle) to Port input invalid (I/O in hold time) | TBD                                                                                                                                                                                                                                                                                                                                                                                                                      | —    | —    | ns    |  |  |

| 19           | TioV2osH    | Port input valid to OSC1↑<br>(I/O in setup time)                      | TBD                                                                                                                                                                                                                                                                                                                                                                                                                      | —    | —    | ns    |  |  |

| 20           | TioR        | Port output rise time <sup>(2)</sup>                                  | —                                                                                                                                                                                                                                                                                                                                                                                                                        | 10   | 25** | ns    |  |  |

| 21           | TioF        | Port output fall time <sup>(2)</sup>                                  | —                                                                                                                                                                                                                                                                                                                                                                                                                        | 10   | 25** | ns    |  |  |

\* These parameters are characterized but not tested.

\*\* These parameters are design targets and are not tested. No characterization data available at this time.

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

**Note 1:** Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

2: Please refer to Figure 15-1 for load conditions.

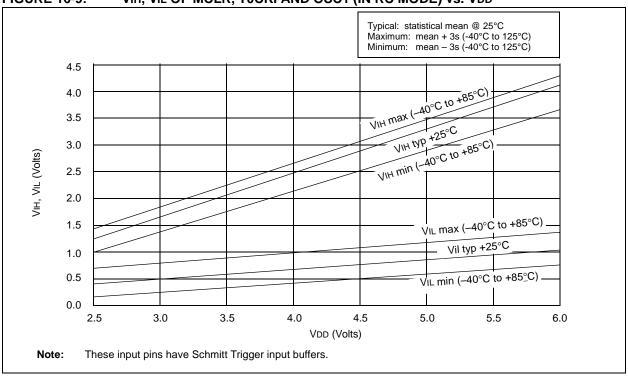

FIGURE 16-9: VIH, VIL OF MCLR, TOCKI AND OSC1 (IN RC MODE) vs. VDD

#### TABLE 18-2:INPUT CAPACITANCE

| Pin         | Typical Capacitance (pF) |          |  |  |  |

|-------------|--------------------------|----------|--|--|--|

| Pin         | 18L PDIP                 | 18L SOIC |  |  |  |

| RA port     | 5.0                      | 4.3      |  |  |  |

| RB port     | 5.0                      | 4.3      |  |  |  |

| MCLR        | 17.0                     | 17.0     |  |  |  |

| OSC1        | 4.0                      | 3.5      |  |  |  |

| OSC2/CLKOUT | 4.3                      | 3.5      |  |  |  |

| тоскі       | 3.2                      | 2.8      |  |  |  |

All capacitance values are typical at  $25^{\circ}$ C. A part-to-part variation of ±25% (three standard deviations) should be taken into account.

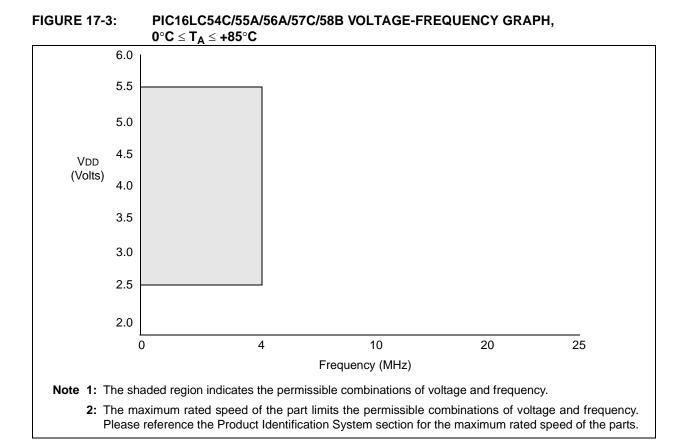

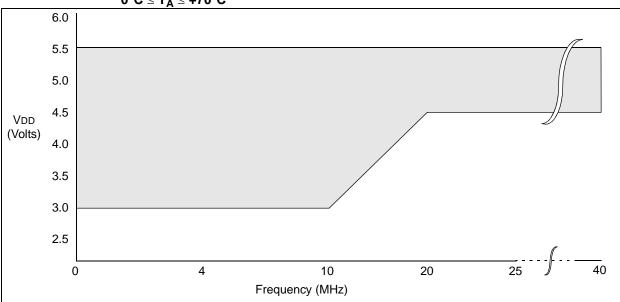

FIGURE 19-1: PIC16C54C/C55A/C56A/C57C/C58B-40 VOLTAGE-FREQUENCY GRAPH,  $0^{\circ}C \le T_A \le +70^{\circ}C$

- **2:** The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

- **3:** Operation between 20 to 40 MHz requires the following:

- VDD between 4.5V. and 5.5V

- OSC1 externally driven

- OSC2 not connected

- HS mode

- Commercial temperatures

Devices qualified for 40 MHz operation have -40 designation (ex: PIC16C54C-40/P).

4: For operation between DC and 20 MHz, see Section 17.1.

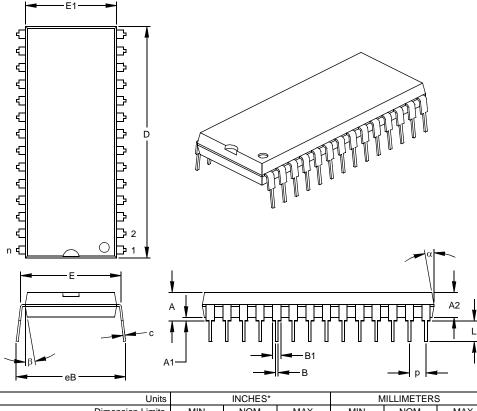

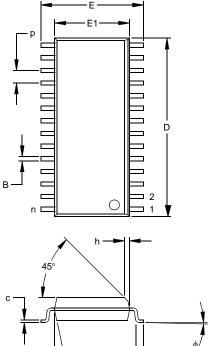

## 28-Lead Plastic Dual In-line (P) - 600 mil (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            |              | INCHES* |       | MILLIMETERS |       |       |       |

|----------------------------|--------------|---------|-------|-------------|-------|-------|-------|

| Dimer                      | ision Limits | MIN     | NOM   | MAX         | MIN   | NOM   | MAX   |

| Number of Pins             | n            |         | 28    |             |       | 28    |       |

| Pitch                      | р            |         | .100  |             |       | 2.54  |       |

| Top to Seating Plane       | А            | .160    | .175  | .190        | 4.06  | 4.45  | 4.83  |

| Molded Package Thickness   | A2           | .140    | .150  | .160        | 3.56  | 3.81  | 4.06  |

| Base to Seating Plane      | A1           | .015    |       |             | 0.38  |       |       |

| Shoulder to Shoulder Width | E            | .595    | .600  | .625        | 15.11 | 15.24 | 15.88 |

| Molded Package Width       | E1           | .505    | .545  | .560        | 12.83 | 13.84 | 14.22 |

| Overall Length             | D            | 1.395   | 1.430 | 1.465       | 35.43 | 36.32 | 37.21 |

| Tip to Seating Plane       | L            | .120    | .130  | .135        | 3.05  | 3.30  | 3.43  |

| Lead Thickness             | С            | .008    | .012  | .015        | 0.20  | 0.29  | 0.38  |

| Upper Lead Width           | B1           | .030    | .050  | .070        | 0.76  | 1.27  | 1.78  |

| Lower Lead Width           | В            | .014    | .018  | .022        | 0.36  | 0.46  | 0.56  |

| Overall Row Spacing        | § eB         | .620    | .650  | .680        | 15.75 | 16.51 | 17.27 |

| Mold Draft Angle Top       | α            | 5       | 10    | 15          | 5     | 10    | 15    |

| Mold Draft Angle Bottom    | β            | 5       | 10    | 15          | 5     | 10    | 15    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

JEDEC Equivalent: MO-011 Drawing No. C04-079

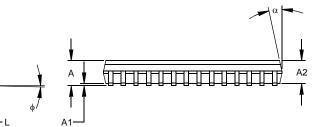

#### 28-Lead Plastic Small Outline (SO) - Wide, 300 mil (SOIC)

For the most current package drawings, please see the Microchip Packaging Specification located Note: at http://www.microchip.com/packaging

|                          | Units |      |      |      | MILLIMETERS |       |       |

|--------------------------|-------|------|------|------|-------------|-------|-------|

| Dimensi                  | MIN   | NOM  | MAX  | MIN  | NOM         | MAX   |       |

| Number of Pins           | n     |      | 28   |      |             | 28    |       |

| Pitch                    | р     |      | .050 |      |             | 1.27  |       |

| Overall Height           | А     | .093 | .099 | .104 | 2.36        | 2.50  | 2.64  |

| Molded Package Thickness | A2    | .088 | .091 | .094 | 2.24        | 2.31  | 2.39  |

| Standoff §               | A1    | .004 | .008 | .012 | 0.10        | 0.20  | 0.30  |

| Overall Width            | E     | .394 | .407 | .420 | 10.01       | 10.34 | 10.67 |

| Molded Package Width     | E1    | .288 | .295 | .299 | 7.32        | 7.49  | 7.59  |

| Overall Length           | D     | .695 | .704 | .712 | 17.65       | 17.87 | 18.08 |

| Chamfer Distance         | h     | .010 | .020 | .029 | 0.25        | 0.50  | 0.74  |

| Foot Length              | L     | .016 | .033 | .050 | 0.41        | 0.84  | 1.27  |

| Foot Angle Top           | φ     | 0    | 4    | 8    | 0           | 4     | 8     |

| Lead Thickness           | С     | .009 | .011 | .013 | 0.23        | 0.28  | 0.33  |

| Lead Width               | В     | .014 | .017 | .020 | 0.36        | 0.42  | 0.51  |

| Mold Draft Angle Top     | α     | 0    | 12   | 15   | 0           | 12    | 15    |

| Mold Draft Angle Bottom  | β     | 0    | 12   | 15   | 0           | 12    | 15    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-013 Drawing No. C04-052

#### Μ

| MCLR Reset                                             |    |

|--------------------------------------------------------|----|

| Register values on2                                    | 20 |

| Memory Map                                             |    |

| PIC16C54/CR54/C55                                      | 25 |

| PIC16C56/CR56                                          | 25 |

| PIC16C57/CR57/C58/CR582                                | 25 |

| Memory Organization                                    |    |

| MOVF                                                   | 56 |

| MOVLW                                                  | 56 |

| MOVWF                                                  | 57 |

| MPLAB C17 and MPLAB C18 C Compilers                    | 31 |

| MPLAB ICD In-Circuit Debugger                          | 33 |

| MPLAB ICE High Performance Universal In-Circuit Emulat | or |

| with MPLAB IDE                                         | 32 |

| MPLAB Integrated Development Environment Software      | 31 |

| MPLINK Object Linker/MPLIB Object Librarian            | 32 |

# Ν

| NOP |

|-----|

|-----|

#### 0

| One-Time-Programmable (OTP) Devices | 7 |

|-------------------------------------|---|

| -                                   |   |

| OPTION                              | - |

| OPTION Register                     |   |

| Value on reset                      |   |

| Oscillator Configurations           |   |

| Oscillator Types                    |   |

| HS                                  |   |

| LP                                  |   |

| RC                                  |   |

| XT                                  |   |

|                                     |   |

## Ρ

| PA0 bit                                            | .29  |

|----------------------------------------------------|------|

| PA1 bit                                            | .29  |

| Paging                                             | . 31 |

| PC                                                 | . 31 |

| Value on reset                                     | .20  |

| PD bit                                             | , 29 |

| Peripheral Features                                | 1    |

| PICDEM 1 Low Cost PIC MCU Demonstration Board      | .63  |

| PICDEM 17 Demonstration Board                      | . 64 |

| PICDEM 2 Low Cost PIC16CXX Demonstration Board     | .63  |

| PICDEM 3 Low Cost PIC16CXXX Demonstration Board    | .64  |

| PICSTART Plus Entry Level Development Programmer   | .63  |

| Pin Configurations                                 |      |

| Pinout Description - PIC16C54, PIC16CR54, PIC16C   | 56,  |

| PIC16CR56, PIC16C58, PIC16CR58                     | .11  |

| Pinout Description - PIC16C55, PIC16C57, PIC16CR57 | . 12 |

| PORTA                                              | . 35 |

| Value on reset                                     | . 20 |

| PORTB                                              | . 35 |

| Value on reset                                     | . 20 |

| PORTC                                              | . 35 |

| Value on reset                                     | . 20 |

| Power-Down Mode                                    | . 47 |

| Power-On Reset (POR)                               | .21  |

| Register values on                                 | . 20 |

| Prescaler                                          |      |

| PRO MATE II Universal Device Programmer            |      |

| Program Counter                                    |      |

| Program Memory Organization                        |      |

| Program Verification/Code Protection               | . 47 |

# Q

| Q cycles                                  |

|-------------------------------------------|

| Quick-Turnaround-Production (QTP) Devices |

| R                                         |

| RC Oscillator                             |

| Read Only Memory (ROM) Devices7           |

| Read-Modify-Write                         |

| Register File Map                         |

| PIC16C54, PIC16CR54, PIC16C55, PIC16C56,  |

| PIC16CR56                                 |

| PIC16C57/CR57                             |

| PIC16C58/CR5827                           |

| Registers                                 |

| Special Function                          |

| Value on reset 20                         |

| Reset 19                                  |

| Reset on Brown-Out 23                     |

| RETLW 57                                  |

| RLF                                       |

| RRF                                       |

### S

| Serialized Quick-Turnaround-Production (SQTP) D<br>SLEEP |       |

|----------------------------------------------------------|-------|

|                                                          | , ,   |

| Software Simulator (MPLAB SIM)                           | 62    |

| Special Features of the CPU                              | 43    |

| Special Function Registers                               |       |

| Stack                                                    | 32    |

| STATUS Register                                          | 9, 29 |

| Value on reset                                           | 20    |

| SUBWF                                                    | 59    |

| SWAPF                                                    | 59    |

|                                                          |       |

# Т