#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 20                                                                         |

| Program Memory Size        | 3KB (2K x 12)                                                              |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 72 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                                   |

| Supplier Device Package    | 28-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc57c-04i-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

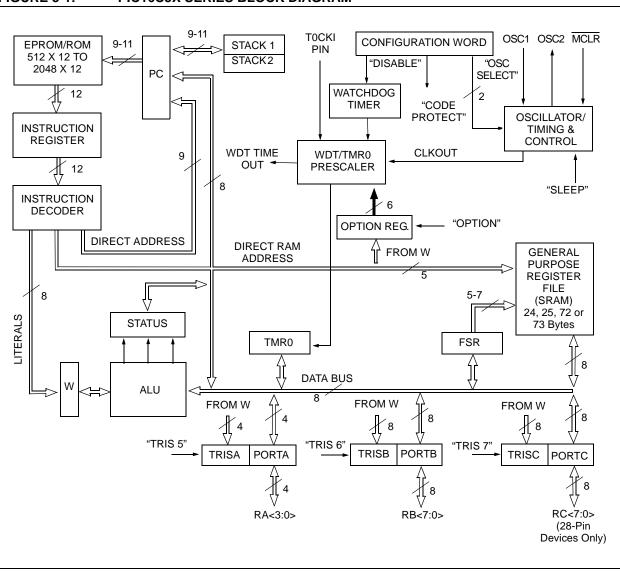

#### FIGURE 3-1: PIC16C5X SERIES BLOCK DIAGRAM

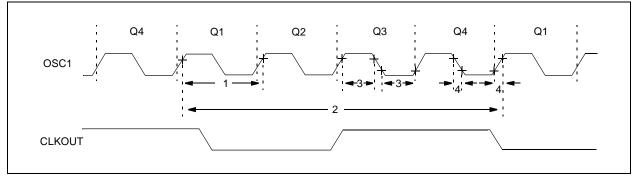

#### 3.1 **Clocking Scheme/Instruction** Cycle

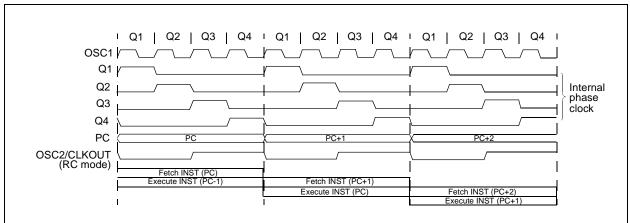

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the program counter is incremented every Q1 and the instruction is fetched from program memory and latched into the instruction register in Q4. It is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 3-2 and Example 3-1.

#### 3.2 Instruction Flow/Pipelining

An Instruction Cycle consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-2: **CLOCK/INSTRUCTION CYCLE**

#### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

is "flushed" from the pipeline, while the new instruction is being fetched and then executed.

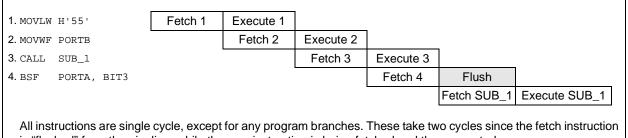

#### 4.4 RC Oscillator

For timing insensitive applications, the RC device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used.

Figure 4-5 shows how the R/C combination is connected to the PIC16C5X. For REXT values below 2.2 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high REXT values (e.g., 1 M $\Omega$ ) the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend keeping REXT between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (CEXT = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

The Electrical Specifications sections show RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

Also, see the Electrical Specifications sections for variation of oscillator frequency due to VDD for given REXT/ CEXT values as well as frequency variation due to operating temperature for given R, C, and VDD values.

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin, and can be used for test purposes or to synchronize other logic.

**Note:** If you change from this device to another device, please verify oscillator characteristics in your application.

#### TABLE 5-3: RESET CONDITIONS FOR ALL REGISTERS

| Register                       | Address | Power-On Reset | MCLR or WDT Reset |

|--------------------------------|---------|----------------|-------------------|

| W                              | N/A     | XXXX XXXX      | uuuu uuuu         |

| TRIS                           | N/A     | 1111 1111      | 1111 1111         |

| OPTION                         | N/A     | 11 1111        | 11 1111           |

| INDF                           | 00h     | XXXX XXXX      | uuuu uuuu         |

| TMR0                           | 01h     | XXXX XXXX      | uuuu uuuu         |

| PCL                            | 02h     | 1111 1111      | 1111 1111         |

| STATUS                         | 03h     | 0001 1xxx      | 000q quuu         |

| FSR <sup>(1)</sup>             | 04h     | 1xxx xxxx      | luuu uuuu         |

| PORTA                          | 05h     | xxxx           | uuuu              |

| PORTB                          | 06h     | XXXX XXXX      | uuuu uuuu         |

| PORTC <sup>(2)</sup>           | 07h     | XXXX XXXX      | uuuu uuuu         |

| General Purpose Register Files | 07-7Fh  | XXXX XXXX      | սսսս սսսս         |

Legend: x = unknown u = unchanged - = unimplemented, read as '0'<math>q = see tables in Table 5-1 for possible values.

- Note 1: These values are valid for PIC16C57/CR57/CR58/CR58. For the PIC16C54/CR54/C55/C56/CR56, the value on RESET is 111x xxxx and for MCLR and WDT Reset, the value is 111u uuuu.

- **2:** General purpose register file on PIC16C54/CR54/C56/CR56/C58/CR58.

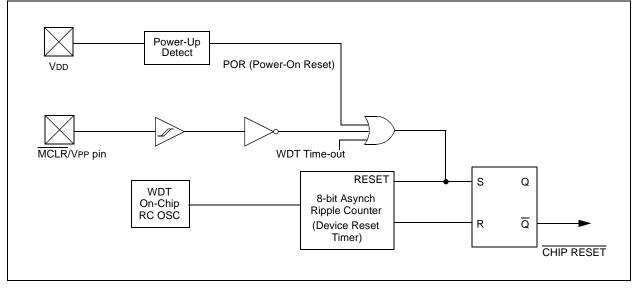

#### FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

#### 6.0 MEMORY ORGANIZATION

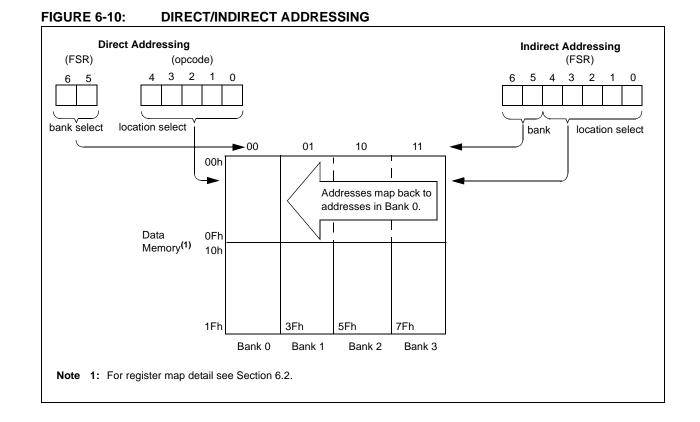

PIC16C5X memory is organized into program memory and data memory. For devices with more than 512 bytes of program memory, a paging scheme is used. Program memory pages are accessed using one or two STATUS Register bits. For devices with a data memory register file of more than 32 registers, a banking scheme is used. Data memory banks are accessed using the File Selection Register (FSR).

#### 6.1 Program Memory Organization

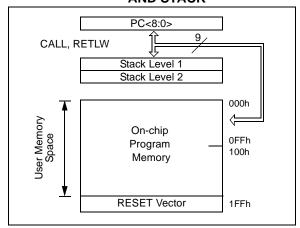

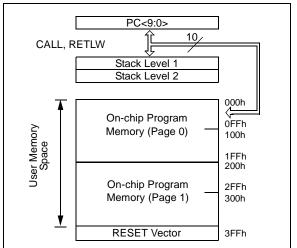

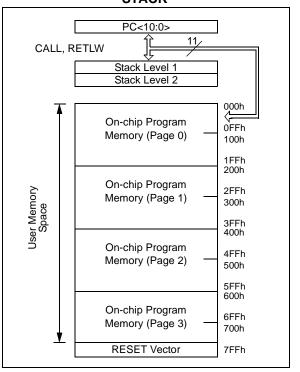

The PIC16C54, PIC16CR54 and PIC16C55 have a 9bit Program Counter (PC) capable of addressing a 512 x 12 program memory space (Figure 6-1). The PIC16C56 and PIC16CR56 have a 10-bit Program Counter (PC) capable of addressing a 1K x 12 program memory space (Figure 6-2). The PIC16CR57, PIC16C58 and PIC16CR58 have an 11-bit Program Counter capable of addressing a 2K x 12 program memory space (Figure 6-3). Accessing a location above the physically implemented address will cause a wraparound.

A NOP at the RESET vector location will cause a restart at location 000h. The RESET vector for the PIC16C54, PIC16CR54 and PIC16C55 is at 1FFh. The RESET vector for the PIC16C56 and PIC16CR56 is at 3FFh. The RESET vector for the PIC16C57, PIC16CR57, PIC16C58, and PIC16CR58 is at 7FFh. See Section 6.5 for additional information using CALL and GOTO instructions.

#### FIGURE 6-1: PIC16C54/CR54/C55 PROGRAM MEMORY MAP AND STACK

#### FIGURE 6-2:

#### PIC16C56/CR56 PROGRAM MEMORY MAP AND STACK

FIGURE 6-3:

PIC16C57/CR57/C58/ CR58 PROGRAM MEMORY MAP AND STACK

# 6.7 Indirect Data Addressing; INDF and FSR Registers

The INDF Register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR Register (FSR is a *pointer*). This is indirect addressing.

#### EXAMPLE 6-1: INDIRECT ADDRESSING

- Register file 08 contains the value 10h

- Register file 09 contains the value 0Ah

- · Load the value 08 into the FSR Register

- A read of the INDF Register will return the value of 10h

- Increment the value of the FSR Register by one (FSR = 09h)

- A read of the INDF register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF Register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 10h-1Fh using indirect addressing is shown in Example 6-2.

#### EXAMPLE 6-2:

#### HOW TO CLEAR RAM USING INDIRECT ADDRESSING

|          | MOVLW | H'10' | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | MOVWF | FSR   | ; to RAM             |

| NEXT     | CLRF  | INDF  | ;clear INDF Register |

|          | INCF  | FSR,F | ;inc pointer         |

|          | BTFSC | FSR,4 | ;all done?           |

|          | GOTO  | NEXT  | ;NO, clear next      |

| CONTINUE |       |       |                      |

|          | :     |       | ;YES, continue       |

The FSR is either a 5-bit (PIC16C54, PIC16CR54, PIC16C55, PIC16C56, PIC16CR56) or 7-bit (PIC16C57, PIC16CR57, PIC16CR58, PIC16CR58) wide register. It is used in conjunction with the INDF Register to indirectly address the data memory area.

The FSR<4:0> bits are used to select data memory addresses 00h to 1Fh.

**PIC16C54, PIC16CR54, PIC16C55, PIC16C56, PIC16CR56:** These do not use banking. FSR<6:5> bits are unimplemented and read as '1's.

**PIC16C57**, **PIC16CR57**, **PIC16C58**, **PIC16CR58**: FSR<6:5> are the bank select bits and are used to select the bank to be addressed (00 = bank 0, 01 = bank 1, 10 = bank 2, 11 = bank 3).

© 1997-2013 Microchip Technology Inc.

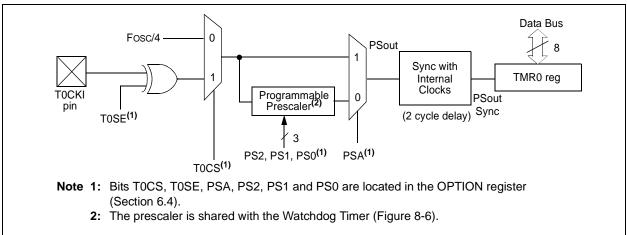

#### 8.0 TIMER0 MODULE AND TMR0 REGISTER

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Edge select for external clock

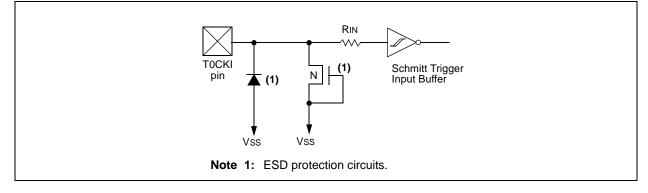

Figure 8-1 is a simplified block diagram of the Timer0 module, while Figure 8-2 shows the electrical structure of the Timer0 input.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two cycles (Figure 8-3 and Figure 8-4). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the T0CS bit (OPTION<5>). In this mode, Timer0 will increment either on every rising or falling edge of pin T0CKI. The incrementing edge is determined by the source edge select bit T0SE (OPTION<4>). Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 8.1.

Note: The prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both.

The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4,..., 1:256 are selectable. Section 8.2 details the operation of the prescaler.

A summary of registers associated with the Timer0 module is found in Table 8-1.

#### FIGURE 8-2: ELECTRICAL STRUCTURE OF TOCKI PIN

| CALL                                                                                                                                           | Subroutine Call                                                                                                                                                                                                                                                     |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                                                                                                                                        | [label] CALL k                                                                                                                                                                                                                                                      |  |  |  |  |

| Operands:                                                                                                                                      | $0 \leq k \leq 255$                                                                                                                                                                                                                                                 |  |  |  |  |

| Operation:                                                                                                                                     | (PC) + 1 $\rightarrow$ TOS;<br>k $\rightarrow$ PC<7:0>;<br>(STATUS<6:5>) $\rightarrow$ PC<10:9>;<br>0 $\rightarrow$ PC<8>                                                                                                                                           |  |  |  |  |

| Status Affected:                                                                                                                               | None                                                                                                                                                                                                                                                                |  |  |  |  |

| Encoding:                                                                                                                                      | 1001 kkkk kkkk                                                                                                                                                                                                                                                      |  |  |  |  |

| Description:                                                                                                                                   | Subroutine call. First, return<br>address (PC+1) is pushed onto the<br>stack. The eight bit immediate<br>address is loaded into PC bits<br><7:0>. The upper bits PC<10:9><br>are loaded from STATUS<6:5>,<br>PC<8> is cleared. CALL is a two-<br>cycle instruction. |  |  |  |  |

| Words:                                                                                                                                         | 1                                                                                                                                                                                                                                                                   |  |  |  |  |

| Cycles:                                                                                                                                        | 2                                                                                                                                                                                                                                                                   |  |  |  |  |

| Example: HERE CALL THERE                                                                                                                       |                                                                                                                                                                                                                                                                     |  |  |  |  |

| Example: HERE CALL THERE<br>Before Instruction<br>PC = address (HERE)<br>After Instruction<br>PC = address (THERE)<br>TOS = address (HERE + 1) |                                                                                                                                                                                                                                                                     |  |  |  |  |

| CLRF | Clear f |

|------|---------|

|      | Oloui I |

| Syntax:                                                    | [label] CLRF f                                                         |                  |  |  |  |

|------------------------------------------------------------|------------------------------------------------------------------------|------------------|--|--|--|

| Operands:                                                  | $0 \le f \le 3^{-1}$                                                   | $0 \le f \le 31$ |  |  |  |

| Operation:                                                 | $\begin{array}{l} 00h \rightarrow (f); \\ 1 \rightarrow Z \end{array}$ |                  |  |  |  |

| Status Affected:                                           | Z                                                                      |                  |  |  |  |

| Encoding:                                                  | 0000 011f ffff                                                         |                  |  |  |  |

| Description:                                               | The contents of register 'f' are cleared and the Z bit is set.         |                  |  |  |  |

| Words:                                                     | 1                                                                      |                  |  |  |  |

| Cycles:                                                    | 1                                                                      |                  |  |  |  |

| Example:                                                   | CLRF FLAG_REG                                                          |                  |  |  |  |

| Before Instruction<br>FLAG_REG = 0x5A<br>After Instruction |                                                                        |                  |  |  |  |

| $FLAG_REG = 0x00$ $Z = 1$                                  |                                                                        |                  |  |  |  |

| CLRW                                                                                                 | Clear W                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                              | [label] CLRW                                                                                                                                                                                                                                                                                                                                                                                            |

| Operands:                                                                                            | None                                                                                                                                                                                                                                                                                                                                                                                                    |

| Operation:                                                                                           | $\begin{array}{l} 00h \rightarrow (W); \\ 1 \rightarrow Z \end{array}$                                                                                                                                                                                                                                                                                                                                  |

| Status Affected:                                                                                     | Z                                                                                                                                                                                                                                                                                                                                                                                                       |

| Encoding:                                                                                            | 0000 0100 0000                                                                                                                                                                                                                                                                                                                                                                                          |

| Description:                                                                                         | The W register is cleared. Zero bit (Z) is set.                                                                                                                                                                                                                                                                                                                                                         |

| Words:                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                       |

| Cycles:                                                                                              | 1                                                                                                                                                                                                                                                                                                                                                                                                       |

| Example:                                                                                             | CLRW                                                                                                                                                                                                                                                                                                                                                                                                    |

| W =<br>After Instruct                                                                                | ion                                                                                                                                                                                                                                                                                                                                                                                                     |

| W =<br>Z =                                                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                       |

| Z =                                                                                                  | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                    |

| Z =<br>CLRWDT<br>Syntax:                                                                             | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                    |

| Z =<br>CLRWDT<br>Syntax:<br>Operands:                                                                | Clear Watchdog Timer<br>[ label ] CLRWDT<br>None                                                                                                                                                                                                                                                                                                                                                        |

| Z =<br>CLRWDT<br>Syntax:                                                                             | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                    |

| Z =<br>CLRWDT<br>Syntax:<br>Operands:                                                                | Clear Watchdog Timer<br>[ <i>label</i> ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow WDT$ prescaler (if assigned);<br>$1 \rightarrow TO;$                                                                                                                                                                                                                                                |

| Z =<br>CLRWDT<br>Syntax:<br>Operands:<br>Operation:                                                  | Clear Watchdog Timer<br>[ <i>label</i> ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow WDT$ prescaler (if assigned);<br>$1 \rightarrow \overline{TO};$<br>$1 \rightarrow \overline{PD}$                                                                                                                                                                                                    |

| Z =<br>CLRWDT<br>Syntax:<br>Operands:<br>Operation:<br>Status Affected:                              | Clear Watchdog Timer<br>[ <i>label</i> ] CLRWDT<br>None<br>$00h \rightarrow WDT;$<br>$0 \rightarrow WDT$ prescaler (if assigned);<br>$1 \rightarrow \overline{TO};$<br>$1 \rightarrow \overline{PD}$<br>$\overline{TO}, \overline{PD}$                                                                                                                                                                  |

| Z =<br>CLRWDT<br>Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                 | Clear Watchdog Timer[ label ] CLRWDTNone $00h \rightarrow WDT;$ $0 \rightarrow WDT$ prescaler (if assigned); $1 \rightarrow \overline{TO};$ $1 \rightarrow \overline{PD}$ $\overline{TO}, \overline{PD}$ $0000  0000  0100$ The CLRWDT instruction resets theWDT. It also resets the prescaler, ifthe prescaler is assigned to theWDT and not Timer0. Status bits                                       |

| Z =<br>CLRWDT<br>Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description: | Clear Watchdog Timer[ label ] CLRWDTNone $00h \rightarrow WDT$ ; $0 \rightarrow WDT$ prescaler (if assigned); $1 \rightarrow \overline{TO}$ ; $1 \rightarrow \overline{PD}$ $\overline{TO}$ , $\overline{PD}$ $0000$ $0000$ $0100$ The CLRWDT instruction resets theWDT. It also resets the prescaler, ifthe prescaler is assigned to theWDT and not Timer0. Status bitsTO and $\overline{PD}$ are set. |

| After Instruction |   |      |

|-------------------|---|------|

| WDT counter       | = | 0x00 |

| WDT prescaler     | = | 0    |

| TO                | = | 1    |

| PD                | = | 1    |

| GOTO                   | Unconditional Branch                                                                                                                                                                        |      |      |  |  |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|--|--|

| Syntax:                | [ label ]                                                                                                                                                                                   | GOTO | k    |  |  |

| Operands:              | $0 \le k \le 5^{-1}$                                                                                                                                                                        | 11   |      |  |  |

| Operation:             | $k \rightarrow PC < 8:0>;$<br>STATUS <6:5> $\rightarrow PC < 10:9>$                                                                                                                         |      |      |  |  |

| Status Affected:       | None                                                                                                                                                                                        |      |      |  |  |

| Encoding:              | 101k                                                                                                                                                                                        | kkkk | kkkk |  |  |

| Description:           | GOTO is an unconditional branch.<br>The 9-bit immediate value is<br>loaded into PC bits <8:0>. The<br>upper bits of PC are loaded from<br>STATUS<6:5>. GOTO is a two-<br>cycle instruction. |      |      |  |  |

| Words:                 | 1                                                                                                                                                                                           |      |      |  |  |

| Cycles:                | 2                                                                                                                                                                                           |      |      |  |  |

| Example:               | GOTO THERE                                                                                                                                                                                  |      |      |  |  |

| After Instruct<br>PC = | tion<br>address (THERE)                                                                                                                                                                     |      |      |  |  |

| INCF                                                    | Increment f                                                                                                                                                          |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                 | [label] INCF f,d                                                                                                                                                     |

| Operands:                                               | $\begin{array}{l} 0 \leq f \leq 31 \\ d  \in  [0,1] \end{array}$                                                                                                     |

| Operation:                                              | (f) + 1 $\rightarrow$ (dest)                                                                                                                                         |

| Status Affected:                                        | Z                                                                                                                                                                    |

| Encoding:                                               | 0010 10df ffff                                                                                                                                                       |

| Description:                                            | The contents of register 'f' are<br>incremented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'. |

| Words:                                                  | 1                                                                                                                                                                    |

| Cycles:                                                 | 1                                                                                                                                                                    |

| Example:                                                | INCF CNT, 1                                                                                                                                                          |

| Before Instru<br>CNT<br>Z<br>After Instruct<br>CNT<br>Z | = 0xFF<br>= 0                                                                                                                                                        |

| INCFSZ                               | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                                      |  |  |  |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                              | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Operands:                            | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                                                  |  |  |  |

| Operation:                           | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                                                                                                            |  |  |  |

| Status Affected:                     | None                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Encoding:                            | 0011 11df ffff                                                                                                                                                                                                                                                                                                                              |  |  |  |

| Description:                         | The contents of register 'f' are<br>incremented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'.<br>If the result is 0, then the next<br>instruction, which is already<br>fetched, is discarded and a NOP is<br>executed instead making it a two-<br>cycle instruction. |  |  |  |

| Words:                               | 1                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| Cycles:                              | 1(2)                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Example:                             | HERE INCFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•<br>•                                                                                                                                                                                                                                                                                     |  |  |  |

| Before Instru<br>PC<br>After Instruc | = address (HERE)                                                                                                                                                                                                                                                                                                                            |  |  |  |

| CNT<br>if CNT<br>PC<br>if CNT<br>PC  | <pre>= CNT + 1;<br/>= 0,<br/>= address (CONTINUE);<br/>≠ 0,<br/>= address (HERE +1)</pre>                                                                                                                                                                                                                                                   |  |  |  |

#### 12.7 Timing Diagrams and Specifications

#### FIGURE 12-2: EXTERNAL CLOCK TIMING - PIC16C54/55/56/57

#### TABLE 12-1: EXTERNAL CLOCK TIMING REQUIREMENTS - PIC16C54/55/56/57

| AC Chara     | acteristics | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array}$ |     |   |     |                   |                        |

|--------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---|-----|-------------------|------------------------|

| Param<br>No. | Symbol      | Characteristic Min Typ† Max Units Conditions                                                                                                                                                                                                                                                                                     |     |   |     |                   | Conditions             |

| 1A           | Fosc        | External CLKIN Frequency <sup>(1)</sup>                                                                                                                                                                                                                                                                                          | DC  |   | 4.0 | MHz               | XT OSC mode            |

|              |             |                                                                                                                                                                                                                                                                                                                                  | DC  | — | 10  | MHz               | 10 MHz mode            |

|              |             |                                                                                                                                                                                                                                                                                                                                  | DC  | _ | 20  | MHz               | HS osc mode (Comm/Ind) |

|              |             | DC — 16 MHz HS osc mode (Ext)                                                                                                                                                                                                                                                                                                    |     |   |     | HS osc mode (Ext) |                        |

|              |             |                                                                                                                                                                                                                                                                                                                                  | DC  | — | 40  | kHz               | LP osc mode            |

|              |             | Oscillator Frequency <sup>(1)</sup>                                                                                                                                                                                                                                                                                              | DC  | _ | 4.0 | MHz               | RC osc mode            |

|              |             |                                                                                                                                                                                                                                                                                                                                  | 0.1 | _ | 4.0 | MHz               | XT OSC mode            |

|              |             |                                                                                                                                                                                                                                                                                                                                  | 4.0 | _ | 10  | MHz               | 10 MHz mode            |

|              |             |                                                                                                                                                                                                                                                                                                                                  | 4.0 | — | 20  | MHz               | HS OSC mode (Comm/Ind) |

|              |             |                                                                                                                                                                                                                                                                                                                                  | 4.0 | _ | 16  | MHz               | HS osc mode (Ext)      |

|              |             |                                                                                                                                                                                                                                                                                                                                  | DC  | — | 40  | kHz               | LP osc mode            |

\* These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

**2:** Instruction cycle period (TCY) equals four times the input oscillator time base period.

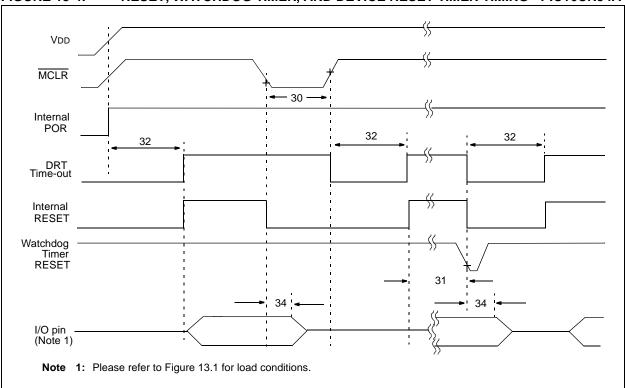

#### FIGURE 13-4: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING - PIC16CR54A

#### TABLE 13-3: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER - PIC16CR54A

| AC Chara     | cteristics | $ \begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \\ \end{array} $ |      |      |      |       |                   |  |  |

|--------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|-------------------|--|--|

| Param<br>No. | Symbol     | Characteristic                                                                                                                                                                                                                                                                                                                        | Min  | Тур† | Max  | Units | Conditions        |  |  |

| 30           | TmcL       | MCLR Pulse Width (low)                                                                                                                                                                                                                                                                                                                | 1.0* |      |      | μS    | VDD = 5.0V        |  |  |

| 31           | Twdt       | Watchdog Timer Time-out Period<br>(No Prescaler)                                                                                                                                                                                                                                                                                      | 7.0* | 18*  | 40*  | ms    | VDD = 5.0V (Comm) |  |  |

| 32           | Tdrt       | Device Reset Timer Period                                                                                                                                                                                                                                                                                                             | 7.0* | 18*  | 30*  | ms    | VDD = 5.0V (Comm) |  |  |

| 34           | Tioz       | I/O Hi-impedance from MCLR Low                                                                                                                                                                                                                                                                                                        |      |      | 1.0* | μS    |                   |  |  |

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### TABLE 14-2: INPUT CAPACITANCE FOR PIC16C54/56

| Pin         | Typical Capa | acitance (pF) |  |

|-------------|--------------|---------------|--|

| F111        | 18L PDIP     | 18L SOIC      |  |

| RA port     | 5.0          | 4.3           |  |

| RB port     | 5.0          | 4.3           |  |

| MCLR        | 17.0         | 17.0          |  |

| OSC1        | 4.0          | 3.5           |  |

| OSC2/CLKOUT | 4.3          | 3.5           |  |

| T0CKI       | 3.2          | 2.8           |  |

All capacitance values are typical at  $25^{\circ}$ C. A part-to-part variation of ±25% (three standard deviations) should be taken into account.

| TABLE 14-3: | INPUT CAPACITANCE FOR |

|-------------|-----------------------|

|             | PIC16C55/57           |

|             | Typical Capacitance (pF) |          |  |  |  |  |

|-------------|--------------------------|----------|--|--|--|--|

| Pin         | 28L PDIP<br>(600 mil)    | 28L SOIC |  |  |  |  |

| RA port     | 5.2                      | 4.8      |  |  |  |  |

| RB port     | 5.6                      | 4.7      |  |  |  |  |

| RC port     | 5.0                      | 4.1      |  |  |  |  |

| MCLR        | 17.0                     | 17.0     |  |  |  |  |

| OSC1        | 6.6                      | 3.5      |  |  |  |  |

| OSC2/CLKOUT | 4.6                      | 3.5      |  |  |  |  |

| T0CKI       | 4.5                      | 3.5      |  |  |  |  |

All capacitance values are typical at  $25^{\circ}$ C. A part-to-part variation of ±25% (three standard deviations) should be taken into account.

#### 15.1 DC Characteristics: PIC16C54A-04, 10, 20 (Commercial) PIC16C54A-04I, 10I, 20I (Industrial) PIC16LC54A-04 (Commercial) PIC16LC54A-04I (Industrial)

| PIC16LC54A-04<br>PIC16LC54A-04I<br>(Commercial, Industrial)                 |        |                                   |                                                      | ard Ope<br>ting Tem        | -                      | ure                  | itions (unless otherwise specified)<br>$0^{\circ}C \le TA \le +70^{\circ}C$ for commercial<br>$40^{\circ}C \le TA \le +85^{\circ}C$ for industrial         |  |  |  |  |

|-----------------------------------------------------------------------------|--------|-----------------------------------|------------------------------------------------------|----------------------------|------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PIC16C54A-04, 10, 20<br>PIC16C54A-04I, 10I, 20I<br>(Commercial, Industrial) |        |                                   | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                            |                        |                      |                                                                                                                                                            |  |  |  |  |

| Param<br>No.                                                                | Symbol | Characteristic/Device             | Min                                                  | Тур†                       | Max                    | Units                | Conditions                                                                                                                                                 |  |  |  |  |

|                                                                             | IPD    | Power-down Current <sup>(2)</sup> |                                                      |                            |                        |                      |                                                                                                                                                            |  |  |  |  |

| D006                                                                        |        | PIC16LC5X                         |                                                      | 2.5<br>0.25<br>2.5<br>0.25 | 12<br>4.0<br>14<br>5.0 | μΑ<br>μΑ<br>μΑ<br>μΑ | VDD = 2.5V, WDT enabled, Commercial<br>VDD = 2.5V, WDT disabled, Commercial<br>VDD = 2.5V, WDT enabled, Industrial<br>VDD = 2.5V, WDT disabled, Industrial |  |  |  |  |

| D006A                                                                       |        | PIC16C5X                          |                                                      | 4.0<br>0.25<br>5.0<br>0.3  | 12<br>4.0<br>14<br>5.0 | μΑ<br>μΑ<br>μΑ<br>μΑ | VDD = 3.0V, WDT enabled, Commercial<br>VDD = 3.0V, WDT disabled, Commercial<br>VDD = 3.0V, WDT enabled, Industrial<br>VDD = 3.0V, WDT disabled, Industrial |  |  |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

\* These parameters are characterized but not tested.

† Data in "Typ" column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/ disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- 3: Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in k $\Omega$ .

# 15.4 DC Characteristics: PIC16C54A-04, 10, 20, PIC16LC54A-04, PIC16LV54A-02 (Commercial) PIC16C54A-04I, 10I, 20I, PIC16LC54A-04I, PIC16LV54A-02I (Industrial) PIC16C54A-04I, 10I, 20I, PIC16LC54A-04I, PIC16LV54A-02I (Industrial) PIC16C54A-04E, 10E, 20E, PIC16LC54A-04E (Extended)

| DC CHARACTERISTICS |        |                                                                                                                                     | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^\circ C \leq TA \leq +70^\circ C \mbox{ for commercial} \\ -40^\circ C \leq TA \leq +85^\circ C \mbox{ for industrial} \\ -20^\circ C \leq TA \leq +85^\circ C \mbox{ for industrial-PIC16LV54A-02I} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for extended} \end{array}$ |                              |                                                        |                            |                                                                                                                                                                                                   |  |

|--------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic                                                                                                                      | Min                                                                                                                                                                                                                                                                                                                                                                                                     | Тур†                         | Мах                                                    | Units                      | Conditions                                                                                                                                                                                        |  |

| D030               | VIL    | Input Low Voltage<br>I/O ports<br>MCLR (Schmitt Trigger)<br>T0CKI (Schmitt Trigger)<br>OSC1 (Schmitt Trigger)<br>OSC1               | Vss<br>Vss<br>Vss<br>Vss<br>Vss<br>Vss                                                                                                                                                                                                                                                                                                                                                                  |                              | 0.2 VDD<br>0.15 VDD<br>0.15 VDD<br>0.15 VDD<br>0.3 VDD | V<br>V<br>V<br>V           | Pin at hi-impedance<br>RC mode only <sup>(3)</sup><br>XT, HS and LP modes                                                                                                                         |  |

| D040               | VIH    | Input High Voltage<br>I/O ports<br>I/O ports<br>MCLR (Schmitt Trigger)<br>T0CKI (Schmitt Trigger)<br>OSC1 (Schmitt Trigger)<br>OSC1 | 0.2 VDD + 1<br>2.0<br>0.85 VDD<br>0.85 VDD<br>0.85 VDD<br>0.85 VDD<br>0.7 VDD                                                                                                                                                                                                                                                                                                                           |                              | VDD<br>VDD<br>VDD<br>VDD<br>VDD<br>VDD<br>VDD          | V<br>V<br>V<br>V<br>V<br>V | For all V <sub>DD</sub> <sup>(4)</sup><br>4.0V < V <sub>DD</sub> ≤ 5.5V <sup>(4)</sup><br>RC mode only <sup>(3)</sup><br>XT, HS and LP modes                                                      |  |

| D050               | VHYS   | Hysteresis of Schmitt<br>Trigger inputs                                                                                             | 0.15 Vdd*                                                                                                                                                                                                                                                                                                                                                                                               | _                            | —                                                      | V                          |                                                                                                                                                                                                   |  |

| D060               | IIL    | Input Leakage Current <sup>(1,2)</sup><br>I/O ports<br>MCLR<br>MCLR<br>TOCKI<br>OSC1                                                | -1.0<br>-5.0<br><br>-3.0<br>-3.0                                                                                                                                                                                                                                                                                                                                                                        | 0.5<br><br>0.5<br>0.5<br>0.5 | +1.0<br>+5.0<br>+3.0<br>+3.0<br>—                      | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ | For VDD $\leq$ 5.5V:<br>VSS $\leq$ VPIN $\leq$ VDD,<br>pin at hi-impedance<br>VPIN = VSS +0.25V<br>VPIN = VDD<br>VSS $\leq$ VPIN $\leq$ VDD<br>VSS $\leq$ VPIN $\leq$ VDD,<br>XT, HS and LP modes |  |

| D080               | VOL    | Output Low Voltage<br>I/O ports<br>OSC2/CLKOUT                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                         | _                            | 0.6<br>0.6                                             | V<br>V                     | IOL = 8.7  mA,  VDD = 4.5 V<br>IOL = 1.6  mA,  VDD = 4.5 V,<br>RC mode only                                                                                                                       |  |

|                    | VOH    | Output High Voltage <sup>(2)</sup><br>I/O ports<br>OSC2/CLKOUT                                                                      | Vdd - 0.7<br>Vdd - 0.7                                                                                                                                                                                                                                                                                                                                                                                  |                              |                                                        | V<br>V                     | IOH = -5.4 mA, VDD = 4.5V<br>IOH = -1.0 mA, VDD = 4.5V,<br>RC mode only                                                                                                                           |  |

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

**Note 1:** The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltage.

2: Negative current is defined as coming out of the pin.

**3:** For the RC mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C5X be driven with external clock in RC mode.

\*

### 19.0 ELECTRICAL CHARACTERISTICS - PIC16LC54C 40MHz

#### Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                                                                 | –55°C to +125°C               |

|----------------------------------------------------------------------------------------------------------------|-------------------------------|

| Storage temperature                                                                                            | –65°C to +150°C               |

| Voltage on VDD with respect to VSS                                                                             | 0 to +7.5V                    |

| Voltage on MCLR with respect to Vss                                                                            | 0 to +14V                     |

| Voltage on all other pins with respect to Vss                                                                  | –0.6V to (VDD + 0.6V)         |

| Total power dissipation <sup>(1)</sup>                                                                         | 800 mW                        |

| Max. current out of Vss pin                                                                                    | 150 mA                        |

| Max. current into Vod pin                                                                                      |                               |

| Max. current into an input pin (T0CKI only)                                                                    | ±500 μA                       |

| Input clamp current, liк (Vi <0 or Vi > VDD)                                                                   | ±20 mA                        |

| Output clamp current, IOK (VO < 0 or VO > VDD)                                                                 | ±20 mA                        |

| Max. output current sunk by any I/O pin                                                                        | 25 mA                         |

| Max. output current sourced by any I/O pin                                                                     | 20 mA                         |

| Max. output current sourced by a single I/O (Port A, B or C)                                                   | 50 mA                         |

| Max. output current sunk by a single I/O (Port A, B or C)                                                      | 50 mA                         |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) | x IOH} + $\Sigma$ (Vol x Iol) |

**†** NOTICE: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# 19.2 DC Characteristics: PIC16C54C/C55A/C56A/C57C/C58B-40 (Commercial)<sup>(1)</sup>

|              |        |                                                                                              | Standard Operating Conditions (unless otherwise specified)Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial |                               |                                        |                      |                                                                                                                                                                               |  |

|--------------|--------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No. | Symbol | Characteristic                                                                               | Min                                                                                                                                 | Тур†                          | Max                                    | Units                | Conditions                                                                                                                                                                    |  |

| D030         | VIL    | Input Low Voltage<br>I/O Ports<br>MCLR (Schmitt Trigger)<br>T0CKI (Schmitt Trigger)<br>OSC1  | Vss<br>Vss<br>Vss<br>Vss                                                                                                            |                               | 0.8<br>0.15 VDD<br>0.15 VDD<br>0.2 VDD | > > ><br>> > >       | 4.5V <vdd <math="">\leq 5.5V<br/>HS, 20 MHz <math>\leq</math> Fosc <math>\leq</math> 40 MHz</vdd>                                                                             |  |

| D040         | Viн    | Input High Voltage<br>I/O ports<br>MCLR (Schmitt Trigger)<br>T0CKI (Schmitt Trigger)<br>OSC1 | 2.0<br>0.85 Vdd<br>0.85 Vdd<br>0.85 Vdd<br>0.8 Vdd                                                                                  |                               | Vdd<br>Vdd<br>Vdd<br>Vdd               | V<br>V<br>V<br>V     | $4.5V < VDD \le 5.5V$<br>HS, 20 MHz $\le$ Fosc $\le$ 40 MHz                                                                                                                   |  |

| D050         | VHYS   | Hysteresis of Schmitt<br>Trigger inputs                                                      | 0.15 Vdd*                                                                                                                           | _                             | _                                      | V                    |                                                                                                                                                                               |  |

| D060         | lı∟    | Input Leakage Current <sup>(2,3)</sup><br>I/O ports<br>MCLR<br>MCLR<br>T0CKI<br>OSC1         | -1.0<br>-5.0<br><br>-3.0<br>-3.0                                                                                                    | 0.5<br>—<br>0.5<br>0.5<br>0.5 | +1.0<br>+5.0<br>+3.0<br>+3.0<br>—      | μΑ<br>μΑ<br>μΑ<br>μΑ | For VDD $\leq$ 5.5V:<br>VSS $\leq$ VPIN $\leq$ VDD,<br>pin at hi-impedance<br>VPIN = VSS +0.25V<br>VPIN = VDD<br>VSS $\leq$ VPIN $\leq$ VDD<br>VSS $\leq$ VPIN $\leq$ VDD, HS |  |

| D080         | Vol    | Output Low Voltage<br>I/O ports                                                              |                                                                                                                                     | _                             | 0.6                                    | V                    | Iol = 8.7 mA, Vdd = 4.5V                                                                                                                                                      |  |

| D090         | Vон    | <b>Output High Voltage<sup>(3)</sup></b><br>I/O ports                                        | Vdd - 0.7                                                                                                                           | _                             | _                                      | V                    | Іон = -5.4 mA, Vdd = 4.5V                                                                                                                                                     |  |

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

**Note 1:** Device operation between 20 MHz to 40 MHz requires the following: VDD between 4.5V to 5.5V, OSC1 pin externally driven, OSC2 pin not connected and HS oscillator mode and commercial temperatures. For operation between DC and 20 MHz, See Section 17.3.

2: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltage.

**3:** Negative current is defined as coming out of the pin.

NOTES:

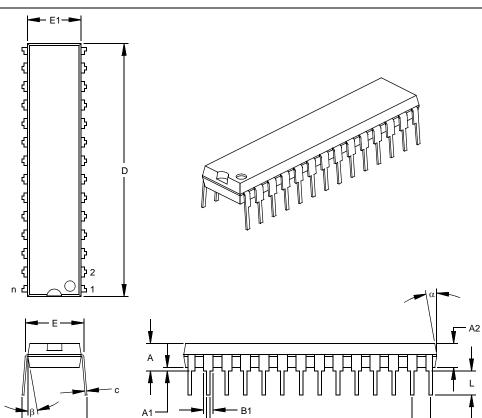

#### 28-Lead Skinny Plastic Dual In-line (SP) - 300 mil (PDIP)

в

|                            |      | INCHES* |       | Μ     | IILLIMETERS |       |       |

|----------------------------|------|---------|-------|-------|-------------|-------|-------|

| Dimensi                    | MIN  | NOM     | MAX   | MIN   | NOM         | MAX   |       |

| Number of Pins             | n    |         | 28    |       |             | 28    |       |

| Pitch                      | р    |         | .100  |       |             | 2.54  |       |

| Top to Seating Plane       | А    | .140    | .150  | .160  | 3.56        | 3.81  | 4.06  |

| Molded Package Thickness   | A2   | .125    | .130  | .135  | 3.18        | 3.30  | 3.43  |

| Base to Seating Plane      | A1   | .015    |       |       | 0.38        |       |       |

| Shoulder to Shoulder Width | Е    | .300    | .310  | .325  | 7.62        | 7.87  | 8.26  |

| Molded Package Width       | E1   | .275    | .285  | .295  | 6.99        | 7.24  | 7.49  |

| Overall Length             | D    | 1.345   | 1.365 | 1.385 | 34.16       | 34.67 | 35.18 |

| Tip to Seating Plane       | L    | .125    | .130  | .135  | 3.18        | 3.30  | 3.43  |

| Lead Thickness             | С    | .008    | .012  | .015  | 0.20        | 0.29  | 0.38  |

| Upper Lead Width           | B1   | .040    | .053  | .065  | 1.02        | 1.33  | 1.65  |

| Lower Lead Width           | В    | .016    | .019  | .022  | 0.41        | 0.48  | 0.56  |

| Overall Row Spacing        | § eB | .320    | .350  | .430  | 8.13        | 8.89  | 10.92 |

| Mold Draft Angle Top       | α    | 5       | 10    | 15    | 5           | 10    | 15    |

| Mold Draft Angle Bottom    | β    | 5       | 10    | 15    | 5           | 10    | 15    |

\* Controlling Parameter § Significant Characteristic

eВ

Dimension D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side.

JEDEC Equivalent: MO-095

Drawing No. C04-070

- p -

Notes:

#### **ON-LINE SUPPORT**

Microchip provides on-line support on the Microchip World Wide Web (WWW) site.