Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | POR, WDT                                                                    |

| Number of I/O              | 20                                                                          |

| Program Memory Size        | 3KB (2K x 12)                                                               |

| Program Memory Type        | ОТР                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 72 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                 |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc57ct-04-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 4.0   |                                                                                        | _    |

|-------|----------------------------------------------------------------------------------------|------|

| 1.0   | General Description                                                                    |      |

| 2.0   | PIC16C5X Device Varieties                                                              |      |

| 3.0   | Architectural Overview                                                                 |      |

| 4.0   | Oscillator Configurations                                                              | . 15 |

| 5.0   | Reset                                                                                  | . 19 |

| 6.0   | Memory Organization                                                                    | . 25 |

| 7.0   | I/O Ports                                                                              | . 35 |

| 8.0   | Timer0 Module and TMR0 Register                                                        | . 37 |

| 9.0   | Special Features of the CPU                                                            | . 43 |

| 10.0  | Instruction Set Summary                                                                | . 49 |

| 11.0  | Development Support                                                                    | . 61 |

| 12.0  | Electrical Characteristics - PIC16C54/55/56/57                                         | . 67 |

| 13.0  | Electrical Characteristics - PIC16CR54A                                                |      |

| 14.0  | Device Characterization - PIC16C54/55/56/57/CR54A                                      | . 91 |

| 15.0  | Electrical Characteristics - PIC16C54A                                                 | 103  |

| 16.0  | Device Characterization - PIC16C54A                                                    | 117  |

| 17.0  | Electrical Characteristics - PIC16C54C/CR54C/C55A/C56A/CR56A/C57C/CR57C/C58B/CR58B     | 131  |

| 18.0  | Device Characterization - PIC16C54C/CR54C/C55A/C56A/CR56A/CR56A/CR57C/CR57C/C58B/CR58B | 145  |

| 19.0  | Electrical Characteristics - PIC16C54C/C55A/C56A/C57C/C58B 40MHz                       | 155  |

| 20.0  | Device Characterization - PIC16C54C/C55A/C56A/C57C/C58B 40MHz                          | 165  |

| 21.0  | Packaging Information                                                                  | 171  |

| Appe  | ndix A: Compatibility                                                                  | 182  |

| On-L  | ne Support                                                                             | 187  |

| Read  | er Response                                                                            | 188  |

| Produ | uct Identification System                                                              | 189  |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

# Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

# Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

# **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

# PIC16C5X

# 8-Bit EPROM/ROM-Based CMOS Microcontrollers

# 1.0 GENERAL DESCRIPTION

The PIC16C5X from Microchip Technology is a family of low cost, high performance, 8-bit fully static, EPROM/ROM-based CMOS microcontrollers. It employs a RISC architecture with only 33 single word/ single cycle instructions. All instructions are single cycle except for program branches which take two cycles. The PIC16C5X delivers performance in an order of magnitude higher than its competitors in the same price category. The 12-bit wide instructions are highly symmetrical resulting in 2:1 code compression over other 8-bit microcontrollers in its class. The easy to use and easy to remember instruction set reduces development time significantly.

The PIC16C5X products are equipped with special features that reduce system cost and power requirements. The Power-on Reset (POR) and Device Reset Timer (DRT) eliminate the need for external RESET circuitry. There are four oscillator configurations to choose from, including the power saving LP (Low Power) oscillator and cost saving RC oscillator. Power saving SLEEP mode, Watchdog Timer and Code Protection features improve system cost, power and reliability.

The UV erasable CERDIP packaged versions are ideal for code development, while the cost effective One Time Programmable (OTP) versions are suitable for production in any volume. The customer can take full advantage of Microchip's price leadership in OTP microcontrollers, while benefiting from the OTP's flexibility.

The PIC16C5X products are supported by a full featured macro assembler, a software simulator, an in-circuit emulator, a low cost development programmer and a full featured programmer. All the tools are supported on IBM<sup>®</sup> PC and compatible machines.

# 1.1 Applications

The PIC16C5X series fits perfectly in applications ranging from high speed automotive and appliance motor control to low power remote transmitters/receivers, pointing devices and telecom processors. The EPROM technology makes customizing application programs (transmitter codes, motor speeds, receiver frequencies, etc.) extremely fast and convenient. The small footprint packages, for through hole or surface mounting, make this microcontroller series perfect for applications with space limitations. Low cost, low power, high performance ease of use and I/O flexibility make the PIC16C5X series very versatile even in areas where no microcontroller use has been considered before (e.g., timer functions, replacement of "glue" logic in larger systems, co-processor applications).

# 6.3 STATUS Register

This register contains the arithmetic status of the ALU, the RESET status and the page preselect bits for program memories larger than 512 words.

The STATUS Register can be the destination for any instruction, as with any other register. If the STATUS Register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not

writable. Therefore, the result of an instruction with the STATUS Register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS Register as  $000u \ u1uu$  (where u = unchanged).

It is recommended, therefore, that only BCF, BSF and MOVWF instructions be used to alter the STATUS Register because these instructions do not affect the Z, DC or C bits from the STATUS Register. For other instructions which do affect STATUS Bits, see Section 10.0, Instruction Set Summary.

# REGISTER 6-1: STATUS REGISTER (ADDRESS: 03h)

|          | R/W-0                                                                                                                                                         | R/W-0                              | R/W-0        | R-1          | R-1                        | R/W-x         | R/W-x          | R/W-x          |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------------|--------------|----------------------------|---------------|----------------|----------------|

|          | PA2                                                                                                                                                           | PA1                                | PA0          | TO           | PD                         | Z             | DC             | С              |

|          | bit 7                                                                                                                                                         |                                    |              |              |                            |               |                | bit 0          |

| bit 7:   | PA2: This bit                                                                                                                                                 | unused at th                       | is time.     |              |                            |               |                |                |

|          |                                                                                                                                                               | A2 bit as a ge<br>with future pr   |              | e read/write | bit is not recor           | mmended, sir  | nce this may a | affect upward  |

| bit 6-5: |                                                                                                                                                               |                                    |              | -            | CR56)(PIC16                |               |                | 58)            |

|          |                                                                                                                                                               |                                    |              |              | 16C57/CR57,<br>16C57/CR57, |               |                |                |

|          |                                                                                                                                                               | (400h - 5FFh                       |              |              |                            | FIC 10C30/C   | N00            |                |

|          | 11 = Page 3                                                                                                                                                   | (600h - 7FFh                       |              |              |                            |               |                |                |

|          | Each page is                                                                                                                                                  |                                    | deperal pur  | ose read/wr  | ite bits in devi           | ices which do | not use them   | for program    |

|          |                                                                                                                                                               |                                    |              |              | affect upward              |               |                |                |

| bit 4:   | TO: Time-ou                                                                                                                                                   |                                    |              | ,            | •                          |               |                |                |

|          |                                                                                                                                                               | ver-up, CLRWI<br>ime-out occur     |              | , or sleep i | nstruction                 |               |                |                |

| bit 3:   | PD: Power-d                                                                                                                                                   | lown bit                           |              |              |                            |               |                |                |

|          | •                                                                                                                                                             | ver-up or by tl<br>ution of the SI |              |              |                            |               |                |                |

| bit 2:   | Z: Zero bit                                                                                                                                                   |                                    |              |              |                            |               |                |                |

|          |                                                                                                                                                               | lt of an arithm<br>It of an arithm |              |              |                            |               |                |                |

| bit 1:   | DC: Digit car                                                                                                                                                 | ry/borrow bit                      | (for ADDWF a | nd SUBWF in  | structions)                |               |                |                |

|          | ADDWF                                                                                                                                                         |                                    |              |              |                            |               |                |                |

|          | <ul> <li>1 = A carry from the 4th low order bit of the result occurred</li> <li>0 = A carry from the 4th low order bit of the result did not occur</li> </ul> |                                    |              |              |                            |               |                |                |

|          | SUBWF                                                                                                                                                         |                                    |              |              |                            |               |                |                |

|          | 1 = A borrow from the 4th low order bit of the result did not occur<br>0 = A borrow from the 4th low order bit of the result occurred                         |                                    |              |              |                            |               |                |                |

|          |                                                                                                                                                               |                                    |              |              |                            |               |                |                |

| bit 0:   | -                                                                                                                                                             | row bit (for AI                    |              |              | F instructions             |               | _              |                |

|          | <b>ADDWF</b><br>1 = A carry o                                                                                                                                 | ocurred                            |              | orrow did n  | ot occur                   | RRF or RLI    |                | , respectively |

|          | $\pm = \pi \operatorname{carry} 0$                                                                                                                            | locurrou                           | / · ·        |              |                            |               |                |                |

| Legena:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | 1 = bit is set   | 0 = bit is cleared        | x = bit is unknown |

# 6.4 **OPTION Register**

The OPTION Register is a 6-bit wide, write-only register which contains various control bits to configure the Timer0/WDT prescaler and Timer0.

By executing the OPTION instruction, the contents of the W Register will be transferred to the OPTION Register. A RESET sets the OPTION<5:0> bits.

# **REGISTER 6-2: OPTION REGISTER**

| U-0   | U-0 | W-1  | W-1  | W-1 | W-1 | W-1 | W-1   |

|-------|-----|------|------|-----|-----|-----|-------|

| _     | _   | TOCS | TOSE | PSA | PS2 | PS1 | PS0   |

| bit 7 |     |      |      |     |     |     | bit 0 |

- bit 7-6: Unimplemented: Read as '0'

- bit 5: **TOCS**: Timer0 clock source select bit

- 1 = Transition on T0CKI pin

- 0 = Internal instruction cycle clock (CLKOUT)

- bit 4: **TOSE**: Timer0 source edge select bit

- 1 = Increment on high-to-low transition on T0CKI pin

- 0 = Increment on low-to-high transition on T0CKI pin

- bit 3: **PSA**: Prescaler assignment bit

- 1 = Prescaler assigned to the WDT

- 0 = Prescaler assigned to Timer0

### bit 2-0: **PS<2:0>:** Prescaler rate select bits

| Bit Value | Timer0 Rate | WDT Rate |

|-----------|-------------|----------|

| 000       | 1:2         | 1:1      |

| 001       | 1:4         | 1:2      |

| 010       | 1:8         | 1:4      |

| 011       | 1:16        | 1:8      |

| 100       | 1:32        | 1:16     |

| 101       | 1:64        | 1:32     |

| 110       | 1 : 128     | 1:64     |

| 111       | 1:256       | 1:128    |

|           |             |          |

| Legend:           |                  |                     |                    |

|-------------------|------------------|---------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b | it, read as '0'    |

| -n = Value at POR | 1 = bit is set   | 0 = bit is cleared  | x = bit is unknown |

# 6.5 Program Counter

As a program instruction is executed, the Program Counter (PC) will contain the address of the next program instruction to be executed. The PC value is increased by one, every instruction cycle, unless an instruction changes the PC.

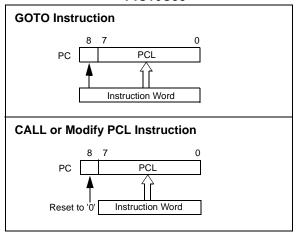

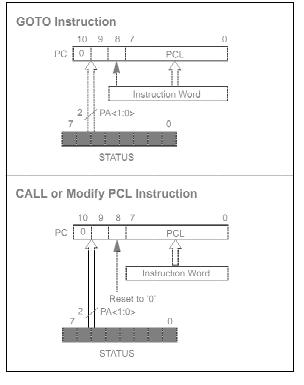

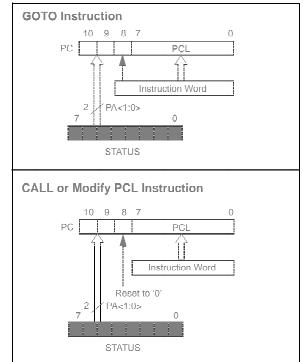

For a GOTO instruction, bits 8:0 of the PC are provided by the GOTO instruction word. The PC Latch (PCL) is mapped to PC<7:0> (Figure 6-7, Figure 6-8 and Figure 6-9).

For the PIC16C56, PIC16CR56, PIC16C57, PIC16CR57, PIC16C757, PIC16C58 and PIC16CR58, a page number must be supplied as well. Bit5 and bit6 of the STA-TUS Register provide page information to bit9 and bit10 of the PC (Figure 6-8 and Figure 6-9).

For a CALL instruction, or any instruction where the PCL is the destination, bits 7:0 of the PC again are provided by the instruction word. However, PC<8> does not come from the instruction word, but is always cleared (Figure 6-7 and Figure 6-8).

Instructions where the PCL is the destination, or modify PCL instructions, include MOVWF PCL, ADDWF PCL, and BSF PCL, 5.

For the PIC16C56, PIC16CR56, PIC16C57, PIC16CR57, PIC16C58 and PIC16CR58, a page number again must be supplied. Bit5 and bit6 of the STA-TUS Register provide page information to bit9 and bit10 of the PC (Figure 6-8 and Figure 6-9).

| Note: | Because PC<8> is cleared in the CALL           |  |  |  |  |  |

|-------|------------------------------------------------|--|--|--|--|--|

|       | instruction, or any modify PCL instruction,    |  |  |  |  |  |

|       | all subroutine calls or computed jumps are     |  |  |  |  |  |

|       | limited to the first 256 locations of any pro- |  |  |  |  |  |

|       | gram memory page (512 words long).             |  |  |  |  |  |

# FIGURE 6-7: LOADING OF PC BRANCH INSTRUCTIONS - PIC16C54, PIC16CR54, PIC16C55

# FIGURE 6-8:

# LOADING OF PC BRANCH INSTRUCTIONS - PIC16C56/PIC16CR56

FIGURE 6-9:

LOADING OF PC BRANCH INSTRUCTIONS - PIC16C57/PIC16CR57, AND PIC16C58/ PIC16CR58

# 6.5.1 PAGING CONSIDERATIONS – PIC16C56/CR56, PIC16C57/CR57 AND PIC16C58/CR58

If the Program Counter is pointing to the last address of a selected memory page, when it increments it will cause the program to continue in the next higher page. However, the page preselect bits in the STATUS Register will not be updated. Therefore, the next GOTO, CALL or modify PCL instruction will send the program to the page specified by the page preselect bits (PA0 or PA<1:0>).

For example, a NOP at location 1FFh (page 0) increments the PC to 200h (page 1). A GOTO xxx at 200h will return the program to address xxh on page 0 (assuming that PA<1:0> are clear).

To prevent this, the page preselect bits must be updated under program control.

# 6.5.2 EFFECTS OF RESET

The Program Counter is set upon a RESET, which means that the PC addresses the last location in the last page (i.e., the RESET vector).

The STATUS Register page preselect bits are cleared upon a RESET, which means that page 0 is pre-selected.

Therefore, upon a RESET, a GOTO instruction at the RESET vector location will automatically cause the program to jump to page 0.

# 6.6 Stack

PIC16C5X devices have a 10-bit or 11-bit wide, two-level hardware push/pop stack.

A CALL instruction will push the current value of stack 1 into stack 2 and then push the current program counter value, incremented by one, into stack level 1. If more than two sequential CALL's are executed, only the most recent two return addresses are stored.

A RETLW instruction will pop the contents of stack level 1 into the program counter and then copy stack level 2 contents into level 1. If more than two sequential RETLW's are executed, the stack will be filled with the address previously stored in level 2. Note that the W Register will be loaded with the literal value specified in the instruction. This is particularly useful for the implementation of data look-up tables within the program memory.

For the RETLW instruction, the PC is loaded with the Top of Stack (TOS) contents. All of the devices covered in this data sheet have a two-level stack. The stack has the same bit width as the device PC, therefore, paging is not an issue when returning from a subroutine.

# 7.0 I/O PORTS

As with any other register, the I/O Registers can be written and read under program control. However, read instructions (e.g., MOVF PORTB, W) always read the I/O pins independent of the pin's input/output modes. On RESET, all I/O ports are defined as input (inputs are at hi-impedance) since the I/O control registers (TRISA, TRISB, TRISC) are all set.

# 7.1 PORTA

PORTA is a 4-bit I/O Register. Only the low order 4 bits are used (RA<3:0>). Bits 7-4 are unimplemented and read as '0's.

# 7.2 PORTB

PORTB is an 8-bit I/O Register (PORTB<7:0>).

# 7.3 PORTC

PORTC is an 8-bit I/O Register for PIC16C55, PIC16C57 and PIC16CR57.

PORTC is a General Purpose Register for PIC16C54, PIC16CR54, PIC16CR56, PIC16CR56, PIC16CS8 and PIC16CR58.

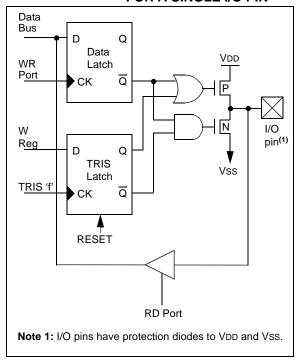

# 7.4 TRIS Registers

The Output Driver Control Registers are loaded with the contents of the W Register by executing the TRIS f instruction. A '1' from a TRIS Register bit puts the corresponding output driver in a hi-impedance (input) mode. A '0' puts the contents of the output data latch on the selected pins, enabling the output buffer.

| Note: | A read of the ports reads the pins, not the    |  |  |  |  |  |

|-------|------------------------------------------------|--|--|--|--|--|

|       | output data latches. That is, if an output     |  |  |  |  |  |

|       | driver on a pin is enabled and driven high,    |  |  |  |  |  |

|       | but the external system is holding it low, a   |  |  |  |  |  |

|       | read of the port will indicate that the pin is |  |  |  |  |  |

|       | low.                                           |  |  |  |  |  |

The TRIS Registers are "write-only" and are set (output drivers disabled) upon RESET.

| TABLE 7-1: | SUMMARY OF PORT REGISTERS |

|------------|---------------------------|

|            |                           |

#### Value on Value on Bit 4 Bit 3 Bit 1 Bit 0 MCLR and Address Name Bit 7 Bit 6 Bit 5 Bit 2 Power-On Reset WDT Reset TRIS N/A I/O Control Registers (TRISA, TRISB, TRISC) 1111 1111 1111 1111 05h PORTA RA3 RA2 RA1 RA0 \_ \_ \_ \_ xxxx \_ \_ \_ \_ uuuu PORTB 06h RB7 RB6 RB5 RB4 RB3 RB2 RB1 RB0 XXXX XXXX uuuu uuuu 07h PORTC RC7 RC6 RC5 RC4 RC3 RC2 RC1 RC0 XXXX XXXX uuuu uuuu

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0', Shaded cells = unimplemented, read as '0'

# 7.5 I/O Interfacing

The equivalent circuit for an I/O port pin is shown in Figure 7-1. All ports may be used for both input and output operation. For input operations these ports are non-latching. Any input must be present until read by an input instruction (e.g., MOVF PORTB, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit (in TRISA, TRISB, TRISC) must be cleared (= 0). For use as an input, the corresponding TRIS bit must be set. Any I/O pin can be programmed individually as input or output.

## FIGURE 7-1: EQUIVALENT CIRCUIT FOR A SINGLE I/O PIN

# PIC16C5X

| COMF                                                 | Complement f                                                                                                                                                          |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                              | [label] COMF f,d                                                                                                                                                      |

| Operands:                                            | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                            |

| Operation:                                           | $(\overline{f}) \rightarrow (dest)$                                                                                                                                   |

| Status Affected:                                     | Z                                                                                                                                                                     |

| Encoding:                                            | 0010 01df ffff                                                                                                                                                        |

| Description:                                         | The contents of register 'f' are<br>complemented. If 'd' is 0 the result<br>is stored in the W register. If 'd' is 1<br>the result is stored back in<br>register 'f'. |

| Words:                                               | 1                                                                                                                                                                     |

| Cycles:                                              | 1                                                                                                                                                                     |

| Example:                                             | COMF REG1,0                                                                                                                                                           |

| Before Instru<br>REG1<br>After Instruct<br>REG1<br>W | = 0x13                                                                                                                                                                |

| DECF                                                    | Decreme                                                                                                                                     | ent f   |      |  |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------|------|--|

| Syntax:                                                 | [ label ]                                                                                                                                   | DECF f, | d    |  |

| Operands:                                               | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                              |         |      |  |

| Operation:                                              | $(f) - 1 \rightarrow$                                                                                                                       | (dest)  |      |  |

| Status Affected:                                        | Z                                                                                                                                           |         |      |  |

| Encoding:                                               | 0000                                                                                                                                        | 11df    | ffff |  |

| Description:                                            | Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If<br>'d' is 1 the result is stored back in<br>register 'f'. |         |      |  |

| Words:                                                  | 1                                                                                                                                           |         |      |  |

| Cycles:                                                 | 1                                                                                                                                           |         |      |  |

| Example:                                                | DECF                                                                                                                                        | CNT,    | 1    |  |

| Before Instru<br>CNT<br>Z<br>After Instruct<br>CNT<br>Z | = 0<br>= 0<br>ion                                                                                                                           | <01     |      |  |

| DECFSZ                                               | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Syntax:                                              | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| Operands:                                            | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

| Operation:                                           | $(f) - 1 \rightarrow d;$ skip if result = 0                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| Status Affected:                                     | None                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| Encoding:                                            | 0010 11df ffff                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| Description:                                         | The contents of register 'f' are dec-<br>remented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'.<br>If the result is 0, the next instruc-<br>tion, which is already fetched, is<br>discarded and a NOP is executed<br>instead making it a two-cycle<br>instruction. |  |  |  |  |  |  |  |  |

| Words:                                               | 1                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

| Cycles:                                              | 1(2)                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| Example:                                             | HERE DECFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| Before Instru<br>PC                                  | = address (HERE)                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| After Instruc<br>CNT<br>if CNT<br>PC<br>if CNT<br>PC | tion<br>= CNT - 1;<br>= 0,<br>= address (CONTINUE);<br>≠ 0,<br>= address (HERE+1)                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

# 13.2 DC Characteristics: PIC16CR54A-04E, 10E, 20E (Extended)

| PIC16CR54A-04E, 10E, 20E<br>(Extended) |        |                                                                                       | Standard Operating Conditions (unless otherwise specified)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                   |                 |                |                                                                                      |  |

|----------------------------------------|--------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------|----------------|--------------------------------------------------------------------------------------|--|

| Param<br>No.                           | Symbol | Characteristic                                                                        | Min                                                                                                                                  | Тур†              | Max             | Units          | Conditions                                                                           |  |

| D001                                   | Vdd    | Supply Voltage<br>RC, XT and LP modes<br>HS mode                                      | 3.25<br>4.5                                                                                                                          |                   | 6.0<br>5.5      | V<br>V         |                                                                                      |  |

| D002                                   | Vdr    | RAM Data Retention Voltage <sup>(1)</sup>                                             | —                                                                                                                                    | 1.5*              | —               | V              | Device in SLEEP mode                                                                 |  |

| D003                                   | VPOR   | VDD Start Voltage to ensure<br>Power-on Reset                                         | —                                                                                                                                    | Vss               | —               | V              | See Section 5.1 for details on<br>Power-on Reset                                     |  |

| D004                                   | Svdd   | VDD Rise Rate to ensure Power-<br>on Reset                                            | 0.05*                                                                                                                                | _                 |                 | V/ms           | See Section 5.1 for details on<br>Power-on Reset                                     |  |

| D010                                   | IDD    | Supply Current <sup>(2)</sup><br>RC <sup>(3)</sup> and XT modes<br>HS mode<br>HS mode |                                                                                                                                      | 1.8<br>4.8<br>9.0 | 3.3<br>10<br>20 | mA<br>mA<br>mA | Fosc = 4.0 MHz, Vdd = 5.5V<br>Fosc = 10 MHz, Vdd = 5.5V<br>Fosc = 16 MHz, Vdd = 5.5V |  |

| D020                                   | IPD    | Power-down Current <sup>(2)</sup>                                                     |                                                                                                                                      | 5.0<br>0.8        | 22<br>18        | μΑ<br>μΑ       | VDD = 3.25V, WDT enabled<br>VDD = 3.25V, WDT disabled                                |  |

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, TOCKI = VDD, MCLR = VDD; WDT enabled/ disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- 3: Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in kΩ.

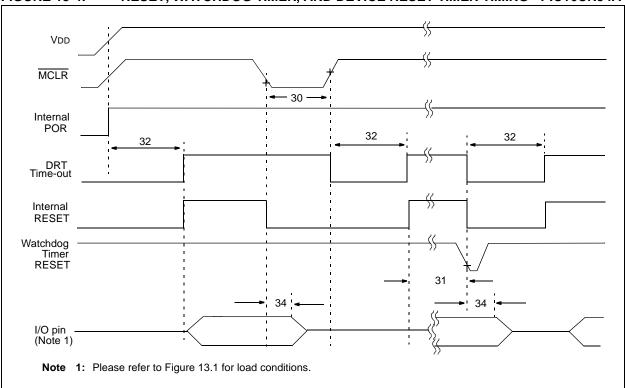

# FIGURE 13-4: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING - PIC16CR54A

# TABLE 13-3: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER - PIC16CR54A

| AC CharacteristicsStandard Operating Conditions (unless otherwise specified)<br>Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |        |                                                  |      |     |      |            |                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------------|------|-----|------|------------|-------------------|

| Param<br>No.                                                                                                                                                                                                                                                               | Symbol | Characteristic Min Typ† Max Units Condi          |      |     |      | Conditions |                   |

| 30                                                                                                                                                                                                                                                                         | TmcL   | MCLR Pulse Width (low)                           | 1.0* |     |      | μS         | VDD = 5.0V        |

| 31                                                                                                                                                                                                                                                                         | Twdt   | Watchdog Timer Time-out Period<br>(No Prescaler) | 7.0* | 18* | 40*  | ms         | VDD = 5.0V (Comm) |

| 32                                                                                                                                                                                                                                                                         | Tdrt   | Device Reset Timer Period                        | 7.0* | 18* | 30*  | ms         | VDD = 5.0V (Comm) |

| 34                                                                                                                                                                                                                                                                         | Tioz   | I/O Hi-impedance from MCLR Low                   |      |     | 1.0* | μS         |                   |

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

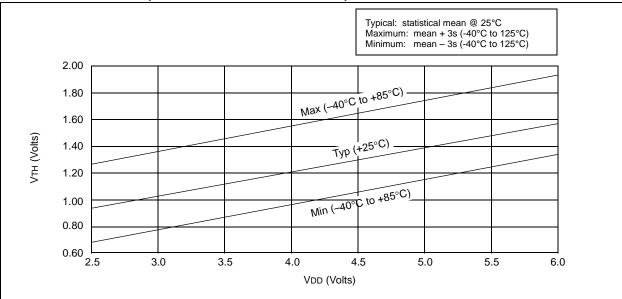

# FIGURE 14-9: VTH (INPUT THRESHOLD VOLTAGE) OF I/O PINS vs. VDD

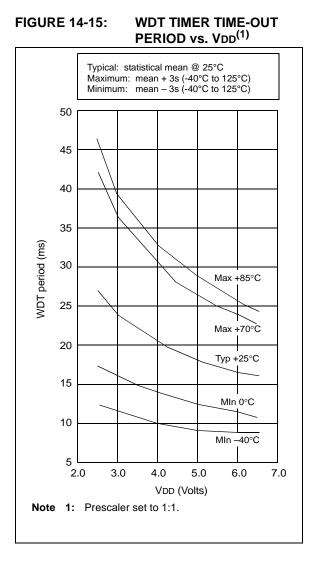

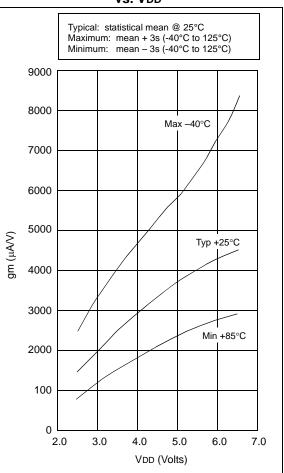

# FIGURE 14-16: TRANSCONDUCTANCE (gm) OF HS OSCILLATOR vs. VDD

# 15.1 DC Characteristics: PIC16C54A-04, 10, 20 (Commercial) PIC16C54A-04I, 10I, 20I (Industrial) PIC16LC54A-04 (Commercial) PIC16LC54A-04I (Industrial)

| PIC16LC54A-04<br>PIC16LC54A-04I<br>(Commercial, Industrial)                 |      |                                               |                                                                                                                                                                                           | Standard Operating Conditions (unless otherwise specified)Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |              |          |                                                                                                       |  |  |

|-----------------------------------------------------------------------------|------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------|-------------------------------------------------------------------------------------------------------|--|--|

| PIC16C54A-04, 10, 20<br>PIC16C54A-04I, 10I, 20I<br>(Commercial, Industrial) |      |                                               | Standard Operating Conditions (unless otherwise specified)Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                                                                                                                                                                                           |              |          |                                                                                                       |  |  |

| Param<br>No. Symbol Characteristic/Device                                   |      |                                               | Min                                                                                                                                                                                       | Тур†                                                                                                                                                                                      | Max          | Units    | Conditions                                                                                            |  |  |

|                                                                             | Vdd  | Supply Voltage                                |                                                                                                                                                                                           |                                                                                                                                                                                           | •            |          | ·                                                                                                     |  |  |

| D001                                                                        |      | PIC16LC54A                                    | 3.0<br>2.5                                                                                                                                                                                | _                                                                                                                                                                                         | 6.25<br>6.25 | V<br>V   | XT and RC modes<br>LP mode                                                                            |  |  |

| D001A                                                                       |      | PIC16C54A                                     | 3.0<br>4.5                                                                                                                                                                                | _                                                                                                                                                                                         | 6.25<br>5.5  | V<br>V   | RC, XT and LP modes<br>HS mode                                                                        |  |  |

| D002                                                                        | Vdr  | RAM Data Retention<br>Voltage <sup>(1)</sup>  | —                                                                                                                                                                                         | 1.5*                                                                                                                                                                                      | —            | V        | Device in SLEEP mode                                                                                  |  |  |

| D003                                                                        | VPOR | VDD Start Voltage to<br>ensure Power-on Reset | —                                                                                                                                                                                         | Vss                                                                                                                                                                                       | —            | V        | See Section 5.1 for details on<br>Power-on Reset                                                      |  |  |

| D004                                                                        | SVDD | VDD Rise Rate to ensure<br>Power-on Reset     | 0.05*                                                                                                                                                                                     | —                                                                                                                                                                                         | —            | V/ms     | See Section 5.1 for details on<br>Power-on Reset                                                      |  |  |

|                                                                             | IDD  | Supply Current <sup>(2)</sup>                 |                                                                                                                                                                                           |                                                                                                                                                                                           |              |          |                                                                                                       |  |  |

| D005                                                                        |      | PIC16LC5X                                     | —                                                                                                                                                                                         | 0.5                                                                                                                                                                                       | 2.5          | mA       | Fosc = 4.0 MHz, VDD = 5.5V,<br>RC <sup>(3)</sup> and XT modes                                         |  |  |

|                                                                             |      |                                               | —                                                                                                                                                                                         | 11                                                                                                                                                                                        | 27           | μA       | Fosc = 32 kHz, VDD = 2.5V,<br>WDT disabled, LP mode, Commercial                                       |  |  |

|                                                                             |      |                                               | —                                                                                                                                                                                         | 11                                                                                                                                                                                        | 35           | μA       | Fosc = 32 kHz, VDD = 2.5V,<br>WDT disabled, LP mode, Industrial                                       |  |  |

| D005A                                                                       |      | PIC16C5X                                      | —                                                                                                                                                                                         | 1.8                                                                                                                                                                                       | 2.4          | mA       | Fosc = 4.0 MHz, VDD = 5.5V,<br>RC <sup>(3)</sup> and XT modes                                         |  |  |

|                                                                             |      |                                               | —                                                                                                                                                                                         | 2.4                                                                                                                                                                                       | 8.0          | mA       | Fosc = 10 MHz, VDD = 5.5V, HS mode                                                                    |  |  |

|                                                                             |      |                                               | _                                                                                                                                                                                         | 4.5<br>14                                                                                                                                                                                 | 16<br>29     | mA<br>μA | Fosc = 20 MHz, VDD = 5.5V, HS mode<br>Fosc = 32 kHz, VDD = 3.0V,<br>WDT disabled, LP mode, Commercial |  |  |

|                                                                             |      |                                               | —                                                                                                                                                                                         | 17                                                                                                                                                                                        | 37           | μA       | Fosc = $32 \text{ kHz}$ , VDD = $3.0 \text{V}$ ,<br>WDT disabled, LP mode, Industrial                 |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

These parameters are characterized but not tested.

- † Data in "Typ" column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- **Note 1:** This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/ disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- 3: Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in k $\Omega$ .

NOTES:

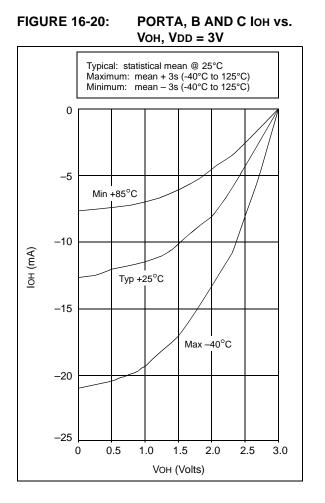

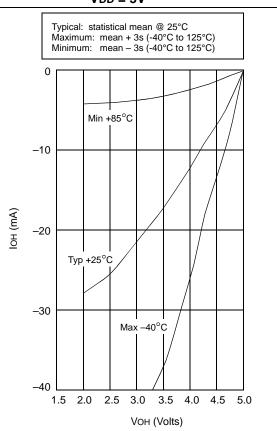

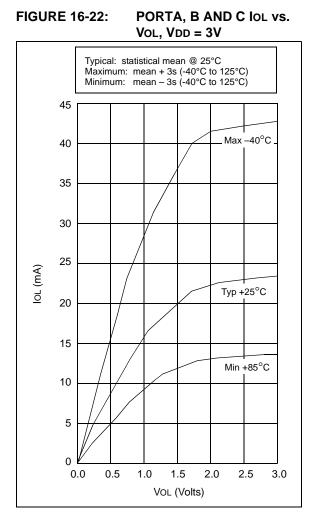

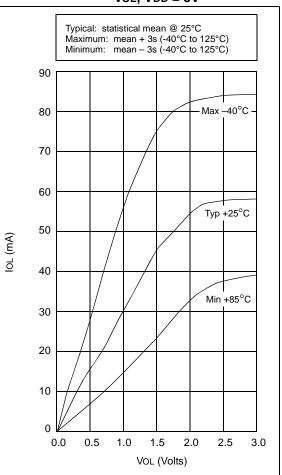

FIGURE 16-21: PORTA, B AND C IOH vs. VOH, VDD = 5V

TABLE 16-2:INPUT CAPACITANCE FOR<br/>PIC16C54A/C58A

| Pin         | Typical Capacitance (pF) |          |  |  |  |  |

|-------------|--------------------------|----------|--|--|--|--|

| FIII        | 18L PDIP                 | 18L SOIC |  |  |  |  |

| RA port     | 5.0                      | 4.3      |  |  |  |  |

| RB port     | 5.0                      | 4.3      |  |  |  |  |

| MCLR        | 17.0                     | 17.0     |  |  |  |  |

| OSC1        | 4.0                      | 3.5      |  |  |  |  |

| OSC2/CLKOUT | 4.3                      | 3.5      |  |  |  |  |

| TOCKI       | 3.2                      | 2.8      |  |  |  |  |

All capacitance values are typical at 25°C. A part-to-part variation of  $\pm 25\%$  (three standard deviations) should be taken into account.

# FIGURE 16-23: PORTA, B AND C IOL vs. VOL, VDD = 5V

# 19.1 DC Characteristics:PIC16C54C/C55A/C56A/C57C/C58B-40 (Commercial)<sup>(1)</sup>

| PIC16C54C/C55A/C56A/C57C/C58B-40<br>(Commercial) |        |                                               |       |                    |            | tions (unless otherwise specified) $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial |                                                                                |

|--------------------------------------------------|--------|-----------------------------------------------|-------|--------------------|------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Param<br>No.                                     | Symbol | Characteristic                                | Min   | Min Typ† Max Units |            | Units                                                                                  | Conditions                                                                     |

| D001                                             | Vdd    | Supply Voltage                                | 4.5   | -                  | 5.5        | V                                                                                      | HS mode from 20 - 40 MHz                                                       |

| D002                                             | Vdr    | RAM Data Retention Voltage <sup>(2)</sup>     |       | 1.5*               | —          | V                                                                                      | Device in SLEEP mode                                                           |

| D003                                             | VPOR   | VDD Start Voltage to ensure<br>Power-on Reset | —     | Vss                | —          | V                                                                                      | See Section 5.1 for details on<br>Power-on Reset                               |

| D004                                             | SVDD   | VDD Rise Rate to ensure Power-<br>on Reset    | 0.05* | _                  | —          | V/ms                                                                                   | See Section 5.1 for details on<br>Power-on Reset                               |

| D010                                             | Idd    | Supply Current <sup>(3)</sup>                 | _     | 5.2<br>6.8         | 12.3<br>16 | mA<br>mA                                                                               | Fosc = 40 MHz, VDD = $4.5V$ , HS mode<br>Fosc = 40 MHz, VDD = $5.5V$ , HS mode |

| D020                                             | IPD    | Power-down Current <sup>(3)</sup>             | _     | 1.8<br>9.8         | 7.0<br>27* | μΑ<br>μΑ                                                                               | VDD = 5.5V, WDT disabled, Commercial<br>VDD = 5.5V, WDT enabled, Commercial    |

\* These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- **Note 1:** Device operation between 20 MHz to 40 MHz requires the following: VDD between 4.5V to 5.5V, OSC1 pin externally driven, OSC2 pin not connected, HS oscillator mode and commercial temperatures. For operation between DC and 20 MHz, See Section 19.1.

- **2:** This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- **3:** The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

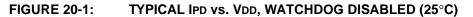

# 20.0 DEVICE CHARACTERIZATION - PIC16LC54C 40MHz

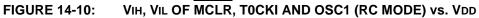

The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

© 1997-2013 Microchip Technology Inc.

# Worldwide Sales and Service

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

# ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney Tel: 61-2-9868-6733

Fax: 61-2-9868-6755 China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

# ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828 Fax: 886-7-330-9305

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

# EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Fax: 45-4485-2829

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

11/29/12