#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | POR, WDT                                                                     |

| Number of I/O              | 20                                                                           |

| Program Memory Size        | 3KB (2K x 12)                                                                |

| Program Memory Type        | OTP                                                                          |

| EEPROM Size                |                                                                              |

| RAM Size                   | 72 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            | -                                                                            |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 28-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc57ct-04i-ss |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

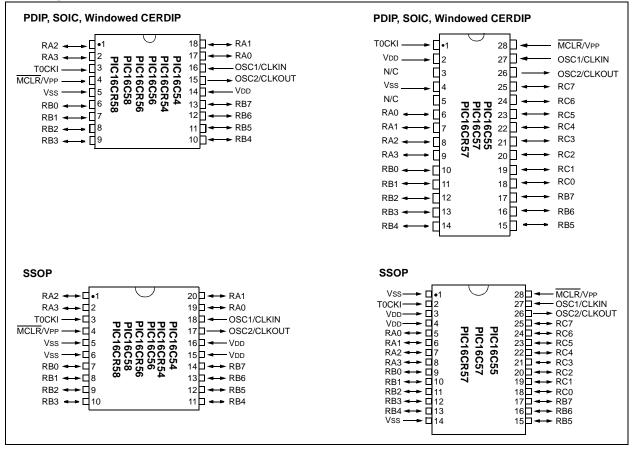

## **Pin Diagrams**

## **Device Differences**

| Device     | Voltage<br>Range | Oscillator<br>Selection<br>(Program) | Oscillator | Process<br>Technology<br>(Microns) | ROM<br>Equivalent | MCLR<br>Filter |

|------------|------------------|--------------------------------------|------------|------------------------------------|-------------------|----------------|

| PIC16C54   | 2.5-6.25         | Factory                              | See Note 1 | 1.2                                | PIC16CR54A        | No             |

| PIC16C54A  | 2.0-6.25         | User                                 | See Note 1 | 0.9                                | —                 | No             |

| PIC16C54C  | 2.5-5.5          | User                                 | See Note 1 | 0.7                                | PIC16CR54C        | Yes            |

| PIC16C55   | 2.5-6.25         | Factory                              | See Note 1 | 1.7                                | —                 | No             |

| PIC16C55A  | 2.5-5.5          | User                                 | See Note 1 | 0.7                                | —                 | Yes            |

| PIC16C56   | 2.5-6.25         | Factory                              | See Note 1 | 1.7                                | —                 | No             |

| PIC16C56A  | 2.5-5.5          | User                                 | See Note 1 | 0.7                                | PIC16CR56A        | Yes            |

| PIC16C57   | 2.5-6.25         | Factory                              | See Note 1 | 1.2                                | —                 | No             |

| PIC16C57C  | 2.5-5.5          | User                                 | See Note 1 | 0.7                                | PIC16CR57C        | Yes            |

| PIC16C58B  | 2.5-5.5          | User                                 | See Note 1 | 0.7                                | PIC16CR58B        | Yes            |

| PIC16CR54A | 2.5-6.25         | Factory                              | See Note 1 | 1.2                                | N/A               | Yes            |

| PIC16CR54C | 2.5-5.5          | Factory                              | See Note 1 | 0.7                                | N/A               | Yes            |

| PIC16CR56A | 2.5-5.5          | Factory                              | See Note 1 | 0.7                                | N/A               | Yes            |

| PIC16CR57C | 2.5-5.5          | Factory                              | See Note 1 | 0.7                                | N/A               | Yes            |

| PIC16CR58B | 2.5-5.5          | Factory                              | See Note 1 | 0.7                                | N/A               | Yes            |

Note 1: If you change from this device to another device, please verify oscillator characteristics in your application.

**Note:** The table shown above shows the generic names of the PIC16C5X devices. For device varieties, please refer to Section 2.0.

NOTES:

NOTES:

## 5.1 Power-On Reset (POR)

The PIC16C5X family incorporates on-chip Power-On Reset (POR) circuitry which provides an internal chip RESET for most power-up situations. To use this feature, the user merely ties the MCLR/VPP pin to VDD. A simplified block diagram of the on-chip Power-On Reset circuit is shown in Figure 5-1.

The Power-On Reset circuit and the Device Reset Timer (Section 5.2) circuit are closely related. On power-up, the RESET latch is set and the DRT is <u>RESET</u>. The DRT timer begins counting once it detects MCLR to be high. After the time-out period, which is typically 18 ms, it will RESET the reset latch and thus end the on-chip RESET signal.

A power-up example where MCLR is not tied to VDD is shown in Figure 5-3. VDD is allowed to rise and stabilize before bringing MCLR high. The chip will actually come out of reset TDRT msec after MCLR goes high.

In Figure 5-4, the on-chip Power-On Reset feature is being used (MCLR and VDD are tied together). The VDD is stable before the start-up timer times out and there is no problem in getting a proper RESET. However, Figure 5-5 depicts a problem situation where VDD rises too slowly. The time between when the DRT senses a high on the MCLR/VPP pin, and when the MCLR/VPP pin (and VDD) actually reach their full value, is too long. In this situation, when the start-up timer times out, VDD has not reached the VDD (min) value and the chip is, therefore, not guaranteed to function correctly. For such situations, we recommend that external RC circuits be used to achieve longer POR delay times (Figure 5-2).

Note: When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met.

For more information on PIC16C5X POR, see *Power-Up Considerations* - AN522 in the <u>Embedded Control Handbook</u>.

The POR circuit does not produce an internal RESET when VDD declines.

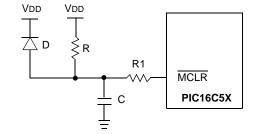

#### FIGURE 5-2:

### EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- External Power-On Reset circuit is required only if VDD power-up is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- R < 40 kΩ is recommended to make sure that voltage drop across R does not violate the device electrical specification.

- R1 =  $100\Omega$  to 1 k $\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C in the event of  $\overline{MCLR}$  pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

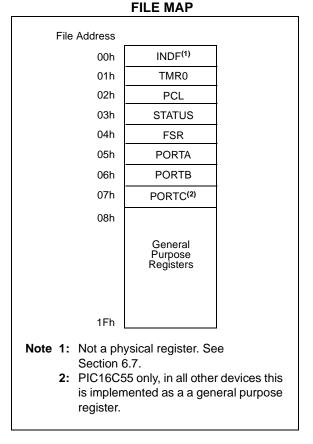

## 6.2 Data Memory Organization

Data memory is composed of registers, or bytes of RAM. Therefore, data memory for a device is specified by its register file. The register file is divided into two functional groups: Special Function Registers and General Purpose Registers.

The Special Function Registers include the TMR0 register, the Program Counter (PC), the Status Register, the I/O registers (ports) and the File Select Register (FSR). In addition, Special Purpose Registers are used to control the I/O port configuration and prescaler options.

The General Purpose Registers are used for data and control information under command of the instructions.

For the PIC16C54, PIC16CR54, PIC16C56 and PIC16CR56, the register file is composed of 7 Special Function Registers and 25 General Purpose Registers (Figure 6-4).

For the PIC16C55, the register file is composed of 8 Special Function Registers and 24 General Purpose Registers.

For the PIC16C57 and PIC16CR57, the register file is composed of 8 Special Function Registers, 24 General Purpose Registers and up to 48 additional General Purpose Registers that may be addressed using a banking scheme (Figure 6-5).

For the PIC16C58 and PIC16CR58, the register file is composed of 7 Special Function Registers, 25 General Purpose Registers and up to 48 additional General Purpose Registers that may be addressed using a banking scheme (Figure 6-6).

## 6.2.1 GENERAL PURPOSE REGISTER FILE

The register file is accessed either directly or indirectly through the File Select Register (FSR). The FSR Register is described in Section 6.7.

## FIGURE 6-4: PIC16C54, PIC16CR54, PIC16C55, PIC16C56, PIC16CR56 REGISTER

## 6.3 STATUS Register

This register contains the arithmetic status of the ALU, the RESET status and the page preselect bits for program memories larger than 512 words.

The STATUS Register can be the destination for any instruction, as with any other register. If the STATUS Register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not

writable. Therefore, the result of an instruction with the STATUS Register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS Register as  $000u \ u1uu$  (where u = unchanged).

It is recommended, therefore, that only BCF, BSF and MOVWF instructions be used to alter the STATUS Register because these instructions do not affect the Z, DC or C bits from the STATUS Register. For other instructions which do affect STATUS Bits, see Section 10.0, Instruction Set Summary.

## REGISTER 6-1: STATUS REGISTER (ADDRESS: 03h)

|          | R/W-0                                                                                                                                       | R/W-0                                                                                                                             | R/W-0    | R-1          | R-1                        | R/W-x       | R/W-x | R/W-x          |  |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------|--------------|----------------------------|-------------|-------|----------------|--|--|--|--|

|          | PA2                                                                                                                                         | PA1                                                                                                                               | PA0      | TO           | PD                         | Z           | DC    | С              |  |  |  |  |

|          | bit 7                                                                                                                                       |                                                                                                                                   |          |              |                            |             |       | bit 0          |  |  |  |  |

| bit 7:   | PA2: This bit                                                                                                                               | unused at th                                                                                                                      | is time. |              |                            |             |       |                |  |  |  |  |

|          | Use of the PA2 bit as a general purpose read/write bit is not recommended, since this may affect upward compatibility with future products. |                                                                                                                                   |          |              |                            |             |       |                |  |  |  |  |

| bit 6-5: |                                                                                                                                             |                                                                                                                                   |          | -            | CR56)(PIC16                |             |       | 58)            |  |  |  |  |

|          |                                                                                                                                             |                                                                                                                                   |          |              | 16C57/CR57,<br>16C57/CR57, |             |       |                |  |  |  |  |

|          |                                                                                                                                             |                                                                                                                                   |          |              |                            | FIC 10C30/C | N00   |                |  |  |  |  |

|          | 10 = Page 2 (400h - 5FFh) - PIC16C57/CR57, PIC16C58/CR58<br>11 = Page 3 (600h - 7FFh) - PIC16C57/CR57, PIC16C58/CR58                        |                                                                                                                                   |          |              |                            |             |       |                |  |  |  |  |

|          |                                                                                                                                             | Each page is 512 words.<br>Using the PA<1:0> bits as general purpose read/write bits in devices which do not use them for program |          |              |                            |             |       |                |  |  |  |  |

|          |                                                                                                                                             |                                                                                                                                   |          |              | affect upward              |             |       |                |  |  |  |  |

| bit 4:   | TO: Time-ou                                                                                                                                 |                                                                                                                                   |          | ,            | •                          |             |       |                |  |  |  |  |

|          |                                                                                                                                             | ver-up, CLRWI<br>ime-out occur                                                                                                    |          | , or sleep i | nstruction                 |             |       |                |  |  |  |  |

| bit 3:   | PD: Power-d                                                                                                                                 | lown bit                                                                                                                          |          |              |                            |             |       |                |  |  |  |  |

|          | •                                                                                                                                           | ver-up or by tl<br>ution of the SI                                                                                                |          |              |                            |             |       |                |  |  |  |  |

| bit 2:   | Z: Zero bit                                                                                                                                 |                                                                                                                                   |          |              |                            |             |       |                |  |  |  |  |

|          |                                                                                                                                             | lt of an arithm<br>It of an arithm                                                                                                |          |              |                            |             |       |                |  |  |  |  |

| bit 1:   | DC: Digit carry/borrow bit (for ADDWF and SUBWF instructions)                                                                               |                                                                                                                                   |          |              |                            |             |       |                |  |  |  |  |

|          | ADDWF                                                                                                                                       |                                                                                                                                   |          |              |                            |             |       |                |  |  |  |  |

|          | 1 = A carry from the 4th low order bit of the result occurred                                                                               |                                                                                                                                   |          |              |                            |             |       |                |  |  |  |  |

|          | <ul> <li>0 = A carry from the 4th low order bit of the result did not occur</li> <li>SUBWF</li> </ul>                                       |                                                                                                                                   |          |              |                            |             |       |                |  |  |  |  |

|          | 1 = A borrow from the 4th low order bit of the result did not occur                                                                         |                                                                                                                                   |          |              |                            |             |       |                |  |  |  |  |

|          | 0 = A borrow from the 4th low order bit of the result occurred                                                                              |                                                                                                                                   |          |              |                            |             |       |                |  |  |  |  |

| bit 0:   | •                                                                                                                                           | row bit (for AI                                                                                                                   |          |              | F instructions             |             | _     |                |  |  |  |  |

|          | <b>ADDWF</b><br>1 = A carry o                                                                                                               | ocurred                                                                                                                           |          | orrow did n  | ot occur                   | RRF or RLI  |       | , respectively |  |  |  |  |

|          | $\pm = \pi \operatorname{carry} 0$                                                                                                          | locurrou                                                                                                                          | / · ·    |              |                            |             |       |                |  |  |  |  |

| Legena:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | 1 = bit is set   | 0 = bit is cleared        | x = bit is unknown |

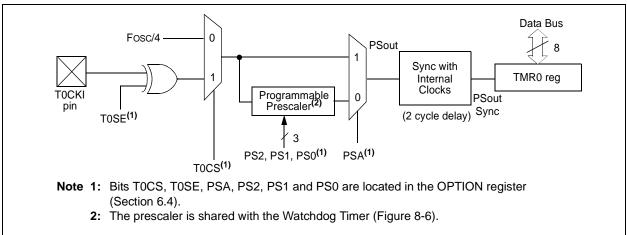

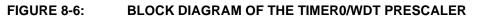

# 8.0 TIMER0 MODULE AND TMR0 REGISTER

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Edge select for external clock

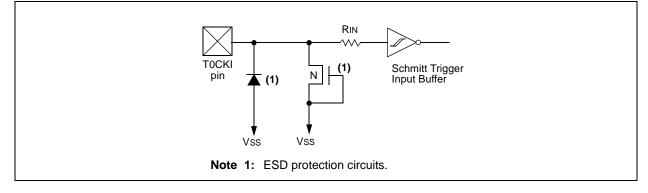

Figure 8-1 is a simplified block diagram of the Timer0 module, while Figure 8-2 shows the electrical structure of the Timer0 input.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two cycles (Figure 8-3 and Figure 8-4). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the T0CS bit (OPTION<5>). In this mode, Timer0 will increment either on every rising or falling edge of pin T0CKI. The incrementing edge is determined by the source edge select bit T0SE (OPTION<4>). Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 8.1.

Note: The prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both.

The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4,..., 1:256 are selectable. Section 8.2 details the operation of the prescaler.

A summary of registers associated with the Timer0 module is found in Table 8-1.

## FIGURE 8-2: ELECTRICAL STRUCTURE OF TOCKI PIN

#### CONFIGURATION WORD FOR PIC16C54/C55/C56/C57 **REGISTER 9-2:**

|           |            |             | İ            |            |                     |             | İ         | СР      | WDTE        | FOSC1      | FOSC0   |

|-----------|------------|-------------|--------------|------------|---------------------|-------------|-----------|---------|-------------|------------|---------|

|           |            | _           | _            | _          |                     |             |           | CP      | WDIE        | FUSCI      |         |

| bit 11    |            |             |              |            |                     |             |           |         |             |            | bit 0   |

|           |            |             |              |            |                     |             |           |         |             |            |         |

| bit 11-4: | Unimple    | mented      | Read as '    | 0'         |                     |             |           |         |             |            |         |

| bit 3:    | CP: Cod    | e protecti  | on bit.      |            |                     |             |           |         |             |            |         |

|           |            | e protecti  |              |            |                     |             |           |         |             |            |         |

|           | 0 = Code   | e protectio | on on        |            |                     |             |           |         |             |            |         |

| bit 2:    | WDTE: \    | Vatchdog    | timer ena    | ble bit    |                     |             |           |         |             |            |         |

|           | 1 = WDT    | enabled     |              |            |                     |             |           |         |             |            |         |

|           | 0 = WDT    | disabled    |              |            |                     |             |           |         |             |            |         |

| bit 1-0:  | FOSC1:I    | FOSC0: (    | Oscillator s | election b | oits <sup>(2)</sup> |             |           |         |             |            |         |

|           | 00 = LF    | oscillato   | or           |            |                     |             |           |         |             |            |         |

|           | 01 = X     | T oscillato | or           |            |                     |             |           |         |             |            |         |

|           |            | S oscillato |              |            |                     |             |           |         |             |            |         |

|           | 11 = R     | C oscillate | or           |            |                     |             |           |         |             |            |         |

| Note 1.   | Refer to t | ha PIC16    | C5X Prog     | rammina    | Specificat          | ions (Liter | atura Num | her DS3 | 190) to d   | otormino l | now to  |

|           |            |             | iration wor  | 0          | opeemear            |             |           |         | , 100) to u |            | 1011 10 |

| 2:        |            | •           | orts XT, R   |            | oscillator          | onlv.       |           |         |             |            |         |

|           |            |             |              |            |                     | - 1         |           |         |             |            |         |

| Legend:   |            |             |              |            |                     |             |           |         |             |            |         |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | 1 = bit is set   | 0 = bit is cleared        | x = bit is unknown |

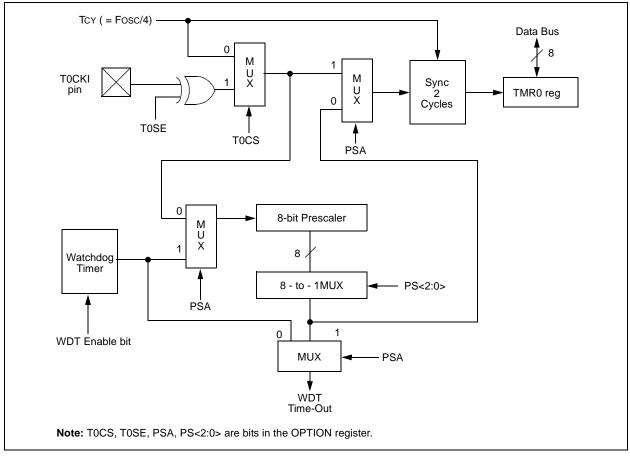

# 9.2 Watchdog Timer (WDT)

The Watchdog Timer (WDT) is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins have been stopped, for example, by execution of a SLEEP instruction. During normal operation or SLEEP, a WDT Reset or Wake-up Reset generates a device RESET.

The  $\overline{\text{TO}}$  bit (STATUS<4>) will be cleared upon a Watchdog Timer Reset (Section 6.3).

The WDT can be permanently disabled by programming the configuration bit WDTE as a '0' (Section 9.1). Refer to the PIC16C5X Programming Specifications (Literature Number DS30190) to determine how to access the configuration word.

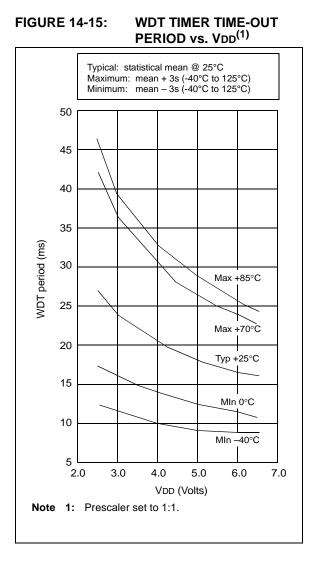

## 9.2.1 WDT PERIOD

An 8-bit counter is available as a prescaler for the Timer0 module (Section 8.2), or as a postscaler for the Watchdog Timer (WDT), respectively. For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that the prescaler may be used by either the Timer0 module or the WDT, but not

both. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the WDT, and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine prescaler assignment and prescale ratio (Section 6.4).

The WDT has a nominal time-out period of 18 ms (with no prescaler). If a longer time-out period is desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT (under software control) by writing to the OPTION register. Thus, time-out a period of a nominal 2.3 seconds can be realized. These periods vary with temperature, VDD and part-to-part process variations (see Device Characterization).

Under worst case conditions (VDD = Min., Temperature = Max., WDT prescaler = 1:128), it may take several seconds before a WDT time-out occurs.

## 9.2.2 WDT PROGRAMMING CONSIDERATIONS

The CLRWDT instruction clears the WDT and the prescaler, if assigned to the WDT, and prevents it from timing out and generating a device RESET.

The SLEEP instruction RESETS the WDT and the prescaler, if assigned to the WDT. This gives the maximum SLEEP time before a WDT Wake-up Reset.

## TABLE 9-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE WATCHDOG TIMER

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | <u>Value</u> on<br>MCLR and<br>WDT Reset |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------------------|------------------------------------------|

| N/A     | OPTION | —     |       | Tosc  | Tose  | PSA   | PS2   | PS1   | PS0   | 11 1111                       | 11 1111                                  |

Legend: u = unchanged, - = unimplemented, read as '0'. Shaded cells not used by Watchdog Timer.

# 11.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK™ Object Linker/

- MPLIB<sup>™</sup> Object Librarian

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- ICEPIC<sup>™</sup> In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD

- Device Programmers

- PRO MATE<sup>®</sup> II Universal Device Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Development Programmer

- Low Cost Demonstration Boards

- PICDEM<sup>™</sup>1 Demonstration Board

- PICDEM 2 Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 17 Demonstration Board

- KEELOQ<sup>®</sup> Demonstration Board

## 11.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup>-based application that contains:

- An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- A full-featured editor

- A project manager

- Customizable toolbar and key mapping

- A status bar

- On-line help

The MPLAB IDE allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- machine code

The ability to use MPLAB IDE with multiple debugging tools allows users to easily switch from the cost-effective simulator to a full-featured emulator with minimal retraining.

# 11.2 MPASM Assembler

The MPASM assembler is a full-featured universal macro assembler for all PIC MCUs.

The MPASM assembler has a command line interface and a Windows shell. It can be used as a stand-alone application on a Windows 3.x or greater system, or it can be used through MPLAB IDE. The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file that contains source lines and generated machine code, and a COD file for debugging.

The MPASM assembler features include:

- Integration into MPLAB IDE projects.

- User-defined macros to streamline assembly code.

- Conditional assembly for multi-purpose source files.

- Directives that allow complete control over the assembly process.

# 11.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI 'C' compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

## 13.2 DC Characteristics: PIC16CR54A-04E, 10E, 20E (Extended)

| PIC16CR54A-04E, 10E, 20E<br>(Extended) |        |                                                                                       | Standard Operating Conditions (unless otherwise specifiedOperating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                   |                 |                |                                                                                      |  |

|----------------------------------------|--------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------|----------------|--------------------------------------------------------------------------------------|--|

| Param<br>No.                           | Symbol | Characteristic                                                                        | Min                                                                                                                                 | Тур†              | Max             | Units          | Conditions                                                                           |  |

| D001                                   | Vdd    | Supply Voltage<br>RC, XT and LP modes<br>HS mode                                      | 3.25<br>4.5                                                                                                                         |                   | 6.0<br>5.5      | V<br>V         |                                                                                      |  |

| D002                                   | Vdr    | RAM Data Retention Voltage <sup>(1)</sup>                                             | —                                                                                                                                   | 1.5*              | —               | V              | Device in SLEEP mode                                                                 |  |

| D003                                   | VPOR   | VDD Start Voltage to ensure<br>Power-on Reset                                         | —                                                                                                                                   | Vss               | —               | V              | See Section 5.1 for details on<br>Power-on Reset                                     |  |

| D004                                   | Svdd   | VDD Rise Rate to ensure Power-<br>on Reset                                            | 0.05*                                                                                                                               | _                 |                 | V/ms           | See Section 5.1 for details on<br>Power-on Reset                                     |  |

| D010                                   | IDD    | Supply Current <sup>(2)</sup><br>RC <sup>(3)</sup> and XT modes<br>HS mode<br>HS mode |                                                                                                                                     | 1.8<br>4.8<br>9.0 | 3.3<br>10<br>20 | mA<br>mA<br>mA | Fosc = 4.0 MHz, Vdd = 5.5V<br>Fosc = 10 MHz, Vdd = 5.5V<br>Fosc = 16 MHz, Vdd = 5.5V |  |

| D020                                   | IPD    | Power-down Current <sup>(2)</sup>                                                     |                                                                                                                                     | 5.0<br>0.8        | 22<br>18        | μΑ<br>μΑ       | VDD = 3.25V, WDT enabled<br>VDD = 3.25V, WDT disabled                                |  |

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, TOCKI = VDD, MCLR = VDD; WDT enabled/ disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- 3: Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in kΩ.

| AC Characteristics  |            | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |        |        |       |                  |  |  |

|---------------------|------------|------------------------------------------------------|------|--------|--------|-------|------------------|--|--|

| Param<br>No. Symbol |            | Characteristic                                       | Min  | Тур†   | Max    | Units | Conditions       |  |  |

| 1                   | Tosc       | External CLKIN Period <sup>(1)</sup>                 | 250  |        | —      | ns    | XT osc mode      |  |  |

|                     |            |                                                      | 250  | —      | —      | ns    | HS osc mode (04) |  |  |

|                     |            |                                                      | 100  | —      | —      | ns    | HS osc mode (10) |  |  |

|                     |            |                                                      | 50   | —      | —      | ns    | HS osc mode (20) |  |  |

|                     |            |                                                      | 5.0  | —      | —      | μS    | LP OSC mode      |  |  |

|                     |            | Oscillator Period <sup>(1)</sup>                     | 250  | _      | —      | ns    | RC osc mode      |  |  |

|                     |            |                                                      | 250  | —      | 10,000 | ns    | XT OSC mode      |  |  |

|                     |            |                                                      | 250  | —      | 250    | ns    | HS osc mode (04) |  |  |

|                     |            |                                                      | 100  | —      | 250    | ns    | HS osc mode (10) |  |  |

|                     |            |                                                      | 50   | —      | 250    | ns    | HS osc mode (20) |  |  |

|                     |            |                                                      | 5.0  | —      | 200    | μS    | LP OSC mode      |  |  |

| 2                   | Тсу        | Instruction Cycle Time <sup>(2)</sup>                | —    | 4/Fosc | —      | _     |                  |  |  |

| 3                   | TosL, TosH | Clock in (OSC1) Low or High                          | 50*  | _      | —      | ns    | XT oscillator    |  |  |

|                     |            | Time                                                 | 20*  | —      | —      | ns    | HS oscillator    |  |  |

|                     |            |                                                      | 2.0* | —      | —      | μS    | LP oscillator    |  |  |

| 4                   | TosR, TosF | Clock in (OSC1) Rise or Fall                         | —    |        | 25*    | ns    | XT oscillator    |  |  |

|                     |            | Time                                                 | —    | —      | 25*    | ns    | HS oscillator    |  |  |

|                     |            |                                                      | _    | —      | 50*    | ns    | LP oscillator    |  |  |

| TABLE 13-1: | EXTERNAL CLOCK TIMING REQUIREMENTS - PIC16CR54A |

|-------------|-------------------------------------------------|

|-------------|-------------------------------------------------|

These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

Note 1: All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

2: Instruction cycle period (TCY) equals four times the input oscillator time base period.

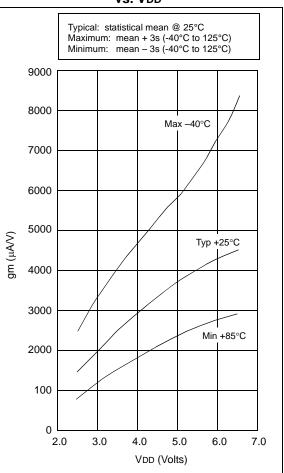

## FIGURE 14-16: TRANSCONDUCTANCE (gm) OF HS OSCILLATOR vs. VDD

## 15.2 DC Characteristics: PIC16C54A-04E, 10E, 20E (Extended) PIC16LC54A-04E (Extended)

|                   |                                       | FICTULCJ                                      | -7 0-      |                                                                                                                                     | cnac         | ч)     |                                                                                         |  |

|-------------------|---------------------------------------|-----------------------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------|--------|-----------------------------------------------------------------------------------------|--|

| PIC16L<br>(Extend | <b>C54A-04E</b><br>ded)               | 1                                             |            | <b>ard Ope</b><br>ting Terr                                                                                                         |              |        | tions (unless otherwise specified) $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |  |

|                   | PIC16C54A-04E, 10E, 20E<br>(Extended) |                                               |            | Standard Operating Conditions (unless otherwise specifiedOperating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |              |        |                                                                                         |  |

| Param<br>No.      | Symbol                                | Characteristic Min Typ† Max Units Conditions  |            |                                                                                                                                     |              |        |                                                                                         |  |

|                   | Vdd                                   | Supply Voltage                                |            |                                                                                                                                     | •            |        |                                                                                         |  |

| D001              |                                       | PIC16LC54A                                    | 3.0<br>2.5 | _                                                                                                                                   | 6.25<br>6.25 | V<br>V | XT and RC modes<br>LP mode                                                              |  |

| D001A             |                                       | PIC16C54A                                     | 3.5<br>4.5 |                                                                                                                                     | 5.5<br>5.5   | V<br>V | RC and XT modes<br>HS mode                                                              |  |

| D002              | Vdr                                   | RAM Data Retention Voltage <sup>(1)</sup>     | —          | 1.5*                                                                                                                                | -            | V      | Device in SLEEP mode                                                                    |  |

| D003              | VPOR                                  | VDD Start Voltage to ensure<br>Power-on Reset | —          | Vss                                                                                                                                 | -            | V      | See Section 5.1 for details on<br>Power-on Reset                                        |  |

| D004              | Svdd                                  | VDD Rise Rate to ensure<br>Power-on Reset     | 0.05*      | _                                                                                                                                   | _            | V/ms   | See Section 5.1 for details on<br>Power-on Reset                                        |  |

|                   | IDD                                   | Supply Current <sup>(2)</sup>                 |            |                                                                                                                                     |              |        |                                                                                         |  |

| D010              |                                       | PIC16LC54A                                    | —          | 0.5                                                                                                                                 | 25           | mA     | Fosc = 4.0 MHz, VDD = 5.5V,<br>RC <sup>(3)</sup> and XT modes                           |  |

|                   |                                       |                                               | —          | 11                                                                                                                                  | 27           | μA     | Fosc = 32 kHz, VDD = 2.5V,<br>LP mode, Commercial                                       |  |

|                   |                                       |                                               | —          | 11                                                                                                                                  | 35           | μA     | Fosc = 32 kHz, VDD = 2.5V,<br>LP mode, Industrial                                       |  |

|                   |                                       |                                               | _          | 11                                                                                                                                  | 37           | μA     | Fosc = 32 kHz, VDD = 2.5V,<br>LP mode, Extended                                         |  |

| D010A             |                                       | PIC16C54A                                     | —          | 1.8                                                                                                                                 | 3.3          | mA     | Fosc = 4.0 MHz, VDD = 5.5V, $RC^{(3)}$ and XT modes                                     |  |

|                   |                                       |                                               | —          | 4.8                                                                                                                                 | 10           | mA     | Fosc = 10 MHz, VDD = 5.5V,<br>HS mode                                                   |  |

|                   |                                       |                                               | —          | 9.0                                                                                                                                 | 20           | mA     | Fosc = 20 MHz, VDD = 5.5V,<br>HS mode                                                   |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

- \* These parameters are characterized but not tested.

- † Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, TOCKI = VDD, MCLR = VDD; WDT enabled/ disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- **3:** Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in kΩ.

## 15.3 DC Characteristics: PIC16LV54A-02 (Commercial) PIC16LV54A-02I (Industrial)

| PIC16LV54A-02<br>PIC16LV54A-02I<br>(Commercial, Industrial) |        |                                                                                                                     |       | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                        |                      |                                                                                                                |  |  |  |

|-------------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------|-------|------------------------------------------------------|------------------------|----------------------|----------------------------------------------------------------------------------------------------------------|--|--|--|

| Param<br>No.                                                | Symbol | Characteristic                                                                                                      | Min   | Тур†                                                 | Max                    | Units                | s Conditions                                                                                                   |  |  |  |

| D001                                                        | Vdd    | Supply Voltage<br>RC and XT modes                                                                                   | 2.0   | _                                                    | 3.8                    | V                    |                                                                                                                |  |  |  |

| D002                                                        | Vdr    | RAM Data Retention<br>Voltage <sup>(1)</sup>                                                                        | —     | 1.5*                                                 | —                      | V                    | Device in SLEEP mode                                                                                           |  |  |  |

| D003                                                        | VPOR   | VDD Start Voltage to ensure<br>Power-on Reset                                                                       | —     | Vss                                                  | —                      | V                    | See Section 5.1 for details on<br>Power-on Reset                                                               |  |  |  |

| D004                                                        | SVDD   | VDD Rise Rate to ensure<br>Power-on Reset                                                                           | 0.05* |                                                      | —                      | V/ms                 | See Section 5.1 for details on<br>Power-on Reset                                                               |  |  |  |

| D010                                                        | IDD    | <b>Supply Current<sup>(2)</sup></b><br>RC <sup>(3)</sup> and XT modes<br>LP mode, Commercial<br>LP mode, Industrial |       | 0.5<br>11<br>14                                      | <br>27<br>35           | μA                   | Fosc = 2.0 MHz, VDD = 3.0V<br>Fosc = 32 kHz, VDD = 2.5V WDT disabled<br>Fosc = 32 kHz, VDD = 2.5V WDT disabled |  |  |  |

| D020                                                        | IPD    | <b>Power-down Current<sup>(2,4)</sup></b><br>Commercial<br>Commercial<br>Industrial<br>Industrial                   |       | 2.5<br>0.25<br>3.5<br>0.3                            | 12<br>4.0<br>14<br>5.0 | μΑ<br>μΑ<br>μΑ<br>μΑ | VDD = 2.5V, WDT enabled<br>VDD = 2.5V, WDT disabled<br>VDD = 2.5V, WDT enabled<br>VDD = 2.5V, WDT disabled     |  |  |  |

These parameters are characterized but not tested.

- † Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- **Note 1:** This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to VSS, T0CKI = VDD, MCLR = VDD; WDT enabled/ disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- **3:** Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in kΩ.

- 4: The oscillator start-up time can be as much as 8 seconds for XT and LP oscillator selection on wake-up from SLEEP mode or during initial power-up.

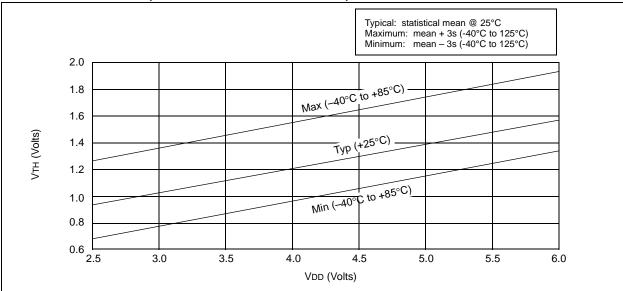

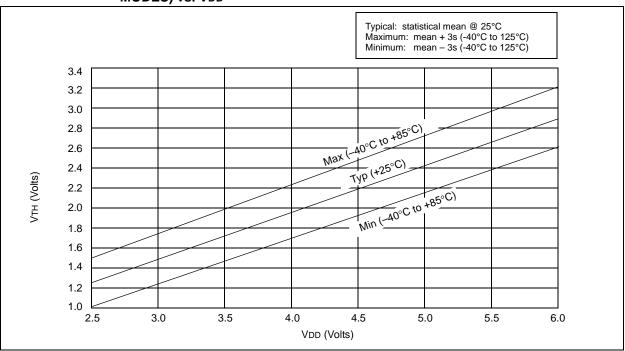

FIGURE 16-7: VTH (INPUT THRESHOLD VOLTAGE) OF I/O PINS - VDD

#### 17.3 DC Characteristics: PIC16C54C/C55A/C56A/C57C/C58B-04, 20 (Commercial, Industrial, Extended) PIC16LC54C/LC55A/LC56A/LC57C/LC58B-04 (Commercial, Industrial) PIC16CR54C/CR56A/CR57C/CR58B-04, 20 (Commercial, Industrial, Extended) PIC16LCR54C/LCR56A/LCR57C/LCR58B-04 (Commercial, Industrial)

| DC CHARACTERISTICS |        |                                                                                                                                     | Standard Operating Con<br>Operating Temperature                                |                               | $\begin{array}{l} \mbox{nditions (unless otherwise specified)} \\ 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array}$ |                            |                                                                                                                                                                                                   |

|--------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                                                                                      | Min                                                                            | Тур†                          | Max                                                                                                                                                                                                                                                                         | Units                      | Conditions                                                                                                                                                                                        |

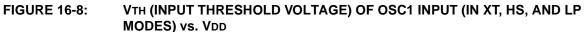

| D030               | VIL    | Input Low Voltage<br>I/O Ports<br>I/O Ports<br>MCLR (Schmitt Trigger)<br>TOCKI (Schmitt Trigger)<br>OSC1 (Schmitt Trigger)<br>OSC1  | Vss<br>Vss<br>Vss<br>Vss<br>Vss<br>Vss<br>Vss                                  | <br><br>                      | 0.8 V<br>0.15 VDD<br>0.15 VDD<br>0.15 VDD<br>0.15 VDD<br>0.3 VDD                                                                                                                                                                                                            | V<br>V<br>V<br>V<br>V      | 4.5V <v<sub>DD ≤ 5.5V<br/>Otherwise<br/>RC mode only<sup>(3)</sup><br/>XT, HS and LP modes</v<sub>                                                                                                |

| D040               | Viн    | Input High Voltage<br>I/O ports<br>I/O ports<br>MCLR (Schmitt Trigger)<br>TOCKI (Schmitt Trigger)<br>OSC1 (Schmitt Trigger)<br>OSC1 | 2.0<br>0.25 Vdd+0.8<br>0.85 Vdd<br>0.85 Vdd<br>0.85 Vdd<br>0.85 Vdd<br>0.7 Vdd | <br>                          | Vdd<br>Vdd<br>Vdd<br>Vdd<br>Vdd<br>Vdd<br>Vdd                                                                                                                                                                                                                               | V<br>V<br>V<br>V<br>V      | 4.5V < VDD ≤ 5.5V<br>Otherwise<br>RC mode only <sup>(3)</sup><br>XT, HS and LP modes                                                                                                              |

| D050               | VHYS   | Hysteresis of Schmitt<br>Trigger inputs                                                                                             | 0.15 Vdd*                                                                      | —                             | _                                                                                                                                                                                                                                                                           | V                          |                                                                                                                                                                                                   |

| D060               | Ιι∟    | Input Leakage Current <sup>(1,2)</sup><br>I/O ports<br>MCLR<br>MCLR<br>T0CKI<br>OSC1                                                | -1.0<br>-5.0<br>-3.0<br>-3.0                                                   | 0.5<br>—<br>0.5<br>0.5<br>0.5 | +1.0<br>+5.0<br>+3.0<br>+3.0<br>—                                                                                                                                                                                                                                           | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ | For VDD $\leq$ 5.5V:<br>VSS $\leq$ VPIN $\leq$ VDD,<br>pin at hi-impedance<br>VPIN = VSS +0.25V<br>VPIN = VDD<br>VSS $\leq$ VPIN $\leq$ VDD<br>VSS $\leq$ VPIN $\leq$ VDD,<br>XT, HS and LP modes |

| D080               | Vol    | Output Low Voltage<br>I/O ports<br>OSC2/CLKOUT                                                                                      |                                                                                | _                             | 0.6<br>0.6                                                                                                                                                                                                                                                                  | V<br>V                     | IOL = 8.7  mA, VDD = 4.5V<br>IOL = 1.6  mA, VDD = 4.5V,<br>RC mode only                                                                                                                           |

| D090               | Vон    | Output High Voltage <sup>(2)</sup><br>I/O ports<br>OSC2/CLKOUT                                                                      | Vdd - 0.7<br>Vdd - 0.7                                                         | _                             | _                                                                                                                                                                                                                                                                           | V<br>V                     | IOH = -5.4 mA, VDD = 4.5V<br>IOH = -1.0 mA, VDD = 4.5V,<br>RC mode only                                                                                                                           |

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- Note 1: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltage.

- **2:** Negative current is defined as coming out of the pin.

- 3: For the RC mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C5X be driven with external clock in RC mode.

# **ON-LINE SUPPORT**

Microchip provides on-line support on the Microchip World Wide Web (WWW) site.

The web site is used by Microchip as a means to make files and information easily available to customers. To view the site, the user must have access to the Internet and a web browser, such as Netscape or Microsoft Explorer. Files are also available for FTP download from our FTP site.

## Connecting to the Microchip Internet Web Site

The Microchip web site is available by using your favorite Internet browser to attach to:

#### www.microchip.com

The file transfer site is available by using an FTP service to connect to:

#### ftp://ftp.microchip.com

The web site and file transfer site provide a variety of services. Users may download files for the latest Development Tools, Data Sheets, Application Notes, User's Guides, Articles and Sample Programs. A variety of Microchip specific business information is also available, including listings of Microchip sales offices, distributors and factory representatives. Other data available for consideration is:

- Latest Microchip Press Releases

- Technical Support Section with Frequently Asked Questions

- Design Tips

- Device Errata

- Job Postings

- Microchip Consultant Program Member Listing

- Links to other useful web sites related to Microchip Products

- Conferences for products, Development Systems, technical information and more

- Listing of seminars and events