Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 2MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | POR, WDT                                                                     |

| Number of I/O              | 12                                                                           |

| Program Memory Size        | 768B (512 x 12)                                                              |

| Program Memory Type        | OTP                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 25 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.8V                                                                    |

| Data Converters            | -                                                                            |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 18-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lv54at-02i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 5.1 Power-On Reset (POR)

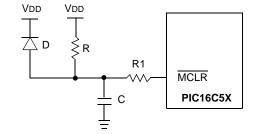

The PIC16C5X family incorporates on-chip Power-On Reset (POR) circuitry which provides an internal chip RESET for most power-up situations. To use this feature, the user merely ties the MCLR/VPP pin to VDD. A simplified block diagram of the on-chip Power-On Reset circuit is shown in Figure 5-1.

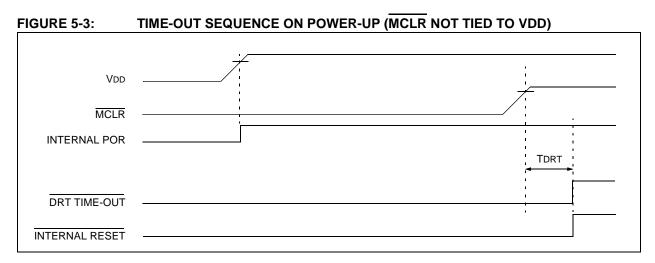

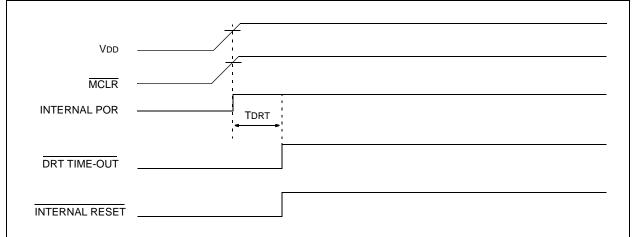

The Power-On Reset circuit and the Device Reset Timer (Section 5.2) circuit are closely related. On power-up, the RESET latch is set and the DRT is <u>RESET</u>. The DRT timer begins counting once it detects MCLR to be high. After the time-out period, which is typically 18 ms, it will RESET the reset latch and thus end the on-chip RESET signal.

A power-up example where MCLR is not tied to VDD is shown in Figure 5-3. VDD is allowed to rise and stabilize before bringing MCLR high. The chip will actually come out of reset TDRT msec after MCLR goes high.

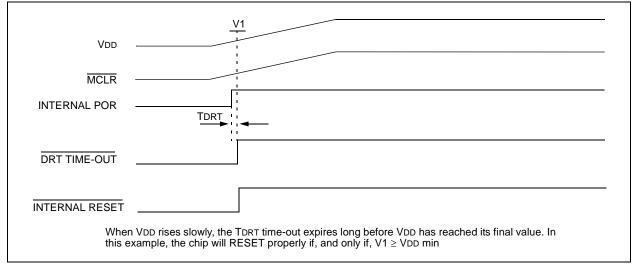

In Figure 5-4, the on-chip Power-On Reset feature is being used (MCLR and VDD are tied together). The VDD is stable before the start-up timer times out and there is no problem in getting a proper RESET. However, Figure 5-5 depicts a problem situation where VDD rises too slowly. The time between when the DRT senses a high on the MCLR/VPP pin, and when the MCLR/VPP pin (and VDD) actually reach their full value, is too long. In this situation, when the start-up timer times out, VDD has not reached the VDD (min) value and the chip is, therefore, not guaranteed to function correctly. For such situations, we recommend that external RC circuits be used to achieve longer POR delay times (Figure 5-2).

Note: When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met.

For more information on PIC16C5X POR, see *Power-Up Considerations* - AN522 in the <u>Embedded Control Handbook</u>.

The POR circuit does not produce an internal RESET when VDD declines.

#### FIGURE 5-2:

#### EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- External Power-On Reset circuit is required only if VDD power-up is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- R < 40 kΩ is recommended to make sure that voltage drop across R does not violate the device electrical specification.

- R1 =  $100\Omega$  to 1 k $\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C in the event of  $\overline{MCLR}$  pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

# PIC16C5X

# FIGURE 5-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): FAST VDD RISE TIME

# FIGURE 5-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): SLOW VDD RISE TIME

#### 6.4 **OPTION Register**

The OPTION Register is a 6-bit wide, write-only register which contains various control bits to configure the Timer0/WDT prescaler and Timer0.

By executing the OPTION instruction, the contents of the W Register will be transferred to the OPTION Register. A RESET sets the OPTION<5:0> bits.

#### **REGISTER 6-2: OPTION REGISTER**

| U-0   | U-0 | W-1  | W-1  | W-1 | W-1 | W-1 | W-1   |

|-------|-----|------|------|-----|-----|-----|-------|

| _     | _   | TOCS | TOSE | PSA | PS2 | PS1 | PS0   |

| bit 7 |     |      |      |     |     |     | bit 0 |

- bit 7-6: Unimplemented: Read as '0'

- bit 5: **TOCS**: Timer0 clock source select bit

- 1 = Transition on T0CKI pin

- 0 = Internal instruction cycle clock (CLKOUT)

- bit 4: **TOSE**: Timer0 source edge select bit

- 1 = Increment on high-to-low transition on T0CKI pin

- 0 = Increment on low-to-high transition on T0CKI pin

- bit 3: **PSA**: Prescaler assignment bit

- 1 = Prescaler assigned to the WDT

- 0 = Prescaler assigned to Timer0

#### bit 2-0: **PS<2:0>:** Prescaler rate select bits

| Bit Value | Timer0 Rate | WDT Rate |

|-----------|-------------|----------|

| 000       | 1:2         | 1:1      |

| 001       | 1:4         | 1:2      |

| 010       | 1:8         | 1:4      |

| 011       | 1:16        | 1:8      |

| 100       | 1:32        | 1:16     |

| 101       | 1:64        | 1:32     |

| 110       | 1:128       | 1:64     |

| 111       | 1:256       | 1:128    |

|           |             |          |

| Legend:           |                  |                     |                    |

|-------------------|------------------|---------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b | it, read as '0'    |

| -n = Value at POR | 1 = bit is set   | 0 = bit is cleared  | x = bit is unknown |

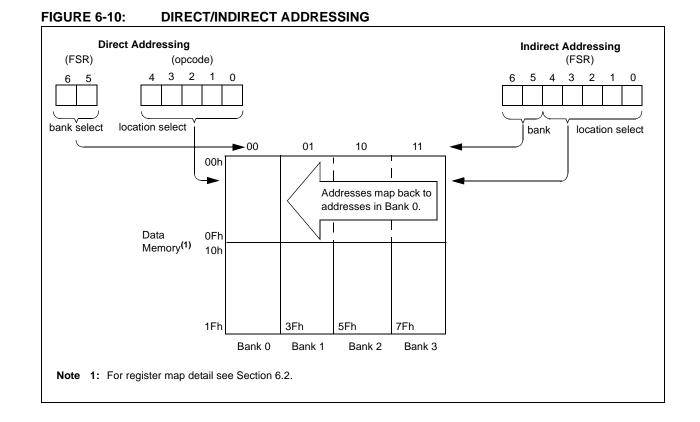

# 6.7 Indirect Data Addressing; INDF and FSR Registers

The INDF Register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR Register (FSR is a *pointer*). This is indirect addressing.

#### EXAMPLE 6-1: INDIRECT ADDRESSING

- Register file 08 contains the value 10h

- Register file 09 contains the value 0Ah

- · Load the value 08 into the FSR Register

- A read of the INDF Register will return the value of 10h

- Increment the value of the FSR Register by one (FSR = 09h)

- A read of the INDF register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF Register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 10h-1Fh using indirect addressing is shown in Example 6-2.

#### EXAMPLE 6-2:

#### HOW TO CLEAR RAM USING INDIRECT ADDRESSING

|          | MOVLW | H'10' | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | MOVWF | FSR   | ; to RAM             |

| NEXT     | CLRF  | INDF  | ;clear INDF Register |

|          | INCF  | FSR,F | ;inc pointer         |

|          | BTFSC | FSR,4 | ;all done?           |

|          | GOTO  | NEXT  | ;NO, clear next      |

| CONTINUE |       |       |                      |

|          | :     |       | ;YES, continue       |

The FSR is either a 5-bit (PIC16C54, PIC16CR54, PIC16C55, PIC16C56, PIC16CR56) or 7-bit (PIC16C57, PIC16CR57, PIC16CR58, PIC16CR58) wide register. It is used in conjunction with the INDF Register to indirectly address the data memory area.

The FSR<4:0> bits are used to select data memory addresses 00h to 1Fh.

**PIC16C54, PIC16CR54, PIC16C55, PIC16C56, PIC16CR56:** These do not use banking. FSR<6:5> bits are unimplemented and read as '1's.

**PIC16C57**, **PIC16CR57**, **PIC16C58**, **PIC16CR58**: FSR<6:5> are the bank select bits and are used to select the bank to be addressed (00 = bank 0, 01 = bank 1, 10 = bank 2, 11 = bank 3).

© 1997-2013 Microchip Technology Inc.

NOTES:

# 9.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits that deal with the needs of realtime applications. The PIC16C5X family of microcontrollers have a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These features are:

- Oscillator Selection (Section 4.0)

- RESET (Section 5.0)

- Power-On Reset (Section 5.1)

- Device Reset Timer (Section 5.2)

- Watchdog Timer (WDT) (Section 9.2)

- SLEEP (Section 9.3)

- Code protection (Section 9.4)

- ID locations (Section 9.5)

The PIC16C5X Family has a Watchdog Timer which can be shut off only through configuration bit WDTE. It runs off of its own RC oscillator for added reliability. There is an 18 ms delay provided by the Device Reset Timer (DRT), intended to keep the chip in RESET until the crystal oscillator is stable. With this timer on-chip, most applications need no external RESET circuitry.

The SLEEP mode is designed to offer a very low current Power-down mode. The user can wake up from SLEEP through external RESET or through a Watchdog Timer time-out. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

#### 12.2 DC Characteristics: PIC16C54/55/56/57-RCI, XTI, 10I, HSI, LPI (Industrial)

| PIC16C54/55/56/57-RCI, XTI, 10I, HSI, LPI<br>(Industrial) |        | Standard Operating Conditions (unless otherwise specified Operating Temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial        |                                 |                                       |                                    |                            |                                                                                                                                                                                                          |

|-----------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------------|------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.                                              | Symbol | Characteristic/Device                                                                                                                        | Min                             | Тур†                                  | Max                                | Units                      | Conditions                                                                                                                                                                                               |

| D001                                                      | Vdd    | Supply Voltage<br>PIC16C5X-RCI<br>PIC16C5X-XTI<br>PIC16C5X-10I<br>PIC16C5X-HSI<br>PIC16C5X-LPI                                               | 3.0<br>3.0<br>4.5<br>4.5<br>2.5 |                                       | 6.25<br>6.25<br>5.5<br>5.5<br>6.25 | V<br>V<br>V<br>V           |                                                                                                                                                                                                          |

| D002                                                      | Vdr    | RAM Data Retention Voltage <sup>(1)</sup>                                                                                                    |                                 | 1.5*                                  |                                    | V                          | Device in SLEEP mode                                                                                                                                                                                     |

| D003                                                      | VPOR   | VDD Start Voltage to ensure<br>Power-on Reset                                                                                                | —                               | Vss                                   | —                                  | V                          | See Section 5.1 for details on<br>Power-on Reset                                                                                                                                                         |

| D004                                                      | SVDD   | VDD Rise Rate to ensure<br>Power-on Reset                                                                                                    | 0.05*                           |                                       | —                                  | V/ms                       | See Section 5.1 for details on<br>Power-on Reset                                                                                                                                                         |

| D010                                                      | IDD    | Supply Current <sup>(2)</sup><br>PIC16C5X-RCI <sup>(3)</sup><br>PIC16C5X-XTI<br>PIC16C5X-10I<br>PIC16C5X-HSI<br>PIC16C5X-HSI<br>PIC16C5X-LPI |                                 | 1.8<br>1.8<br>4.8<br>4.8<br>9.0<br>15 | 3.3<br>3.3<br>10<br>10<br>20<br>40 | mA<br>mA<br>mA<br>mA<br>μA | Fosc = 4 MHz, VDD = $5.5V$<br>Fosc = 4 MHz, VDD = $5.5V$<br>Fosc = 10 MHz, VDD = $5.5V$<br>Fosc = 10 MHz, VDD = $5.5V$<br>Fosc = 20 MHz, VDD = $5.5V$<br>Fosc = $32$ kHz, VDD = $3.0V$ ,<br>WDT disabled |

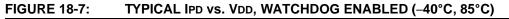

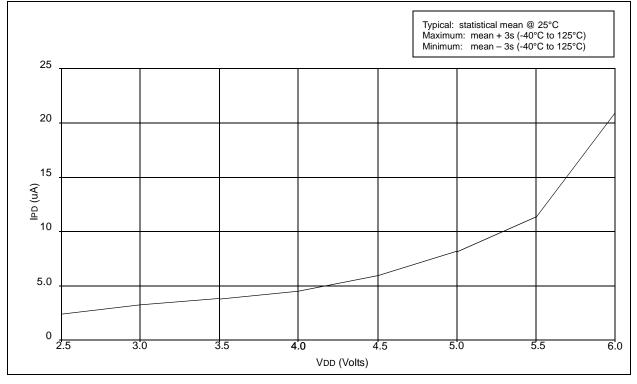

| D020                                                      | Ipd    | Power-down Current <sup>(2)</sup>                                                                                                            | _                               | 4.0<br>0.6                            | 14<br>12                           | μΑ<br>μΑ                   | VDD = 3.0V, WDT enabled<br>VDD = 3.0V, WDT disabled                                                                                                                                                      |

\* These parameters are characterized but not tested.

- † Data in "Typ" column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, oscillator type, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tristated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in SLEEP mode. The power-down current in SLEEP mode does not depend on the oscillator type.

- **3:** Does not include current through REXT. The current through the resistor can be estimated by the formula: IR = VDD/2REXT (mA) with REXT in kΩ.

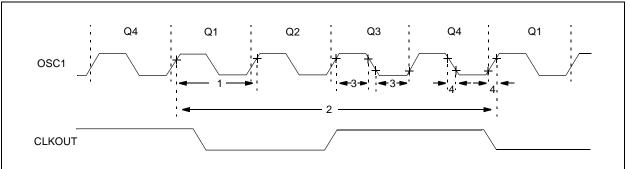

#### **13.6** Timing Diagrams and Specifications

#### FIGURE 13-2: EXTERNAL CLOCK TIMING - PIC16CR54A

#### TABLE 13-1: EXTERNAL CLOCK TIMING REQUIREMENTS - PIC16CR54A

| AC Chara     | cteristics | Standard Operating Conditions (unless otherwise specified)Operating Temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |     |   |     |     | -                |  |  |

|--------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---|-----|-----|------------------|--|--|

| Param<br>No. | Symbol     | Characteristic Min Typ† Max Units Conditions                                                                                                                                                                                                   |     |   |     |     |                  |  |  |

|              | Fosc       | External CLKIN Frequency <sup>(1)</sup>                                                                                                                                                                                                        | DC  | _ | 4.0 | MHz | XT OSC mode      |  |  |

|              |            |                                                                                                                                                                                                                                                | DC  | — | 4.0 | MHz | HS osc mode (04) |  |  |

|              |            |                                                                                                                                                                                                                                                | DC  | _ | 10  | MHz | HS osc mode (10) |  |  |

|              |            |                                                                                                                                                                                                                                                | DC  | — | 20  | MHz | HS osc mode (20) |  |  |

|              |            |                                                                                                                                                                                                                                                | DC  | _ | 200 | kHz | LP osc mode      |  |  |

|              |            | Oscillator Frequency <sup>(1)</sup>                                                                                                                                                                                                            | DC  |   | 4.0 | MHz | RC OSC mode      |  |  |

|              |            |                                                                                                                                                                                                                                                | 0.1 | _ | 4.0 | MHz | XT osc mode      |  |  |

|              |            |                                                                                                                                                                                                                                                | 4.0 | _ | 4.0 | MHz | HS osc mode (04) |  |  |

|              |            |                                                                                                                                                                                                                                                | 4.0 | _ | 10  | MHz | HS osc mode (10) |  |  |

|              |            |                                                                                                                                                                                                                                                | 4.0 | _ | 20  | MHz | HS osc mode (20) |  |  |

|              |            |                                                                                                                                                                                                                                                | 5.0 | — | 200 | kHz | LP osc mode      |  |  |

\* These parameters are characterized but not tested.

† Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

Note 1: All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

**2:** Instruction cycle period (TCY) equals four times the input oscillator time base period.

## 15.0 ELECTRICAL CHARACTERISTICS - PIC16C54A

| Absolute Maximum Ratings <sup>(†)</sup>                                                                  |                                      |

|----------------------------------------------------------------------------------------------------------|--------------------------------------|

| Ambient temperature under bias                                                                           | –55°C to +125°C                      |

| Storage temperature                                                                                      | –65°C to +150°C                      |

| Voltage on VDD with respect to Vss                                                                       | 0 to +7.5V                           |

| Voltage on MCLR with respect to Vss                                                                      | 0 to +14V                            |

| Voltage on all other pins with respect to Vss                                                            | –0.6V to (VDD + 0.6V)                |

| Total power dissipation <sup>(1)</sup>                                                                   | 800 mW                               |

| Max. current out of Vss pin                                                                              | 150 mA                               |

| Max. current into Vod pin                                                                                | 100 mA                               |

| Max. current into an input pin (T0CKI only)                                                              | ±500 μA                              |

| Input clamp current, Iik (VI < 0 or VI > VDD)                                                            | ±20 mA                               |

| Output clamp current, IOK (VO < 0 or VO > VDD)                                                           |                                      |

| Max. output current sunk by any I/O pin                                                                  | 25 mA                                |

| Max. output current sourced by any I/O pin                                                               | 20 mA                                |

| Max. output current sourced by a single I/O port (PORTA or B)                                            | 50 mA                                |

| Max. output current sunk by a single I/O port (PORTA or B)                                               | 50 mA                                |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VD | D-VOH) X IOH} + $\Sigma$ (VOL X IOL) |

† NOTICE: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

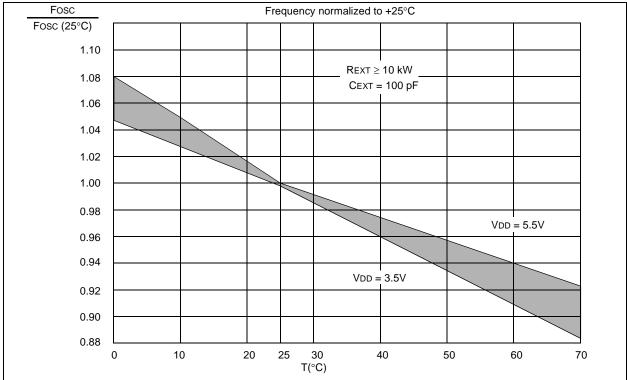

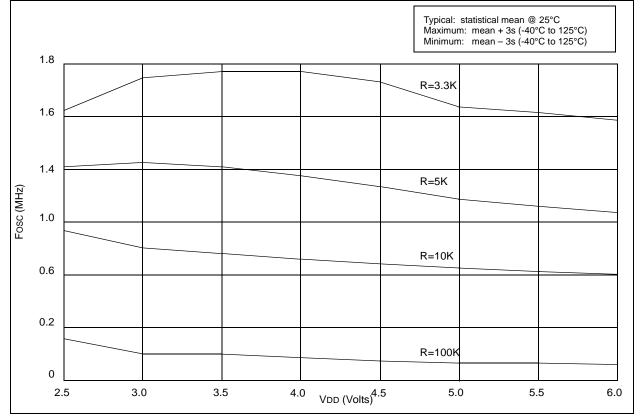

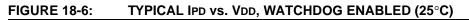

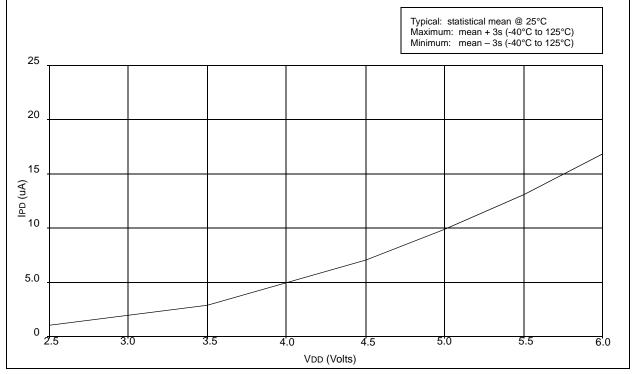

### 18.0 DEVICE CHARACTERIZATION - PIC16LC54A

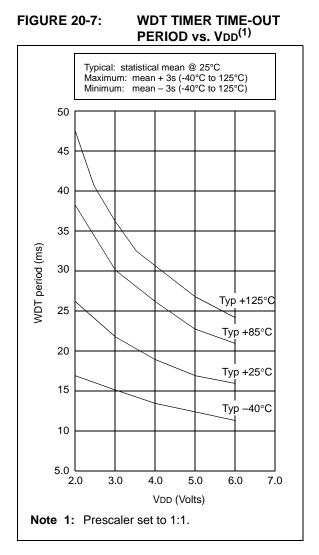

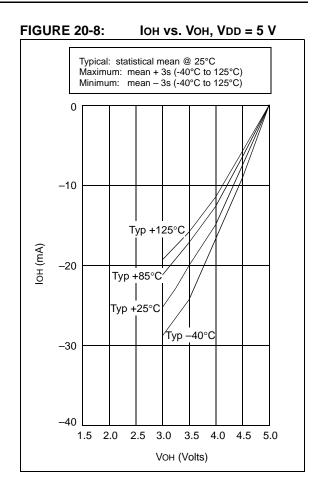

The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

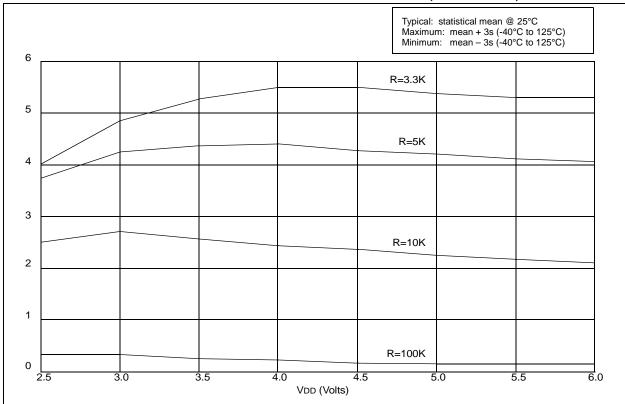

FIGURE 18-1: TYPICAL RC OSCILLATOR FREQUENCY vs. TEMPERATURE

#### TABLE 18-1: RC OSCILLATOR FREQUENCIES

| Сехт   | Rext | Average<br>Fosc @ 5V, 25°C |       |  |

|--------|------|----------------------------|-------|--|

| 20 pF  | 3.3K | 5 MHz                      | ± 27% |  |

|        | 5K   | 3.8 MHz                    | ± 21% |  |

|        | 10K  | 2.2 MHz                    | ± 21% |  |

|        | 100K | 262 kHz                    | ± 31% |  |

| 100 pF | 3.3K | 1.63 MHz                   | ± 13% |  |

|        | 5K   | 1.2 MHz                    | ± 13% |  |

|        | 10K  | 684 kHz                    | ± 18% |  |

|        | 100K | 71 kHz                     | ± 25% |  |

| 300 pF | 3.3K | 660 kHz                    | ± 10% |  |

|        | 5.0K | 484 kHz                    | ± 14% |  |

|        | 10K  | 267 kHz                    | ± 15% |  |

|        | 100K | 29 kHz                     | ± 19% |  |

The frequencies are measured on DIP packages.

The percentage variation indicated here is part-to-part variation due to normal process distribution. The variation indicated is  $\pm 3$  standard deviation from average value for VDD = 5V.

#### FIGURE 18-2: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD, CEXT = 20 PF, 25°C

## 19.0 ELECTRICAL CHARACTERISTICS - PIC16LC54C 40MHz

#### Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                                                                 | –55°C to +125°C               |

|----------------------------------------------------------------------------------------------------------------|-------------------------------|

| Storage temperature                                                                                            | –65°C to +150°C               |

| Voltage on VDD with respect to VSS                                                                             | 0 to +7.5V                    |

| Voltage on MCLR with respect to Vss                                                                            | 0 to +14V                     |

| Voltage on all other pins with respect to Vss                                                                  | –0.6V to (VDD + 0.6V)         |

| Total power dissipation <sup>(1)</sup>                                                                         | 800 mW                        |

| Max. current out of Vss pin                                                                                    | 150 mA                        |

| Max. current into Vod pin                                                                                      |                               |

| Max. current into an input pin (T0CKI only)                                                                    | ±500 μA                       |

| Input clamp current, liк (Vi <0 or Vi > VDD)                                                                   | ±20 mA                        |

| Output clamp current, IOK (VO < 0 or VO > VDD)                                                                 | ±20 mA                        |

| Max. output current sunk by any I/O pin                                                                        | 25 mA                         |

| Max. output current sourced by any I/O pin                                                                     | 20 mA                         |

| Max. output current sourced by a single I/O (Port A, B or C)                                                   | 50 mA                         |

| Max. output current sunk by a single I/O (Port A, B or C)                                                      | 50 mA                         |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) | x IOH} + $\Sigma$ (Vol x Iol) |

**†** NOTICE: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

### **19.3 Timing Parameter Symbology and Load Conditions**

The timing parameter symbols have been created with one of the following formats:

1. TppS2ppS

| 2. Tp | pS                                      |                    |

|-------|-----------------------------------------|--------------------|

| Т     |                                         |                    |

| F     | Frequency                               | T Time             |

| Lowe  | ercase letters (pp) and their meanings: |                    |

| рр    |                                         |                    |

| 2     | to                                      | mc MCLR            |

| ck    | CLKOUT                                  | osc oscillator     |

| су    | cycle time                              | os OSC1            |

| drt   | device reset timer                      | t0 T0CKI           |

| io    | I/O port                                | wdt watchdog timer |

| Uppe  | ercase letters and their meanings:      |                    |

| S     |                                         |                    |

| F     | Fall                                    | P Period           |

| н     | High                                    | R Rise             |

| Ι     | Invalid (Hi-impedance)                  | V Valid            |

| L     | Low                                     | Z Hi-impedance     |

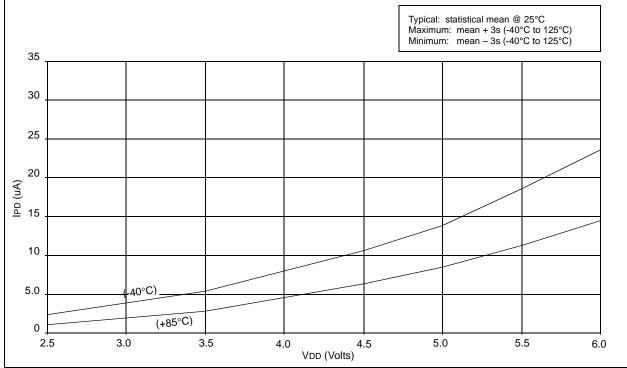

#### FIGURE 19-2: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS -PIC16C54C/C55A/C56A/C57C/C58B-40

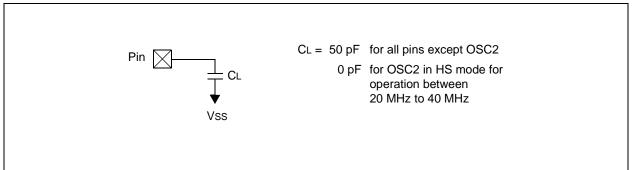

### 20.0 DEVICE CHARACTERIZATION - PIC16LC54C 40MHz

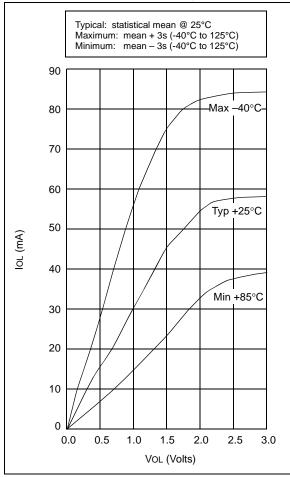

The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

© 1997-2013 Microchip Technology Inc.

#### TABLE 20-1: INPUT CAPACITANCE

| Pin         | Typical Capa | acitance (pF) |

|-------------|--------------|---------------|

| FIII        | 18L PDIP     | 18L SOIC      |

| RA port     | 5.0          | 4.3           |

| RB port     | 5.0          | 4.3           |

| MCLR        | 17.0         | 17.0          |

| OSC1        | 4.0          | 3.5           |

| OSC2/CLKOUT | 4.3          | 3.5           |

| тоскі       | 3.2          | 2.8           |

All capacitance values are typical at  $25^{\circ}$ C. A part-to-part variation of ±25% (three standard deviations) should be taken into account.

#### FIGURE 20-9: IOL vs. VOL, VDD = 5 V

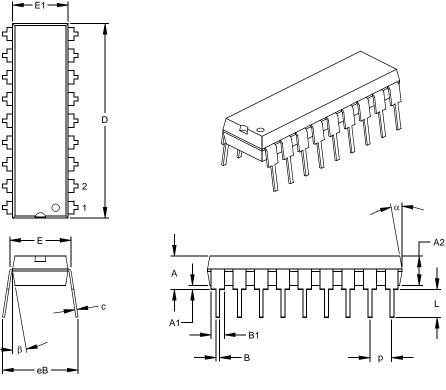

#### 18-Lead Plastic Dual In-line (P) – 300 mil (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units     | INCHES* |      |      | MILLIMETERS |       |       |

|----------------------------|-----------|---------|------|------|-------------|-------|-------|

| Dimensio                   | on Limits | MIN     | NOM  | MAX  | MIN         | NOM   | MAX   |

| Number of Pins             | n         |         | 18   |      |             | 18    |       |

| Pitch                      | р         |         | .100 |      |             | 2.54  |       |

| Top to Seating Plane       | Α         | .140    | .155 | .170 | 3.56        | 3.94  | 4.32  |

| Molded Package Thickness   | A2        | .115    | .130 | .145 | 2.92        | 3.30  | 3.68  |

| Base to Seating Plane      | A1        | .015    |      |      | 0.38        |       |       |

| Shoulder to Shoulder Width | Е         | .300    | .313 | .325 | 7.62        | 7.94  | 8.26  |

| Molded Package Width       | E1        | .240    | .250 | .260 | 6.10        | 6.35  | 6.60  |

| Overall Length             | D         | .890    | .898 | .905 | 22.61       | 22.80 | 22.99 |

| Tip to Seating Plane       | L         | .125    | .130 | .135 | 3.18        | 3.30  | 3.43  |

| Lead Thickness             | С         | .008    | .012 | .015 | 0.20        | 0.29  | 0.38  |

| Upper Lead Width           | B1        | .045    | .058 | .070 | 1.14        | 1.46  | 1.78  |

| Lower Lead Width           | В         | .014    | .018 | .022 | 0.36        | 0.46  | 0.56  |

| Overall Row Spacing §      | eB        | .310    | .370 | .430 | 7.87        | 9.40  | 10.92 |

| Mold Draft Angle Top       | α         | 5       | 10   | 15   | 5           | 10    | 15    |

| Mold Draft Angle Bottom    | β         | 5       | 10   | 15   | 5           | 10    | 15    |

\* Controlling Parameter § Significant Characteristic

Notes:

n

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-001 Drawing No. C04-007

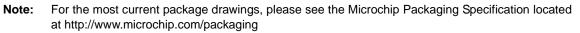

#### 28-Lead Skinny Plastic Dual In-line (SP) - 300 mil (PDIP)

в

|                            | Units     | nits INCHES* |       |       | MILLIMETERS |       |       |

|----------------------------|-----------|--------------|-------|-------|-------------|-------|-------|

| Dimensi                    | on Limits | MIN          | NOM   | MAX   | MIN         | NOM   | MAX   |

| Number of Pins             | n         |              | 28    |       |             | 28    |       |

| Pitch                      | р         |              | .100  |       |             | 2.54  |       |

| Top to Seating Plane       | А         | .140         | .150  | .160  | 3.56        | 3.81  | 4.06  |

| Molded Package Thickness   | A2        | .125         | .130  | .135  | 3.18        | 3.30  | 3.43  |

| Base to Seating Plane      | A1        | .015         |       |       | 0.38        |       |       |

| Shoulder to Shoulder Width | E         | .300         | .310  | .325  | 7.62        | 7.87  | 8.26  |

| Molded Package Width       | E1        | .275         | .285  | .295  | 6.99        | 7.24  | 7.49  |

| Overall Length             | D         | 1.345        | 1.365 | 1.385 | 34.16       | 34.67 | 35.18 |

| Tip to Seating Plane       | L         | .125         | .130  | .135  | 3.18        | 3.30  | 3.43  |

| Lead Thickness             | С         | .008         | .012  | .015  | 0.20        | 0.29  | 0.38  |

| Upper Lead Width           | B1        | .040         | .053  | .065  | 1.02        | 1.33  | 1.65  |

| Lower Lead Width           | В         | .016         | .019  | .022  | 0.41        | 0.48  | 0.56  |

| Overall Row Spacing        | èB        | .320         | .350  | .430  | 8.13        | 8.89  | 10.92 |

| Mold Draft Angle Top       | α         | 5            | 10    | 15    | 5           | 10    | 15    |

| Mold Draft Angle Bottom    | β         | 5            | 10    | 15    | 5           | 10    | 15    |

\* Controlling Parameter § Significant Characteristic

eВ

Dimension D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side.

JEDEC Equivalent: MO-095

Drawing No. C04-070

- p -

Notes:

### APPENDIX A: COMPATIBILITY

To convert code written for PIC16CXX to PIC16C5X, the user should take the following steps:

- 1. Check any CALL, GOTO or instructions that modify the PC to determine if any program memory page select operations (PA2, PA1, PA0 bits) need to be made.

- 2. Revisit any computed jump operations (write to PC or add to PC, etc.) to make sure page bits are set properly under the new scheme.

- 3. Eliminate any special function register page switching. Redefine data variables to reallocate them.

- 4. Verify all writes to STATUS, OPTION, and FSR registers since these have changed.

- 5. Change RESET vector to proper value for processor used.

- 6. Remove any use of the ADDLW, RETURN and SUBLW instructions.

- 7. Rewrite any code segments that use interrupts.

### APPENDIX B: REVISION HISTORY

Revision KE (January 2013)

Added a note to each package outline drawing.