# E · K Hat ice Semiconductor Corporation - <u>LCMXO3L-4300E-6MG256I Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                           |

|--------------------------------|----------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 540                                                                              |

| Number of Logic Elements/Cells | 4320                                                                             |

| Total RAM Bits                 | 94208                                                                            |

| Number of I/O                  | 206                                                                              |

| Number of Gates                | -                                                                                |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                    |

| Mounting Type                  | Surface Mount                                                                    |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                               |

| Package / Case                 | 256-VFBGA                                                                        |

| Supplier Device Package        | 256-CSFBGA (9x9)                                                                 |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lcmxo3l-4300e-6mg256i |

|                                |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## MachXO3 Family Data Sheet Introduction

#### January 2016

### **Features**

### Solutions

- Smallest footprint, lowest power, high data throughput bridging solutions for mobile applications

- Optimized footprint, logic density, IO count, IO performance devices for IO management and logic applications

- High IO/logic, lowest cost/IO, high IO devices for IO expansion applications

### ■ Flexible Architecture

- Logic Density ranging from 640 to 9.4K LUT4

- High IO to LUT ratio with up to 384 IO pins

### Advanced Packaging

- 0.4 mm pitch: 1K to 4K densities in very small footprint WLCSP (2.5 mm x 2.5 mm to 3.8 mm x 3.8 mm) with 28 to 63 IOs

- 0.5 mm pitch: 640 to 6.9K LUT densities in 6 mm x 6 mm to 10 mm x 10 mm BGA packages with up to 281 IOs

- 0.8 mm pitch: 1K to 9.4K densities with up to 384 IOs in BGA packages

### Pre-Engineered Source Synchronous I/O

- DDR registers in I/O cells

- Dedicated gearing logic

- 7:1 Gearing for Display I/Os

- Generic DDR, DDRx2, DDRx4

### High Performance, Flexible I/O Buffer

- Programmable sysIO<sup>™</sup> buffer supports wide range of interfaces:

- LVCMOS 3.3/2.5/1.8/1.5/1.2

- LVTTL

- LVDS, Bus-LVDS, MLVDS, LVPECL

- MIPI D-PHY Emulated

- Schmitt trigger inputs, up to 0.5 V hysteresis

- Ideal for IO bridging applications

- I/Os support hot socketing

- On-chip differential termination

- Programmable pull-up or pull-down mode

### ■ Flexible On-Chip Clocking

- · Eight primary clocks

- Up to two edge clocks for high-speed I/O interfaces (top and bottom sides only)

- Up to two analog PLLs per device with fractional-n frequency synthesis

- Wide input frequency range (7 MHz to 400 MHz)

- Non-volatile, Multi-time Programmable

- Instant-on

- Powers up in microseconds

- · Optional dual boot with external SPI memory

- Single-chip, secure solution

- Programmable through JTAG, SPI or I<sup>2</sup>C

- MachXO3L includes multi-time programmable NVCM

- MachXO3LF infinitely reconfigurable Flash

Supports background programming of non-volatile memory

### ■ TransFR Reconfiguration

In-field logic update while IO holds the system state

### Enhanced System Level Support

- On-chip hardened functions: SPI, I<sup>2</sup>C, timer/ counter

- On-chip oscillator with 5.5% accuracy

- Unique TraceID for system tracking

- Single power supply with extended operating range

- IEEE Standard 1149.1 boundary scan

- IEEE 1532 compliant in-system programming

#### Applications

- Consumer Electronics

- Compute and Storage

- Wireless Communications

- Industrial Control Systems

- Automotive System

#### Low Cost Migration Path

- Migration from the Flash based MachXO3LF to the NVCM based MachXO3L

- · Pin compatible and equivalent timing

© 2016 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

#### Advance Data Sheet DS1047

### Table 1-1. MachXO3L/LF Family Selection Guide

| Features                                                |                                  | MachXO3L-640/<br>MachXO3LF-640 | MachXO3L-1300/<br>MachXO3LF-1300 | MachXO3L-2100/<br>MachXO3LF-2100 | MachXO3L-4300/<br>MachXO3LF-4300 | MachXO3L-6900/<br>MachXO3LF-6900 | MachXO3L-9400/<br>MachXO3LF-9400 |

|---------------------------------------------------------|----------------------------------|--------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|

| LUTs                                                    |                                  | 640                            | 1300                             | 2100                             | 4300                             | 6900                             | 9400                             |

| Distributed RAM (kbits)                                 |                                  | 5                              | 10                               | 16                               | 34                               | 54                               | 73                               |

| EBR SRAM (                                              | kbits)                           | 64                             | 64                               | 74                               | 92                               | 240                              | 432                              |

| Number of PLLs                                          |                                  | 1                              | 1                                | 1                                | 2                                | 2                                | 2                                |

| Hardened I <sup>2</sup> C                               |                                  | 2                              | 2                                | 2                                | 2                                | 2                                | 2                                |

| Functions:                                              | SPI                              | 1                              | 1                                | 1                                | 1                                | 1                                | 1                                |

|                                                         | Timer/Counter                    | 1                              | 1                                | 1                                | 1                                | 1                                | 1                                |

|                                                         | Oscillator                       | 1                              | 1                                | 1                                | 1                                | 1                                | 1                                |

| MIPI D-PHY                                              | Support                          | Yes                            | Yes                              | Yes                              | Yes                              | Yes                              | Yes                              |

| Multi Time Pr<br>NVCM                                   | ogrammable                       | MachXO3L-640                   | MachXO3L-1300                    | MachXO3L-2100                    | MachXO3L-4300                    | MachXO3L-6900                    | MachXO3L-9400                    |

| Programmable Flash                                      |                                  | MachXO3LF-640                  | MachXO3LF-1300                   | MachXO3LF-2100                   | MachXO3LF-4300                   | MachXO3LF-6900                   | MachXO3LF-9400                   |

| Packages IO                                             |                                  |                                |                                  |                                  |                                  |                                  |                                  |

| 36-ball WLCSP <sup>1</sup><br>(2.5 mm x 2.5 mm, 0.4 mm) |                                  |                                | 28                               |                                  |                                  |                                  |                                  |

| 49-ball WLCS<br>(3.2 mm x 3.2                           | SP <sup>1</sup><br>2 mm, 0.4 mm) |                                |                                  | 38                               |                                  |                                  |                                  |

| 81-ball WLCS<br>(3.8 mm x 3.8                           | SP <sup>1</sup><br>3 mm, 0.4 mm) |                                |                                  |                                  | 63                               |                                  |                                  |

| 121-ball csfB<br>(6 mm x 6 mr                           |                                  | 100                            | 100                              | 100                              | 100                              |                                  |                                  |

| 256-ball csfB<br>(9 mm x 9 mr                           |                                  | 2                              | 206                              | 206                              | 206                              | 206                              | 206                              |

| 324-ball csfB<br>(10 mm x 10                            |                                  |                                |                                  | 268                              | 268                              | 281                              |                                  |

| 256-ball caB0<br>(14 mm x 14                            |                                  |                                | 206                              | 206                              | 206                              | 206                              | 206                              |

| 324-ball caB0<br>(15 mm x 15                            |                                  |                                |                                  | 279                              | 279                              | 279                              |                                  |

| 400-ball caB0<br>(17 mm x 17                            |                                  |                                |                                  |                                  | 335                              | 335                              | 335                              |

| 484-ball caB0<br>(19 mm x 19                            |                                  |                                |                                  |                                  |                                  |                                  | 384                              |

1. Package is only available for E=1.2 V devices.

2. Package is only available for C=2.5 V/3.3 V devices.

### Introduction

MachXO3<sup>™</sup> device family is an Ultra-Low Density family that supports the most advanced programmable bridging and IO expansion. It has the breakthrough IO density and the lowest cost per IO. The device IO features have the integrated support for latest industry standard IO.

The MachXO3L/LF family of low power, instant-on, non-volatile PLDs has five devices with densities ranging from 640 to 9400 Look-Up Tables (LUTs). In addition to LUT-based, low-cost programmable logic these devices feature Embedded Block RAM (EBR), Distributed RAM, Phase Locked Loops (PLLs), pre-engineered source synchronous I/O support, advanced configuration support including dual-boot capability and hardened versions of commonly used functions such as SPI controller, I<sup>2</sup>C controller and timer/counter. MachXO3LF devices also support User Flash Memory (UFM). These features allow these devices to be used in low cost, high volume consumer and system applications.

The MachXO3L/LF devices are designed on a 65nm non-volatile low power process. The device architecture has several features such as programmable low swing differential I/Os and the ability to turn off I/O banks, on-chip PLLs

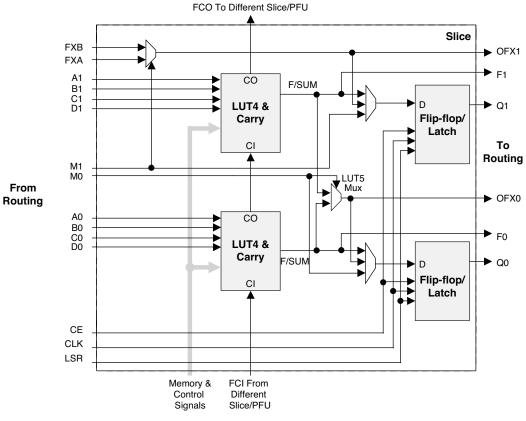

### Figure 2-4. Slice Diagram

For Slices 0 and 1, memory control signals are generated from Slice 2 as follows:

- WCK is CLK

WRE is from LSR

- DI[3:2] for Slice 1 and DI[1:0] for Slice 0 data from Slice 2

- WAD [A:D] is a 4-bit address from slice 2 LUT input

Table 2-2. Slice Signal Descriptions

| Function | Туре             | Signal Names   | Description                                                          |

|----------|------------------|----------------|----------------------------------------------------------------------|

| Input    | Data signal      | A0, B0, C0, D0 | Inputs to LUT4                                                       |

| Input    | Data signal      | A1, B1, C1, D1 | Inputs to LUT4                                                       |

| Input    | Multi-purpose    | M0/M1          | Multi-purpose input                                                  |

| Input    | Control signal   | CE             | Clock enable                                                         |

| Input    | Control signal   | LSR            | Local set/reset                                                      |

| Input    | Control signal   | CLK            | System clock                                                         |

| Input    | Inter-PFU signal | FCIN           | Fast carry in <sup>1</sup>                                           |

| Output   | Data signals     | F0, F1         | LUT4 output register bypass signals                                  |

| Output   | Data signals     | Q0, Q1         | Register outputs                                                     |

| Output   | Data signals     | OFX0           | Output of a LUT5 MUX                                                 |

| Output   | Data signals     | OFX1           | Output of a LUT6, LUT7, LUT8 <sup>2</sup> MUX depending on the slice |

| Output   | Inter-PFU signal | FCO            | Fast carry out <sup>1</sup>                                          |

1. See Figure 2-3 for connection details.

2. Requires two PFUs.

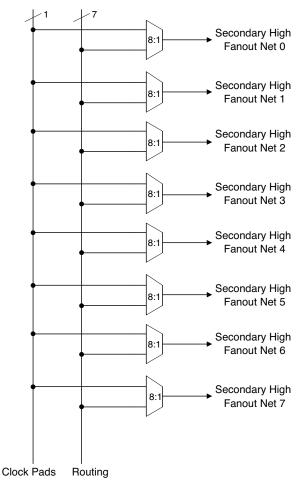

#### Figure 2-6. Secondary High Fanout Nets for MachXO3L/LF Devices

### sysCLOCK Phase Locked Loops (PLLs)

The sysCLOCK PLLs provide the ability to synthesize clock frequencies. All MachXO3L/LF devices have one or more sysCLOCK PLL. CLKI is the reference frequency input to the PLL and its source can come from an external I/O pin or from internal routing. CLKFB is the feedback signal to the PLL which can come from internal routing or an external I/O pin. The feedback divider is used to multiply the reference frequency and thus synthesize a higher frequency clock output.

The MachXO3L/LF sysCLOCK PLLs support high resolution (16-bit) fractional-N synthesis. Fractional-N frequency synthesis allows the user to generate an output clock which is a non-integer multiple of the input frequency. For more information about using the PLL with Fractional-N synthesis, please see TN1282, MachXO3 sysCLOCK PLL Design and Usage Guide.

Each output has its own output divider, thus allowing the PLL to generate different frequencies for each output. The output dividers can have a value from 1 to 128. The output dividers may also be cascaded together to generate low frequency clocks. The CLKOP, CLKOS, CLKOS2, and CLKOS3 outputs can all be used to drive the MachXO3L/LF clock distribution network directly or general purpose routing resources can be used.

The LOCK signal is asserted when the PLL determines it has achieved lock and de-asserted if a loss of lock is detected. A block diagram of the PLL is shown in Figure 2-7.

The setup and hold times of the device can be improved by programming a phase shift into the CLKOS, CLKOS2, and CLKOS3 output clocks which will advance or delay the output clock with reference to the CLKOP output clock.

### Input Gearbox

Each PIC on the bottom edge has a built-in 1:8 input gearbox. Each of these input gearboxes may be programmed as a 1:7 de-serializer or as one IDDRX4 (1:8) gearbox or as two IDDRX2 (1:4) gearboxes. Table 2-9 shows the gearbox signals.

### Table 2-9. Input Gearbox Signal List

| Name      | I/O Type | Description                                                                                                                                                |

|-----------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D         | Input    | High-speed data input after programmable delay in PIO A input register block                                                                               |

| ALIGNWD   | Input    | Data alignment signal from device core                                                                                                                     |

| SCLK      | Input    | Slow-speed system clock                                                                                                                                    |

| ECLK[1:0] | Input    | High-speed edge clock                                                                                                                                      |

| RST       | Input    | Reset                                                                                                                                                      |

| Q[7:0]    | Output   | Low-speed data to device core:<br>Video RX(1:7): Q[6:0]<br>GDDRX4(1:8): Q[7:0]<br>GDDRX2(1:4)(IOL-A): Q4, Q5, Q6, Q7<br>GDDRX2(1:4)(IOL-C): Q0, Q1, Q2, Q3 |

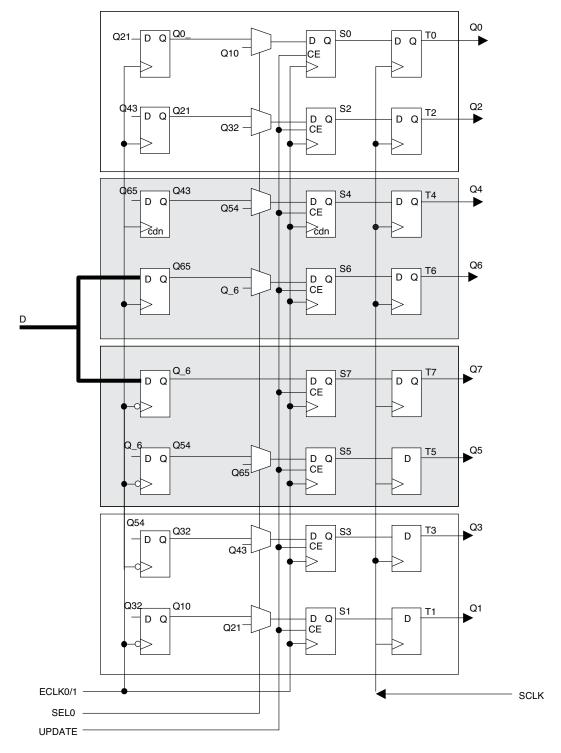

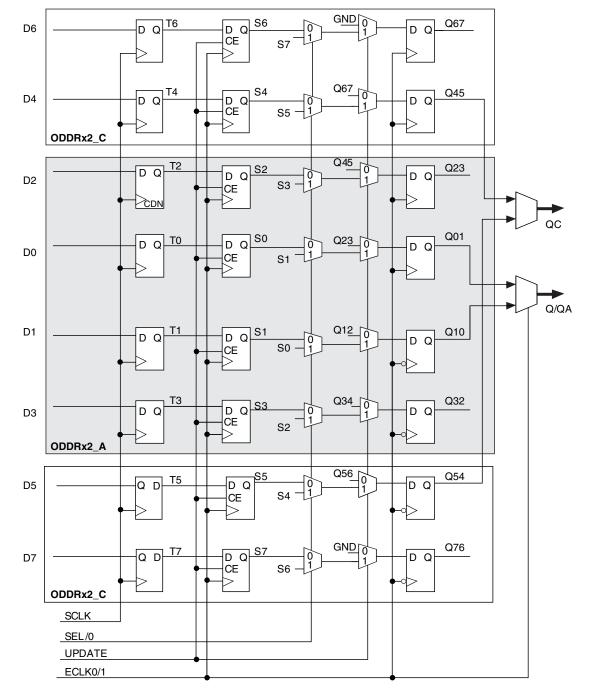

These gearboxes have three stage pipeline registers. The first stage registers sample the high-speed input data by the high-speed edge clock on its rising and falling edges. The second stage registers perform data alignment based on the control signals UPDATE and SEL0 from the control block. The third stage pipeline registers pass the data to the device core synchronized to the low-speed system clock. Figure 2-13 shows a block diagram of the input gearbox.

### Figure 2-13. Input Gearbox

More information on the input gearbox is available in TN1281, Implementing High-Speed Interfaces with MachXO3 Devices.

### Figure 2-14. Output Gearbox

More information on the output gearbox is available in TN1281, Implementing High-Speed Interfaces with MachXO3 Devices.

### sysIO Buffer

Each I/O is associated with a flexible buffer referred to as a sysIO buffer. These buffers are arranged around the periphery of the device in groups referred to as banks. The sysIO buffers allow users to implement a wide variety of standards that are found in today's systems including LVCMOS, TTL, PCI, LVDS, BLVDS, MLVDS and LVPECL.

Each bank is capable of supporting multiple I/O standards. In the MachXO3L/LF devices, single-ended output buffers, ratioed input buffers (LVTTL, LVCMOS and PCI), differential (LVDS) input buffers are powered using I/O supply voltage ( $V_{CCIO}$ ). Each sysIO bank has its own  $V_{CCIO}$ .

MachXO3L/LF devices contain three types of sysIO buffer pairs.

#### 1. Left and Right sysIO Buffer Pairs

The sysIO buffer pairs in the left and right banks of the device consist of two single-ended output drivers and two single-ended input buffers (for ratioed inputs such as LVCMOS and LVTTL). The I/O pairs on the left and right of the devices also have differential input buffers.

#### 2. Bottom sysIO Buffer Pairs

The sysIO buffer pairs in the bottom bank of the device consist of two single-ended output drivers and two single-ended input buffers (for ratioed inputs such as LVCMOS and LVTTL). The I/O pairs on the bottom also have differential input buffers. Only the I/Os on the bottom banks have programmable PCI clamps and differential input termination. The PCI clamp is enabled after  $V_{CC}$  and  $V_{CCIO}$  are at valid operating levels and the device has been configured.

#### 3. Top sysIO Buffer Pairs

The sysIO buffer pairs in the top bank of the device consist of two single-ended output drivers and two singleended input buffers (for ratioed inputs such as LVCMOS and LVTTL). The I/O pairs on the top also have differential I/O buffers. Half of the sysIO buffer pairs on the top edge have true differential outputs. The sysIO buffer pair comprising of the A and B PIOs in every PIC on the top edge have a differential output driver.

### Typical I/O Behavior During Power-up

The internal power-on-reset (POR) signal is deactivated when  $V_{CC}$  and  $V_{CCIO0}$  have reached  $V_{PORUP}$  level defined in the Power-On-Reset Voltage table in the DC and Switching Characteristics section of this data sheet. After the POR signal is deactivated, the FPGA core logic becomes active. It is the user's responsibility to ensure that all  $V_{CCIO}$  banks are active with valid input logic levels to properly control the output logic states of all the I/O banks that are critical to the application. The default configuration of the I/O pins in a blank device is tri-state with a weak pulldown to GND (some pins such as PROGRAMN and the JTAG pins have weak pull-up to  $V_{CCIO}$  as the default functionality). The I/O pins will maintain the blank configuration until  $V_{CC}$  and  $V_{CCIO}$  (for I/O banks containing configuration I/Os) have reached  $V_{PORUP}$  levels at which time the I/Os will take on the user-configured settings only after a proper download/configuration.

There are various ways a user can ensure that there are no spurious signals on critical outputs as the device powers up. These are discussed in more detail in TN1280, MachXO3 sysIO Usage Guide.

### **Supported Standards**

The MachXO3L/LF sysIO buffer supports both single-ended and differential standards. Single-ended standards can be further subdivided into LVCMOS, LVTTL, and PCI. The buffer supports the LVTTL, PCI, LVCMOS 1.2 V, 1.5 V, 1.8 V, 2.5 V, and 3.3 V standards. In the LVCMOS and LVTTL modes, the buffer has individually configurable options for drive strength, bus maintenance (weak pull-up, weak pull-down, bus-keeper latch or none) and open drain. BLVDS, MLVDS and LVPECL output emulation is supported on all devices. The MachXO3L/LF devices support on-chip LVDS output buffers on approximately 50% of the I/Os on the top bank. Differential receivers for LVDS, BLVDS, MLVDS and LVPECL are supported on all banks of MachXO3L/LF devices. PCI support is provided in the bottom bank of the MachXO3L/LF devices. Table 2-11 summarizes the I/O characteristics of the MachXO3L/LF PLDs.

### Hot Socketing

The MachXO3L/LF devices have been carefully designed to ensure predictable behavior during power-up and power-down. Leakage into I/O pins is controlled to within specified limits. This allows for easy integration with the rest of the system. These capabilities make the MachXO3L/LF ideal for many multiple power supply and hot-swap applications.

### **On-chip Oscillator**

Every MachXO3L/LF device has an internal CMOS oscillator. The oscillator output can be routed as a clock to the clock tree or as a reference clock to the sysCLOCK PLL using general routing resources. The oscillator frequency can be divided by internal logic. There is a dedicated programming bit and a user input to enable/disable the oscillator. The oscillator frequency ranges from 2.08 MHz to 133 MHz. The software default value of the Master Clock (MCLK) is nominally 2.08 MHz. When a different MCLK is selected during the design process, the following sequence takes place:

- 1. Device powers up with a nominal MCLK frequency of 2.08 MHz.

- 2. During configuration, users select a different master clock frequency.

- 3. The MCLK frequency changes to the selected frequency once the clock configuration bits are received.

- 4. If the user does not select a master clock frequency, then the configuration bitstream defaults to the MCLK frequency of 2.08 MHz.

Table 2-13 lists all the available MCLK frequencies.

#### Table 2-13. Available MCLK Frequencies

| MCLK (MHz, Nominal) | MCLK (MHz, Nominal) | MCLK (MHz, Nominal) |

|---------------------|---------------------|---------------------|

| 2.08 (default)      | 9.17                | 33.25               |

| 2.46                | 10.23               | 38                  |

| 3.17                | 13.3                | 44.33               |

| 4.29                | 14.78               | 53.2                |

| 5.54                | 20.46               | 66.5                |

| 7                   | 26.6                | 88.67               |

| 8.31                | 29.56               | 133                 |

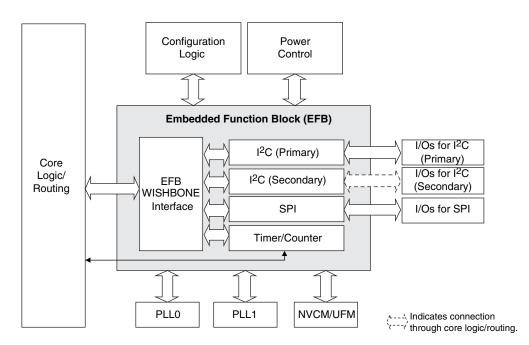

### **Embedded Hardened IP Functions**

All MachXO3L/LF devices provide embedded hardened functions such as SPI, I<sup>2</sup>C and Timer/Counter. MachXO3LF devices also provide User Flash Memory (UFM). These embedded blocks interface through the WISHBONE interface with routing as shown in Figure 2-17.

### Figure 2-17. Embedded Function Block Interface

### Hardened I<sup>2</sup>C IP Core

Every MachXO3L/LF device contains two  $I^2C$  IP cores. These are the primary and secondary  $I^2C$  IP cores. Either of the two cores can be configured either as an  $I^2C$  master or as an  $I^2C$  slave. The only difference between the two IP cores is that the primary core has pre-assigned I/O pins whereas users can assign I/O pins for the secondary core.

When the IP core is configured as a master it will be able to control other devices on the  $I^2C$  bus through the interface. When the core is configured as the slave, the device will be able to provide I/O expansion to an  $I^2C$  Master. The  $I^2C$  cores support the following functionality:

- Master and Slave operation

- 7-bit and 10-bit addressing

- Multi-master arbitration support

- Up to 400 kHz data transfer speed

- General call support

- Interface to custom logic through 8-bit WISHBONE interface

There are some limitations on the use of the hardened user SPI. These are defined in the following technical notes:

- TN1087, Minimizing System Interruption During Configuration Using TransFR Technology (Appendix B)

- TN1293, Using Hardened Control Functions in MachXO3 Devices

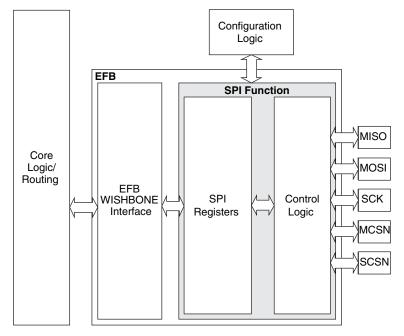

### Figure 2-19. SPI Core Block Diagram

Table 2-15 describes the signals interfacing with the SPI cores.

Table 2-15. SPI Core Signal Description

| Signal Name | I/O | Master/Slave | Description                                                                                                                                                                               |  |  |  |

|-------------|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| spi_csn[0]  | 0   | Master       | SPI master chip-select output                                                                                                                                                             |  |  |  |

| spi_csn[17] | 0   | Master       | Additional SPI chip-select outputs (total up to eight slaves)                                                                                                                             |  |  |  |

| spi_scsn    | I   | Slave        | SPI slave chip-select input                                                                                                                                                               |  |  |  |

| spi_irq     | 0   | Master/Slave | Interrupt request                                                                                                                                                                         |  |  |  |

| spi_clk     | I/O | Master/Slave | SPI clock. Output in master mode. Input in slave mode.                                                                                                                                    |  |  |  |

| spi_miso    | I/O | Master/Slave | SPI data. Input in master mode. Output in slave mode.                                                                                                                                     |  |  |  |

| spi_mosi    | I/O | Master/Slave | SPI data. Output in master mode. Input in slave mode.                                                                                                                                     |  |  |  |

| sn          | I   | Slave        | Configuration Slave Chip Select (active low), dedicated for selecting the Con-<br>figuration Logic.                                                                                       |  |  |  |

| cfg_stdby   | 0   | Master/Slave | Stand-by signal – To be connected only to the power module of the MachXO3L/LF device. The signal is enabled only if the "Wakeup Enable" feature has been set within the EFB GUI, SPI Tab. |  |  |  |

| cfg_wake    | О   | Master/Slave | Wake-up signal – To be connected only to the power module of the MachXO3L/LF device. The signal is enabled only if the "Wakeup Enable" feature has been set within the EFB GUI, SPI Tab.  |  |  |  |

### Table 2-17. MachXO3L/LF Power Saving Features Description

| Device Subsystem                               | Feature Description                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bandgap                                        | The bandgap can be turned off in standby mode. When the Bandgap is turned off, ana-<br>log circuitry such as the POR, PLLs, on-chip oscillator, and differential I/O buffers are<br>also turned off. Bandgap can only be turned off for 1.2 V devices.                                                                                       |

| Power-On-Reset (POR)                           | The POR can be turned off in standby mode. This monitors VCC levels. In the event of unsafe $V_{CC}$ drops, this circuit reconfigures the device. When the POR circuitry is turned off, limited power detector circuitry is still active. This option is only recommended for applications in which the power supply rails are reliable.     |

| On-Chip Oscillator                             | The on-chip oscillator has two power saving features. It may be switched off if it is not needed in your design. It can also be turned off in Standby mode.                                                                                                                                                                                  |

| PLL                                            | Similar to the on-chip oscillator, the PLL also has two power saving features. It can be statically switched off if it is not needed in a design. It can also be turned off in Standby mode. The PLL will wait until all output clocks from the PLL are driven low before powering off.                                                      |

| I/O Bank Controller                            | Differential I/O buffers (used to implement standards such as LVDS) consume more than ratioed single-ended I/Os such as LVCMOS and LVTTL. The I/O bank controller allows the user to turn these I/Os off dynamically on a per bank selection.                                                                                                |

| Dynamic Clock Enable for Primary<br>Clock Nets | Each primary clock net can be dynamically disabled to save power.                                                                                                                                                                                                                                                                            |

| Power Guard                                    | Power Guard is a feature implemented in input buffers. This feature allows users to switch off the input buffer when it is not needed. This feature can be used in both clock and data paths. Its biggest impact is that in the standby mode it can be used to switch off clock inputs that are distributed using general routing resources. |

For more details on the standby mode refer to TN1289, Power Estimation and Management for MachXO3 Devices.

### Power On Reset

MachXO3L/LF devices have power-on reset circuitry to monitor  $V_{CCINT}$  and  $V_{CCIO}$  voltage levels during power-up and operation. At power-up, the POR circuitry monitors  $V_{CCINT}$  and  $V_{CCIO}$  (controls configuration) voltage levels. It then triggers download from the on-chip configuration NVCM/Flash memory after reaching the  $V_{PORUP}$  level specified in the Power-On-Reset Voltage table in the DC and Switching Characteristics section of this data sheet. For "E" devices without voltage regulators,  $V_{CCINT}$  is the same as the  $V_{CC}$  supply voltage. For "C" devices with voltage regulators,  $V_{CCINT}$  is regulated from the  $V_{CC}$  supply voltage. From this voltage reference, the time taken for configuration and entry into user mode is specified as NVCM/Flash Download Time ( $t_{REFRESH}$ ) in the DC and Switching Characteristics section of this data sheet. Before and during configuration. Note that for "C" devices, a separate POR circuit monitors external  $V_{CC}$  voltage in addition to the POR circuit that monitors the internal post-regulated power supply voltage level.

Once the device enters into user mode, the POR circuitry can optionally continue to monitor  $V_{CCINT}$  levels. If  $V_{CCINT}$  drops below  $V_{PORDNBG}$  level (with the bandgap circuitry switched on) or below  $V_{PORDNSRAM}$  level (with the bandgap circuitry switched off to conserve power) device functionality cannot be guaranteed. In such a situation the POR issues a reset and begins monitoring the  $V_{CCINT}$  and  $V_{CCIO}$  voltage levels.  $V_{PORDNBG}$  and  $V_{PORDNSRAM}$  are both specified in the Power-On-Reset Voltage table in the DC and Switching Characteristics section of this data sheet.

Note that once an "E" device enters user mode, users can switch off the bandgap to conserve power. When the bandgap circuitry is switched off, the POR circuitry also shuts down. The device is designed such that a mini-mal, low power POR circuit is still operational (this corresponds to the  $V_{PORDNSRAM}$  reset point described in the paragraph above). However this circuit is not as accurate as the one that operates when the bandgap is switched on. The low power POR circuit emulates an SRAM cell and is biased to trip before the vast majority of SRAM cells flip. If users are concerned about the  $V_{CC}$  supply dropping below  $V_{CC}$  (min) they should not shut down the bandgap or POR circuit.

### LVDS Emulation

MachXO3L/LF devices can support LVDS outputs via emulation (LVDS25E). The output is emulated using complementary LVCMOS outputs in conjunction with resistors across the driver outputs on all devices. The scheme shown in Figure 3-1 is one possible solution for LVDS standard implementation. Resistor values in Figure 3-1 are industry standard values for 1% resistors.

Note: All resistors are ±1%.

### Table 3-1. LVDS25E DC Conditions

#### **Over Recommended Operating Conditions**

| Parameter         | Description                 | Тур.  | Units |  |  |  |  |  |

|-------------------|-----------------------------|-------|-------|--|--|--|--|--|

| Z <sub>OUT</sub>  | Output impedance            | 20    | Ohms  |  |  |  |  |  |

| R <sub>S</sub>    | Driver series resistor      | 158   | Ohms  |  |  |  |  |  |

| R <sub>P</sub>    | Driver parallel resistor    | 140   | Ohms  |  |  |  |  |  |

| R <sub>T</sub>    | Receiver termination        | 100   | Ohms  |  |  |  |  |  |

| V <sub>OH</sub>   | Output high voltage         | 1.43  | V     |  |  |  |  |  |

| V <sub>OL</sub>   | Output low voltage          | 1.07  | V     |  |  |  |  |  |

| V <sub>OD</sub>   | Output differential voltage | 0.35  | V     |  |  |  |  |  |

| V <sub>CM</sub>   | Output common mode voltage  | 1.25  | V     |  |  |  |  |  |

| Z <sub>BACK</sub> | Back impedance              | 100.5 | Ohms  |  |  |  |  |  |

| I <sub>DC</sub>   | DC output current           | 6.03  | mA    |  |  |  |  |  |

### Maximum sysIO Buffer Performance

| I/O Standard | Max. Speed | Units |

|--------------|------------|-------|

| MIPI         | 450        | MHz   |

| LVDS25       | 400        | MHz   |

| LVDS25E      | 150        | MHz   |

| BLVDS25      | 150        | MHz   |

| BLVDS25E     | 150        | MHz   |

| MLVDS25      | 150        | MHz   |

| MLVDS25E     | 150        | MHz   |

| LVPECL33     | 150        | MHz   |

| LVPECL33E    | 150        | MHz   |

| LVTTL33      | 150        | MHz   |

| LVTTL33D     | 150        | MHz   |

| LVCMOS33     | 150        | MHz   |

| LVCMOS33D    | 150        | MHz   |

| LVCMOS25     | 150        | MHz   |

| LVCMOS25D    | 150        | MHz   |

| LVCMOS18     | 150        | MHz   |

| LVCMOS18D    | 150        | MHz   |

| LVCMOS15     | 150        | MHz   |

| LVCMOS15D    | 150        | MHz   |

| LVCMOS12     | 91         | MHz   |

| LVCMOS12D    | 91         | MHz   |

## MachXO3L/LF External Switching Characteristics – C/E Devices<sup>1, 2, 3, 4, 5, 6, 10</sup>

|                                    |                                                  |                         | _     | 6    | -     | 5        |       |  |

|------------------------------------|--------------------------------------------------|-------------------------|-------|------|-------|----------|-------|--|

| Parameter                          | Description                                      | Device                  | Min.  | Max. | Min.  | Max.     | Units |  |

| Clocks                             |                                                  | I                       |       |      |       |          |       |  |

| Primary Clo                        | ocks                                             |                         |       |      |       |          |       |  |

| f <sub>MAX_PRI</sub> <sup>7</sup>  | Frequency for Primary Clock Tree                 | All MachXO3L/LF devices |       | 388  | —     | 323      | MHz   |  |

| t <sub>W_PRI</sub>                 | Clock Pulse Width for Primary Clock              | All MachXO3L/LF devices | 0.5   | _    | 0.6   |          | ns    |  |

|                                    |                                                  | MachXO3L/LF-1300        | _     | 867  | —     | 897      | ps    |  |

|                                    |                                                  | MachXO3L/LF-2100        |       | 867  | _     | 897      | ps    |  |

| t <sub>SKEW_PRI</sub>              | Primary Clock Skew Within a Device               | MachXO3L/LF-4300        |       | 865  | _     | 892      | ps    |  |

| 0.12.1                             |                                                  | MachXO3L/LF-6900        |       | 902  | _     | 942      | ps    |  |

|                                    |                                                  | MachXO3L/LF-9400        | _     | 908  | _     | 950      | ps    |  |

| Edge Clock                         |                                                  |                         |       |      |       |          |       |  |

| f <sub>MAX_EDGE</sub> <sup>7</sup> |                                                  | MachXO3L/LF             |       | 400  | _     | 333      | MHz   |  |

| _                                  |                                                  |                         |       |      |       |          |       |  |

| t <sub>PD</sub>                    | Best case propagation delay through one<br>LUT-4 | All MachXO3L/LF devices | _     | 6.72 | _     | 6.96     | ns    |  |

| General I/O                        | Pin Parameters (Using Primary Clock with         | out PLL)                |       | I    |       |          | 1     |  |

|                                    |                                                  | MachXO3L/LF-1300        | —     | 7.46 | _     | 7.66     | ns    |  |

|                                    |                                                  | MachXO3L/LF-2100        | _     | 7.46 | —     | 7.66     | ns    |  |

| t <sub>CO</sub>                    | Clock to Output - PIO Output Register            | MachXO3L/LF-4300        | _     | 7.51 | _     | 7.71     | ns    |  |

| -00                                |                                                  | MachXO3L/LF-6900        | _     | 7.54 | _     | 7.75     | ns    |  |

|                                    |                                                  | MachXO3L/LF-9400        | _     | 7.53 | _     | 7.83     | ns    |  |

|                                    |                                                  | MachXO3L/LF-1300        | -0.20 |      | -0.20 | —        | ns    |  |

|                                    |                                                  | MachXO3L/LF-2100        | -0.20 |      | -0.20 |          | ns    |  |

| t <sub>SU</sub>                    | Clock to Data Setup - PIO Input Register         | MachXO3L/LF-4300        | -0.23 |      | -0.23 |          | ns    |  |

|                                    |                                                  | MachXO3L/LF-6900        | -0.23 | _    | -0.23 |          | ns    |  |

|                                    |                                                  | MachXO3L/LF-9400        | -0.24 |      | -0.24 | —        | ns    |  |

|                                    |                                                  | MachXO3L/LF-1300        | 1.89  |      | 2.13  |          | ns    |  |

|                                    |                                                  | MachXO3L/LF-2100        | 1.89  |      | 2.13  |          | ns    |  |

| t <sub>H</sub>                     | Clock to Data Hold - PIO Input Register          | MachXO3L/LF-4300        | 1.94  | _    | 2.18  | _        | ns    |  |

|                                    | s                                                | MachXO3L/LF-6900        | 1.98  |      | 2.23  |          | ns    |  |

|                                    |                                                  | MachXO3L/LF-9400        | 1.99  |      | 2.24  |          | ns    |  |

|                                    |                                                  | MachXO3L/LF-1300        | 1.61  |      | 1.76  |          | ns    |  |

|                                    |                                                  | MachXO3L/LF-2100        | 1.61  |      | 1.76  |          | ns    |  |

| t <sub>SU_DEL</sub>                |                                                  | MachXO3L/LF-4300        | 1.66  | _    | 1.81  | _        | ns    |  |

| 00_DEE                             |                                                  | MachXO3L/LF-6900        | 1.53  | _    | 1.67  | _        | ns    |  |

|                                    |                                                  | MachXO3L/LF-9400        | 1.65  | _    | 1.80  | <u> </u> | ns    |  |

|                                    |                                                  | MachXO3L/LF-1300        | -0.23 | _    | -0.23 | _        | ns    |  |

|                                    |                                                  | MachXO3L/LF-2100        | -0.23 | _    | -0.23 | _        | ns    |  |

| t <sub>H_DEL</sub>                 |                                                  | MachXO3L/LF-4300        | -0.25 |      | -0.25 |          | ns    |  |

|                                    | Input Data Delay                                 | MachXO3L/LF-6900        | -0.21 |      | -0.21 |          | ns    |  |

|                                    |                                                  | MachXO3L/LF-9400        | -0.24 |      | -0.24 |          | ns    |  |

| f <sub>MAX_IO</sub>                | Clock Frequency of I/O and PEU Register          | All MachXO3L/LF devices |       | 388  |       | 323      | MHz   |  |

### Over Recommended Operating Conditions

### DC and Switching Characteristics MachXO3 Family Data Sheet

|                        |                                                                   |                  | -     | 6    | -     | ·5                                                                         |       |

|------------------------|-------------------------------------------------------------------|------------------|-------|------|-------|----------------------------------------------------------------------------|-------|

| Parameter              | Description                                                       | Device           | Min.  | Max. | Min.  | Max.                                                                       | Units |

|                        |                                                                   | MachXO3L/LF-1300 | 2.87  | _    | 3.18  | —                                                                          | ns    |

|                        |                                                                   | MachXO3L/LF-2100 | 2.87  |      | 3.18  | —                                                                          | ns    |

| t <sub>SU_DELPLL</sub> | Clock to Data Setup - PIO Input Register<br>with Data Input Delay | MachXO3L/LF-4300 | 2.96  |      | 3.28  | —                                                                          | ns    |

|                        | with Data input Delay                                             | MachXO3L/LF-6900 | 3.05  | _    | 3.35  | —                                                                          | ns    |

|                        |                                                                   | MachXO3L/LF-9400 | 3.06  |      | 3.37  | 5<br>Max.<br>—<br>—<br>—<br>—<br>—<br>—<br>—<br>—<br>—<br>—<br>—<br>—<br>— | ns    |

|                        |                                                                   | MachXO3L/LF-1300 | -0.83 |      | -0.83 | —                                                                          | ns    |

|                        |                                                                   | MachXO3L/LF-2100 | -0.83 |      | -0.83 | —                                                                          | ns    |

| t <sub>H_DELPLL</sub>  | Clock to Data Hold - PIO Input Register with<br>Input Data Delay  | MachXO3L/LF-4300 | -0.87 |      | -0.87 | —                                                                          | ns    |

|                        |                                                                   | MachXO3L/LF-6900 | -0.91 | —    | -0.91 | —                                                                          | ns    |

|                        |                                                                   | MachXO3L/LF-9400 | -0.93 | —    | -0.93 | —                                                                          | ns    |

### DC and Switching Characteristics MachXO3 Family Data Sheet

|                                  |                                                                                    |                                                             | -        | -6      | -     | 5     |       |

|----------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------|----------|---------|-------|-------|-------|

| Parameter                        | Description                                                                        | Device                                                      | Min.     | Max.    | Min.  | Max.  | Units |

|                                  | DRX4 Outputs with Clock and Data Centere X.ECLK.Centered <sup>8, 9</sup>           | d at Pin Using PCLK Pin f                                   | or Clock | Input – |       |       |       |

| t <sub>DVB</sub>                 | Output Data Valid Before CLK Output                                                |                                                             | 0.455    | —       | 0.570 |       | ns    |

| t <sub>DVA</sub>                 | Output Data Valid After CLK Output                                                 | 7                                                           | 0.455    | —       | 0.570 | —     | ns    |

| f <sub>DATA</sub>                | DDRX4 Serial Output Data Speed                                                     | MachXO3L/LF devices,                                        | —        | 800     |       | 630   | Mbps  |

| f <sub>DDRX4</sub>               | DDRX4 ECLK Frequency<br>(minimum limited by PLL)                                   | top side only                                               | _        | 400     | _     | 315   | MHz   |

| f <sub>SCLK</sub>                | SCLK Frequency                                                                     | _                                                           | —        | 100     | —     | 79    | MHz   |

| 7:1 LVDS 0                       | outputs – GDDR71_TX.ECLK.7:1 <sup>8,9</sup>                                        |                                                             | •        | •       |       |       |       |

| t <sub>DIB</sub>                 | Output Data Invalid Before CLK Output                                              | MachXO3L/LF devices,<br>top side only                       | —        | 0.160   |       | 0.180 | ns    |

| t <sub>DIA</sub>                 | Output Data Invalid After CLK Output                                               |                                                             | —        | 0.160   | —     | 0.180 | ns    |

| f <sub>DATA</sub>                | DDR71 Serial Output Data Speed                                                     |                                                             | —        | 756     | —     | 630   | Mbps  |

| f <sub>DDR71</sub>               | DDR71 ECLK Frequency                                                               |                                                             | —        | 378     |       | 315   | MHz   |

| f <sub>CLKOUT</sub>              | 7:1 Output Clock Frequency (SCLK) (mini-<br>mum limited by PLL)                    |                                                             | _        | 108     | _     | 90    | MHz   |

|                                  | Outputs with Clock and Data Centered at F<br>X.ECLK.Centered <sup>10, 11, 12</sup> | in Using PCLK Pin for Clo                                   | ck Input | -       |       |       |       |

| t <sub>DVB</sub>                 | Output Data Valid Before CLK Output                                                |                                                             | 0.200    | —       | 0.200 |       | UI    |

| t <sub>DVA</sub>                 | Output Data Valid After CLK Output                                                 |                                                             | 0.200    | —       | 0.200 |       | UI    |

| f <sub>DATA</sub> <sup>14</sup>  | MIPI D-PHY Output Data Speed                                                       | All MachXO3L/LF                                             | —        | 900     |       | 900   | Mbps  |

| f <sub>DDRX4</sub> <sup>14</sup> | MIPI D-PHY ECLK Frequency (minimum limited by PLL)                                 | top side only<br>mini-<br>d at Pin Using PCLK Pin for Clock | _        | 450     | —     | 450   | MHz   |

| f <sub>SCLK</sub> <sup>14</sup>  | SCLK Frequency                                                                     | 1                                                           | —        | 112.5   | —     | 112.5 | MHz   |

1. Exact performance may vary with device and design implementation. Commercial timing numbers are shown at 85 °C and 1.14 V. Other operating conditions, including industrial, can be extracted from the Diamond software.

2. General I/O timing numbers based on LVCMOS 2.5, 8 mA, 0pf load, fast slew rate.

3. Generic DDR timing numbers based on LVDS I/O (for input, output, and clock ports).

4. 7:1 LVDS (GDDR71) uses the LVDS I/O standard (for input, output, and clock ports).

5. For Generic DDRX1 mode  $t_{SU} = t_{HO} = (t_{DVE} - t_{DVA} - 0.03 \text{ ns})/2$ .

6. The t<sub>SU DEL</sub> and t<sub>H DEL</sub> values use the SCLK\_ZERHOLD default step size. Each step is 105 ps (-6), 113 ps (-5), 120 ps (-4).

7. This number for general purpose usage. Duty cycle tolerance is +/-10%.

8. Duty cycle is  $\pm -5\%$  for system usage.

9. Performance is calculated with 0.225 UI.

10. Performance is calculated with 0.20 UI.

11. Performance for Industrial devices are only supported with VCC between 1.16 V to 1.24 V.

12. Performance for Industrial devices and -5 devices are not modeled in the Diamond design tool.

13. The above timing numbers are generated using the Diamond design tool. Exact performance may vary with the device selected.

14. Above 800 Mbps is only supported with WLCSP and csfBGA packages

15. Between 800 Mbps to 900 Mbps:

a. VIDTH exceeds the MIPI D-PHY Input DC Conditions Table 3-4 and can be calculated with the equation tSU or tH = -0.0005\*VIDTH + 0.3284

b. Example calculations

i. tSU and tHO = 0.28 with VIDTH = 100 mV

ii. tSU and tHO = 0.25 with VIDTH = 170 mV

iii. tSU and tHO = 0.20 with VIDTH = 270 mV

| Part Number               | LUTs | Supply Voltage | Speed | Package             | Leads | Temp.                                 |

|---------------------------|------|----------------|-------|---------------------|-------|---------------------------------------|

| LCMXO3L-2100E-6MG324I     | 2100 | 1.2 V          | 6     | Halogen-Free csfBGA | 324   | IND                                   |

| LCMXO3L-2100C-5BG256C     | 2100 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 256   | СОМ                                   |

| LCMXO3L-2100C-6BG256C     | 2100 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 256   | COM                                   |

| LCMXO3L-2100C-5BG256I     | 2100 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 256   | IND                                   |

| LCMXO3L-2100C-6BG256I     | 2100 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 256   | IND                                   |

| LCMXO3L-2100C-5BG324C     | 2100 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 324   | COM                                   |

| LCMXO3L-2100C-6BG324C     | 2100 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 324   | COM                                   |

| LCMXO3L-2100C-5BG324I     | 2100 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 324   | IND                                   |

| LCMXO3L-2100C-6BG324I     | 2100 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 324   | IND                                   |

|                           |      |                |       | ·                   |       | · · · · · · · · · · · · · · · · · · · |

| Part Number               | LUTs | Supply Voltage | Speed | Package             | Leads | Temp.                                 |

| LCMXO3L-4300E-5UWG81CTR   | 4300 | 1.2 V          | 5     | Halogen-Free WLCSP  | 81    | COM                                   |

| LCMXO3L-4300E-5UWG81CTR50 | 4300 | 1.2 V          | 5     | Halogen-Free WLCSP  | 81    | COM                                   |

| LCMXO3L-4300E-5UWG81CTR1K | 4300 | 1.2 V          | 5     | Halogen-Free WLCSP  | 81    | COM                                   |

| LCMXO3L-4300E-5UWG81ITR   | 4300 | 1.2 V          | 5     | Halogen-Free WLCSP  | 81    | IND                                   |

| LCMXO3L-4300E-5UWG81ITR50 | 4300 | 1.2 V          | 5     | Halogen-Free WLCSP  | 81    | IND                                   |

| LCMXO3L-4300E-5UWG81ITR1K | 4300 | 1.2 V          | 5     | Halogen-Free WLCSP  | 81    | IND                                   |

| LCMXO3L-4300E-5MG121C     | 4300 | 1.2 V          | 5     | Halogen-Free csfBGA | 121   | COM                                   |

| LCMXO3L-4300E-6MG121C     | 4300 | 1.2 V          | 6     | Halogen-Free csfBGA | 121   | COM                                   |

| LCMXO3L-4300E-5MG121I     | 4300 | 1.2 V          | 5     | Halogen-Free csfBGA | 121   | IND                                   |

| LCMXO3L-4300E-6MG121I     | 4300 | 1.2 V          | 6     | Halogen-Free csfBGA | 121   | IND                                   |

| LCMXO3L-4300E-5MG256C     | 4300 | 1.2 V          | 5     | Halogen-Free csfBGA | 256   | COM                                   |

| LCMXO3L-4300E-6MG256C     | 4300 | 1.2 V          | 6     | Halogen-Free csfBGA | 256   | COM                                   |

| LCMXO3L-4300E-5MG256I     | 4300 | 1.2 V          | 5     | Halogen-Free csfBGA | 256   | IND                                   |

| LCMXO3L-4300E-6MG256I     | 4300 | 1.2 V          | 6     | Halogen-Free csfBGA | 256   | IND                                   |

| LCMXO3L-4300E-5MG324C     | 4300 | 1.2 V          | 5     | Halogen-Free csfBGA | 324   | COM                                   |

| LCMXO3L-4300E-6MG324C     | 4300 | 1.2 V          | 6     | Halogen-Free csfBGA | 324   | COM                                   |

| LCMXO3L-4300E-5MG324I     | 4300 | 1.2 V          | 5     | Halogen-Free csfBGA | 324   | IND                                   |

| LCMXO3L-4300E-6MG324I     | 4300 | 1.2 V          | 6     | Halogen-Free csfBGA | 324   | IND                                   |

| LCMXO3L-4300C-5BG256C     | 4300 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 256   | COM                                   |

| LCMXO3L-4300C-6BG256C     | 4300 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 256   | COM                                   |

| LCMXO3L-4300C-5BG256I     | 4300 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 256   | IND                                   |

| LCMXO3L-4300C-6BG256I     | 4300 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 256   | IND                                   |

| LCMXO3L-4300C-5BG324C     | 4300 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 324   | COM                                   |

| LCMXO3L-4300C-6BG324C     | 4300 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 324   | СОМ                                   |

| LCMXO3L-4300C-5BG324I     | 4300 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 324   | IND                                   |

| LCMXO3L-4300C-6BG324I     | 4300 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 324   | IND                                   |

| LCMXO3L-4300C-5BG400C     | 4300 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 400   | СОМ                                   |

| LCMXO3L-4300C-6BG400C     | 4300 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 400   | СОМ                                   |

| LCMXO3L-4300C-5BG400I     | 4300 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 400   | IND                                   |

| LCMXO3L-4300C-6BG400I     | 4300 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 400   | IND                                   |

| Part Number            | LUTs | Supply Voltage | Speed | Package             | Leads | Temp. |

|------------------------|------|----------------|-------|---------------------|-------|-------|

| LCMXO3LF-6900E-5MG256C | 6900 | 1.2 V          | 5     | Halogen-Free csfBGA | 256   | COM   |

| LCMXO3LF-6900E-6MG256C | 6900 | 1.2 V          | 6     | Halogen-Free csfBGA | 256   | COM   |

| LCMXO3LF-6900E-5MG256I | 6900 | 1.2 V          | 5     | Halogen-Free csfBGA | 256   | IND   |

| LCMXO3LF-6900E-6MG256I | 6900 | 1.2 V          | 6     | Halogen-Free csfBGA | 256   | IND   |

| LCMXO3LF-6900E-5MG324C | 6900 | 1.2 V          | 5     | Halogen-Free csfBGA | 324   | COM   |

| LCMXO3LF-6900E-6MG324C | 6900 | 1.2 V          | 6     | Halogen-Free csfBGA | 324   | COM   |

| LCMXO3LF-6900E-5MG324I | 6900 | 1.2 V          | 5     | Halogen-Free csfBGA | 324   | IND   |

| LCMXO3LF-6900E-6MG324I | 6900 | 1.2 V          | 6     | Halogen-Free csfBGA | 324   | IND   |

| LCMXO3LF-6900C-5BG256C | 6900 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 256   | COM   |

| LCMXO3LF-6900C-6BG256C | 6900 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 256   | COM   |

| LCMXO3LF-6900C-5BG256I | 6900 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 256   | IND   |

| LCMXO3LF-6900C-6BG256I | 6900 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 256   | IND   |

| LCMXO3LF-6900C-5BG324C | 6900 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 324   | COM   |

| LCMXO3LF-6900C-6BG324C | 6900 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 324   | COM   |

| LCMXO3LF-6900C-5BG324I | 6900 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 324   | IND   |

| LCMXO3LF-6900C-6BG324I | 6900 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 324   | IND   |

| LCMXO3LF-6900C-5BG400C | 6900 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 400   | COM   |

| LCMXO3LF-6900C-6BG400C | 6900 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 400   | COM   |

| LCMXO3LF-6900C-5BG400I | 6900 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 400   | IND   |

| LCMXO3LF-6900C-6BG400I | 6900 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 400   | IND   |

|                        |      |                |       |                     |       |       |

| Part Number            | LUTs | Supply Voltage | Speed | Package             | Leads | Temp. |

| LCMXO3LF-9400E-5MG256C | 9400 | 1.2 V          | 5     | Halogen-Free csfBGA | 256   | COM   |

| LCMXO3LF-9400E-6MG256C | 9400 | 1.2 V          | 6     | Halogen-Free csfBGA | 256   | COM   |

| LCMXO3LF-9400E-5MG256I | 9400 | 1.2 V          | 5     | Halogen-Free csfBGA | 256   | IND   |

| LCMXO3LF-9400E-6MG256I | 9400 | 1.2 V          | 6     | Halogen-Free csfBGA | 256   | IND   |

| LCMXO3LF-9400C-5BG256C | 9400 | 2.5 V/3.3 V    | 5     | Halogen-Free caBGA  | 256   | COM   |

| LCMXO3LF-9400C-6BG256C | 9400 | 2.5 V/3.3 V    | 6     | Halogen-Free caBGA  | 256   | COM   |

| LCMXO3LF-9400C-5BG256I | 9400 | 2.5 V/3.3 V    | 5     | Halogen-Free caBGA  | 256   | IND   |

| LCMXO3LF-9400C-6BG256I | 9400 | 2.5 V/3.3 V    | 6     | Halogen-Free caBGA  | 256   | IND   |

| LCMXO3LF-9400C-5BG400C | 9400 | 2.5 V/3.3 V    | 5     | Halogen-Free caBGA  | 400   | COM   |

| LCMXO3LF-9400C-6BG400C | 9400 | 2.5 V/3.3 V    | 6     | Halogen-Free caBGA  | 400   | COM   |

| LCMXO3LF-9400C-5BG400I | 9400 | 2.5 V/3.3 V    | 5     | Halogen-Free caBGA  | 400   | IND   |

| LCMXO3LF-9400C-6BG400I | 9400 | 2.5 V/3.3 V    | 6     | Halogen-Free caBGA  | 400   | IND   |

| LCMXO3LF-9400C-5BG484C | 9400 | 2.5 V/3.3 V    | 5     | Halogen-Free caBGA  | 484   | COM   |

| LCMXO3LF-9400C-6BG484C | 9400 | 2.5 V/3.3 V    | 6     | Halogen-Free caBGA  | 484   | COM   |

| LCMXO3LF-9400C-5BG484I | 9400 | 2.5 V/3.3 V    | 5     | Halogen-Free caBGA  | 484   | IND   |

| LCMXO3LF-9400C-6BG484I | 9400 | 2.5 V/3.3 V    | 6     | Halogen-Free caBGA  | 484   | IND   |

| Date           | Version | Section                                                                                                                            | Change Summary                                                                                                                                                                                                                                                                            |

|----------------|---------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| April 2016 1.6 | 1.6     | Introduction                                                                                                                       | Updated Features section.<br>— Revised logic density range and IO to LUT ratio under Flexible Archi-<br>tecture.<br>— Revised 0.8 mm pitch information under Advanced Packaging.<br>— Added MachXO3L-9400/MachXO3LF-9400 information to Table 1-1,<br>MachXO3L/LF Family Selection Guide. |

|                |         | Updated Introduction section.<br>— Changed density from 6900 to 9400 LUTs.<br>— Changed caBGA packaging to 19 x 19 mm.             |                                                                                                                                                                                                                                                                                           |

|                |         | Architecture                                                                                                                       | Updated Architecture Overview section.<br>— Changed statement to "All logic density devices in this family"<br>— Updated Figure 2-2 heading and notes.                                                                                                                                    |

|                |         |                                                                                                                                    | Updated sysCLOCK Phase Locked Loops (PLLs) section.<br>— Changed statement to "All MachXO3L/LF devices have one or more<br>sysCLOCK PLL."                                                                                                                                                 |

|                |         | Updated Programmable I/O Cells (PIC) section.<br>— Changed statement to "All PIO pairs can implement differential receiv-<br>ers." |                                                                                                                                                                                                                                                                                           |

|                |         |                                                                                                                                    | Updated sysIO Buffer Banks section. Updated Figure 2-5 heading.                                                                                                                                                                                                                           |

|                |         |                                                                                                                                    | Updated Device Configuration section. Added Password and Soft Error Correction.                                                                                                                                                                                                           |

|                |         | DC and Switching<br>Characteristics                                                                                                | Updated Static Supply Current – C/E Devices section. Added LCMXO3L/<br>LF-9400C and LCMXO3L/LF-9400E devices.                                                                                                                                                                             |

|                |         |                                                                                                                                    | Updated Programming and Erase Supply Current – C/E Devices section.<br>— Added LCMXO3L/LF-9400C and LCMXO3L/LF-9400E devices.<br>— Changed LCMXO3L/LF-640E and LCMXO3L/LF-1300E Typ. values.                                                                                              |

|                |         |                                                                                                                                    | Updated MachXO3L/LF External Switching Characteristics – C/E<br>Devices section. Added MachXO3L/LF-9400 devices.                                                                                                                                                                          |

|                |         |                                                                                                                                    | Updated NVCM/Flash Download Time section. Added LCMXO3L/LF-<br>9400C device.                                                                                                                                                                                                              |

|                |         |                                                                                                                                    | Updated sysCONFIG Port Timing Specifications section.<br>— Added LCMXO3L/LF-9400C device.<br>— Changed t <sub>INITL</sub> units to from ns to us.<br>— Changed t <sub>DPPINIT</sub> and t <sub>DPPDONE</sub> Max. values are per PCN#03A-16.                                              |

|                |         | Pinout Information                                                                                                                 | Updated Pin Information Summary section. Added LCMXO3L/LF-9400C device.                                                                                                                                                                                                                   |

|                |         | Ordering Information                                                                                                               | Updated MachXO3 Part Number Description section.<br>— Added 9400 = 9400 LUTs.<br>— Added BG484 package.                                                                                                                                                                                   |

|                |         |                                                                                                                                    | Updated MachXO3L Ultra Low Power Commercial and Industrial Grade Devices, Halogen Free (RoHS) Packaging section. Added LCMXO3L-9400C part numbers.                                                                                                                                        |

|                |         |                                                                                                                                    | Updated MachXO3LF Ultra Low Power Commercial and Industrial Grade Devices, Halogen Free (RoHS) Packaging section. Added LCMXO3L-9400C part numbers.                                                                                                                                       |