# E · / Fattice Semiconductor Corporation - <u>LCMXO3L-9400C-6BG400I Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| 2014                           |                                                                                  |

|--------------------------------|----------------------------------------------------------------------------------|

| Product Status                 | Active                                                                           |

| Number of LABs/CLBs            | 1175                                                                             |

| Number of Logic Elements/Cells | 9400                                                                             |

| Total RAM Bits                 | 442368                                                                           |

| Number of I/O                  | 335                                                                              |

| Number of Gates                | -                                                                                |

| Voltage - Supply               | 2.375V ~ 3.465V                                                                  |

| Mounting Type                  | Surface Mount                                                                    |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                               |

| Package / Case                 | 400-LFBGA                                                                        |

| Supplier Device Package        | 400-CABGA (17x17)                                                                |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lcmxo3l-9400c-6bg400i |

|                                |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

and oscillators dynamically. These features help manage static and dynamic power consumption resulting in low static power for all members of the family.

The MachXO3L/LF devices are available in two versions C and E with two speed grades: -5 and -6, with -6 being the fastest. C devices have an internal linear voltage regulator which supports external VCC supply voltages of 3.3 V or 2.5 V. E devices only accept 1.2 V as the external VCC supply voltage. With the exception of power supply voltage both C and E are functionally compatible with each other.

The MachXO3L/LF PLDs are available in a broad range of advanced halogen-free packages ranging from the space saving 2.5 x 2.5 mm WLCSP to the 19 x 19 mm caBGA. MachXO3L/LF devices support density migration within the same package. Table 1-1 shows the LUT densities, package and I/O options, along with other key parameters.

The MachXO3L/LF devices offer enhanced I/O features such as drive strength control, slew rate control, PCI compatibility, bus-keeper latches, pull-up resistors, pull-down resistors, open drain outputs and hot socketing. Pull-up, pull-down and bus-keeper features are controllable on a "per-pin" basis.

A user-programmable internal oscillator is included in MachXO3L/LF devices. The clock output from this oscillator may be divided by the timer/counter for use as clock input in functions such as LED control, key-board scanner and similar state machines.

The MachXO3L/LF devices also provide flexible, reliable and secure configuration from on-chip NVCM/Flash. These devices can also configure themselves from external SPI Flash or be configured by an external master through the JTAG test access port or through the I<sup>2</sup>C port. Additionally, MachXO3L/LF devices support dual-boot capability (using external Flash memory) and remote field upgrade (TransFR) capability.

Lattice provides a variety of design tools that allow complex designs to be efficiently implemented using the MachXO3L/LF family of devices. Popular logic synthesis tools provide synthesis library support for MachXO3L/LF. Lattice design tools use the synthesis tool output along with the user-specified preferences and constraints to place and route the design in the MachXO3L/LF device. These tools extract the timing from the routing and back-annotate it into the design for timing verification.

Lattice provides many pre-engineered IP (Intellectual Property) LatticeCORE<sup>™</sup> modules, including a number of reference designs licensed free of charge, optimized for the MachXO3L/LF PLD family. By using these configurable soft core IP cores as standardized blocks, users are free to concentrate on the unique aspects of their design, increasing their productivity.

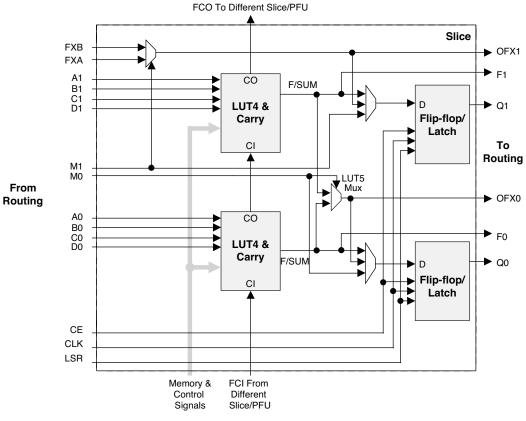

#### Figure 2-4. Slice Diagram

For Slices 0 and 1, memory control signals are generated from Slice 2 as follows:

- WCK is CLK

WRE is from LSR

- DI[3:2] for Slice 1 and DI[1:0] for Slice 0 data from Slice 2

- WAD [A:D] is a 4-bit address from slice 2 LUT input

Table 2-2. Slice Signal Descriptions

| Function | Туре             | Signal Names   | Description                                                          |

|----------|------------------|----------------|----------------------------------------------------------------------|

| Input    | Data signal      | A0, B0, C0, D0 | Inputs to LUT4                                                       |

| Input    | Data signal      | A1, B1, C1, D1 | Inputs to LUT4                                                       |

| Input    | Multi-purpose    | M0/M1          | Multi-purpose input                                                  |

| Input    | Control signal   | CE             | Clock enable                                                         |

| Input    | Control signal   | LSR            | Local set/reset                                                      |

| Input    | Control signal   | CLK            | System clock                                                         |

| Input    | Inter-PFU signal | FCIN           | Fast carry in <sup>1</sup>                                           |

| Output   | Data signals     | F0, F1         | LUT4 output register bypass signals                                  |

| Output   | Data signals     | Q0, Q1         | Register outputs                                                     |

| Output   | Data signals     | OFX0           | Output of a LUT5 MUX                                                 |

| Output   | Data signals     | OFX1           | Output of a LUT6, LUT7, LUT8 <sup>2</sup> MUX depending on the slice |

| Output   | Inter-PFU signal | FCO            | Fast carry out <sup>1</sup>                                          |

1. See Figure 2-3 for connection details.

2. Requires two PFUs.

#### Modes of Operation

Each slice has up to four potential modes of operation: Logic, Ripple, RAM and ROM.

#### Logic Mode

In this mode, the LUTs in each slice are configured as 4-input combinatorial lookup tables. A LUT4 can have 16 possible input combinations. Any four input logic functions can be generated by programming this lookup table. Since there are two LUT4s per slice, a LUT5 can be constructed within one slice. Larger look-up tables such as LUT6, LUT7 and LUT8 can be constructed by concatenating other slices. Note LUT8 requires more than four slices.

#### **Ripple Mode**

Ripple mode supports the efficient implementation of small arithmetic functions. In Ripple mode, the following functions can be implemented by each slice:

- Addition 2-bit

- Subtraction 2-bit

- Add/subtract 2-bit using dynamic control

- Up counter 2-bit

- Down counter 2-bit

- Up/down counter with asynchronous clear

- Up/down counter with preload (sync)

- Ripple mode multiplier building block

- Multiplier support

- Comparator functions of A and B inputs

- A greater-than-or-equal-to B

- A not-equal-to B

- A less-than-or-equal-to B

Ripple mode includes an optional configuration that performs arithmetic using fast carry chain methods. In this configuration (also referred to as CCU2 mode) two additional signals, Carry Generate and Carry Propagate, are generated on a per-slice basis to allow fast arithmetic functions to be constructed by concatenating slices.

#### **RAM Mode**

In this mode, a 16x4-bit distributed single port RAM (SPR) can be constructed by using each LUT block in Slice 0 and Slice 1 as a 16x1-bit memory. Slice 2 is used to provide memory address and control signals.

MachXO3L/LF devices support distributed memory initialization.

The Lattice design tools support the creation of a variety of different size memories. Where appropriate, the software will construct these using distributed memory primitives that represent the capabilities of the PFU. Table 2-3 shows the number of slices required to implement different distributed RAM primitives. For more information about using RAM in MachXO3L/LF devices, please see TN1290, Memory Usage Guide for MachXO3 Devices.

#### Table 2-3. Number of Slices Required For Implementing Distributed RAM

|                            | SPR 16x4         | PDPR 16x4     |

|----------------------------|------------------|---------------|

| Number of slices           | 3                | 3             |

| Note: SPB = Single Port BA | M. PDPR = Pseudo | Dual Port RAM |

ote: SPR = Single Port RAM, PDPR = Pseudo Dual

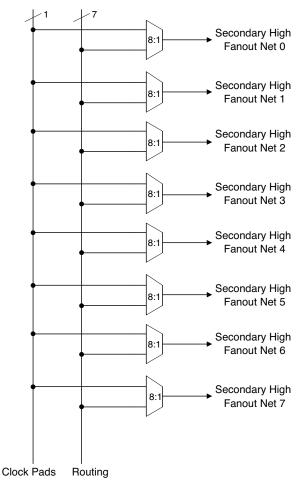

#### Figure 2-6. Secondary High Fanout Nets for MachXO3L/LF Devices

#### sysCLOCK Phase Locked Loops (PLLs)

The sysCLOCK PLLs provide the ability to synthesize clock frequencies. All MachXO3L/LF devices have one or more sysCLOCK PLL. CLKI is the reference frequency input to the PLL and its source can come from an external I/O pin or from internal routing. CLKFB is the feedback signal to the PLL which can come from internal routing or an external I/O pin. The feedback divider is used to multiply the reference frequency and thus synthesize a higher frequency clock output.

The MachXO3L/LF sysCLOCK PLLs support high resolution (16-bit) fractional-N synthesis. Fractional-N frequency synthesis allows the user to generate an output clock which is a non-integer multiple of the input frequency. For more information about using the PLL with Fractional-N synthesis, please see TN1282, MachXO3 sysCLOCK PLL Design and Usage Guide.

Each output has its own output divider, thus allowing the PLL to generate different frequencies for each output. The output dividers can have a value from 1 to 128. The output dividers may also be cascaded together to generate low frequency clocks. The CLKOP, CLKOS, CLKOS2, and CLKOS3 outputs can all be used to drive the MachXO3L/LF clock distribution network directly or general purpose routing resources can be used.

The LOCK signal is asserted when the PLL determines it has achieved lock and de-asserted if a loss of lock is detected. A block diagram of the PLL is shown in Figure 2-7.

The setup and hold times of the device can be improved by programming a phase shift into the CLKOS, CLKOS2, and CLKOS3 output clocks which will advance or delay the output clock with reference to the CLKOP output clock.

If an EBR is pre-loaded during configuration, the GSR input must be disabled or the release of the GSR during device wake up must occur before the release of the device I/Os becoming active.

These instructions apply to all EBR RAM, ROM and FIFO implementations. For the EBR FIFO mode, the GSR signal is always enabled and the WE and RE signals act like the clock enable signals in Figure 2-10. The reset timing rules apply to the RPReset input versus the RE input and the RST input versus the WE and RE inputs. Both RST and RPReset are always asynchronous EBR inputs. For more details refer to TN1290, Memory Usage Guide for MachXO3 Devices.

Note that there are no reset restrictions if the EBR synchronous reset is used and the EBR GSR input is disabled.

## Programmable I/O Cells (PIC)

The programmable logic associated with an I/O is called a PIO. The individual PIO are connected to their respective sysIO buffers and pads. On the MachXO3L/LF devices, the PIO cells are assembled into groups of four PIO cells called a Programmable I/O Cell or PIC. The PICs are placed on all four sides of the device.

On all the MachXO3L/LF devices, two adjacent PIOs can be combined to provide a complementary output driver pair.

All PIO pairs can implement differential receivers. Half of the PIO pairs on the top edge of these devices can be configured as true LVDS transmit pairs. The PIO pairs on the bottom edge of these devices have on-chip differential termination and also provide PCI support.

### Input Gearbox

Each PIC on the bottom edge has a built-in 1:8 input gearbox. Each of these input gearboxes may be programmed as a 1:7 de-serializer or as one IDDRX4 (1:8) gearbox or as two IDDRX2 (1:4) gearboxes. Table 2-9 shows the gearbox signals.

#### Table 2-9. Input Gearbox Signal List

| Name      | I/O Type | Description                                                                                                                                                |

|-----------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D         | Input    | High-speed data input after programmable delay in PIO A input register block                                                                               |

| ALIGNWD   | Input    | Data alignment signal from device core                                                                                                                     |

| SCLK      | Input    | Slow-speed system clock                                                                                                                                    |

| ECLK[1:0] | Input    | High-speed edge clock                                                                                                                                      |

| RST       | Input    | Reset                                                                                                                                                      |

| Q[7:0]    | Output   | Low-speed data to device core:<br>Video RX(1:7): Q[6:0]<br>GDDRX4(1:8): Q[7:0]<br>GDDRX2(1:4)(IOL-A): Q4, Q5, Q6, Q7<br>GDDRX2(1:4)(IOL-C): Q0, Q1, Q2, Q3 |

These gearboxes have three stage pipeline registers. The first stage registers sample the high-speed input data by the high-speed edge clock on its rising and falling edges. The second stage registers perform data alignment based on the control signals UPDATE and SEL0 from the control block. The third stage pipeline registers pass the data to the device core synchronized to the low-speed system clock. Figure 2-13 shows a block diagram of the input gearbox.

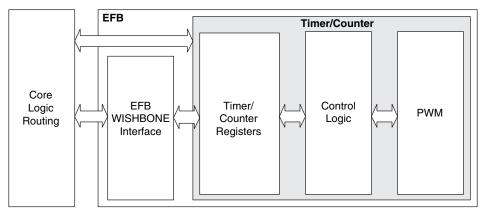

#### Hardened Timer/Counter

MachXO3L/LF devices provide a hard Timer/Counter IP core. This Timer/Counter is a general purpose, bi-directional, 16-bit timer/counter module with independent output compare units and PWM support. The Timer/Counter supports the following functions:

- Supports the following modes of operation:

- Watchdog timer

- Clear timer on compare match

- Fast PWM

- Phase and Frequency Correct PWM

- Programmable clock input source

- Programmable input clock prescaler

- One static interrupt output to routing

- One wake-up interrupt to on-chip standby mode controller.

- Three independent interrupt sources: overflow, output compare match, and input capture

- Auto reload

- Time-stamping support on the input capture unit

- Waveform generation on the output

- Glitch-free PWM waveform generation with variable PWM period

- Internal WISHBONE bus access to the control and status registers

- · Stand-alone mode with preloaded control registers and direct reset input

#### Figure 2-20. Timer/Counter Block Diagram

Table 2-16. Timer/Counter Signal Description

| Port    | I/O                                                                                  | Description                                                                                                                                                                                                          |

|---------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tc_clki | I                                                                                    | Timer/Counter input clock signal                                                                                                                                                                                     |

| tc_rstn | I Register tc_rstn_ena is preloaded by configuration to always keep this pin enabled |                                                                                                                                                                                                                      |

| tc_ic   | I                                                                                    | Input capture trigger event, applicable for non-pwm modes with WISHBONE interface. If enabled, a rising edge of this signal will be detected and synchronized to capture tc_cnt value into tc_icr for time-stamping. |

| tc_int  | 0                                                                                    | Without WISHBONE – Can be used as overflow flag<br>With WISHBONE – Controlled by three IRQ registers                                                                                                                 |

| tc_oc   | 0                                                                                    | Timer counter output signal                                                                                                                                                                                          |

For more details on these embedded functions, please refer to TN1293, Using Hardened Control Functions in MachXO3 Devices.

## **User Flash Memory (UFM)**

MachXO3LF devices provide a User Flash Memory block, which can be used for a variety of applications including storing a portion of the configuration image, initializing EBRs, to store PROM data or, as a general purpose user Flash memory. The UFM block connects to the device core through the embedded function block WISHBONE interface. Users can also access the UFM block through the JTAG, I2C and SPI interfaces of the device. The UFM block offers the following features:

- Non-volatile storage up to 256 kbits

- 100K write cycles

- Write access is performed page-wise; each page has 128 bits (16 bytes)

- Auto-increment addressing

- WISHBONE interface

For more information on the UFM, please refer to TN1293, Using Hardened Control Functions in MachXO3 Devices.

## **Standby Mode and Power Saving Options**

MachXO3L/LF devices are available in two options, the C and E devices. The C devices have a built-in voltage regulator to allow for 2.5 V V<sub>CC</sub> and 3.3 V V<sub>CC</sub> while the E devices operate at 1.2 V V<sub>CC</sub>.

MachXO3L/LF devices have been designed with features that allow users to meet the static and dynamic power requirements of their applications by controlling various device subsystems such as the bandgap, power-on-reset circuitry, I/O bank controllers, power guard, on-chip oscillator, PLLs, etc. In order to maximize power savings, MachXO3L/LF devices support a low power Stand-by mode.

In the stand-by mode the MachXO3L/LF devices are powered on and configured. Internal logic, I/Os and memories are switched on and remain operational, as the user logic waits for an external input. The device enters this mode when the standby input of the standby controller is toggled or when an appropriate I<sup>2</sup>C or JTAG instruction is issued by an external master. Various subsystems in the device such as the band gap, power-on-reset circuitry etc can be configured such that they are automatically turned "off" or go into a low power consumption state to save power when the device enters this state. Note that the MachXO3L/LF devices are powered on when in standby mode and all power supplies should remain in the Recommended Operating Conditions.

#### Security and One-Time Programmable Mode (OTP)

For applications where security is important, the lack of an external bitstream provides a solution that is inherently more secure than SRAM-based FPGAs. This is further enhanced by device locking. MachXO3L/LF devices contain security bits that, when set, prevent the readback of the SRAM configuration and NVCM/Flash spaces. The device can be in one of two modes:

- 1. Unlocked Readback of the SRAM configuration and NVCM/Flash spaces is allowed.

- 2. Permanently Locked The device is permanently locked.

Once set, the only way to clear the security bits is to erase the device. To further complement the security of the device, a One Time Programmable (OTP) mode is available. Once the device is set in this mode it is not possible to erase or re-program the NVCM/Flash and SRAM OTP portions of the device. For more details, refer to TN1279, MachXO3 Programming and Configuration Usage Guide.

#### Password

The MachXO3LF supports a password-based security access feature also known as Flash Protect Key. Optionally, the MachXO3L device can be ordered with a custom specification (c-spec) to support this feature. The Flash Protect Key feature provides a method of controlling access to the Configuration and Programming modes of the device. When enabled, the Configuration and Programming edit mode operations (including Write, Verify and Erase operations) are allowed only when coupled with a Flash Protect Key which matches that expected by the device. Without a valid Flash Protect Key, the user can perform only rudimentary non-configuration operations such as Read Device ID. For more details, refer to TN1313, Using Password Security with MachXO3 Devices.

#### **Dual Boot**

MachXO3L/LF devices can optionally boot from two patterns, a primary bitstream and a golden bitstream. If the primary bitstream is found to be corrupt while being downloaded into the SRAM, the device shall then automatically re-boot from the golden bitstream. Note that the primary bitstream must reside in the external SPI Flash. The golden image MUST reside in an on-chip NVCM/Flash. For more details, refer to TN1279, MachXO3 Programming and Configuration Usage Guide.

#### Soft Error Detection

The SED feature is a CRC check of the SRAM cells after the device is configured. This check ensures that the SRAM cells were configured successfully. This feature is enabled by a configuration bit option. The Soft Error Detection can also be initiated in user mode via an input to the fabric. The clock for the Soft Error Detection circuit is generated using a dedicated divider. The undivided clock from the on-chip oscillator is the input to this divider. For low power applications users can switch off the Soft Error Detection circuit. For more details, refer to TN1292, MachXO3 Soft Error Detection Usage Guide.

#### Soft Error Correction

The MachXO3LF device supports Soft Error Correction (SEC). Optionally, the MachXO3L device can be ordered with a custom specification (c-spec) to support this feature. When BACKGROUND\_RECONFIG is enabled using the Lattice Diamond Software in a design, asserting the PROGRAMN pin or issuing the REFRESH sysConfig command refreshes the SRAM array from configuration memory. Only the detected error bit is corrected. No other SRAM cells are changed, allowing the user design to function uninterrupted.

During the project design phase, if the overall system cannot guarantee containment of the error or its subsequent effects on downstream data or control paths, Lattice recommends using SED only. The MachXO3 can be then be soft-reset by asserting PROGRAMN or issuing the Refresh command over a sysConfig port in response to SED. Soft-reset additionally erases the SRAM array prior to the SRAM refresh, and asserts internal Reset circuitry to guarantee a known state. For more details, refer to TN1292, MachXO3 Soft Error Detection (SED)/Correction (SEC) Usage Guide.

## **DC Electrical Characteristics**

| Parameter                                   | Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Min.                                                    | Тур.                                                    | Max.                                                    | Units                                                   |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|

|                                             | Clamp OFF and $V_{CCIO} < V_{IN} < V_{IH}$ (MAX)                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                         | _                                                       | +175                                                    | μA                                                      |

|                                             | Clamp OFF and $V_{IN} = V_{CCIO}$                                                                                                                                                                                                                                                                                                                                                                                                                                     | -10                                                     | _                                                       | 10                                                      | μA                                                      |

| Input or I/O Leakage                        | Clamp OFF and V <sub>CCIO</sub> - 0.97 V < V <sub>IN</sub> <<br>V <sub>CCIO</sub>                                                                                                                                                                                                                                                                                                                                                                                     | -175                                                    |                                                         | —                                                       | μΑ                                                      |

|                                             | Clamp OFF and 0 V < $V_{IN}$ < $V_{CCIO}$ - 0.97 V                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                         | _                                                       | 10                                                      | μA                                                      |

|                                             | Clamp OFF and V <sub>IN</sub> = GND                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                         | _                                                       | 10                                                      | μA                                                      |

|                                             | Clamp ON and 0 V < V <sub>IN</sub> < V <sub>CCIO</sub>                                                                                                                                                                                                                                                                                                                                                                                                                |                                                         | _                                                       | 10                                                      | μA                                                      |

| I/O Active Pull-up Current                  | 0 < V <sub>IN</sub> < 0.7 V <sub>CCIO</sub>                                                                                                                                                                                                                                                                                                                                                                                                                           | -30                                                     |                                                         | -309                                                    | μA                                                      |

| I/O Active Pull-down<br>Current             | V <sub>IL</sub> (MAX) < V <sub>IN</sub> < V <sub>CCIO</sub>                                                                                                                                                                                                                                                                                                                                                                                                           | 30                                                      |                                                         | 305                                                     | μA                                                      |

| Bus Hold Low sustaining<br>current          | $V_{IN} = V_{IL} (MAX)$                                                                                                                                                                                                                                                                                                                                                                                                                                               | 30                                                      |                                                         | —                                                       | μA                                                      |

| Bus Hold High sustaining<br>current         | V <sub>IN</sub> = 0.7V <sub>CCIO</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                | -30                                                     | _                                                       | _                                                       | μΑ                                                      |

| Bus Hold Low Overdrive<br>current           | $0 \le V_{IN} \le V_{CCIO}$                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                       | _                                                       | 305                                                     | μΑ                                                      |

| Bus Hold High Overdrive<br>current          | $0 \le V_{IN} \le V_{CCIO}$                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                       | _                                                       | -309                                                    | μA                                                      |

| Bus Hold Trip Points                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | V <sub>IL</sub><br>(MAX)                                | _                                                       | V <sub>IH</sub><br>(MIN)                                | V                                                       |

| I/O Capacitance <sup>2</sup>                | $V_{CCIO} = 3.3 V, 2.5 V, 1.8 V, 1.5 V, 1.2 V, V_{CC} = Typ., V_{IO} = 0 to V_{IH} (MAX)$                                                                                                                                                                                                                                                                                                                                                                             | 3                                                       | 5                                                       | 9                                                       | pf                                                      |

| Dedicated Input<br>Capacitance <sup>2</sup> | $V_{CCIO} = 3.3 V, 2.5 V, 1.8 V, 1.5 V, 1.2 V, V_{CC} = Typ., V_{IO} = 0 to V_{IH} (MAX)$                                                                                                                                                                                                                                                                                                                                                                             | 3                                                       | 5.5                                                     | 7                                                       | pf                                                      |

|                                             | V <sub>CCIO</sub> = 3.3 V, Hysteresis = Large                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                         | 450                                                     |                                                         | mV                                                      |

|                                             | V <sub>CCIO</sub> = 2.5 V, Hysteresis = Large                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                         | 250                                                     |                                                         | mV                                                      |

|                                             | V <sub>CCIO</sub> = 1.8 V, Hysteresis = Large                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                         | 125                                                     |                                                         | mV                                                      |

| Hysteresis for Schmitt                      | V <sub>CCIO</sub> = 1.5 V, Hysteresis = Large                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                         | 100                                                     |                                                         | mV                                                      |

| Trigger Inputs⁵                             | V <sub>CCIO</sub> = 3.3 V, Hysteresis = Small                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                         | 250                                                     |                                                         | mV                                                      |

|                                             | V <sub>CCIO</sub> = 2.5 V, Hysteresis = Small                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                         | 150                                                     |                                                         | mV                                                      |

|                                             | V <sub>CCIO</sub> = 1.8 V, Hysteresis = Small                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                         | 60                                                      |                                                         | mV                                                      |

|                                             | V <sub>CCIO</sub> = 1.5 V, Hysteresis = Small                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                         | 40                                                      |                                                         | mV                                                      |

|                                             | Input or I/O Leakage         I/O Active Pull-up Current         I/O Active Pull-down         Current         Bus Hold Low sustaining         current         Bus Hold Low sustaining         current         Bus Hold Low Overdrive         current         Bus Hold Low Overdrive         current         Bus Hold High Overdrive         current         Bus Hold Trip Points         I/O Capacitance <sup>2</sup> Dedicated Input         Capacitance <sup>2</sup> | $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$ | $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$ | $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$ | $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$ |

1. Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tri-stated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

2. T<sub>A</sub> 25 °C, f = 1.0 MHz.

3. Please refer to V<sub>IL</sub> and V<sub>IH</sub> in the sysIO Single-Ended DC Electrical Characteristics table of this document.

When V<sub>IH</sub> is higher than V<sub>CCIO</sub>, a transient current typically of 30 ns in duration or less with a peak current of 6mA can occur on the high-tolow transition. For true LVDS output pins in MachXO3L/LF devices, V<sub>IH</sub> must be less than or equal to V<sub>CCIO</sub>.

5. With bus keeper circuit turned on. For more details, refer to TN1280, MachXO3 sysIO Usage Guide.

## Static Supply Current – C/E Devices<sup>1, 2, 3, 6</sup>

| Symbol          | Parameter                                       | Device                            | Typ.⁴ | Units |

|-----------------|-------------------------------------------------|-----------------------------------|-------|-------|

| I <sub>CC</sub> | Core Power Supply                               | LCMXO3L/LF-1300C 256 Ball Package | 4.8   | mA    |

|                 |                                                 | LCMXO3L/LF-2100C                  | 4.8   | mA    |

|                 |                                                 | LCMXO3L/LF-2100C 324 Ball Package | 8.45  | mA    |

|                 |                                                 | LCMXO3L/LF-4300C                  | 8.45  | mA    |

|                 |                                                 | LCMXO3L/LF-4300C 400 Ball Package | 12.87 | mA    |

|                 |                                                 | LCMXO3L/LF-6900C7                 | 12.87 | mA    |

|                 |                                                 | LCMXO3L/LF-9400C7                 | 17.86 | mA    |

|                 |                                                 | LCMXO3L/LF-640E                   | 1.00  | mA    |

|                 |                                                 | LCMXO3L/LF-1300E                  | 1.00  | mA    |

|                 |                                                 | LCMXO3L/LF-1300E 256 Ball Package | 1.39  | mA    |

|                 |                                                 | LCMXO3L/LF-2100E                  | 1.39  | mA    |

|                 |                                                 | LCMXO3L/LF-2100E 324 Ball Package | 2.55  | mA    |

|                 |                                                 | LCMXO3L/LF-4300E                  | 2.55  | mA    |

|                 |                                                 | LCMXO3L/LF-6900E                  | 4.06  | mA    |

|                 |                                                 | LCMXO3L/LF-9400E                  | 5.66  | mA    |

| ICCIO           | Bank Power Supply <sup>5</sup><br>VCCIO = 2.5 V | All devices                       | 0     | mA    |

1. For further information on supply current, please refer to TN1289, Power Estimation and Management for MachXO3 Devices.

2. Assumes blank pattern with the following characteristics: all outputs are tri-stated, all inputs are configured as LVCMOS and held at V<sub>CCIO</sub> or GND, on-chip oscillator is off, on-chip PLL is off.

3. Frequency = 0 MHz.

4.  $T_J = 25$  °C, power supplies at nominal voltage.

5. Does not include pull-up/pull-down.

6. To determine the MachXO3L/LF peak start-up current data, use the Power Calculator tool.

7. Determination of safe ambient operating conditions requires use of the Diamond Power Calculator tool.

|                                                                              | Description                             | Min. | Тур. | Max. | Units |

|------------------------------------------------------------------------------|-----------------------------------------|------|------|------|-------|

| Low Power                                                                    |                                         |      |      |      |       |

| VCCIO VCCIO of the Bank with LVCMOS12D 6 mA<br>drive bidirectional IO buffer |                                         |      | 1.2  |      | V     |

| VIH                                                                          | Logic 1 input voltage                   | —    | _    | 0.88 | V     |

| VIL                                                                          | Logic 0 input voltage, not in ULP State | 0.55 | _    | _    | V     |

| VHYST                                                                        | Input hysteresis                        | 25   | —    | —    | mV    |

1. Over Recommended Operating Conditions

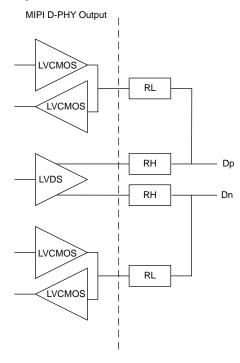

#### Figure 3-5. MIPI D-PHY Output Using External Resistors

## MachXO3L/LF External Switching Characteristics – C/E Devices<sup>1, 2, 3, 4, 5, 6, 10</sup>

|                                    |                                                  |                         | _     | 6    | -     | 5        |       |

|------------------------------------|--------------------------------------------------|-------------------------|-------|------|-------|----------|-------|

| Parameter                          | Description                                      | Device                  | Min.  | Max. | Min.  | Max.     | Units |

| Clocks                             |                                                  | I                       |       |      |       |          |       |

| Primary Clo                        | ocks                                             |                         |       |      |       |          |       |

| f <sub>MAX_PRI</sub> <sup>7</sup>  | Frequency for Primary Clock Tree                 | All MachXO3L/LF devices |       | 388  | —     | 323      | MHz   |

| t <sub>W_PRI</sub>                 | Clock Pulse Width for Primary Clock              | All MachXO3L/LF devices | 0.5   | _    | 0.6   |          | ns    |

|                                    |                                                  | MachXO3L/LF-1300        | _     | 867  | —     | 897      | ps    |

|                                    |                                                  | MachXO3L/LF-2100        |       | 867  | _     | 897      | ps    |

| t <sub>SKEW_PRI</sub>              | Primary Clock Skew Within a Device               | MachXO3L/LF-4300        |       | 865  | _     | 892      | ps    |

| 0.12.1                             |                                                  | MachXO3L/LF-6900        |       | 902  | _     | 942      | ps    |

|                                    |                                                  | MachXO3L/LF-9400        | _     | 908  | _     | 950      | ps    |

| Edge Clock                         |                                                  |                         |       |      |       |          |       |

| f <sub>MAX_EDGE</sub> <sup>7</sup> | Frequency for Edge Clock                         | MachXO3L/LF             | _     | 400  | _     | 333      | MHz   |

| _                                  | n Propagation Delay                              |                         |       |      |       |          |       |

| t <sub>PD</sub>                    | Best case propagation delay through one<br>LUT-4 | All MachXO3L/LF devices | _     | 6.72 | _     | 6.96     | ns    |

| General I/O                        | Pin Parameters (Using Primary Clock with         | out PLL)                |       | I    |       |          | 1     |

|                                    |                                                  | MachXO3L/LF-1300        | —     | 7.46 | _     | 7.66     | ns    |

|                                    | Clock to Output - PIO Output Register            | MachXO3L/LF-2100        | _     | 7.46 | —     | 7.66     | ns    |

| t <sub>CO</sub>                    |                                                  | MachXO3L/LF-4300        | _     | 7.51 | _     | 7.71     | ns    |

| 00                                 |                                                  | MachXO3L/LF-6900        | _     | 7.54 | _     | 7.75     | ns    |

|                                    |                                                  | MachXO3L/LF-9400        | _     | 7.53 | _     | 7.83     | ns    |

|                                    |                                                  | MachXO3L/LF-1300        | -0.20 | —    | -0.20 | —        | ns    |

|                                    |                                                  | MachXO3L/LF-2100        | -0.20 |      | -0.20 |          | ns    |

| t <sub>SU</sub>                    | Clock to Data Setup - PIO Input Register         | MachXO3L/LF-4300        | -0.23 |      | -0.23 |          | ns    |

|                                    |                                                  | MachXO3L/LF-6900        | -0.23 | _    | -0.23 |          | ns    |

|                                    |                                                  | MachXO3L/LF-9400        | -0.24 | —    | -0.24 | —        | ns    |

|                                    |                                                  | MachXO3L/LF-1300        | 1.89  |      | 2.13  |          | ns    |

|                                    |                                                  | MachXO3L/LF-2100        | 1.89  |      | 2.13  |          | ns    |

| t <sub>H</sub>                     | Clock to Data Hold - PIO Input Register          | MachXO3L/LF-4300        | 1.94  | _    | 2.18  | _        | ns    |

|                                    |                                                  | MachXO3L/LF-6900        | 1.98  |      | 2.23  |          | ns    |

|                                    |                                                  | MachXO3L/LF-9400        | 1.99  |      | 2.24  |          | ns    |

|                                    |                                                  | MachXO3L/LF-1300        | 1.61  |      | 1.76  |          | ns    |

|                                    |                                                  | MachXO3L/LF-2100        | 1.61  |      | 1.76  |          | ns    |

| t <sub>SU_DEL</sub>                | Clock to Data Setup - PIO Input Register         | MachXO3L/LF-4300        | 1.66  | _    | 1.81  | _        | ns    |

| 00_DEE                             | with Data Input Delay                            | MachXO3L/LF-6900        | 1.53  | _    | 1.67  | _        | ns    |

|                                    |                                                  | MachXO3L/LF-9400        | 1.65  | _    | 1.80  | <u> </u> | ns    |

|                                    |                                                  | MachXO3L/LF-1300        | -0.23 | _    | -0.23 | _        | ns    |

|                                    |                                                  | MachXO3L/LF-2100        | -0.23 | _    | -0.23 | _        | ns    |

| t <sub>H_DEL</sub>                 | Clock to Data Hold - PIO Input Register with     | MachXO3L/LF-4300        | -0.25 |      | -0.25 |          | ns    |

| DEE                                | Input Data Delay                                 | MachXO3L/LF-6900        | -0.21 |      | -0.21 |          | ns    |

|                                    |                                                  | MachXO3L/LF-9400        | -0.24 |      | -0.24 |          | ns    |

| f <sub>MAX_IO</sub>                | Clock Frequency of I/O and PFU Register          | All MachXO3L/LF devices |       | 388  |       | 323      | MHz   |

#### Over Recommended Operating Conditions

## DC and Switching Characteristics MachXO3 Family Data Sheet

|                      |                                                                   |                  | -     | 6    | _     | 5    |       |

|----------------------|-------------------------------------------------------------------|------------------|-------|------|-------|------|-------|

| Parameter            | Description                                                       | Device           | Min.  | Max. | Min.  | Max. | Units |

| General I/O          | Pin Parameters (Using Edge Clock without                          | t PLL)           |       |      | 1     |      | 1     |

|                      |                                                                   | MachXO3L/LF-1300 | —     | 7.53 | —     | 7.76 | ns    |

|                      |                                                                   | MachXO3L/LF-2100 | —     | 7.53 | —     | 7.76 | ns    |

| t <sub>COE</sub>     | Clock to Output - PIO Output Register                             | MachXO3L/LF-4300 | —     | 7.45 |       | 7.68 | ns    |

|                      |                                                                   | MachXO3L/LF-6900 | —     | 7.53 |       | 7.76 | ns    |

|                      |                                                                   | MachXO3L/LF-9400 | —     | 8.93 | —     | 9.35 | ns    |

|                      |                                                                   | MachXO3L/LF-1300 | -0.19 |      | -0.19 |      | ns    |

|                      |                                                                   | MachXO3L/LF-2100 | -0.19 |      | -0.19 | _    | ns    |

| t <sub>SUE</sub>     | Clock to Data Setup - PIO Input Register                          | MachXO3L/LF-4300 | -0.16 | _    | -0.16 | _    | ns    |

|                      |                                                                   | MachXO3L/LF-6900 | -0.19 |      | -0.19 |      | ns    |

|                      |                                                                   | MachXO3L/LF-9400 | -0.20 | _    | -0.20 | _    | ns    |

|                      |                                                                   | MachXO3L/LF-1300 | 1.97  | _    | 2.24  | _    | ns    |

|                      |                                                                   | MachXO3L/LF-2100 | 1.97  |      | 2.24  |      | ns    |

| t <sub>HE</sub>      | Clock to Data Hold - PIO Input Register                           | MachXO3L/LF-4300 | 1.89  |      | 2.16  |      | ns    |

|                      |                                                                   | MachXO3L/LF-6900 | 1.97  | _    | 2.24  | _    | ns    |

|                      |                                                                   | MachXO3L/LF-9400 | 1.98  |      | 2.25  |      | ns    |

|                      | Clock to Data Setup - PIO Input Register<br>with Data Input Delay | MachXO3L/LF-1300 | 1.56  |      | 1.69  | _    | ns    |

|                      |                                                                   | MachXO3L/LF-2100 | 1.56  |      | 1.69  |      | ns    |

| t <sub>SU_DELE</sub> |                                                                   | MachXO3L/LF-4300 | 1.74  | _    | 1.88  | _    | ns    |

| 00_0222              |                                                                   | MachXO3L/LF-6900 | 1.66  | _    | 1.81  | _    | ns    |

|                      |                                                                   | MachXO3L/LF-9400 | 1.71  |      | 1.85  |      | ns    |

|                      |                                                                   | MachXO3L/LF-1300 | -0.23 | _    | -0.23 | _    | ns    |

|                      |                                                                   | MachXO3L/LF-2100 | -0.23 |      | -0.23 |      | ns    |

| t <sub>H_DELE</sub>  | Clock to Data Hold - PIO Input Register with<br>Input Data Delay  | MachXO3L/LF-4300 | -0.34 |      | -0.34 |      | ns    |

|                      | input bata bolay                                                  | MachXO3L/LF-6900 | -0.29 |      | -0.29 |      | ns    |

|                      |                                                                   | MachXO3L/LF-9400 | -0.30 |      | -0.30 |      | ns    |

| General I/O          | Pin Parameters (Using Primary Clock with                          | PLL)             |       |      |       |      |       |

|                      |                                                                   | MachXO3L/LF-1300 | —     | 5.98 |       | 6.01 | ns    |

|                      |                                                                   | MachXO3L/LF-2100 | —     | 5.98 | _     | 6.01 | ns    |

| t <sub>COPLL</sub>   | Clock to Output - PIO Output Register                             | MachXO3L/LF-4300 | —     | 5.99 | —     | 6.02 | ns    |

|                      |                                                                   | MachXO3L/LF-6900 | —     | 6.02 | _     | 6.06 | ns    |

|                      |                                                                   | MachXO3L/LF-9400 | —     | 5.55 | _     | 6.13 | ns    |

|                      |                                                                   | MachXO3L/LF-1300 | 0.36  | _    | 0.36  | —    | ns    |

|                      |                                                                   | MachXO3L/LF-2100 | 0.36  | _    | 0.36  | _    | ns    |

| t <sub>SUPLL</sub>   | Clock to Data Setup - PIO Input Register                          | MachXO3L/LF-4300 | 0.35  |      | 0.35  |      | ns    |

|                      |                                                                   | MachXO3L/LF-6900 | 0.34  | —    | 0.34  | —    | ns    |

|                      |                                                                   | MachXO3L/LF-9400 | 0.33  |      | 0.33  |      | ns    |

|                      |                                                                   | MachXO3L/LF-1300 | 0.42  |      | 0.49  |      | ns    |

|                      |                                                                   | MachXO3L/LF-2100 | 0.42  | —    | 0.49  | —    | ns    |

| t <sub>HPLL</sub>    | Clock to Data Hold - PIO Input Register                           | MachXO3L/LF-4300 | 0.43  | —    | 0.50  | _    | ns    |

|                      |                                                                   | MachXO3L/LF-6900 | 0.46  |      | 0.54  |      | ns    |

|                      |                                                                   | MachXO3L/LF-9400 | 0.47  | —    | 0.55  | —    | ns    |

## DC and Switching Characteristics MachXO3 Family Data Sheet

|                        |                                                                   |                  | -6    |      | -5    |      |       |  |

|------------------------|-------------------------------------------------------------------|------------------|-------|------|-------|------|-------|--|

| Parameter              | Description                                                       | Device           | Min.  | Max. | Min.  | Max. | Units |  |

|                        |                                                                   | MachXO3L/LF-1300 | 2.87  | _    | 3.18  | —    | ns    |  |

|                        |                                                                   | MachXO3L/LF-2100 | 2.87  |      | 3.18  | —    | ns    |  |

| t <sub>SU_DELPLL</sub> | Clock to Data Setup - PIO Input Register<br>with Data Input Delay | MachXO3L/LF-4300 | 2.96  |      | 3.28  | —    | ns    |  |

|                        |                                                                   | MachXO3L/LF-6900 | 3.05  | _    | 3.35  | —    | ns    |  |

|                        |                                                                   | MachXO3L/LF-9400 | 3.06  |      | 3.37  | —    | ns    |  |

|                        |                                                                   | MachXO3L/LF-1300 | -0.83 |      | -0.83 | —    | ns    |  |

|                        | Clock to Data Hold - PIO Input Register with<br>Input Data Delay  | MachXO3L/LF-2100 | -0.83 |      | -0.83 | —    | ns    |  |

| Ter and an a           |                                                                   | MachXO3L/LF-4300 | -0.87 |      | -0.87 | —    | ns    |  |

|                        | input Data Dotay                                                  | MachXO3L/LF-6900 | -0.91 | —    | -0.91 | —    | ns    |  |

|                        |                                                                   | MachXO3L/LF-9400 | -0.93 | —    | -0.93 | —    | ns    |  |

## I<sup>2</sup>C Port Timing Specifications<sup>1, 2</sup>

| Symbol           | Parameter                   | Min. | Max. | Units |

|------------------|-----------------------------|------|------|-------|

| f <sub>MAX</sub> | Maximum SCL clock frequency |      | 400  | kHz   |

1. MachXO3L/LF supports the following modes:

• Standard-mode (Sm), with a bit rate up to 100 kbit/s (user and configuration mode)

• Fast-mode (Fm), with a bit rate up to 400 kbit/s (user and configuration mode)

2. Refer to the  $I^2C$  specification for timing requirements.

## SPI Port Timing Specifications<sup>1</sup>

| Symbol           | Parameter                   | Min. | Max. | Units |

|------------------|-----------------------------|------|------|-------|

| f <sub>MAX</sub> | Maximum SCK clock frequency | —    | 45   | MHz   |

1. Applies to user mode only. For configuration mode timing specifications, refer to sysCONFIG Port Timing Specifications table in this data sheet.

## **Switching Test Conditions**

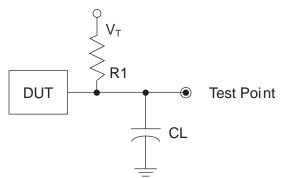

Figure 3-9 shows the output test load used for AC testing. The specific values for resistance, capacitance, voltage, and other test conditions are shown in Table 3-6.

#### Figure 3-9. Output Test Load, LVTTL and LVCMOS Standards

| Table 3-6. Test Fixture Required Components, | Non-Terminated Interfaces |

|----------------------------------------------|---------------------------|

|----------------------------------------------|---------------------------|

| Test Condition                             | R1       | CL  | Timing Ref.               | VT              |

|--------------------------------------------|----------|-----|---------------------------|-----------------|

|                                            |          |     | LVTTL, LVCMOS 3.3 = 1.5 V | —               |

|                                            |          |     | LVCMOS 2.5 = $V_{CCIO}/2$ | _               |

| LVTTL and LVCMOS settings (L -> H, H -> L) | $\infty$ | 0pF | LVCMOS 1.8 = $V_{CCIO}/2$ | _               |

|                                            |          |     | LVCMOS 1.5 = $V_{CCIO}/2$ |                 |

|                                            |          |     | LVCMOS 1.2 = $V_{CCIO}/2$ | _               |

| LVTTL and LVCMOS 3.3 (Z -> H)              |          |     | V <sub>OL</sub>           |                 |

| LVTTL and LVCMOS 3.3 (Z -> L)              |          |     | 1.5                       | V <sub>OH</sub> |

| Other LVCMOS (Z -> H)                      | 188      | 0pF | V <sub>CCIO</sub> /2      | V <sub>OL</sub> |

| Other LVCMOS (Z -> L)                      | 100      | opr | V <sub>CCIO</sub> /2      | V <sub>OH</sub> |

| LVTTL + LVCMOS (H -> Z)                    |          |     | V <sub>OH</sub> - 0.15    | V <sub>OL</sub> |

| LVTTL + LVCMOS (L -> Z)                    | 7        |     | V <sub>OL</sub> - 0.15    | V <sub>OH</sub> |

Note: Output test conditions for all other interfaces are determined by the respective standards.

|                                                        | MachXO3L/LF-4300 |           |           |           |          |          |          |

|--------------------------------------------------------|------------------|-----------|-----------|-----------|----------|----------|----------|

|                                                        | WLCSP81          | CSFBGA121 | CSFBGA256 | CSFBGA324 | CABGA256 | CABGA324 | CABGA400 |

| General Purpose IO per Bank                            |                  |           |           |           |          |          |          |

| Bank 0                                                 | 29               | 24        | 50        | 71        | 50       | 71       | 83       |

| Bank 1                                                 | 0                | 26        | 52        | 62        | 52       | 68       | 84       |

| Bank 2                                                 | 20               | 26        | 52        | 72        | 52       | 72       | 84       |

| Bank 3                                                 | 7                | 7         | 16        | 22        | 16       | 24       | 28       |

| Bank 4                                                 | 0                | 7         | 16        | 14        | 16       | 16       | 24       |

| Bank 5                                                 | 7                | 10        | 20        | 27        | 20       | 28       | 32       |

| Total General Purpose<br>Single Ended IO               | 63               | 100       | 206       | 268       | 206      | 279      | 335      |

| Differential IO per Bank                               | •                | •         |           |           |          | •        |          |

| Bank 0                                                 | 15               | 12        | 25        | 36        | 25       | 36       | 42       |

| Bank 1                                                 | 0                | 13        | 26        | 30        | 26       | 34       | 42       |

| Bank 2                                                 | 10               | 13        | 26        | 36        | 26       | 36       | 42       |

| Bank 3                                                 | 3                | 3         | 8         | 10        | 8        | 12       | 14       |

| Bank 4                                                 | 0                | 3         | 8         | 6         | 8        | 8        | 12       |

| Bank 5                                                 | 3                | 5         | 10        | 13        | 10       | 14       | 16       |

| Total General Purpose<br>Differential IO               | 31               | 49        | 103       | 131       | 103      | 140      | 168      |

| Dual Function IO                                       | 25               | 37        | 37        | 37        | 37       | 37       | 37       |

| Number 7:1 or 8:1 Gearboxes                            | •                | •         |           |           |          | •        |          |

| Number of 7:1 or 8:1 Output Gearbox Available (Bank 0) | 10               | 7         | 18        | 18        | 18       | 18       | 21       |

| Number of 7:1 or 8:1 Input Gearbox Available (Bank 2)  | 10               | 13        | 18        | 18        | 18       | 18       | 21       |

| High-speed Differential Outputs                        |                  |           |           |           |          |          |          |

| Bank 0                                                 | 10               | 7         | 18        | 18        | 18       | 18       | 21       |

| VCCIO Pins                                             |                  |           |           |           |          |          |          |

| Bank 0                                                 | 3                | 1         | 4         | 4         | 4        | 4        | 5        |

| Bank 1                                                 | 0                | 1         | 3         | 4         | 4        | 4        | 5        |

| Bank 2                                                 | 2                | 1         | 4         | 4         | 4        | 4        | 5        |

| Bank 3                                                 | 1                | 1         | 2         | 2         | 1        | 2        | 2        |

| Bank 4                                                 | 0                | 1         | 2         | 2         | 2        | 2        | 2        |

| Bank 5                                                 | 1                | 1         | 2         | 2         | 1        | 2        | 2        |

| VCC                                                    | 4                | 4         | 8         | 8         | 8        | 10       | 10       |

| GND                                                    | 6                | 10        | 24        | 16        | 24       | 16       | 33       |

| NC                                                     | 0                | 0         | 0         | 13        | 1        | 0        | 0        |

| Reserved for Configuration                             | 1                | 1         | 1         | 1         | 1        | 1        | 1        |

| Total Count of Bonded Pins                             | 81               | 121       | 256       | 324       | 256      | 324      | 400      |

| Part Number               | LUTs | Supply Voltage | Speed | Package             | Leads | Temp. |

|---------------------------|------|----------------|-------|---------------------|-------|-------|

| LCMXO3L-2100E-6MG324I     | 2100 | 1.2 V          | 6     | Halogen-Free csfBGA | 324   | IND   |

| LCMXO3L-2100C-5BG256C     | 2100 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 256   | СОМ   |

| LCMXO3L-2100C-6BG256C     | 2100 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 256   | COM   |

| LCMXO3L-2100C-5BG256I     | 2100 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 256   | IND   |

| LCMXO3L-2100C-6BG256I     | 2100 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 256   | IND   |

| LCMXO3L-2100C-5BG324C     | 2100 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 324   | COM   |

| LCMXO3L-2100C-6BG324C     | 2100 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 324   | СОМ   |

| LCMXO3L-2100C-5BG324I     | 2100 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 324   | IND   |

| LCMXO3L-2100C-6BG324I     | 2100 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 324   | IND   |

|                           |      |                |       |                     |       |       |

| Part Number               | LUTs | Supply Voltage | Speed | Package             | Leads | Temp. |

| LCMXO3L-4300E-5UWG81CTR   | 4300 | 1.2 V          | 5     | Halogen-Free WLCSP  | 81    | COM   |

| LCMXO3L-4300E-5UWG81CTR50 | 4300 | 1.2 V          | 5     | Halogen-Free WLCSP  | 81    | COM   |

| LCMXO3L-4300E-5UWG81CTR1K | 4300 | 1.2 V          | 5     | Halogen-Free WLCSP  | 81    | COM   |

| LCMXO3L-4300E-5UWG81ITR   | 4300 | 1.2 V          | 5     | Halogen-Free WLCSP  | 81    | IND   |

| LCMXO3L-4300E-5UWG81ITR50 | 4300 | 1.2 V          | 5     | Halogen-Free WLCSP  | 81    | IND   |

| LCMXO3L-4300E-5UWG81ITR1K | 4300 | 1.2 V          | 5     | Halogen-Free WLCSP  | 81    | IND   |

| LCMXO3L-4300E-5MG121C     | 4300 | 1.2 V          | 5     | Halogen-Free csfBGA | 121   | COM   |

| LCMXO3L-4300E-6MG121C     | 4300 | 1.2 V          | 6     | Halogen-Free csfBGA | 121   | COM   |

| LCMXO3L-4300E-5MG121I     | 4300 | 1.2 V          | 5     | Halogen-Free csfBGA | 121   | IND   |

| LCMXO3L-4300E-6MG121I     | 4300 | 1.2 V          | 6     | Halogen-Free csfBGA | 121   | IND   |

| LCMXO3L-4300E-5MG256C     | 4300 | 1.2 V          | 5     | Halogen-Free csfBGA | 256   | COM   |

| LCMXO3L-4300E-6MG256C     | 4300 | 1.2 V          | 6     | Halogen-Free csfBGA | 256   | COM   |

| LCMXO3L-4300E-5MG256I     | 4300 | 1.2 V          | 5     | Halogen-Free csfBGA | 256   | IND   |

| LCMXO3L-4300E-6MG256I     | 4300 | 1.2 V          | 6     | Halogen-Free csfBGA | 256   | IND   |

| LCMXO3L-4300E-5MG324C     | 4300 | 1.2 V          | 5     | Halogen-Free csfBGA | 324   | COM   |

| LCMXO3L-4300E-6MG324C     | 4300 | 1.2 V          | 6     | Halogen-Free csfBGA | 324   | COM   |

| LCMXO3L-4300E-5MG324I     | 4300 | 1.2 V          | 5     | Halogen-Free csfBGA | 324   | IND   |

| LCMXO3L-4300E-6MG324I     | 4300 | 1.2 V          | 6     | Halogen-Free csfBGA | 324   | IND   |

| LCMXO3L-4300C-5BG256C     | 4300 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 256   | COM   |

| LCMXO3L-4300C-6BG256C     | 4300 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 256   | COM   |

| LCMXO3L-4300C-5BG256I     | 4300 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 256   | IND   |

| LCMXO3L-4300C-6BG256I     | 4300 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 256   | IND   |

| LCMXO3L-4300C-5BG324C     | 4300 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 324   | COM   |

| LCMXO3L-4300C-6BG324C     | 4300 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 324   | СОМ   |

| LCMXO3L-4300C-5BG324I     | 4300 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 324   | IND   |

| LCMXO3L-4300C-6BG324I     | 4300 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 324   | IND   |

| LCMXO3L-4300C-5BG400C     | 4300 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 400   | СОМ   |