# E · ) ( Fattice Semiconductor Corporation - LCMXO3L-9400E-5BG256I Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                           |

|--------------------------------|----------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 1175                                                                             |

| Number of Logic Elements/Cells | 9400                                                                             |

| Total RAM Bits                 | 442368                                                                           |

| Number of I/O                  | 206                                                                              |

| Number of Gates                | -                                                                                |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                    |

| Mounting Type                  | Surface Mount                                                                    |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                               |

| Package / Case                 | 256-LFBGA                                                                        |

| Supplier Device Package        | 256-CABGA (14x14)                                                                |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lcmxo3l-9400e-5bg256i |

|                                |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

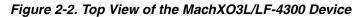

MachXO3L/LF-1300, MachXO3L/LF-2100, MachXO3L/LF-6900 and MachXO3L/LF-9400 are similar to MachXO3L/LF-4300. MachXO3L/LF-1300 has a lower LUT count, one PLL, and seven EBR blocks. MachXO3L/LF-2100 has a lower LUT count, one PLL, and eight EBR blocks. MachXO3L/LF-6900 has a higher LUT count, two PLLs, and 26 EBR blocks. MachXO3L/LF-9400 has a higher LUT count, two PLLs, and 48 EBR blocks.

• MachXO3L devices have NVCM, MachXO3LF devices have Flash.

The logic blocks, Programmable Functional Unit (PFU) and sysMEM EBR blocks, are arranged in a two-dimensional grid with rows and columns. Each row has either the logic blocks or the EBR blocks. The PIO cells are located at the periphery of the device, arranged in banks. The PFU contains the building blocks for logic, arithmetic, RAM, ROM, and register functions. The PIOs utilize a flexible I/O buffer referred to as a sysIO buffer that supports operation with a variety of interface standards. The blocks are connected with many vertical and horizontal routing channel resources. The place and route software tool automatically allocates these routing resources.

In the MachXO3L/LF family, the number of sysIO banks varies by device. There are different types of I/O buffers on the different banks. Refer to the details in later sections of this document. The sysMEM EBRs are large, dedicated fast memory blocks. These blocks can be configured as RAM, ROM or FIFO. FIFO support includes dedicated FIFO pointer and flag "hard" control logic to minimize LUT usage.

The MachXO3L/LF registers in PFU and sysI/O can be configured to be SET or RESET. After power up and device is configured, the device enters into user mode with these registers SET/RESET according to the configuration setting, allowing device entering to a known state for predictable system function.

The MachXO3L/LF architecture also provides up to two sysCLOCK Phase Locked Loop (PLL) blocks. These blocks are located at the ends of the on-chip NVCM/Flash block. The PLLs have multiply, divide, and phase shifting capabilities that are used to manage the frequency and phase relationships of the clocks.

MachXO3L/LF devices provide commonly used hardened functions such as SPI controller, I<sup>2</sup>C controller and timer/ counter.

MachXO3LF devices also provide User Flash Memory (UFM). These hardened functions and the UFM interface to the core logic and routing through a WISHBONE interface. The UFM can also be accessed through the SPI, I<sup>2</sup>C and JTAG ports.

Every device in the family has a JTAG port that supports programming and configuration of the device as well as access to the user logic. The MachXO3L/LF devices are available for operation from 3.3 V, 2.5 V and 1.2 V power sup-plies, providing easy integration into the overall system.

### **ROM Mode**

ROM mode uses the LUT logic; hence, slices 0-3 can be used in ROM mode. Preloading is accomplished through the programming interface during PFU configuration.

For more information on the RAM and ROM modes, please refer to TN1290, Memory Usage Guide for MachXO3 Devices.

## Routing

There are many resources provided in the MachXO3L/LF devices to route signals individually or as buses with related control signals. The routing resources consist of switching circuitry, buffers and metal interconnect (routing) segments.

The inter-PFU connections are made with three different types of routing resources: x1 (spans two PFUs), x2 (spans three PFUs) and x6 (spans seven PFUs). The x1, x2, and x6 connections provide fast and efficient connections in the horizontal and vertical directions.

The design tools take the output of the synthesis tool and places and routes the design. Generally, the place and route tool is completely automatic, although an interactive routing editor is available to optimize the design.

## **Clock/Control Distribution Network**

Each MachXO3L/LF device has eight clock inputs (PCLK [T, C] [Banknum]\_[2..0]) – three pins on the left side, two pins each on the bottom and top sides and one pin on the right side. These clock inputs drive the clock nets. These eight inputs can be differential or single-ended and may be used as general purpose I/O if they are not used to drive the clock nets. When using a single ended clock input, only the PCLKT input can drive the clock tree directly.

The MachXO3L/LF architecture has three types of clocking resources: edge clocks, primary clocks and secondary high fanout nets. MachXO3L/LF devices have two edge clocks each on the top and bottom edges. Edge clocks are used to clock I/O registers and have low injection time and skew. Edge clock inputs are from PLL outputs, primary clock pads, edge clock bridge outputs and CIB sources.

The eight primary clock lines in the primary clock network drive throughout the entire device and can provide clocks for all resources within the device including PFUs, EBRs and PICs. In addition to the primary clock signals, MachXO3L/LF devices also have eight secondary high fanout signals which can be used for global control signals, such as clock enables, synchronous or asynchronous clears, presets, output enables, etc. Internal logic can drive the global clock network for internally-generated global clocks and control signals.

The maximum frequency for the primary clock network is shown in the MachXO3L/LF External Switching Characteristics table.

Primary clock signals for the MachXO3L/LF-1300 and larger devices are generated from eight 27:1 muxes The available clock sources include eight I/O sources, 11 routing inputs, eight clock divider inputs and up to eight sys-CLOCK PLL outputs.

### Table 2-4. PLL Signal Descriptions (Continued)

| Port Name     | I/O | Description                                                                                            |  |  |  |

|---------------|-----|--------------------------------------------------------------------------------------------------------|--|--|--|

| CLKOP         | 0   | Primary PLL output clock (with phase shift adjustment)                                                 |  |  |  |

| CLKOS         | 0   | Secondary PLL output clock (with phase shift adjust)                                                   |  |  |  |

| CLKOS2        | 0   | Secondary PLL output clock2 (with phase shift adjust)                                                  |  |  |  |

| CLKOS3        | 0   | Secondary PLL output clock3 (with phase shift adjust)                                                  |  |  |  |

| LOCK          | 0   | PLL LOCK, asynchronous signal. Active high indicates PLL is locked to input and feed-<br>back signals. |  |  |  |

| DPHSRC        | 0   | Dynamic Phase source – ports or WISHBONE is active                                                     |  |  |  |

| STDBY         | I   | Standby signal to power down the PLL                                                                   |  |  |  |

| RST           | I   | PLL reset without resetting the M-divider. Active high reset.                                          |  |  |  |

| RESETM        | I   | PLL reset - includes resetting the M-divider. Active high reset.                                       |  |  |  |

| RESETC        | I   | Reset for CLKOS2 output divider only. Active high reset.                                               |  |  |  |

| RESETD        | I   | Reset for CLKOS3 output divider only. Active high reset.                                               |  |  |  |

| ENCLKOP       | I   | Enable PLL output CLKOP                                                                                |  |  |  |

| ENCLKOS       | I   | Enable PLL output CLKOS when port is active                                                            |  |  |  |

| ENCLKOS2      | I   | Enable PLL output CLKOS2 when port is active                                                           |  |  |  |

| ENCLKOS3      | I   | Enable PLL output CLKOS3 when port is active                                                           |  |  |  |

| PLLCLK        | I   | PLL data bus clock input signal                                                                        |  |  |  |

| PLLRST        | I   | PLL data bus reset. This resets only the data bus not any register values.                             |  |  |  |

| PLLSTB        | I   | PLL data bus strobe signal                                                                             |  |  |  |

| PLLWE         | I   | PLL data bus write enable signal                                                                       |  |  |  |

| PLLADDR [4:0] | I   | PLL data bus address                                                                                   |  |  |  |

| PLLDATI [7:0] | ļ   | PLL data bus data input                                                                                |  |  |  |

| PLLDATO [7:0] | 0   | PLL data bus data output                                                                               |  |  |  |

| PLLACK        | 0   | PLL data bus acknowledge signal                                                                        |  |  |  |

## sysMEM Embedded Block RAM Memory

The MachXO3L/LF devices contain sysMEM Embedded Block RAMs (EBRs). The EBR consists of a 9-Kbit RAM, with dedicated input and output registers. This memory can be used for a wide variety of purposes including data buffering, PROM for the soft processor and FIFO.

### sysMEM Memory Block

The sysMEM block can implement single port, dual port, pseudo dual port, or FIFO memories. Each block can be used in a variety of depths and widths as shown in Table 2-5.

| Port Name        | Description                 | Active State      |

|------------------|-----------------------------|-------------------|

| CLK              | Clock                       | Rising Clock Edge |

| CE               | Clock Enable                | Active High       |

| OCE <sup>1</sup> | Output Clock Enable         | Active High       |

| RST              | Reset                       | Active High       |

| BE <sup>1</sup>  | Byte Enable                 | Active High       |

| WE               | Write Enable                | Active High       |

| AD               | Address Bus                 | —                 |

| DI               | Data In                     | _                 |

| DO               | Data Out                    | _                 |

| CS               | Chip Select                 | Active High       |

| AFF              | FIFO RAM Almost Full Flag   | _                 |

| FF               | FIFO RAM Full Flag          | _                 |

| AEF              | FIFO RAM Almost Empty Flag  | _                 |

| EF               | FIFO RAM Empty Flag         | _                 |

| RPRST            | FIFO RAM Read Pointer Reset | _                 |

### Table 2-6. EBR Signal Descriptions

1. Optional signals.

2. For dual port EBR primitives a trailing 'A' or 'B' in the signal name specifies the EBR port A or port B respectively.

3. For FIFO RAM mode primitive, a trailing 'R' or 'W' in the signal name specifies the FIFO read port or write port respectively.

4. For FIFO RAM mode primitive FULLI has the same function as CSW(2) and EMPTYI has the same function as CSR(2).

In FIFO mode, CLKW is the write port clock, CSW is the write port chip select, CLKR is the read port clock, CSR is the read port clock, CSR is the read port clock.

The EBR memory supports three forms of write behavior for single or dual port operation:

- 1. **Normal** Data on the output appears only during the read cycle. During a write cycle, the data (at the current address) does not appear on the output. This mode is supported for all data widths.

- 2. Write Through A copy of the input data appears at the output of the same port. This mode is supported for all data widths.

- 3. Read-Before-Write When new data is being written, the old contents of the address appears at the output.

#### **FIFO Configuration**

The FIFO has a write port with data-in, CEW, WE and CLKW signals. There is a separate read port with data-out, RCE, RE and CLKR signals. The FIFO internally generates Almost Full, Full, Almost Empty and Empty Flags. The Full and Almost Full flags are registered with CLKW. The Empty and Almost Empty flags are registered with CLKR. Table 2-7 shows the range of programming values for these flags.

#### Table 2-7. Programmable FIFO Flag Ranges

| Flag Name         | Programming Range                  |

|-------------------|------------------------------------|

| Full (FF)         | 1 to max (up to 2 <sup>N</sup> -1) |

| Almost Full (AF)  | 1 to Full-1                        |

| Almost Empty (AE) | 1 to Full-1                        |

| Empty (EF)        | 0                                  |

N = Address bit width.

The FIFO state machine supports two types of reset signals: RST and RPRST. The RST signal is a global reset that clears the contents of the FIFO by resetting the read/write pointer and puts the FIFO flags in their initial reset

### **Output Register Block**

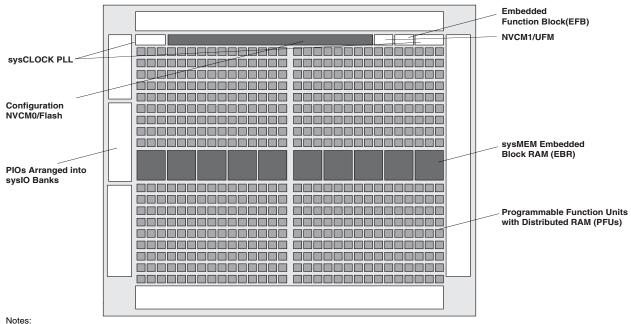

The output register block registers signals from the core of the device before they are passed to the sysIO buffers.

### Left, Top, Bottom Edges

In SDR mode, D0 feeds one of the flip-flops that then feeds the output. The flip-flop can be configured as a D-type register or latch.

In DDR generic mode, D0 and D1 inputs are fed into registers on the positive edge of the clock. At the next falling edge the registered D1 input is registered into the register Q1. A multiplexer running off the same clock is used to switch the mux between the outputs of registers Q0 and Q1 that will then feed the output.

Figure 2-12 shows the output register block on the left, top and bottom edges.

Figure 2-12. MachXO3L/LF Output Register Block Diagram (PIO on the Left, Top and Bottom Edges)

### Tri-state Register Block

The tri-state register block registers tri-state control signals from the core of the device before they are passed to the sysIO buffers. The block contains a register for SDR operation. In SDR, TD input feeds one of the flip-flops that then feeds the output.

## sysIO Buffer

Each I/O is associated with a flexible buffer referred to as a sysIO buffer. These buffers are arranged around the periphery of the device in groups referred to as banks. The sysIO buffers allow users to implement a wide variety of standards that are found in today's systems including LVCMOS, TTL, PCI, LVDS, BLVDS, MLVDS and LVPECL.

Each bank is capable of supporting multiple I/O standards. In the MachXO3L/LF devices, single-ended output buffers, ratioed input buffers (LVTTL, LVCMOS and PCI), differential (LVDS) input buffers are powered using I/O supply voltage ( $V_{CCIO}$ ). Each sysIO bank has its own  $V_{CCIO}$ .

MachXO3L/LF devices contain three types of sysIO buffer pairs.

### 1. Left and Right sysIO Buffer Pairs

The sysIO buffer pairs in the left and right banks of the device consist of two single-ended output drivers and two single-ended input buffers (for ratioed inputs such as LVCMOS and LVTTL). The I/O pairs on the left and right of the devices also have differential input buffers.

### 2. Bottom sysIO Buffer Pairs

The sysIO buffer pairs in the bottom bank of the device consist of two single-ended output drivers and two single-ended input buffers (for ratioed inputs such as LVCMOS and LVTTL). The I/O pairs on the bottom also have differential input buffers. Only the I/Os on the bottom banks have programmable PCI clamps and differential input termination. The PCI clamp is enabled after  $V_{CC}$  and  $V_{CCIO}$  are at valid operating levels and the device has been configured.

### 3. Top sysIO Buffer Pairs

The sysIO buffer pairs in the top bank of the device consist of two single-ended output drivers and two singleended input buffers (for ratioed inputs such as LVCMOS and LVTTL). The I/O pairs on the top also have differential I/O buffers. Half of the sysIO buffer pairs on the top edge have true differential outputs. The sysIO buffer pair comprising of the A and B PIOs in every PIC on the top edge have a differential output driver.

### Typical I/O Behavior During Power-up

The internal power-on-reset (POR) signal is deactivated when  $V_{CC}$  and  $V_{CCIO0}$  have reached  $V_{PORUP}$  level defined in the Power-On-Reset Voltage table in the DC and Switching Characteristics section of this data sheet. After the POR signal is deactivated, the FPGA core logic becomes active. It is the user's responsibility to ensure that all  $V_{CCIO}$  banks are active with valid input logic levels to properly control the output logic states of all the I/O banks that are critical to the application. The default configuration of the I/O pins in a blank device is tri-state with a weak pulldown to GND (some pins such as PROGRAMN and the JTAG pins have weak pull-up to  $V_{CCIO}$  as the default functionality). The I/O pins will maintain the blank configuration until  $V_{CC}$  and  $V_{CCIO}$  (for I/O banks containing configuration I/Os) have reached  $V_{PORUP}$  levels at which time the I/Os will take on the user-configured settings only after a proper download/configuration.

There are various ways a user can ensure that there are no spurious signals on critical outputs as the device powers up. These are discussed in more detail in TN1280, MachXO3 sysIO Usage Guide.

### **Supported Standards**

The MachXO3L/LF sysIO buffer supports both single-ended and differential standards. Single-ended standards can be further subdivided into LVCMOS, LVTTL, and PCI. The buffer supports the LVTTL, PCI, LVCMOS 1.2 V, 1.5 V, 1.8 V, 2.5 V, and 3.3 V standards. In the LVCMOS and LVTTL modes, the buffer has individually configurable options for drive strength, bus maintenance (weak pull-up, weak pull-down, bus-keeper latch or none) and open drain. BLVDS, MLVDS and LVPECL output emulation is supported on all devices. The MachXO3L/LF devices support on-chip LVDS output buffers on approximately 50% of the I/Os on the top bank. Differential receivers for LVDS, BLVDS, MLVDS and LVPECL are supported on all banks of MachXO3L/LF devices. PCI support is provided in the bottom bank of the MachXO3L/LF devices. Table 2-11 summarizes the I/O characteristics of the MachXO3L/LF PLDs.

## **Embedded Hardened IP Functions**

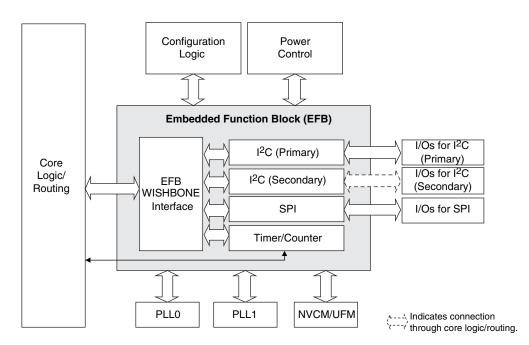

All MachXO3L/LF devices provide embedded hardened functions such as SPI, I<sup>2</sup>C and Timer/Counter. MachXO3LF devices also provide User Flash Memory (UFM). These embedded blocks interface through the WISHBONE interface with routing as shown in Figure 2-17.

### Figure 2-17. Embedded Function Block Interface

### Hardened I<sup>2</sup>C IP Core

Every MachXO3L/LF device contains two  $I^2C$  IP cores. These are the primary and secondary  $I^2C$  IP cores. Either of the two cores can be configured either as an  $I^2C$  master or as an  $I^2C$  slave. The only difference between the two IP cores is that the primary core has pre-assigned I/O pins whereas users can assign I/O pins for the secondary core.

When the IP core is configured as a master it will be able to control other devices on the  $I^2C$  bus through the interface. When the core is configured as the slave, the device will be able to provide I/O expansion to an  $I^2C$  Master. The  $I^2C$  cores support the following functionality:

- Master and Slave operation

- 7-bit and 10-bit addressing

- Multi-master arbitration support

- Up to 400 kHz data transfer speed

- General call support

- Interface to custom logic through 8-bit WISHBONE interface

## MachXO3 Family Data Sheet DC and Switching Characteristics

#### February 2017

#### Advance Data Sheet DS1047

## Absolute Maximum Ratings<sup>1, 2, 3</sup>

|                                               | MachXO3L/LF E (1.2 V) | MachXO3L/LF C (2.5 V/3.3 V) |

|-----------------------------------------------|-----------------------|-----------------------------|

| Supply Voltage V <sub>CC</sub>                | –0.5 V to 1.32 V      | 0.5 V to 3.75 V             |

| Output Supply Voltage V <sub>CCIO</sub>       | –0.5 V to 3.75 V      | –0.5 V to 3.75 V            |

| I/O Tri-state Voltage Applied <sup>4, 5</sup> | –0.5 V to 3.75 V      | –0.5 V to 3.75 V            |

| Dedicated Input Voltage Applied <sup>4</sup>  | –0.5 V to 3.75 V      | –0.5 V to 3.75 V            |

| Storage Temperature (Ambient)                 | –55 °C to 125 °C      | –55 °C to 125 °C            |

| Junction Temperature (T <sub>J</sub> )        | –40 °C to 125 °C      | –40 °C to 125 °C            |

1. Stress above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

2. Compliance with the Lattice Thermal Management document is required.

3. All voltages referenced to GND.

4. Overshoot and undershoot of -2 V to (V<sub>IHMAX</sub> + 2) volts is permitted for a duration of <20 ns.

5. The dual function  $I^2C$  pins SCL and SDA are limited to -0.25 V to 3.75 V or to -0.3 V with a duration of <20 ns.

## **Recommended Operating Conditions**<sup>1</sup>

| Symbol                               | Parameter                                   | Min.  | Max.  | Units |

|--------------------------------------|---------------------------------------------|-------|-------|-------|

| <b>V</b> = 1                         | Core Supply Voltage for 1.2 V Devices       | 1.14  | 1.26  | V     |

| V <sub>CC</sub> <sup>1</sup>         | Core Supply Voltage for 2.5 V/3.3 V Devices | 2.375 | 3.465 | V     |

| V <sub>CCIO</sub> <sup>1, 2, 3</sup> | I/O Driver Supply Voltage                   | 1.14  | 3.465 | V     |

| t <sub>JCOM</sub>                    | Junction Temperature Commercial Operation   | 0     | 85    | °C    |

| t <sub>JIND</sub>                    | Junction Temperature Industrial Operation   | -40   | 100   | °C    |

1. Like power supplies must be tied together. For example, if V<sub>CCIO</sub> and V<sub>CC</sub> are both the same voltage, they must also be the same supply.

2. See recommended voltages by I/O standard in subsequent table.

3. V<sub>CCIO</sub> pins of unused I/O banks should be connected to the V<sub>CC</sub> power supply on boards.

## **Power Supply Ramp Rates**<sup>1</sup>

| Symbol            | Parameter                                       |      | Тур. | Max. | Units |

|-------------------|-------------------------------------------------|------|------|------|-------|

| t <sub>RAMP</sub> | Power supply ramp rates for all power supplies. | 0.01 |      | 100  | V/ms  |

1. Assumes monotonic ramp rates.

<sup>© 2017</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## Power-On-Reset Voltage Levels<sup>1, 2, 3, 4, 5</sup>

| Symbol                  | Parameter                                                                                                                                                 | Min. | Тур. | Max. | Units |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>PORUP</sub>      | Power-On-Reset ramp up trip point (band gap based circuit monitoring $V_{CCINT}$ and $V_{CCIO0})$                                                         | 0.9  | _    | 1.06 | V     |

| V <sub>PORUPEXT</sub>   | Power-On-Reset ramp up trip point (band gap based circuit monitoring external $V_{CC}$ power supply)                                                      | 1.5  | _    | 2.1  | V     |

| V <sub>PORDNBG</sub>    | $\begin{array}{c} \mbox{Power-On-Reset ramp down trip point (band gap based circuit} \\ \mbox{monitoring } V_{\mbox{CCINT}} \end{array} 0.75 \end{array}$ |      | _    | 0.93 | V     |

| V <sub>PORDNBGEXT</sub> | Power-On-Reset ramp down trip point (band gap based circuit monitoring $V_{CC})$                                                                          | 0.98 | _    | 1.33 | V     |

| V <sub>PORDNSRAM</sub>  | Power-On-Reset ramp down trip point (SRAM based circuit monitoring $V_{CCINT}$ )                                                                          | _    | 0.6  | _    | V     |

| VPORDNSRAMEXT           | Power-On-Reset ramp down trip point (SRAM based circuit monitoring $V_{CC}$ )                                                                             | _    | 0.96 | _    | V     |

1. These POR trip points are only provided for guidance. Device operation is only characterized for power supply voltages specified under recommended operating conditions.

2. For devices without voltage regulators V<sub>CCINT</sub> is the same as the V<sub>CC</sub> supply voltage. For devices with voltage regulators, V<sub>CCINT</sub> is regulated from the V<sub>CC</sub> supply voltage.

3. Note that V<sub>PORUP</sub> (min.) and V<sub>PORDNBG</sub> (max.) are in different process corners. For any given process corner V<sub>PORDNBG</sub> (max.) is always 12.0 mV below V<sub>PORUP</sub> (min.).

4. V<sub>PORUPEXT</sub> is for C devices only. In these devices a separate POR circuit monitors the external V<sub>CC</sub> power supply.

5. V<sub>CCIO0</sub> does not have a Power-On-Reset ramp down trip point. V<sub>CCIO0</sub> must remain within the Recommended Operating Conditions to ensure proper operation.

## Hot Socketing Specifications<sup>1, 2, 3</sup>

| Symbol          | Parameter                    | Condition                   | Max.    | Units |

|-----------------|------------------------------|-----------------------------|---------|-------|

| I <sub>DK</sub> | Input or I/O leakage Current | $0 < V_{IN} < V_{IH}$ (MAX) | +/-1000 | μΑ    |

1. Insensitive to sequence of  $V_{CC}$  and  $V_{CCIO}$ . However, assumes monotonic rise/fall rates for  $V_{CC}$  and  $V_{CCIO}$ .

2.  $0 < V_{CC} < V_{CC}$  (MAX),  $0 < V_{CCIO} < V_{CCIO}$  (MAX).

3. I<sub>DK</sub> is additive to I<sub>PU</sub>, I<sub>PD</sub> or I<sub>BH</sub>.

## **ESD** Performance

Please refer to the MachXO2 Product Family Qualification Summary for complete qualification data, including ESD performance.

## Programming and Erase Supply Current – C/E Devices<sup>1, 2, 3, 4</sup>

| Symbol            | Parameter                           | Device                            | Typ.⁴ | Units |

|-------------------|-------------------------------------|-----------------------------------|-------|-------|

| I <sub>CC</sub>   | Core Power Supply                   | LCMXO3L/LF-1300C 256 Ball Package | 22.1  | mA    |

|                   |                                     | LCMXO3L/LF-2100C                  | 22.1  | mA    |

|                   |                                     | LCMXO3L/LF-2100C 324 Ball Package | 26.8  | mA    |

|                   |                                     | LCMXO3L/LF-4300C                  | 26.8  | mA    |

|                   |                                     | LCMXO3L/LF-4300C 400 Ball Package | 33.2  | mA    |

|                   |                                     | LCMXO3L/LF-6900C                  | 33.2  | mA    |

|                   |                                     | LCMXO3L/LF-9400C                  | 39.6  | mA    |

|                   |                                     | LCMXO3L/LF-640E                   | 17.7  | mA    |

|                   |                                     | LCMXO3L/LF-1300E                  | 17.7  | mA    |

|                   |                                     | LCMXO3L/LF-1300E 256 Ball Package | 18.3  | mA    |

|                   |                                     | LCMXO3L/LF-2100E                  | 18.3  | mA    |

|                   |                                     | LCMXO3L/LF-2100E 324 Ball Package | 20.4  | mA    |

|                   |                                     | LCMXO3L/LF-4300E                  | 20.4  | mA    |

|                   |                                     | LCMXO3L/LF-6900E                  | 23.9  | mA    |

|                   |                                     | LCMXO3L/LF-9400E                  | 28.5  | mA    |

| I <sub>CCIO</sub> | Bank Power Supply⁵<br>VCCIO = 2.5 V | All devices                       | 0     | mA    |

1. For further information on supply current, please refer to TN1289, Power Estimation and Management for MachXO3 Devices.

2. Assumes all inputs are held at  $V_{\mbox{\scriptsize CCIO}}$  or GND and all outputs are tri-stated.

3. Typical user pattern.

4. JTAG programming is at 25 MHz.

5.  $T_J = 25$  °C, power supplies at nominal voltage.

6. Per bank.  $V_{CCIO} = 2.5$  V. Does not include pull-up/pull-down.

## sysIO Single-Ended DC Electrical Characteristics<sup>1, 2</sup>

| Input/Output        | V                     | IL                    | V                     | н        | V <sub>OL</sub> Max. | V <sub>OH</sub> Min.      | I <sub>OL</sub> Max. <sup>4</sup> | I <sub>OH</sub> Max.⁴ |

|---------------------|-----------------------|-----------------------|-----------------------|----------|----------------------|---------------------------|-----------------------------------|-----------------------|

| Standard            | Min. (V) <sup>3</sup> | Max. (V)              | Min. (V)              | Max. (V) | (V)                  | (V)                       | (mA)                              | (mA)                  |

|                     |                       |                       |                       |          |                      |                           | 4                                 | -4                    |

|                     |                       |                       |                       |          | 0.4                  | V <sub>CCIO</sub> - 0.4   | 8                                 | -8                    |

| LVCMOS 3.3<br>LVTTL | -0.3                  | 0.8                   | 2.0                   | 3.6      | 0.4                  | VCCIO - 0.4               | 12                                | -12                   |

|                     |                       |                       |                       |          |                      |                           | 16                                | -16                   |

|                     |                       |                       |                       |          | 0.2                  | V <sub>CCIO</sub> - 0.2   | 0.1                               | -0.1                  |

|                     |                       |                       |                       |          |                      |                           | 4                                 | -4                    |

|                     |                       |                       |                       |          | 0.4                  | V 0.4                     | 8                                 | -8                    |

| LVCMOS 2.5          | -0.3                  | 0.7                   | 1.7                   | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4   | 12                                | -12                   |

|                     |                       |                       |                       |          |                      |                           | 16                                | -16                   |

|                     |                       |                       |                       |          | 0.2                  | V <sub>CCIO</sub> - 0.2   | 0.1                               | -0.1                  |

|                     |                       |                       |                       |          |                      |                           | 4                                 | -4                    |

| LVCMOS 1.8          | 0.0                   |                       | 0.051/                | 0.0      | 0.4                  | V <sub>CCIO</sub> - 0.4   | 8                                 | -8                    |

| LVCINIOS 1.8        | -0.3                  | 0.35V <sub>CCIO</sub> | 0.65V <sub>CCIO</sub> | 3.6      |                      |                           | 12                                | -12                   |

|                     |                       |                       |                       |          | 0.2                  | V <sub>CCIO</sub> - 0.2   | 0.1                               | -0.1                  |

|                     |                       |                       |                       |          | 0.4                  | V 04                      | 4                                 | -4                    |

| LVCMOS 1.5          | -0.3                  | 0.35V <sub>CCIO</sub> | 0.65V <sub>CCIO</sub> | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4   | 8                                 | -8                    |

|                     |                       |                       |                       |          | 0.2                  | V <sub>CCIO</sub> - 0.2   | 0.1                               | -0.1                  |

|                     |                       |                       |                       |          | 0.4                  | V 04                      | 4                                 | -2                    |

| LVCMOS 1.2          | -0.3                  | 0.35V <sub>CCIO</sub> | 0.65V <sub>CCIO</sub> | 3.6      | 0.4                  | 4 V <sub>CCIO</sub> - 0.4 | 8                                 | -6                    |

|                     |                       |                       |                       |          | 0.2                  | V <sub>CCIO</sub> - 0.2   | 0.1                               | -0.1                  |

| LVCMOS25R33         | -0.3                  | VREF-0.1              | VREF+0.1              | 3.6      | NA                   | NA                        | NA                                | NA                    |

| LVCMOS18R33         | -0.3                  | VREF-0.1              | VREF+0.1              | 3.6      | NA                   | NA                        | NA                                | NA                    |

| LVCMOS18R25         | -0.3                  | VREF-0.1              | VREF+0.1              | 3.6      | NA                   | NA                        | NA                                | NA                    |

| LVCMOS15R33         | -0.3                  | VREF-0.1              | VREF+0.1              | 3.6      | NA                   | NA                        | NA                                | NA                    |

| LVCMOS15R25         | -0.3                  | VREF-0.1              | VREF+0.1              | 3.6      | NA                   | NA                        | NA                                | NA                    |

| LVCMOS12R33         | -0.3                  | VREF-0.1              | VREF+0.1              | 3.6      | 0.40                 | NA Open<br>Drain          | 24, 16, 12,<br>8, 4               | NA Open<br>Drain      |

| LVCMOS12R25         | -0.3                  | VREF-0.1              | VREF+0.1              | 3.6      | 0.40                 | NA Open<br>Drain          | 16, 12, 8, 4                      | NA Open<br>Drain      |

| LVCMOS10R33         | -0.3                  | VREF-0.1              | VREF+0.1              | 3.6      | 0.40                 | NA Open<br>Drain          | 24, 16, 12,<br>8, 4               | NA Open<br>Drain      |

| LVCMOS10R25         | -0.3                  | VREF-0.1              | VREF+0.1              | 3.6      | 0.40                 | NA Open<br>Drain          | 16, 12, 8, 4                      | NA Open<br>Drain      |

|                     |                       |                       |                       |          |                      |                           |                                   |                       |

MachXO3L/LF devices allow LVCMOS inputs to be placed in I/O banks where V<sub>CCIO</sub> is different from what is specified in the applicable JEDEC specification. This is referred to as a ratioed input buffer. In a majority of cases this operation follows or exceeds the applicable JEDEC specification. The cases where MachXO3L/LF devices do not meet the relevant JEDEC specification are documented in the table below.

2. MachXO3L/LF devices allow for LVCMOS referenced I/Os which follow applicable JEDEC specifications. For more details about mixed mode operation please refer to please refer to TN1280, MachXO3 sysIO Usage Guide.

3. The dual function I<sup>2</sup>C pins SCL and SDA are limited to a  $V_{IL}$  min of -0.25 V or to -0.3 V with a duration of <10 ns.

4. For electromigration, the average DC current sourced or sinked by I/O pads between two consecutive VCCIO or GND pad connections, or between the last VCCIO or GND in an I/O bank and the end of an I/O bank, as shown in the Logic Signal Connections table (also shown as I/O grouping) shall not exceed a maximum of n \* 8 mA. "n" is the number of I/O pads between the two consecutive bank VCCIO or GND connections or between the last VCCIO and GND in a bank and the end of a bank. IO Grouping can be found in the Data Sheet Pin Tables, which can also be generated from the Lattice Diamond software.

## Typical Building Block Function Performance – C/E Devices<sup>1</sup>

### Pin-to-Pin Performance (LVCMOS25 12 mA Drive)

| Function        | –6 Timing | Units |

|-----------------|-----------|-------|

| Basic Functions |           |       |

| 16-bit decoder  | 8.9       | ns    |

| 4:1 MUX         | 7.5       | ns    |

| 16:1 MUX        | 8.3       | ns    |

### **Register-to-Register Performance**

| Function                                                                     | –6 Timing | Units |

|------------------------------------------------------------------------------|-----------|-------|

| Basic Functions                                                              |           |       |

| 16:1 MUX                                                                     | 412       | MHz   |

| 16-bit adder                                                                 | 297       | MHz   |

| 16-bit counter                                                               | 324       | MHz   |

| 64-bit counter                                                               | 161       | MHz   |

| Embedded Memory Functions                                                    |           |       |

| 1024x9 True-Dual Port RAM<br>(Write Through or Normal, EBR output registers) | 183       | MHz   |

| Distributed Memory Functions                                                 |           |       |

| 16x4 Pseudo-Dual Port RAM (one PFU)                                          | 500       | MHz   |

The above timing numbers are generated using the Diamond design tool. Exact performance may vary with device and tool version. The tool uses internal parameters that have been characterized but are not tested on every device. Commercial timing numbers are shown at 85 °C and 1.14 V. Other operating conditions, including industrial, can be extracted from the Diamond software.

## **Derating Logic Timing**

Logic timing provided in the following sections of the data sheet and the Lattice design tools are worst case numbers in the operating range. Actual delays may be much faster. Lattice design tools can provide logic timing numbers at a particular temperature and voltage.

## MachXO3L/LF External Switching Characteristics – C/E Devices<sup>1, 2, 3, 4, 5, 6, 10</sup>

|                                    |                                                  |                         | _     | 6    | -     | 5    | Units |

|------------------------------------|--------------------------------------------------|-------------------------|-------|------|-------|------|-------|

| Parameter                          | Description                                      | Device                  | Min.  | Max. | Min.  | Max. |       |

| Clocks                             |                                                  | I                       |       |      |       |      |       |

| Primary Clo                        | ocks                                             |                         |       |      |       |      |       |

| f <sub>MAX_PRI</sub> <sup>7</sup>  | Frequency for Primary Clock Tree                 | All MachXO3L/LF devices |       | 388  | —     | 323  | MHz   |

| t <sub>W_PRI</sub>                 | Clock Pulse Width for Primary Clock              | All MachXO3L/LF devices | 0.5   | _    | 0.6   |      | ns    |

|                                    |                                                  | MachXO3L/LF-1300        | _     | 867  | —     | 897  | ps    |

|                                    |                                                  | MachXO3L/LF-2100        |       | 867  | _     | 897  | ps    |

| t <sub>SKEW_PRI</sub>              | Primary Clock Skew Within a Device               | MachXO3L/LF-4300        | _     | 865  | —     | 892  | ps    |

| 0.12.1                             |                                                  | MachXO3L/LF-6900        |       | 902  | _     | 942  | ps    |

|                                    |                                                  | MachXO3L/LF-9400        | _     | 908  | _     | 950  | ps    |

| Edge Clock                         |                                                  |                         |       |      |       |      |       |

| f <sub>MAX_EDGE</sub> <sup>7</sup> | Frequency for Edge Clock                         | MachXO3L/LF             | _     | 400  | _     | 333  | MHz   |

| _                                  | n Propagation Delay                              |                         |       |      |       |      |       |

| t <sub>PD</sub>                    | Best case propagation delay through one<br>LUT-4 | All MachXO3L/LF devices | _     | 6.72 | _     | 6.96 | ns    |

| General I/O                        | Pin Parameters (Using Primary Clock with         | out PLL)                |       | I    |       |      | I     |

|                                    |                                                  | MachXO3L/LF-1300        | —     | 7.46 | _     | 7.66 | ns    |

|                                    | Clock to Output - PIO Output Register            | MachXO3L/LF-2100        | _     | 7.46 | —     | 7.66 | ns    |

| t <sub>CO</sub>                    |                                                  | MachXO3L/LF-4300        | _     | 7.51 | _     | 7.71 | ns    |

| 00                                 |                                                  | MachXO3L/LF-6900        | _     | 7.54 | _     | 7.75 | ns    |

|                                    |                                                  | MachXO3L/LF-9400        | _     | 7.53 | _     | 7.83 | ns    |

|                                    |                                                  | MachXO3L/LF-1300        | -0.20 | _    | -0.20 | _    | ns    |

|                                    |                                                  | MachXO3L/LF-2100        | -0.20 |      | -0.20 | —    | ns    |

| t <sub>SU</sub>                    | Clock to Data Setup - PIO Input Register         | MachXO3L/LF-4300        | -0.23 |      | -0.23 | —    | ns    |

|                                    |                                                  | MachXO3L/LF-6900        | -0.23 |      | -0.23 | _    | ns    |

|                                    |                                                  | MachXO3L/LF-9400        | -0.24 |      | -0.24 | _    | ns    |

|                                    |                                                  | MachXO3L/LF-1300        | 1.89  |      | 2.13  | _    | ns    |

|                                    |                                                  | MachXO3L/LF-2100        | 1.89  |      | 2.13  |      | ns    |

| t <sub>H</sub>                     | Clock to Data Hold - PIO Input Register          | MachXO3L/LF-4300        | 1.94  |      | 2.18  |      | ns    |

|                                    |                                                  | MachXO3L/LF-6900        | 1.98  |      | 2.23  | _    | ns    |

|                                    |                                                  | MachXO3L/LF-9400        | 1.99  |      | 2.24  |      | ns    |

|                                    |                                                  | MachXO3L/LF-1300        | 1.61  |      | 1.76  |      | ns    |

|                                    |                                                  | MachXO3L/LF-2100        | 1.61  |      | 1.76  |      | ns    |

| t <sub>SU_DEL</sub>                | Clock to Data Setup - PIO Input Register         | MachXO3L/LF-4300        | 1.66  |      | 1.81  |      | ns    |

| JU_DLL                             | with Data Input Delay                            | MachXO3L/LF-6900        | 1.53  |      | 1.67  |      | ns    |

|                                    |                                                  | MachXO3L/LF-9400        | 1.65  |      | 1.80  |      | ns    |

|                                    |                                                  | MachXO3L/LF-1300        | -0.23 |      | -0.23 |      | ns    |

|                                    |                                                  | MachXO3L/LF-2100        | -0.23 |      | -0.23 |      | ns    |

| t <sub>H_DEL</sub>                 | Clock to Data Hold - PIO Input Register with     | MachXO3L/LF-4300        | -0.25 |      | -0.25 |      | ns    |

| ILUEL                              | Input Data Delay                                 | MachXO3L/LF-6900        | -0.21 | _    | -0.21 |      | ns    |

|                                    |                                                  | MachXO3L/LF-9400        | -0.24 |      | -0.24 |      | ns    |

| f <sub>MAX_IO</sub>                | Clock Frequency of I/O and PFU Register          | All MachXO3L/LF devices |       | 388  |       | 323  | MHz   |

### Over Recommended Operating Conditions

## DC and Switching Characteristics MachXO3 Family Data Sheet

|                      |                                                                   |                  | -     | 6    | -5    |      |       |  |

|----------------------|-------------------------------------------------------------------|------------------|-------|------|-------|------|-------|--|

| Parameter            | Description                                                       | Device           | Min.  | Max. | Min.  | Max. | Units |  |

| General I/O          | Pin Parameters (Using Edge Clock without                          | t PLL)           |       |      | 1     |      | 1     |  |

|                      |                                                                   | MachXO3L/LF-1300 | —     | 7.53 | —     | 7.76 | ns    |  |

|                      |                                                                   | MachXO3L/LF-2100 | —     | 7.53 | —     | 7.76 | ns    |  |

| t <sub>COE</sub>     | Clock to Output - PIO Output Register                             | MachXO3L/LF-4300 | —     | 7.45 |       | 7.68 | ns    |  |

|                      |                                                                   | MachXO3L/LF-6900 | —     | 7.53 |       | 7.76 | ns    |  |

|                      |                                                                   | MachXO3L/LF-9400 | —     | 8.93 | —     | 9.35 | ns    |  |

|                      |                                                                   | MachXO3L/LF-1300 | -0.19 |      | -0.19 |      | ns    |  |

|                      |                                                                   | MachXO3L/LF-2100 | -0.19 |      | -0.19 | _    | ns    |  |

| t <sub>SUE</sub>     | Clock to Data Setup - PIO Input Register                          | MachXO3L/LF-4300 | -0.16 | _    | -0.16 | _    | ns    |  |

|                      |                                                                   | MachXO3L/LF-6900 | -0.19 |      | -0.19 |      | ns    |  |

|                      |                                                                   | MachXO3L/LF-9400 | -0.20 | _    | -0.20 | _    | ns    |  |

|                      |                                                                   | MachXO3L/LF-1300 | 1.97  | _    | 2.24  | _    | ns    |  |

|                      |                                                                   | MachXO3L/LF-2100 | 1.97  |      | 2.24  |      | ns    |  |

| t <sub>HE</sub>      | Clock to Data Hold - PIO Input Register                           | MachXO3L/LF-4300 | 1.89  |      | 2.16  |      | ns    |  |

|                      |                                                                   | MachXO3L/LF-6900 | 1.97  | _    | 2.24  | _    | ns    |  |

|                      |                                                                   | MachXO3L/LF-9400 | 1.98  |      | 2.25  |      | ns    |  |

|                      | Clock to Data Setup - PIO Input Register<br>with Data Input Delay | MachXO3L/LF-1300 | 1.56  |      | 1.69  | _    | ns    |  |

|                      |                                                                   | MachXO3L/LF-2100 | 1.56  |      | 1.69  |      | ns    |  |

| t <sub>SU_DELE</sub> |                                                                   | MachXO3L/LF-4300 | 1.74  | _    | 1.88  | _    | ns    |  |

| _                    |                                                                   | MachXO3L/LF-6900 | 1.66  | _    | 1.81  | _    | ns    |  |

|                      |                                                                   | MachXO3L/LF-9400 | 1.71  |      | 1.85  |      | ns    |  |

|                      | Clock to Data Hold - PIO Input Register with<br>Input Data Delay  | MachXO3L/LF-1300 | -0.23 | _    | -0.23 | _    | ns    |  |

|                      |                                                                   | MachXO3L/LF-2100 | -0.23 |      | -0.23 |      | ns    |  |

| t <sub>H_DELE</sub>  |                                                                   | MachXO3L/LF-4300 | -0.34 |      | -0.34 |      | ns    |  |

|                      | input bata bolay                                                  | MachXO3L/LF-6900 | -0.29 |      | -0.29 |      | ns    |  |

|                      |                                                                   | MachXO3L/LF-9400 | -0.30 |      | -0.30 |      | ns    |  |

| General I/O          | Pin Parameters (Using Primary Clock with                          | PLL)             |       |      |       |      |       |  |

|                      |                                                                   | MachXO3L/LF-1300 | —     | 5.98 |       | 6.01 | ns    |  |

|                      |                                                                   | MachXO3L/LF-2100 | —     | 5.98 | _     | 6.01 | ns    |  |

| t <sub>COPLL</sub>   | Clock to Output - PIO Output Register                             | MachXO3L/LF-4300 | —     | 5.99 | —     | 6.02 | ns    |  |

|                      |                                                                   | MachXO3L/LF-6900 | —     | 6.02 | _     | 6.06 | ns    |  |

|                      |                                                                   | MachXO3L/LF-9400 | —     | 5.55 | _     | 6.13 | ns    |  |

|                      |                                                                   | MachXO3L/LF-1300 | 0.36  | _    | 0.36  | —    | ns    |  |

|                      |                                                                   | MachXO3L/LF-2100 | 0.36  |      | 0.36  | _    | ns    |  |

| t <sub>SUPLL</sub>   | Clock to Data Setup - PIO Input Register                          | MachXO3L/LF-4300 | 0.35  |      | 0.35  |      | ns    |  |

|                      |                                                                   | MachXO3L/LF-6900 | 0.34  | —    | 0.34  | —    | ns    |  |

|                      |                                                                   | MachXO3L/LF-9400 | 0.33  |      | 0.33  |      | ns    |  |

|                      |                                                                   | MachXO3L/LF-1300 | 0.42  |      | 0.49  |      | ns    |  |

|                      |                                                                   | MachXO3L/LF-2100 | 0.42  | —    | 0.49  | —    | ns    |  |

| t <sub>HPLL</sub>    | Clock to Data Hold - PIO Input Register                           | MachXO3L/LF-4300 | 0.43  | —    | 0.50  | _    | ns    |  |

|                      |                                                                   | MachXO3L/LF-6900 | 0.46  |      | 0.54  |      | ns    |  |

|                      |                                                                   | MachXO3L/LF-9400 | 0.47  | —    | 0.55  | —    | ns    |  |

|                        |                                                                            |                                          | -         | -6      | -5       |        |                     |

|------------------------|----------------------------------------------------------------------------|------------------------------------------|-----------|---------|----------|--------|---------------------|

| Parameter              | Description                                                                | Device                                   | Min.      | Max.    | Min.     | Max.   | Units               |

| Generic DDF            | RX1 Inputs with Clock and Data Aligned at                                  | Pin Using PCLK Pin for Cl                | ock Inpu  | it —    |          |        |                     |

| GDDRX1_RX              | K.SCLK.Aligned <sup>8, 9</sup>                                             | -                                        | -         |         |          |        |                     |

| t <sub>DVA</sub>       | Input Data Valid After CLK                                                 |                                          |           | 0.317   | —        | 0.344  | UI                  |

| t <sub>DVE</sub>       | Input Data Hold After CLK                                                  | All MachXO3L/LF<br>devices,              | 0.742     | —       | 0.702    |        | UI                  |

| f <sub>DATA</sub>      | DDRX1 Input Data Speed                                                     | all sides                                | —         | 300     | —        | 250    | Mbps                |

| f <sub>DDRX1</sub>     | DDRX1 SCLK Frequency                                                       |                                          | —         | 150     | —        | 125    | MHz                 |

| Generic DD<br>GDDRX1_R | RX1 Inputs with Clock and Data Centered<br>X.SCLK.Centered <sup>8, 9</sup> | d at Pin Using PCLK Pin fo               | or Clock  | Input – |          |        |                     |

| t <sub>SU</sub>        | Input Data Setup Before CLK                                                |                                          | 0.566     | —       | 0.560    | —      | ns                  |

| t <sub>HO</sub>        | Input Data Hold After CLK                                                  | All MachXO3L/LF                          | 0.778     | —       | 0.879    | —      | ns                  |

| f <sub>DATA</sub>      | DDRX1 Input Data Speed                                                     | devices,<br>all sides                    |           | 300     | —        |        | Mbps                |

| f <sub>DDRX1</sub>     | DDRX1 SCLK Frequency                                                       |                                          |           | 150     | —        | 125    | MHz                 |

|                        | RX2 Inputs with Clock and Data Aligned a K.ECLK.Aligned <sup>8,9</sup>     | t Pin Using PCLK Pin for C               | Clock Inp | out –   | 1        | ı      |                     |

| t <sub>DVA</sub>       | Input Data Valid After CLK                                                 |                                          | —         | 0.316   | —        | 0.342  | UI                  |

| t <sub>DVE</sub>       | Input Data Hold After CLK                                                  | _                                        | 0.710     |         | 0.675    |        | UI                  |

| f <sub>DATA</sub>      | DDRX2 Serial Input Data Speed                                              | MachXO3L/LF devices,                     |           | 664     |          | 554    | Mbps                |

| f <sub>DDRX2</sub>     | DDRX2 ECLK Frequency                                                       | _bottom side only                        |           | 332     | _        | 277    | MHz                 |

| f <sub>SCLK</sub>      | SCLK Frequency                                                             | _                                        |           | 166     |          | 139    | MHz                 |

|                        | RX2 Inputs with Clock and Data Centered                                    | at Pin Using PCLK Pin for                | Clock II  | nput –  |          |        | ł                   |

|                        | K.ECLK.Centered <sup>8,9</sup>                                             | Ū                                        |           | •       |          |        |                     |

| t <sub>SU</sub>        | Input Data Setup Before CLK                                                |                                          | 0.233     | —       | 0.219    |        | ns                  |

| t <sub>HO</sub>        | Input Data Hold After CLK                                                  |                                          | 0.287     | —       | 0.287    |        | ns                  |

| f <sub>DATA</sub>      | DDRX2 Serial Input Data Speed                                              | MachXO3L/LF devices,                     |           | 664     | —        | 554    | Mbps                |

| f <sub>DDRX2</sub>     | DDRX2 ECLK Frequency                                                       | ,                                        |           | 332     | —        | 277    | MHz                 |

| f <sub>SCLK</sub>      | SCLK Frequency                                                             |                                          |           | 166     | —        | 139    | MHz                 |

| Generic DDF            | R4 Inputs with Clock and Data Aligned at F                                 | in Using PCLK Pin for Cloo               | k Input   | – GDDR  | X4_RX.   | ECLK.A | ligned <sup>8</sup> |

| t <sub>DVA</sub>       | Input Data Valid After ECLK                                                |                                          |           | 0.307   | —        | 0.320  | UI                  |

| t <sub>DVE</sub>       | Input Data Hold After ECLK                                                 |                                          | 0.782     |         | 0.699    |        | UI                  |

| f <sub>DATA</sub>      | DDRX4 Serial Input Data Speed                                              | MachXO3L/LF devices,<br>bottom side only | —         | 800     | —        | 630    | Mbps                |

| f <sub>DDRX4</sub>     | DDRX4 ECLK Frequency                                                       |                                          |           | 400     | —        | 315    | MHz                 |

| f <sub>SCLK</sub>      | SCLK Frequency                                                             |                                          |           | 100     | —        | 79     | MHz                 |

| Generic DDF            | 4 Inputs with Clock and Data Centered at I                                 | Pin Using PCLK Pin for Cloo              | k Input   | - GDDR  | X4_RX.E  | CLK.Ce | ntered <sup>8</sup> |

| t <sub>SU</sub>        | Input Data Setup Before ECLK                                               |                                          | 0.233     |         | 0.219    |        | ns                  |

| t <sub>HO</sub>        | Input Data Hold After ECLK                                                 |                                          | 0.287     |         | 0.287    |        | ns                  |

| f <sub>DATA</sub>      | DDRX4 Serial Input Data Speed                                              | MachXO3L/LF devices,<br>bottom side only |           | 800     | —        | 630    | Mbps                |

| f <sub>DDRX4</sub>     | DDRX4 ECLK Frequency                                                       |                                          |           | 400     | —        | 315    | MHz                 |

| f <sub>SCLK</sub>      | SCLK Frequency                                                             |                                          | _         | 100     | —        | 79     | MHz                 |

| 7:1 LVDS In            | outs (GDDR71_RX.ECLK.7:1) <sup>9</sup>                                     |                                          | 1         | 1       | 1        | 1      | L                   |

| t <sub>DVA</sub>       | Input Data Valid After ECLK                                                |                                          | _         | 0.290   |          | 0.320  | UI                  |

| t <sub>DVE</sub>       | Input Data Hold After ECLK                                                 |                                          | 0.739     |         | 0.699    |        | UI                  |

| f <sub>DATA</sub>      | DDR71 Serial Input Data Speed                                              | MachXO3L/LF devices,                     | —         | 756     | —        | 630    | Mbps                |

| f <sub>DDR71</sub>     | DDR71 ECLK Frequency                                                       | bottom side only                         | <u> </u>  | 378     | <b> </b> | 315    | MHz                 |

| f <sub>CLKIN</sub>     | 7:1 Input Clock Frequency (SCLK) (mini-<br>mum limited by PLL)             | ii-                                      |           | 108     | _        | 90     | MHz                 |

LCMXO3L-9400C-6BG4841

484

IND

| Part Number           | LUTs | Supply Voltage | Speed    | Package             | Leads | Temp. |

|-----------------------|------|----------------|----------|---------------------|-------|-------|

| LCMXO3L-6900E-5MG256C | 6900 | 1.2 V          | 5        | Halogen-Free csfBGA | 256   | COM   |

| LCMXO3L-6900E-6MG256C | 6900 | 1.2 V          | 6        | Halogen-Free csfBGA | 256   | COM   |

| LCMXO3L-6900E-5MG256I | 6900 | 1.2 V          | 5        | Halogen-Free csfBGA | 256   | IND   |

| LCMXO3L-6900E-6MG256I | 6900 | 1.2 V          | 6        | Halogen-Free csfBGA | 256   | IND   |

| LCMXO3L-6900E-5MG324C | 6900 | 1.2 V          | 5        | Halogen-Free csfBGA | 324   | COM   |

| LCMXO3L-6900E-6MG324C | 6900 | 1.2 V          | 6        | Halogen-Free csfBGA | 324   | COM   |

| LCMXO3L-6900E-5MG324I | 6900 | 1.2 V          | 5        | Halogen-Free csfBGA | 324   | IND   |

| LCMXO3L-6900E-6MG324I | 6900 | 1.2 V          | 6        | Halogen-Free csfBGA | 324   | IND   |

| LCMXO3L-6900C-5BG256C | 6900 | 2.5 V / 3.3 V  | 5        | Halogen-Free caBGA  | 256   | COM   |

| LCMXO3L-6900C-6BG256C | 6900 | 2.5 V / 3.3 V  | 6        | Halogen-Free caBGA  | 256   | COM   |

| LCMXO3L-6900C-5BG256I | 6900 | 2.5 V / 3.3 V  | 5        | Halogen-Free caBGA  | 256   | IND   |

| LCMXO3L-6900C-6BG256I | 6900 | 2.5 V / 3.3 V  | 6        | Halogen-Free caBGA  | 256   | IND   |

| LCMXO3L-6900C-5BG324C | 6900 | 2.5 V / 3.3 V  | 5        | Halogen-Free caBGA  | 324   | COM   |

| LCMXO3L-6900C-6BG324C | 6900 | 2.5 V / 3.3 V  | 6        | Halogen-Free caBGA  | 324   | COM   |

| LCMXO3L-6900C-5BG324I | 6900 | 2.5 V / 3.3 V  | 5        | Halogen-Free caBGA  | 324   | IND   |

| LCMXO3L-6900C-6BG324I | 6900 | 2.5 V / 3.3 V  | 6        | Halogen-Free caBGA  | 324   | IND   |

| LCMXO3L-6900C-5BG400C | 6900 | 2.5 V / 3.3 V  | 5        | Halogen-Free caBGA  | 400   | COM   |

| LCMXO3L-6900C-6BG400C | 6900 | 2.5 V / 3.3 V  | 6        | Halogen-Free caBGA  | 400   | COM   |

| LCMXO3L-6900C-5BG4001 | 6900 | 2.5 V / 3.3 V  | 5        | Halogen-Free caBGA  | 400   | IND   |

| LCMXO3L-6900C-6BG400I | 6900 | 2.5 V / 3.3 V  | 6        | Halogen-Free caBGA  | 400   | IND   |

|                       |      |                | <u> </u> | <b></b>             |       | -     |

| Part Number           | LUTs | Supply Voltage | Speed    | Package             | Leads | Temp. |

| LCMXO3L-9400E-5MG256C | 9400 | 1.2 V          | 5        | Halogen-Free csfBGA | 256   | COM   |

| LCMXO3L-9400E-6MG256C | 9400 | 1.2 V          | 6        | Halogen-Free csfBGA | 256   | COM   |

| LCMXO3L-9400E-5MG256I | 9400 | 1.2 V          | 5        | Halogen-Free csfBGA | 256   | IND   |

| LCMXO3L-9400E-6MG256I | 9400 | 1.2 V          | 6        | Halogen-Free csfBGA | 256   | IND   |

| LCMXO3L-9400C-5BG256C | 9400 | 2.5 V/3.3 V    | 5        | Halogen-Free caBGA  | 256   | COM   |

| LCMXO3L-9400C-6BG256C | 9400 | 2.5 V/3.3 V    | 6        | Halogen-Free caBGA  | 256   | COM   |

| LCMXO3L-9400C-5BG256I | 9400 | 2.5 V/3.3 V    | 5        | Halogen-Free caBGA  | 256   | IND   |

| LCMXO3L-9400C-6BG256I | 9400 | 2.5 V/3.3 V    | 6        | Halogen-Free caBGA  | 256   | IND   |

| LCMXO3L-9400C-5BG400C | 9400 | 2.5 V/3.3 V    | 5        | Halogen-Free caBGA  | 400   | COM   |

| LCMXO3L-9400C-6BG400C | 9400 | 2.5 V/3.3 V    | 6        | Halogen-Free caBGA  | 400   | COM   |

| LCMXO3L-9400C-5BG400I | 9400 | 2.5 V/3.3 V    | 5        | Halogen-Free caBGA  | 400   | IND   |

| LCMXO3L-9400C-6BG400I | 9400 | 2.5 V/3.3 V    | 6        | Halogen-Free caBGA  | 400   | IND   |

| LCMXO3L-9400C-5BG484C | 9400 | 2.5 V/3.3 V    | 5        | Halogen-Free caBGA  | 484   | COM   |

| LCMXO3L-9400C-6BG484C | 9400 | 2.5 V/3.3 V    | 6        | Halogen-Free caBGA  | 484   | COM   |

| LCMXO3L-9400C-5BG484I | 9400 | 2.5 V/3.3 V    | 5        | Halogen-Free caBGA  | 484   | IND   |

2.5 V/3.3 V

6

Halogen-Free caBGA

9400

| Part Number                | LUTs | Supply Voltage | Speed | Package             | Leads | Temp. |

|----------------------------|------|----------------|-------|---------------------|-------|-------|

| LCMXO3LF-2100E-6MG324I     | 2100 | 1.2 V          | 6     | Halogen-Free csfBGA | 324   | IND   |

| LCMXO3LF-2100C-5BG256C     | 2100 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 256   | COM   |

| LCMXO3LF-2100C-6BG256C     | 2100 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 256   | COM   |

| LCMXO3LF-2100C-5BG256I     | 2100 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 256   | IND   |

| LCMXO3LF-2100C-6BG256I     | 2100 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 256   | IND   |

| LCMXO3LF-2100C-5BG324C     | 2100 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 324   | COM   |

| LCMXO3LF-2100C-6BG324C     | 2100 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 324   | COM   |

| LCMXO3LF-2100C-5BG324I     | 2100 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 324   | IND   |

| LCMXO3LF-2100C-6BG324I     | 2100 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 324   | IND   |

|                            |      |                |       |                     |       |       |

| Part Number                | LUTs | Supply Voltage | Speed | Package             | Leads | Temp. |

| LCMXO3LF-4300E-5UWG81CTR   | 4300 | 1.2 V          | 5     | Halogen-Free WLCSP  | 81    | COM   |

| LCMXO3LF-4300E-5UWG81CTR50 | 4300 | 1.2 V          | 5     | Halogen-Free WLCSP  | 81    | COM   |

| LCMXO3LF-4300E-5UWG81CTR1K | 4300 | 1.2 V          | 5     | Halogen-Free WLCSP  | 81    | COM   |

| LCMXO3LF-4300E-5UWG81ITR   | 4300 | 1.2 V          | 5     | Halogen-Free WLCSP  | 81    | IND   |

| LCMXO3LF-4300E-5UWG81ITR50 | 4300 | 1.2 V          | 5     | Halogen-Free WLCSP  | 81    | IND   |

| LCMXO3LF-4300E-5UWG81ITR1K | 4300 | 1.2 V          | 5     | Halogen-Free WLCSP  | 81    | IND   |

| LCMXO3LF-4300E-5MG121C     | 4300 | 1.2 V          | 5     | Halogen-Free csfBGA | 121   | COM   |

| LCMXO3LF-4300E-6MG121C     | 4300 | 1.2 V          | 6     | Halogen-Free csfBGA | 121   | COM   |

| LCMXO3LF-4300E-5MG121I     | 4300 | 1.2 V          | 5     | Halogen-Free csfBGA | 121   | IND   |

| LCMXO3LF-4300E-6MG121I     | 4300 | 1.2 V          | 6     | Halogen-Free csfBGA | 121   | IND   |

| LCMXO3LF-4300E-5MG256C     | 4300 | 1.2 V          | 5     | Halogen-Free csfBGA | 256   | COM   |

| LCMXO3LF-4300E-6MG256C     | 4300 | 1.2 V          | 6     | Halogen-Free csfBGA | 256   | COM   |

| LCMXO3LF-4300E-5MG256I     | 4300 | 1.2 V          | 5     | Halogen-Free csfBGA | 256   | IND   |

| LCMXO3LF-4300E-6MG256I     | 4300 | 1.2 V          | 6     | Halogen-Free csfBGA | 256   | IND   |

| LCMXO3LF-4300E-5MG324C     | 4300 | 1.2 V          | 5     | Halogen-Free csfBGA | 324   | COM   |

| LCMXO3LF-4300E-6MG324C     | 4300 | 1.2 V          | 6     | Halogen-Free csfBGA | 324   | COM   |

| LCMXO3LF-4300E-5MG324I     | 4300 | 1.2 V          | 5     | Halogen-Free csfBGA | 324   | IND   |

| LCMXO3LF-4300E-6MG324I     | 4300 | 1.2 V          | 6     | Halogen-Free csfBGA | 324   | IND   |

| LCMXO3LF-4300C-5BG256C     | 4300 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 256   | COM   |

| LCMXO3LF-4300C-6BG256C     | 4300 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 256   | COM   |

| LCMXO3LF-4300C-5BG256I     | 4300 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 256   | IND   |

| LCMXO3LF-4300C-6BG256I     | 4300 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 256   | IND   |

| LCMXO3LF-4300C-5BG324C     | 4300 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 324   | COM   |

| LCMXO3LF-4300C-6BG324C     | 4300 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 324   | COM   |

| LCMXO3LF-4300C-5BG324I     | 4300 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 324   | IND   |

| LCMXO3LF-4300C-6BG324I     | 4300 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 324   | IND   |

| LCMXO3LF-4300C-5BG400C     | 4300 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 400   | COM   |

| LCMXO3LF-4300C-6BG400C     | 4300 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 400   | COM   |

| LCMXO3LF-4300C-5BG400I     | 4300 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 400   | IND   |

| LCMXO3LF-4300C-6BG400I     | 4300 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 400   | IND   |

## MachXO3 Family Data Sheet Supplemental Information

#### January 2016

Advance Data Sheet DS1047

### For Further Information

A variety of technical notes for the MachXO3 family are available on the Lattice web site.

- TN1282, MachXO3 sysCLOCK PLL Design and Usage Guide

- TN1281, Implementing High-Speed Interfaces with MachXO3 Devices

- TN1280, MachXO3 sysIO Usage Guide

- TN1279, MachXO3 Programming and Configuration Usage Guide

- TN1074, PCB Layout Recommendations for BGA Packages

- TN1087, Minimizing System Interruption During Configuration Using TransFR Technology

- AN8066, Boundary Scan Testability with Lattice sysIO Capability

- MachXO3 Device Pinout Files

- Thermal Management document

- Lattice design tools

© 2016 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Date       | Version                             | Section                                                                                                                | Change Summary                                                                                                                                                                                                                                                                            |

|------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| April 2016 | April 2016 1.6 Introduction         | Introduction                                                                                                           | Updated Features section.<br>— Revised logic density range and IO to LUT ratio under Flexible Archi-<br>tecture.<br>— Revised 0.8 mm pitch information under Advanced Packaging.<br>— Added MachXO3L-9400/MachXO3LF-9400 information to Table 1-1,<br>MachXO3L/LF Family Selection Guide. |

|            |                                     | Updated Introduction section.<br>— Changed density from 6900 to 9400 LUTs.<br>— Changed caBGA packaging to 19 x 19 mm. |                                                                                                                                                                                                                                                                                           |