Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                                  |

|--------------------------------|----------------------------------------------------------------------------------|

| Product Status                 | Active                                                                           |

| Number of LABs/CLBs            | 80                                                                               |

| Number of Logic Elements/Cells | 640                                                                              |

| Total RAM Bits                 | 65536                                                                            |

| Number of I/O                  | 100                                                                              |

| Number of Gates                | -                                                                                |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                    |

| Mounting Type                  | Surface Mount                                                                    |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                               |

| Package / Case                 | 121-VFBGA, CSPBGA                                                                |

| Supplier Device Package        | 121-CSFBGA (6x6)                                                                 |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lcmxo3lf-640e-5mg121i |

|                                |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Table 1-1. MachXO3L/LF Family Selection Guide

| Features                                                |                                  | MachXO3L-640/<br>MachXO3LF-640 | MachXO3L-1300/<br>MachXO3LF-1300 | MachXO3L-2100/<br>MachXO3LF-2100 | MachXO3L-4300/<br>MachXO3LF-4300 | MachXO3L-6900/<br>MachXO3LF-6900 | MachXO3L-9400/<br>MachXO3LF-9400 |

|---------------------------------------------------------|----------------------------------|--------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|

| LUTs                                                    |                                  | 640                            | 1300                             | 2100                             | 4300                             | 6900                             | 9400                             |

| Distributed R                                           | AM (kbits)                       | 5                              | 10                               | 16                               | 34                               | 54                               | 73                               |

| EBR SRAM (                                              | kbits)                           | 64                             | 64                               | 74                               | 92                               | 240                              | 432                              |

| Number of PL                                            | Ls                               | 1                              | 1                                | 1                                | 2                                | 2                                | 2                                |

| Hardened                                                | I <sup>2</sup> C                 | 2                              | 2                                | 2                                | 2                                | 2                                | 2                                |

| Functions:                                              | SPI                              | 1                              | 1                                | 1                                | 1                                | 1                                | 1                                |

|                                                         | Timer/Counter                    | 1                              | 1                                | 1                                | 1                                | 1                                | 1                                |

|                                                         | Oscillator                       | 1                              | 1                                | 1                                | 1                                | 1                                | 1                                |

| MIPI D-PHY                                              | Support                          | Yes                            | Yes                              | Yes                              | Yes                              | Yes                              | Yes                              |

| Multi Time Pr<br>NVCM                                   | ogrammable                       | MachXO3L-640                   | MachXO3L-1300                    | MachXO3L-2100                    | MachXO3L-4300                    | MachXO3L-6900                    | MachXO3L-9400                    |

| Programmabl                                             | le Flash                         | MachXO3LF-640                  | MachXO3LF-1300                   | MachXO3LF-2100                   | MachXO3LF-4300                   | MachXO3LF-6900                   | MachXO3LF-9400                   |

| Packages                                                |                                  |                                |                                  | ю                                |                                  |                                  |                                  |

| 36-ball WLCS<br>(2.5 mm x 2.5                           | SP <sup>1</sup><br>5 mm, 0.4 mm) |                                | 28                               |                                  |                                  |                                  |                                  |

| 49-ball WLCS<br>(3.2 mm x 3.2                           | SP <sup>1</sup><br>2 mm, 0.4 mm) |                                |                                  | 38                               |                                  |                                  |                                  |

| 81-ball WLCS<br>(3.8 mm x 3.8                           | SP <sup>1</sup><br>3 mm, 0.4 mm) |                                |                                  |                                  | 63                               |                                  |                                  |

| 121-ball csfB<br>(6 mm x 6 mr                           |                                  | 100                            | 100                              | 100                              | 100                              |                                  |                                  |

| 256-ball csfB<br>(9 mm x 9 mr                           |                                  | 2                              | 206                              | 206                              | 206                              | 206                              | 206                              |

| 324-ball csfBGA <sup>1</sup><br>(10 mm x 10 mm, 0.5 mm) |                                  |                                |                                  | 268                              | 268                              | 281                              |                                  |

| 256-ball caBGA <sup>2</sup><br>(14 mm x 14 mm, 0.8 mm)  |                                  |                                | 206                              | 206                              | 206                              | 206                              | 206                              |

| 324-ball caB0<br>(15 mm x 15                            |                                  |                                |                                  | 279                              | 279                              | 279                              |                                  |

| 400-ball caB0<br>(17 mm x 17                            |                                  |                                |                                  |                                  | 335                              | 335                              | 335                              |

| 484-ball caB0<br>(19 mm x 19                            |                                  |                                |                                  |                                  |                                  |                                  | 384                              |

1. Package is only available for E=1.2 V devices.

2. Package is only available for C=2.5 V/3.3 V devices.

### Introduction

MachXO3<sup>™</sup> device family is an Ultra-Low Density family that supports the most advanced programmable bridging and IO expansion. It has the breakthrough IO density and the lowest cost per IO. The device IO features have the integrated support for latest industry standard IO.

The MachXO3L/LF family of low power, instant-on, non-volatile PLDs has five devices with densities ranging from 640 to 9400 Look-Up Tables (LUTs). In addition to LUT-based, low-cost programmable logic these devices feature Embedded Block RAM (EBR), Distributed RAM, Phase Locked Loops (PLLs), pre-engineered source synchronous I/O support, advanced configuration support including dual-boot capability and hardened versions of commonly used functions such as SPI controller, I<sup>2</sup>C controller and timer/counter. MachXO3LF devices also support User Flash Memory (UFM). These features allow these devices to be used in low cost, high volume consumer and system applications.

The MachXO3L/LF devices are designed on a 65nm non-volatile low power process. The device architecture has several features such as programmable low swing differential I/Os and the ability to turn off I/O banks, on-chip PLLs

and oscillators dynamically. These features help manage static and dynamic power consumption resulting in low static power for all members of the family.

The MachXO3L/LF devices are available in two versions C and E with two speed grades: -5 and -6, with -6 being the fastest. C devices have an internal linear voltage regulator which supports external VCC supply voltages of 3.3 V or 2.5 V. E devices only accept 1.2 V as the external VCC supply voltage. With the exception of power supply voltage both C and E are functionally compatible with each other.

The MachXO3L/LF PLDs are available in a broad range of advanced halogen-free packages ranging from the space saving 2.5 x 2.5 mm WLCSP to the 19 x 19 mm caBGA. MachXO3L/LF devices support density migration within the same package. Table 1-1 shows the LUT densities, package and I/O options, along with other key parameters.

The MachXO3L/LF devices offer enhanced I/O features such as drive strength control, slew rate control, PCI compatibility, bus-keeper latches, pull-up resistors, pull-down resistors, open drain outputs and hot socketing. Pull-up, pull-down and bus-keeper features are controllable on a "per-pin" basis.

A user-programmable internal oscillator is included in MachXO3L/LF devices. The clock output from this oscillator may be divided by the timer/counter for use as clock input in functions such as LED control, key-board scanner and similar state machines.

The MachXO3L/LF devices also provide flexible, reliable and secure configuration from on-chip NVCM/Flash. These devices can also configure themselves from external SPI Flash or be configured by an external master through the JTAG test access port or through the I<sup>2</sup>C port. Additionally, MachXO3L/LF devices support dual-boot capability (using external Flash memory) and remote field upgrade (TransFR) capability.

Lattice provides a variety of design tools that allow complex designs to be efficiently implemented using the MachXO3L/LF family of devices. Popular logic synthesis tools provide synthesis library support for MachXO3L/LF. Lattice design tools use the synthesis tool output along with the user-specified preferences and constraints to place and route the design in the MachXO3L/LF device. These tools extract the timing from the routing and back-annotate it into the design for timing verification.

Lattice provides many pre-engineered IP (Intellectual Property) LatticeCORE<sup>™</sup> modules, including a number of reference designs licensed free of charge, optimized for the MachXO3L/LF PLD family. By using these configurable soft core IP cores as standardized blocks, users are free to concentrate on the unique aspects of their design, increasing their productivity.

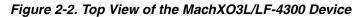

MachXO3L/LF-1300, MachXO3L/LF-2100, MachXO3L/LF-6900 and MachXO3L/LF-9400 are similar to MachXO3L/LF-4300. MachXO3L/LF-1300 has a lower LUT count, one PLL, and seven EBR blocks. MachXO3L/LF-2100 has a lower LUT count, one PLL, and eight EBR blocks. MachXO3L/LF-6900 has a higher LUT count, two PLLs, and 26 EBR blocks. MachXO3L/LF-9400 has a higher LUT count, two PLLs, and 48 EBR blocks.

• MachXO3L devices have NVCM, MachXO3LF devices have Flash.

The logic blocks, Programmable Functional Unit (PFU) and sysMEM EBR blocks, are arranged in a two-dimensional grid with rows and columns. Each row has either the logic blocks or the EBR blocks. The PIO cells are located at the periphery of the device, arranged in banks. The PFU contains the building blocks for logic, arithmetic, RAM, ROM, and register functions. The PIOs utilize a flexible I/O buffer referred to as a sysIO buffer that supports operation with a variety of interface standards. The blocks are connected with many vertical and horizontal routing channel resources. The place and route software tool automatically allocates these routing resources.

In the MachXO3L/LF family, the number of sysIO banks varies by device. There are different types of I/O buffers on the different banks. Refer to the details in later sections of this document. The sysMEM EBRs are large, dedicated fast memory blocks. These blocks can be configured as RAM, ROM or FIFO. FIFO support includes dedicated FIFO pointer and flag "hard" control logic to minimize LUT usage.

The MachXO3L/LF registers in PFU and sysI/O can be configured to be SET or RESET. After power up and device is configured, the device enters into user mode with these registers SET/RESET according to the configuration setting, allowing device entering to a known state for predictable system function.

The MachXO3L/LF architecture also provides up to two sysCLOCK Phase Locked Loop (PLL) blocks. These blocks are located at the ends of the on-chip NVCM/Flash block. The PLLs have multiply, divide, and phase shifting capabilities that are used to manage the frequency and phase relationships of the clocks.

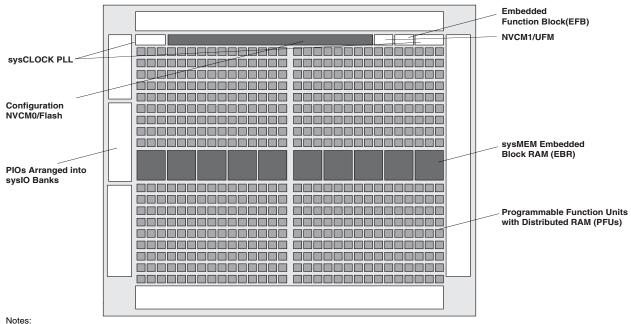

MachXO3L/LF devices provide commonly used hardened functions such as SPI controller, I<sup>2</sup>C controller and timer/ counter.

MachXO3LF devices also provide User Flash Memory (UFM). These hardened functions and the UFM interface to the core logic and routing through a WISHBONE interface. The UFM can also be accessed through the SPI, I<sup>2</sup>C and JTAG ports.

Every device in the family has a JTAG port that supports programming and configuration of the device as well as access to the user logic. The MachXO3L/LF devices are available for operation from 3.3 V, 2.5 V and 1.2 V power sup-plies, providing easy integration into the overall system.

Table 2-5. sysMEM Block Configurations

| Memory Mode      | Configurations                                               |

|------------------|--------------------------------------------------------------|

| Single Port      | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9             |

| True Dual Port   | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9             |

| Pseudo Dual Port | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18 |

| FIFO             | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18 |

#### Bus Size Matching

All of the multi-port memory modes support different widths on each of the ports. The RAM bits are mapped LSB word 0 to MSB word 0, LSB word 1 to MSB word 1, and so on. Although the word size and number of words for each port varies, this mapping scheme applies to each port.

#### **RAM Initialization and ROM Operation**

If desired, the contents of the RAM can be pre-loaded during device configuration. EBR initialization data can be loaded from the NVCM or Configuration Flash.

MachXO3LF EBR initialization data can also be loaded from the UFM. To maximize the number of UFM bits, initialize the EBRs used in your design to an all-zero pattern. Initializing to an all-zero pattern does not use up UFM bits. MachXO3LF devices have been designed such that multiple EBRs share the same initialization memory space if they are initialized to the same pattern.

By preloading the RAM block during the chip configuration cycle and disabling the write controls, the sysMEM block can also be utilized as a ROM.

#### Memory Cascading

Larger and deeper blocks of RAM can be created using EBR sysMEM Blocks. Typically, the Lattice design tools cascade memory transparently, based on specific design inputs.

#### Single, Dual, Pseudo-Dual Port and FIFO Modes

Figure 2-8 shows the five basic memory configurations and their input/output names. In all the sysMEM RAM modes, the input data and addresses for the ports are registered at the input of the memory array. The output data of the memory is optionally registered at the memory array output.

### Output Gearbox

Each PIC on the top edge has a built-in 8:1 output gearbox. Each of these output gearboxes may be programmed as a 7:1 serializer or as one ODDRX4 (8:1) gearbox or as two ODDRX2 (4:1) gearboxes. Table 2-10 shows the gearbox signals.

### Table 2-10. Output Gearbox Signal List

| Name                       | I/O Type | Description                     |

|----------------------------|----------|---------------------------------|

| Q                          | Output   | High-speed data output          |

| D[7:0]                     | Input    | Low-speed data from device core |

| Video TX(7:1): D[6:0]      |          |                                 |

| GDDRX4(8:1): D[7:0]        |          |                                 |

| GDDRX2(4:1)(IOL-A): D[3:0] |          |                                 |

| GDDRX2(4:1)(IOL-C): D[7:4] |          |                                 |

| SCLK                       | Input    | Slow-speed system clock         |

| ECLK [1:0]                 | Input    | High-speed edge clock           |

| RST                        | Input    | Reset                           |

The gearboxes have three stage pipeline registers. The first stage registers sample the low-speed input data on the low-speed system clock. The second stage registers transfer data from the low-speed clock registers to the high-speed clock registers. The third stage pipeline registers controlled by high-speed edge clock shift and mux the high-speed data out to the sysIO buffer. Figure 2-14 shows the output gearbox block diagram.

There are some limitations on the use of the hardened user SPI. These are defined in the following technical notes:

- TN1087, Minimizing System Interruption During Configuration Using TransFR Technology (Appendix B)

- TN1293, Using Hardened Control Functions in MachXO3 Devices

### Figure 2-19. SPI Core Block Diagram

Table 2-15 describes the signals interfacing with the SPI cores.

Table 2-15. SPI Core Signal Description

| Signal Name | I/O | Master/Slave | Description                                                                                                                                                                               |  |

|-------------|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| spi_csn[0]  | 0   | Master       | SPI master chip-select output                                                                                                                                                             |  |

| spi_csn[17] | 0   | Master       | Additional SPI chip-select outputs (total up to eight slaves)                                                                                                                             |  |

| spi_scsn    | I   | Slave        | SPI slave chip-select input                                                                                                                                                               |  |

| spi_irq     | 0   | Master/Slave | Interrupt request                                                                                                                                                                         |  |

| spi_clk     | I/O | Master/Slave | SPI clock. Output in master mode. Input in slave mode.                                                                                                                                    |  |

| spi_miso    | I/O | Master/Slave | SPI data. Input in master mode. Output in slave mode.                                                                                                                                     |  |

| spi_mosi    | I/O | Master/Slave | SPI data. Output in master mode. Input in slave mode.                                                                                                                                     |  |

| sn          | I   | Slave        | Configuration Slave Chip Select (active low), dedicated for selecting the Co figuration Logic.                                                                                            |  |

| cfg_stdby   | 0   | Master/Slave | Stand-by signal – To be connected only to the power module of the MachXO3L/LF device. The signal is enabled only if the "Wakeup Enable" feature has been set within the EFB GUI, SPI Tab. |  |

| cfg_wake    | О   | Master/Slave | Wake-up signal – To be connected only to the power module of the MachXO3L/LF device. The signal is enabled only if the "Wakeup Enable" feature has been set within the EFB GUI, SPI Tab.  |  |

For more details on these embedded functions, please refer to TN1293, Using Hardened Control Functions in MachXO3 Devices.

### **User Flash Memory (UFM)**

MachXO3LF devices provide a User Flash Memory block, which can be used for a variety of applications including storing a portion of the configuration image, initializing EBRs, to store PROM data or, as a general purpose user Flash memory. The UFM block connects to the device core through the embedded function block WISHBONE interface. Users can also access the UFM block through the JTAG, I2C and SPI interfaces of the device. The UFM block offers the following features:

- Non-volatile storage up to 256 kbits

- 100K write cycles

- Write access is performed page-wise; each page has 128 bits (16 bytes)

- Auto-increment addressing

- WISHBONE interface

For more information on the UFM, please refer to TN1293, Using Hardened Control Functions in MachXO3 Devices.

### **Standby Mode and Power Saving Options**

MachXO3L/LF devices are available in two options, the C and E devices. The C devices have a built-in voltage regulator to allow for 2.5 V V<sub>CC</sub> and 3.3 V V<sub>CC</sub> while the E devices operate at 1.2 V V<sub>CC</sub>.

MachXO3L/LF devices have been designed with features that allow users to meet the static and dynamic power requirements of their applications by controlling various device subsystems such as the bandgap, power-on-reset circuitry, I/O bank controllers, power guard, on-chip oscillator, PLLs, etc. In order to maximize power savings, MachXO3L/LF devices support a low power Stand-by mode.

In the stand-by mode the MachXO3L/LF devices are powered on and configured. Internal logic, I/Os and memories are switched on and remain operational, as the user logic waits for an external input. The device enters this mode when the standby input of the standby controller is toggled or when an appropriate I<sup>2</sup>C or JTAG instruction is issued by an external master. Various subsystems in the device such as the band gap, power-on-reset circuitry etc can be configured such that they are automatically turned "off" or go into a low power consumption state to save power when the device enters this state. Note that the MachXO3L/LF devices are powered on when in standby mode and all power supplies should remain in the Recommended Operating Conditions.

# MachXO3 Family Data Sheet DC and Switching Characteristics

#### February 2017

#### Advance Data Sheet DS1047

## Absolute Maximum Ratings<sup>1, 2, 3</sup>

|                                               | MachXO3L/LF E (1.2 V) | MachXO3L/LF C (2.5 V/3.3 V) |

|-----------------------------------------------|-----------------------|-----------------------------|

| Supply Voltage V <sub>CC</sub>                | –0.5 V to 1.32 V      | 0.5 V to 3.75 V             |

| Output Supply Voltage V <sub>CCIO</sub>       | –0.5 V to 3.75 V      | –0.5 V to 3.75 V            |

| I/O Tri-state Voltage Applied <sup>4, 5</sup> | –0.5 V to 3.75 V      | –0.5 V to 3.75 V            |

| Dedicated Input Voltage Applied <sup>4</sup>  | –0.5 V to 3.75 V      | –0.5 V to 3.75 V            |

| Storage Temperature (Ambient)                 | –55 °C to 125 °C      | –55 °C to 125 °C            |

| Junction Temperature (T <sub>J</sub> )        | –40 °C to 125 °C      | –40 °C to 125 °C            |

1. Stress above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

2. Compliance with the Lattice Thermal Management document is required.

3. All voltages referenced to GND.

4. Overshoot and undershoot of -2 V to (V<sub>IHMAX</sub> + 2) volts is permitted for a duration of <20 ns.

5. The dual function  $I^2C$  pins SCL and SDA are limited to -0.25 V to 3.75 V or to -0.3 V with a duration of <20 ns.

## **Recommended Operating Conditions**<sup>1</sup>

| Symbol                               | Parameter                                      |       | Max.  | Units |

|--------------------------------------|------------------------------------------------|-------|-------|-------|

| <b>V</b> = 1                         | Core Supply Voltage for 1.2 V Devices          | 1.14  | 1.26  | V     |

| V <sub>CC</sub> <sup>1</sup>         | Core Supply Voltage for 2.5 V/3.3 V Devices    | 2.375 | 3.465 | V     |

| V <sub>CCIO</sub> <sup>1, 2, 3</sup> | I/O Driver Supply Voltage                      | 1.14  | 3.465 | V     |

| t <sub>JCOM</sub>                    | JCOM Junction Temperature Commercial Operation |       | 85    | °C    |

| t <sub>JIND</sub>                    | Junction Temperature Industrial Operation      | -40   | 100   | °C    |

1. Like power supplies must be tied together. For example, if V<sub>CCIO</sub> and V<sub>CC</sub> are both the same voltage, they must also be the same supply.

2. See recommended voltages by I/O standard in subsequent table.

3. V<sub>CCIO</sub> pins of unused I/O banks should be connected to the V<sub>CC</sub> power supply on boards.

### **Power Supply Ramp Rates**<sup>1</sup>

| Symbol            | Parameter                                       | Min. | Тур. | Max. | Units |

|-------------------|-------------------------------------------------|------|------|------|-------|

| t <sub>RAMP</sub> | Power supply ramp rates for all power supplies. | 0.01 |      | 100  | V/ms  |

1. Assumes monotonic ramp rates.

<sup>© 2017</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# Power-On-Reset Voltage Levels<sup>1, 2, 3, 4, 5</sup>

| Symbol                  | Parameter                                                                                            | Min. | Тур. | Max. | Units |

|-------------------------|------------------------------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>PORUP</sub>      | Power-On-Reset ramp up trip point (band gap based circuit monitoring $V_{CCINT}$ and $V_{CCIO0})$    | 0.9  | _    | 1.06 | V     |

| V <sub>PORUPEXT</sub>   | Power-On-Reset ramp up trip point (band gap based circuit monitoring external $V_{CC}$ power supply) | 1.5  | _    | 2.1  | V     |

| V <sub>PORDNBG</sub>    | Power-On-Reset ramp down trip point (band gap based circuit monitoring $V_{\mbox{CCINT}})$           | 0.75 | _    | 0.93 | V     |

| V <sub>PORDNBGEXT</sub> | Power-On-Reset ramp down trip point (band gap based circuit monitoring $V_{CC})$                     | 0.98 | _    | 1.33 | V     |

| V <sub>PORDNSRAM</sub>  | Power-On-Reset ramp down trip point (SRAM based circuit monitoring $V_{CCINT}$ )                     | _    | 0.6  | _    | V     |

| VPORDNSRAMEXT           | Power-On-Reset ramp down trip point (SRAM based circuit monitoring $V_{CC}$ )                        | _    | 0.96 | _    | V     |

1. These POR trip points are only provided for guidance. Device operation is only characterized for power supply voltages specified under recommended operating conditions.

2. For devices without voltage regulators V<sub>CCINT</sub> is the same as the V<sub>CC</sub> supply voltage. For devices with voltage regulators, V<sub>CCINT</sub> is regulated from the V<sub>CC</sub> supply voltage.

3. Note that V<sub>PORUP</sub> (min.) and V<sub>PORDNBG</sub> (max.) are in different process corners. For any given process corner V<sub>PORDNBG</sub> (max.) is always 12.0 mV below V<sub>PORUP</sub> (min.).

4. V<sub>PORUPEXT</sub> is for C devices only. In these devices a separate POR circuit monitors the external V<sub>CC</sub> power supply.

5. V<sub>CCIO0</sub> does not have a Power-On-Reset ramp down trip point. V<sub>CCIO0</sub> must remain within the Recommended Operating Conditions to ensure proper operation.

### Hot Socketing Specifications<sup>1, 2, 3</sup>

| Symbol          | Parameter                    | Condition                   | Max.    | Units |

|-----------------|------------------------------|-----------------------------|---------|-------|

| I <sub>DK</sub> | Input or I/O leakage Current | $0 < V_{IN} < V_{IH}$ (MAX) | +/-1000 | μΑ    |

1. Insensitive to sequence of  $V_{CC}$  and  $V_{CCIO}$ . However, assumes monotonic rise/fall rates for  $V_{CC}$  and  $V_{CCIO}$ .

2.  $0 < V_{CC} < V_{CC}$  (MAX),  $0 < V_{CCIO} < V_{CCIO}$  (MAX).

3. I<sub>DK</sub> is additive to I<sub>PU</sub>, I<sub>PD</sub> or I<sub>BH</sub>.

### **ESD** Performance

Please refer to the MachXO2 Product Family Qualification Summary for complete qualification data, including ESD performance.

|           | Description                                                            | Min. | Тур. | Max. | Units |

|-----------|------------------------------------------------------------------------|------|------|------|-------|

| Low Power |                                                                        |      |      |      |       |

| VCCIO     | VCCIO of the Bank with LVCMOS12D 6 mA<br>drive bidirectional IO buffer |      | 1.2  |      | V     |

| VIH       | Logic 1 input voltage                                                  | —    | _    | 0.88 | V     |

| VIL       | Logic 0 input voltage, not in ULP State                                | 0.55 | _    | _    | V     |

| VHYST     | Input hysteresis                                                       | 25   | —    | —    | mV    |

1. Over Recommended Operating Conditions

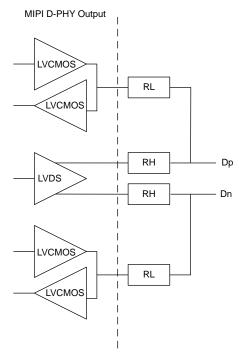

### Figure 3-5. MIPI D-PHY Output Using External Resistors

## Maximum sysIO Buffer Performance

| I/O Standard | Max. Speed | Units |

|--------------|------------|-------|

| MIPI         | 450        | MHz   |

| LVDS25       | 400        | MHz   |

| LVDS25E      | 150        | MHz   |

| BLVDS25      | 150        | MHz   |

| BLVDS25E     | 150        | MHz   |

| MLVDS25      | 150        | MHz   |

| MLVDS25E     | 150        | MHz   |

| LVPECL33     | 150        | MHz   |

| LVPECL33E    | 150        | MHz   |

| LVTTL33      | 150        | MHz   |

| LVTTL33D     | 150        | MHz   |

| LVCMOS33     | 150        | MHz   |

| LVCMOS33D    | 150        | MHz   |

| LVCMOS25     | 150        | MHz   |

| LVCMOS25D    | 150        | MHz   |

| LVCMOS18     | 150        | MHz   |

| LVCMOS18D    | 150        | MHz   |

| LVCMOS15     | 150        | MHz   |

| LVCMOS15D    | 150        | MHz   |

| LVCMOS12     | 91         | MHz   |

| LVCMOS12D    | 91         | MHz   |

# MachXO3L/LF External Switching Characteristics – C/E Devices<sup>1, 2, 3, 4, 5, 6, 10</sup>

|                                    |                                                  |                         | _     | 6    | -     | 5    |       |  |

|------------------------------------|--------------------------------------------------|-------------------------|-------|------|-------|------|-------|--|

| Parameter                          | Description                                      | Device                  | Min.  | Max. | Min.  | Max. | Units |  |

| Clocks                             |                                                  | I                       |       |      |       |      |       |  |

| Primary Clo                        | ocks                                             |                         |       |      |       |      |       |  |

| f <sub>MAX_PRI</sub> <sup>7</sup>  | Frequency for Primary Clock Tree                 | All MachXO3L/LF devices |       | 388  | —     | 323  | MHz   |  |

| t <sub>W_PRI</sub>                 | Clock Pulse Width for Primary Clock              | All MachXO3L/LF devices | 0.5   | _    | 0.6   |      | ns    |  |

|                                    |                                                  | MachXO3L/LF-1300        | _     | 867  | —     | 897  | ps    |  |

|                                    |                                                  | MachXO3L/LF-2100        |       | 867  | _     | 897  | ps    |  |

| t <sub>SKEW_PRI</sub>              | Primary Clock Skew Within a Device               | MachXO3L/LF-4300        | _     | 865  | —     | 892  | ps    |  |

| 0.12.1                             |                                                  | MachXO3L/LF-6900        |       | 902  | _     | 942  | ps    |  |

|                                    |                                                  | MachXO3L/LF-9400        | _     | 908  | _     | 950  | ps    |  |

| Edge Clock                         |                                                  |                         |       |      |       |      |       |  |

| f <sub>MAX_EDGE</sub> <sup>7</sup> | Frequency for Edge Clock                         | MachXO3L/LF             | _     | 400  | _     | 333  | MHz   |  |

| _                                  | n Propagation Delay                              |                         |       |      |       |      |       |  |

| t <sub>PD</sub>                    | Best case propagation delay through one<br>LUT-4 | All MachXO3L/LF devices | _     | 6.72 | _     | 6.96 | ns    |  |

| General I/O                        | Pin Parameters (Using Primary Clock with         | out PLL)                |       | I    |       |      | I     |  |

|                                    |                                                  | MachXO3L/LF-1300        | —     | 7.46 | _     | 7.66 | ns    |  |

|                                    | Clock to Output - PIO Output Register            | MachXO3L/LF-2100        | _     | 7.46 | —     | 7.66 | ns    |  |

| t <sub>CO</sub>                    |                                                  | MachXO3L/LF-4300        | _     | 7.51 | _     | 7.71 | ns    |  |

|                                    |                                                  | MachXO3L/LF-6900        | _     | 7.54 | _     | 7.75 | ns    |  |

|                                    |                                                  | MachXO3L/LF-9400        | _     | 7.53 | _     | 7.83 | ns    |  |

|                                    |                                                  | MachXO3L/LF-1300        | -0.20 | _    | -0.20 | _    | ns    |  |

|                                    |                                                  | MachXO3L/LF-2100        | -0.20 |      | -0.20 | —    | ns    |  |

| t <sub>SU</sub>                    | Clock to Data Setup - PIO Input Register         | MachXO3L/LF-4300        | -0.23 |      | -0.23 | —    | ns    |  |

|                                    |                                                  | MachXO3L/LF-6900        | -0.23 |      | -0.23 | _    | ns    |  |

|                                    |                                                  | MachXO3L/LF-9400        | -0.24 |      | -0.24 | _    | ns    |  |

|                                    |                                                  | MachXO3L/LF-1300        | 1.89  |      | 2.13  | _    | ns    |  |

|                                    |                                                  | MachXO3L/LF-2100        | 1.89  |      | 2.13  |      | ns    |  |

| t <sub>H</sub>                     | Clock to Data Hold - PIO Input Register          | MachXO3L/LF-4300        | 1.94  |      | 2.18  |      | ns    |  |

|                                    |                                                  | MachXO3L/LF-6900        | 1.98  |      | 2.23  | _    | ns    |  |

|                                    |                                                  | MachXO3L/LF-9400        | 1.99  |      | 2.24  |      | ns    |  |

|                                    |                                                  | MachXO3L/LF-1300        | 1.61  |      | 1.76  |      | ns    |  |

|                                    |                                                  | MachXO3L/LF-2100        | 1.61  |      | 1.76  |      | ns    |  |

| t <sub>SU_DEL</sub>                | Clock to Data Setup - PIO Input Register         | MachXO3L/LF-4300        | 1.66  |      | 1.81  |      | ns    |  |

| JU_DLL                             | with Data Input Delay                            | MachXO3L/LF-6900        | 1.53  |      | 1.67  |      | ns    |  |

|                                    |                                                  | MachXO3L/LF-9400        | 1.65  |      | 1.80  |      | ns    |  |

|                                    |                                                  | MachXO3L/LF-1300        | -0.23 |      | -0.23 |      | ns    |  |

|                                    |                                                  | MachXO3L/LF-2100        | -0.23 |      | -0.23 |      | ns    |  |

| t <sub>H_DEL</sub>                 | Clock to Data Hold - PIO Input Register with     | MachXO3L/LF-4300        | -0.25 | _    | -0.25 |      | ns    |  |

| ILUEL                              | Input Data Delay                                 | MachXO3L/LF-6900        | -0.21 | _    | -0.21 |      | ns    |  |

|                                    |                                                  | MachXO3L/LF-9400        | -0.24 |      | -0.24 |      | ns    |  |

| f <sub>MAX_IO</sub>                | Clock Frequency of I/O and PFU Register          | All MachXO3L/LF devices |       | 388  |       | 323  | MHz   |  |

### Over Recommended Operating Conditions

|                        |                                                                            |                                          | -         | -6      | -5       |        |                     |

|------------------------|----------------------------------------------------------------------------|------------------------------------------|-----------|---------|----------|--------|---------------------|

| Parameter              | Description                                                                | Device                                   | Min.      | Max.    | Min.     | Max.   | Units               |

| Generic DDF            | RX1 Inputs with Clock and Data Aligned at                                  | Pin Using PCLK Pin for Cl                | ock Inpu  | it —    |          |        |                     |

| GDDRX1_RX              | K.SCLK.Aligned <sup>8, 9</sup>                                             | -                                        | -         |         |          |        |                     |

| t <sub>DVA</sub>       | Input Data Valid After CLK                                                 |                                          |           | 0.317   | —        | 0.344  | UI                  |

| t <sub>DVE</sub>       | Input Data Hold After CLK                                                  | All MachXO3L/LF<br>devices,              | 0.742     | —       | 0.702    |        | UI                  |

| f <sub>DATA</sub>      | DDRX1 Input Data Speed                                                     | all sides                                | —         | 300     | —        | 250    | Mbps                |

| f <sub>DDRX1</sub>     | DDRX1 SCLK Frequency                                                       |                                          | —         | 150     | —        | 125    | MHz                 |

| Generic DD<br>GDDRX1_R | RX1 Inputs with Clock and Data Centered<br>X.SCLK.Centered <sup>8, 9</sup> | d at Pin Using PCLK Pin fo               | or Clock  | Input – |          |        |                     |

| t <sub>SU</sub>        | Input Data Setup Before CLK                                                |                                          | 0.566     | —       | 0.560    |        | ns                  |

| t <sub>HO</sub>        | Input Data Hold After CLK                                                  | All MachXO3L/LF                          | 0.778     | —       | 0.879    | —      | ns                  |

| f <sub>DATA</sub>      | DDRX1 Input Data Speed                                                     | devices,<br>all sides                    |           | 300     | —        |        | Mbps                |

| f <sub>DDRX1</sub>     | DDRX1 SCLK Frequency                                                       |                                          |           | 150     | —        | 125    | MHz                 |

|                        | RX2 Inputs with Clock and Data Aligned a K.ECLK.Aligned <sup>8,9</sup>     | t Pin Using PCLK Pin for C               | Clock Inp | out –   | 1        | ı      |                     |

| t <sub>DVA</sub>       | Input Data Valid After CLK                                                 |                                          | —         | 0.316   | —        | 0.342  | UI                  |

| t <sub>DVE</sub>       | Input Data Hold After CLK                                                  | _                                        | 0.710     |         | 0.675    |        | UI                  |

| f <sub>DATA</sub>      | DDRX2 Serial Input Data Speed                                              | MachXO3L/LF devices,                     |           | 664     |          | 554    | Mbps                |

| f <sub>DDRX2</sub>     | DDRX2 ECLK Frequency                                                       | _bottom side only                        |           | 332     | _        | 277    | MHz                 |

| f <sub>SCLK</sub>      | SCLK Frequency                                                             | _                                        |           | 166     |          | 139    | MHz                 |

|                        | RX2 Inputs with Clock and Data Centered                                    | at Pin Using PCLK Pin for                | Clock II  | nput –  |          |        | ł                   |

|                        | K.ECLK.Centered <sup>8,9</sup>                                             | Ū                                        |           | •       |          |        |                     |

| t <sub>SU</sub>        | Input Data Setup Before CLK                                                |                                          | 0.233     | —       | 0.219    |        | ns                  |

| t <sub>HO</sub>        | Input Data Hold After CLK                                                  |                                          | 0.287     | —       | 0.287    |        | ns                  |

| f <sub>DATA</sub>      | DDRX2 Serial Input Data Speed                                              | MachXO3L/LF devices,                     |           | 664     | —        | 554    | Mbps                |

| f <sub>DDRX2</sub>     | DDRX2 ECLK Frequency                                                       | ,                                        |           | 332     | —        | 277    | MHz                 |

| f <sub>SCLK</sub>      | SCLK Frequency                                                             |                                          |           | 166     | —        | 139    | MHz                 |

| Generic DDF            | R4 Inputs with Clock and Data Aligned at F                                 | in Using PCLK Pin for Cloo               | k Input   | – GDDR  | X4_RX.   | ECLK.A | ligned <sup>8</sup> |

| t <sub>DVA</sub>       | Input Data Valid After ECLK                                                |                                          |           | 0.307   | —        | 0.320  | UI                  |

| t <sub>DVE</sub>       | Input Data Hold After ECLK                                                 |                                          | 0.782     |         | 0.699    |        | UI                  |

| f <sub>DATA</sub>      | DDRX4 Serial Input Data Speed                                              | MachXO3L/LF devices,<br>bottom side only | —         | 800     | —        | 630    | Mbps                |

| f <sub>DDRX4</sub>     | DDRX4 ECLK Frequency                                                       |                                          |           | 400     | —        | 315    | MHz                 |

| f <sub>SCLK</sub>      | SCLK Frequency                                                             |                                          |           | 100     | —        | 79     | MHz                 |

| Generic DDF            | 4 Inputs with Clock and Data Centered at I                                 | Pin Using PCLK Pin for Cloo              | k Input   | - GDDR  | X4_RX.E  | CLK.Ce | ntered <sup>8</sup> |

| t <sub>SU</sub>        | Input Data Setup Before ECLK                                               |                                          | 0.233     |         | 0.219    |        | ns                  |

| t <sub>HO</sub>        | Input Data Hold After ECLK                                                 |                                          | 0.287     | —       | 0.287    |        | ns                  |

| f <sub>DATA</sub>      | DDRX4 Serial Input Data Speed                                              | MachXO3L/LF devices,<br>bottom side only |           | 800     | —        | 630    | Mbps                |

| f <sub>DDRX4</sub>     | DDRX4 ECLK Frequency                                                       |                                          |           | 400     | —        | 315    | MHz                 |

| f <sub>SCLK</sub>      | SCLK Frequency                                                             |                                          | _         | 100     | —        | 79     | MHz                 |

| 7:1 LVDS Inp           | outs (GDDR71_RX.ECLK.7:1) <sup>9</sup>                                     |                                          | 1         | 1       | 1        | 1      | L                   |

| t <sub>DVA</sub>       | Input Data Valid After ECLK                                                |                                          | _         | 0.290   |          | 0.320  | UI                  |

| t <sub>DVE</sub>       | Input Data Hold After ECLK                                                 |                                          | 0.739     |         | 0.699    |        | UI                  |

| f <sub>DATA</sub>      | DDR71 Serial Input Data Speed                                              | MachXO3L/LF devices,                     | —         | 756     | —        | 630    | Mbps                |

| f <sub>DDR71</sub>     | DDR71 ECLK Frequency                                                       | bottom side only                         | <u> </u>  | 378     | <b> </b> | 315    | MHz                 |

| f <sub>CLKIN</sub>     | 7:1 Input Clock Frequency (SCLK) (mini-<br>mum limited by PLL)             |                                          | _         | 108     | _        | 90     | MHz                 |

|                                  |                                                                                |                              | -6       |         | -       | 5       |                      |

|----------------------------------|--------------------------------------------------------------------------------|------------------------------|----------|---------|---------|---------|----------------------|

| Parameter                        | Description                                                                    | Device                       | Min.     | Max.    | Min.    | Max.    | Units                |

| MIPI D-PHY                       | Inputs with Clock and Data Centered at P                                       | in Using PCLK Pin for Cloo   | k Input  | -       |         |         | 1                    |

|                                  | X.ECLK.Centered <sup>10, 11, 12</sup>                                          |                              | 1        | I       | I       |         | I                    |

| t <sub>SU</sub> <sup>15</sup>    | Input Data Setup Before ECLK                                                   |                              | 0.200    | —       | 0.200   |         | UI                   |

| t <sub>HO</sub> <sup>15</sup>    | Input Data Hold After ECLK                                                     | All MachXO3L/LF              | 0.200    | —       | 0.200   | —       | UI                   |

| f <sub>DATA</sub> <sup>14</sup>  | MIPI D-PHY Input Data Speed                                                    | devices, bottom side only    |          | 900     | —       | 900     | Mbps                 |

| f <sub>DDRX4</sub> <sup>14</sup> | MIPI D-PHY ECLK Frequency                                                      |                              |          | 450     | —       | 450     | MHz                  |

| f <sub>SCLK</sub> <sup>14</sup>  | SCLK Frequency                                                                 |                              |          | 112.5   | —       | 112.5   | MHz                  |

| Generic DDI                      | R Outputs with Clock and Data Aligned at I                                     | Pin Using PCLK Pin for Clo   | ck Input | – GDDF  | RX1_TX. | SCLK.A  | ligned <sup>8</sup>  |

| t <sub>DIA</sub>                 | Output Data Invalid After CLK Output                                           |                              |          | 0.520   | —       | 0.550   | ns                   |

| t <sub>DIB</sub>                 | Output Data Invalid Before CLK Output                                          | All MachXO3L/LF<br>devices.  |          | 0.520   | —       | 0.550   | ns                   |

| f <sub>DATA</sub>                | DDRX1 Output Data Speed                                                        | all sides                    | —        | 300     | —       | 250     | Mbps                 |

| f <sub>DDRX1</sub>               | DDRX1 SCLK frequency                                                           |                              |          | 150     | —       | 125     | MHz                  |

|                                  | R Outputs with Clock and Data Centered at                                      | Pin Using PCLK Pin for Cloo  | k Input  | – GDDR  | X1_TX.9 | SCLK.Ce | entered <sup>8</sup> |

| t <sub>DVB</sub>                 | Output Data Valid Before CLK Output                                            |                              | 1.210    |         | 1.510   |         | ns                   |

| t <sub>DVA</sub>                 | Output Data Valid After CLK Output                                             | All MachXO3L/LF              | 1.210    |         | 1.510   |         | ns                   |

| f <sub>DATA</sub>                | DDRX1 Output Data Speed                                                        | devices,                     |          | 300     | —       | 250     | Mbps                 |

| f <sub>DDRX1</sub>               | DDRX1 SCLK Frequency<br>(minimum limited by PLL)                               | all sides                    | _        | 150     | —       | 125     | MHz                  |

| Generic DDF                      | RX2 Outputs with Clock and Data Aligned a                                      | t Pin Using PCLK Pin for Clo | ock Inpu | t – GDD | RX2_TX  | .ECLK.A | \ligned <sup>8</sup> |

| t <sub>DIA</sub>                 | Output Data Invalid After CLK Output                                           |                              | _        | 0.200   | —       | 0.215   | ns                   |

| t <sub>DIB</sub>                 | Output Data Invalid Before CLK Output                                          |                              |          | 0.200   | —       | 0.215   | ns                   |

| f <sub>DATA</sub>                | DDRX2 Serial Output Data Speed                                                 | MachXO3L/LF devices,         |          | 664     | —       | 554     | Mbps                 |

| f <sub>DDRX2</sub>               | DDRX2 ECLK frequency                                                           | top side only                |          | 332     | _       | 277     | MHz                  |

| f <sub>SCLK</sub>                | SCLK Frequency                                                                 |                              |          | 166     | _       | 139     | MHz                  |

|                                  | RX2 Outputs with Clock and Data Centere                                        | ed at Pin Using PCLK Pin fo  | or Clock | Input – |         |         | <u> </u>             |

|                                  | K.ECLK.Centered <sup>8, 9</sup>                                                | 0                            |          | •       |         |         |                      |

| t <sub>DVB</sub>                 | Output Data Valid Before CLK Output                                            |                              | 0.535    |         | 0.670   | _       | ns                   |

| t <sub>DVA</sub>                 | Output Data Valid After CLK Output                                             |                              | 0.535    | —       | 0.670   |         | ns                   |

| f <sub>DATA</sub>                | DDRX2 Serial Output Data Speed                                                 | MachXO3L/LF devices,         |          | 664     | —       | 554     | Mbps                 |

| f <sub>DDRX2</sub>               | DDRX2 ECLK Frequency<br>(minimum limited by PLL)                               | top side only                | _        | 332     | _       | 277     | MHz                  |

| f <sub>SCLK</sub>                | SCLK Frequency                                                                 |                              |          | 166     | —       | 139     | MHz                  |

| Generic DD                       | L<br>RX4 Outputs with Clock and Data Aligned<br>K.ECLK.Aligned <sup>8, 9</sup> | at Pin Using PCLK Pin for    | Clock I  | nput –  | 1       |         | L                    |

| t <sub>DIA</sub>                 | Output Data Invalid After CLK Output                                           |                              | _        | 0.200   | —       | 0.215   | ns                   |

| t <sub>DIB</sub>                 | Output Data Invalid Before CLK Output                                          | -                            |          | 0.200   |         | 0.215   | ns                   |

| f <sub>DATA</sub>                | DDRX4 Serial Output Data Speed                                                 | MachXO3L/LF devices,         |          | 800     |         | 630     | Mbps                 |

| f <sub>DDRX4</sub>               | DDRX4 ECLK Frequency                                                           | top side only                |          | 400     |         | 315     | MHz                  |

| f <sub>SCLK</sub>                | SCLK Frequency                                                                 | -                            |          | 100     |         | 79      | MHz                  |

| SOLK                             |                                                                                |                              |          |         |         |         |                      |

### sysCLOCK PLL Timing

| Parameter                       | Descriptions                                   | Conditions                              | Min.   | Max.  | Units      |  |

|---------------------------------|------------------------------------------------|-----------------------------------------|--------|-------|------------|--|

| :<br>IN                         | Input Clock Frequency (CLKI, CLKFB)            |                                         | 7      | 400   | MHz        |  |

| OUT                             | Output Clock Frequency (CLKOP, CLKOS, CLKOS2)  |                                         | 1.5625 | 400   | MHz        |  |

| OUT2                            | Output Frequency (CLKOS3 cascaded from CLKOS2) |                                         | 0.0122 | 400   | MHz        |  |

| fvco                            | PLL VCO Frequency                              |                                         | 200    | 800   | MHz        |  |

| PFD                             | Phase Detector Input Frequency                 |                                         | 7      | 400   | MHz        |  |

| AC Characteri                   | istics                                         | •                                       |        |       |            |  |

| <sup>t</sup> dt                 | Output Clock Duty Cycle                        | Without duty trim selected <sup>3</sup> | 45     | 55    | %          |  |

| DT_TRIM <sup>7</sup>            | Edge Duty Trim Accuracy                        |                                         | -75    | 75    | %          |  |

| t <sub>PH</sub> <sup>4</sup>    | Output Phase Accuracy                          |                                         | -6     | 6     | %          |  |

|                                 | Outrout Clask Daviad Littar                    | f <sub>OUT</sub> > 100 MHz              | —      | 150   | ps p-p     |  |

| t <sub>opjit</sub> 1,8          | Output Clock Period Jitter                     | f <sub>OUT</sub> < 100 MHz              | —      | 0.007 | UIPP       |  |

|                                 | Output Cleak Cycle to avala littar             | f <sub>OUT</sub> > 100 MHz              | —      | 180   | ps p-p     |  |

|                                 | Output Clock Cycle-to-cycle Jitter             | f <sub>OUT</sub> < 100 MHz              | —      | 0.009 | UIPP       |  |

|                                 | Output Clock Phase litter                      | f <sub>PFD</sub> > 100 MHz              | —      | 160   | ps p-p     |  |

|                                 | Output Clock Phase Jitter                      | f <sub>PFD</sub> < 100 MHz              | —      | 0.011 | UIPP       |  |

|                                 | Output Clock Pariod littar (Eractional N)      | f <sub>OUT</sub> > 100 MHz              | —      | 230   | ps p-p     |  |

|                                 | Output Clock Period Jitter (Fractional-N)      | f <sub>OUT</sub> < 100 MHz              | _      | 0.12  | UIPP       |  |

|                                 | Output Clock Cycle-to-cycle Jitter             | f <sub>OUT</sub> > 100 MHz              | —      | 230   | ps p-p     |  |

|                                 | (Fractional-N)                                 | f <sub>OUT</sub> < 100 MHz              |        | 0.12  | UIPP       |  |

| t <sub>SPO</sub>                | Static Phase Offset                            | Divider ratio = integer                 | -120   | 120   | ps         |  |

| tw                              | Output Clock Pulse Width                       | At 90% or 10% <sup>3</sup>              | 0.9    | _     | ns         |  |

| LOCK <sup>2, 5</sup>            | PLL Lock-in Time                               |                                         |        | 15    | ms         |  |

| UNLOCK                          | PLL Unlock Time                                |                                         |        | 50    | ns         |  |

|                                 | Innut Clask Davied Litter                      | f <sub>PFD</sub> ≥ 20 MHz               | —      | 1,000 | ps p-p     |  |

| <sup>t</sup> IPJIT <sup>6</sup> | Input Clock Period Jitter                      | f <sub>PFD</sub> < 20 MHz               | —      | 0.02  | UIPP       |  |

| thi                             | Input Clock High Time                          | 90% to 90%                              | 0.5    | —     | ns         |  |

| t <sub>LO</sub>                 | Input Clock Low Time                           | 10% to 10%                              | 0.5    | —     | ns         |  |

| STABLE <sup>5</sup>             | STANDBY High to PLL Stable                     |                                         | —      | 15    | ms         |  |

| RST                             | RST/RESETM Pulse Width                         |                                         | 1      | —     | ns         |  |

| RSTREC                          | RST Recovery Time                              |                                         | 1      | —     | ns         |  |

| RST_DIV                         | RESETC/D Pulse Width                           |                                         | 10     | —     | ns         |  |

| t <sub>RSTREC_DIV</sub>         | RESETC/D Recovery Time                         |                                         | 1      | _     | ns         |  |

| ROTATE-SETUP                    | PHASESTEP Setup Time                           |                                         | 10     |       | ns         |  |

| t <sub>ROTATE_WD</sub>          | PHASESTEP Pulse Width                          |                                         | 4      |       | VCO Cycles |  |

#### **Over Recommended Operating Conditions**

1. Period jitter sample is taken over 10,000 samples of the primary PLL output with a clean reference clock. Cycle-to-cycle jitter is taken over 1000 cycles. Phase jitter is taken over 2000 cycles. All values per JESD65B.

2. Output clock is valid after t<sub>LOCK</sub> for PLL reset and dynamic delay adjustment.

3. Using LVDS output buffers.

4. CLKOS as compared to CLKOP output for one phase step at the maximum VCO frequency. See TN1282, MachXO3 sysCLOCK PLL Design and Usage Guide for more details.

5. At minimum  $\rm f_{PFD}$  As the  $\rm f_{PFD}$  increases the time will decrease to approximately 60% the value listed.

6. Maximum allowed jitter on an input clock. PLL unlock may occur if the input jitter exceeds this specification. Jitter on the input clock may be transferred to the output clocks, resulting in jitter measurements outside the output specifications listed in this table.

7. Edge Duty Trim Accuracy is a percentage of the setting value. Settings available are 70 ps, 140 ps, and 280 ps in addition to the default value of none.

8. Jitter values measured with the internal oscillator operating. The jitter values will increase with loading of the PLD fabric and in the presence of SSO noise.

# sysCONFIG Port Timing Specifications

| Symbol               | Parameter              |                                                         | Min. | Max. | Units |

|----------------------|------------------------|---------------------------------------------------------|------|------|-------|

| All Configuration Mo | odes                   |                                                         |      |      |       |

| t <sub>PRGM</sub>    | PROGRAMN low pul       | se accept                                               | 55   | —    | ns    |

| t <sub>PRGMJ</sub>   | PROGRAMN low pul       | se rejection                                            | —    | 25   | ns    |

| t <sub>INITL</sub>   | INITN low time         | INITN low time LCMXO3L/LF-640/<br>LCMXO3L/LF-1300       |      | 55   | us    |

|                      |                        | LCMXO3L/LF-1300<br>256-Ball Package/<br>LCMXO3L/LF-2100 | _    | 70   | us    |

|                      |                        | LCMXO3L/LF-2100<br>324-Ball Package/<br>LCMXO3-4300     | _    | 105  | us    |

|                      |                        | LCMXO3L/LF-4300<br>400-Ball Package/<br>LCMXO3-6900     | _    | 130  | us    |

|                      |                        | LCMXO3L/LF-9400C                                        | _    | 175  | us    |

| t <sub>DPPINIT</sub> | PROGRAMN low to        | PROGRAMN low to INITN low                               |      |      | ns    |

| t <sub>DPPDONE</sub> | PROGRAMN low to I      | DONE low                                                | _    | 150  | ns    |

| t <sub>IODISS</sub>  | PROGRAMN low to        | I/O disable                                             | —    | 120  | ns    |

| Slave SPI            | ·                      |                                                         |      |      |       |

| f <sub>MAX</sub>     | CCLK clock frequence   | CCLK clock frequency                                    |      | 66   | MHz   |

| t <sub>CCLKH</sub>   | CCLK clock pulse wi    | dth high                                                | 7.5  | —    | ns    |

| t <sub>CCLKL</sub>   | CCLK clock pulse wi    | dth low                                                 | 7.5  | —    | ns    |

| t <sub>STSU</sub>    | CCLK setup time        |                                                         | 2    | —    | ns    |

| t <sub>STH</sub>     | CCLK hold time         |                                                         | 0    | —    | ns    |

| t <sub>STCO</sub>    | CCLK falling edge to   | valid output                                            | —    | 10   | ns    |

| t <sub>STOZ</sub>    | CCLK falling edge to   | valid disable                                           | _    | 10   | ns    |

| t <sub>STOV</sub>    | CCLK falling edge to   | valid enable                                            | _    | 10   | ns    |

| t <sub>SCS</sub>     | Chip select high time  | )                                                       | 25   | —    | ns    |

| t <sub>SCSS</sub>    | Chip select setup tim  | e                                                       | 3    | —    | ns    |

| t <sub>SCSH</sub>    | Chip select hold time  | )                                                       | 3    | —    | ns    |

| Master SPI           |                        |                                                         |      |      |       |

| f <sub>MAX</sub>     | MCLK clock frequence   | су                                                      |      | 133  | MHz   |

| t <sub>MCLKH</sub>   | MCLK clock pulse wi    | MCLK clock pulse width high                             |      | —    | ns    |

| t <sub>MCLKL</sub>   | MCLK clock pulse wi    | MCLK clock pulse width low                              |      | —    | ns    |

| t <sub>STSU</sub>    | MCLK setup time        |                                                         | 5    | —    | ns    |

| t <sub>STH</sub>     | MCLK hold time         |                                                         | 1    | —    | ns    |

| t <sub>CSSPI</sub>   | INITN high to chip se  | elect low                                               | 100  | 200  | ns    |

| t <sub>MCLK</sub>    | INITN high to first MO | CLK edge                                                | 0.75 | 1    | us    |

# Signal Descriptions (Cont.)

| Signal Name            | I/O       | Descriptions                                                                                                                                                 |

|------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configuration (Dual fu | inction p | ins used during sysCONFIG)                                                                                                                                   |

| PROGRAMN               | I         | Initiates configuration sequence when asserted low. This pin always has an active pull-up.                                                                   |

| INITN                  | I/O       | Open Drain pin. Indicates the FPGA is ready to be configured. During configuration, a pull-up is enabled.                                                    |

| DONE                   | I/O       | Open Drain pin. Indicates that the configuration sequence is complete, and the start-up sequence is in progress.                                             |

| MCLK/CCLK              | I/O       | Input Configuration Clock for configuring an FPGA in Slave SPI mode. Output Configuration Clock for configuring an FPGA in SPI and SPIm configuration modes. |

| SN                     | I         | Slave SPI active low chip select input.                                                                                                                      |

| CSSPIN                 | I/O       | Master SPI active low chip select output.                                                                                                                    |

| SI/SPISI               | I/O       | Slave SPI serial data input and master SPI serial data output.                                                                                               |

| SO/SPISO               | I/O       | Slave SPI serial data output and master SPI serial data input.                                                                                               |

| SCL                    | I/O       | Slave I <sup>2</sup> C clock input and master I <sup>2</sup> C clock output.                                                                                 |

| SDA                    | I/O       | Slave I <sup>2</sup> C data input and master I <sup>2</sup> C data output.                                                                                   |

|                                                        | MachXO3L/LF-9400C |          |          |          |  |  |  |

|--------------------------------------------------------|-------------------|----------|----------|----------|--|--|--|

|                                                        | CSFBGA256         | CABGA256 | CABGA400 | CABGA484 |  |  |  |

| General Purpose IO per Bank                            |                   | •        |          | •        |  |  |  |

| Bank 0                                                 | 50                | 50       | 83       | 95       |  |  |  |

| Bank 1                                                 | 52                | 52       | 84       | 96       |  |  |  |

| Bank 2                                                 | 52                | 52       | 84       | 96       |  |  |  |

| Bank 3                                                 | 16                | 16       | 28       | 36       |  |  |  |

| Bank 4                                                 | 16                | 16       | 24       | 24       |  |  |  |

| Bank 5                                                 | 20                | 20       | 32       | 36       |  |  |  |

| Total General Purpose Single Ended IO                  | 206               | 206      | 335      | 383      |  |  |  |

| Differential IO per Bank                               |                   | •        |          | •        |  |  |  |

| Bank 0                                                 | 25                | 25       | 42       | 48       |  |  |  |

| Bank 1                                                 | 26                | 26       | 42       | 48       |  |  |  |

| Bank 2                                                 | 26                | 26       | 42       | 48       |  |  |  |

| Bank 3                                                 | 8                 | 8        | 14       | 18       |  |  |  |

| Bank 4                                                 | 8                 | 8        | 12       | 12       |  |  |  |

| Bank 5                                                 | 10                | 10       | 16       | 18       |  |  |  |

| Total General Purpose Differential IO                  | 103               | 103      | 168      | 192      |  |  |  |

| Dual Function IO                                       | 37                | 37       | 37       | 45       |  |  |  |

| Number 7:1 or 8:1 Gearboxes                            | •                 |          |          | •        |  |  |  |

| Number of 7:1 or 8:1 Output Gearbox Available (Bank 0) | 20                | 20       | 22       | 24       |  |  |  |

| Number of 7:1 or 8:1 Input Gearbox Available (Bank 2)  | 20                | 20       | 22       | 24       |  |  |  |

| High-speed Differential Outputs                        | •                 |          |          | •        |  |  |  |

| Bank 0                                                 | 20                | 20       | 21       | 24       |  |  |  |

| VCCIO Pins                                             | •                 |          |          | •        |  |  |  |

| Bank 0                                                 | 4                 | 4        | 5        | 9        |  |  |  |

| Bank 1                                                 | 3                 | 4        | 5        | 9        |  |  |  |

| Bank 2                                                 | 4                 | 4        | 5        | 9        |  |  |  |

| Bank 3                                                 | 2                 | 1        | 2        | 3        |  |  |  |

| Bank 4                                                 | 2                 | 2        | 2        | 3        |  |  |  |

| Bank 5                                                 | 2                 | 1        | 2        | 3        |  |  |  |

| VCC                                                    | 8                 | 8        | 10       | 12       |  |  |  |