# E · ) ( Fatt ce Semiconductor Corporation - <u>LCMXO3LF-6900C-5BG400I Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                            |

|--------------------------------|-----------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 858                                                                               |

| Number of Logic Elements/Cells | 6864                                                                              |

| Total RAM Bits                 | 245760                                                                            |

| Number of I/O                  | 335                                                                               |

| Number of Gates                | -                                                                                 |

| Voltage - Supply               | 2.375V ~ 3.465V                                                                   |

| Mounting Type                  | Surface Mount                                                                     |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                                |

| Package / Case                 | 400-LFBGA                                                                         |

| Supplier Device Package        | 400-CABGA (17x17)                                                                 |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lcmxo3lf-6900c-5bg400i |

|                                |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table 1-1. MachXO3L/LF Family Selection Guide

| Features                                                |                                  | MachXO3L-640/<br>MachXO3LF-640 | MachXO3L-1300/<br>MachXO3LF-1300 | MachXO3L-2100/<br>MachXO3LF-2100 | MachXO3L-4300/<br>MachXO3LF-4300 | MachXO3L-6900/<br>MachXO3LF-6900 | MachXO3L-9400/<br>MachXO3LF-9400 |

|---------------------------------------------------------|----------------------------------|--------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|

| LUTs                                                    |                                  | 640                            | 1300                             | 2100                             | 4300                             | 6900                             | 9400                             |

| Distributed R                                           | AM (kbits)                       | 5                              | 10                               | 16                               | 34                               | 54                               | 73                               |

| EBR SRAM (                                              | kbits)                           | 64                             | 64                               | 74                               | 92                               | 240                              | 432                              |

| Number of PL                                            | Ls                               | 1                              | 1                                | 1                                | 2                                | 2                                | 2                                |

| Hardened                                                | I <sup>2</sup> C                 | 2                              | 2                                | 2                                | 2                                | 2                                | 2                                |

| Functions:                                              | SPI                              | 1                              | 1                                | 1                                | 1                                | 1                                | 1                                |

|                                                         | Timer/Counter                    | 1                              | 1                                | 1                                | 1                                | 1                                | 1                                |

|                                                         | Oscillator                       | 1                              | 1                                | 1                                | 1                                | 1                                | 1                                |

| MIPI D-PHY                                              | Support                          | Yes                            | Yes                              | Yes                              | Yes                              | Yes                              | Yes                              |

| Multi Time Pr<br>NVCM                                   | ogrammable                       | MachXO3L-640                   | MachXO3L-1300                    | MachXO3L-2100                    | MachXO3L-4300                    | MachXO3L-6900                    | MachXO3L-9400                    |

| Programmable Flash                                      |                                  | MachXO3LF-640                  | MachXO3LF-1300                   | MachXO3LF-2100                   | MachXO3LF-4300                   | MachXO3LF-6900                   | MachXO3LF-9400                   |

| Packages                                                |                                  |                                |                                  | ю                                |                                  |                                  |                                  |

| 36-ball WLCSP <sup>1</sup><br>(2.5 mm x 2.5 mm, 0.4 mm) |                                  |                                | 28                               |                                  |                                  |                                  |                                  |

| 49-ball WLCS<br>(3.2 mm x 3.2                           | SP <sup>1</sup><br>2 mm, 0.4 mm) |                                |                                  | 38                               |                                  |                                  |                                  |

| 81-ball WLCS<br>(3.8 mm x 3.8                           | SP <sup>1</sup><br>3 mm, 0.4 mm) |                                |                                  |                                  | 63                               |                                  |                                  |

| 121-ball csfBGA <sup>1</sup><br>(6 mm x 6 mm, 0.5 mm)   |                                  | 100                            | 100                              | 100                              | 100                              |                                  |                                  |

| 256-ball csfB<br>(9 mm x 9 mr                           |                                  | 2                              | 206                              | 206                              | 206                              | 206                              | 206                              |

| 324-ball csfB<br>(10 mm x 10                            |                                  |                                |                                  | 268                              | 268                              | 281                              |                                  |

| 256-ball caB0<br>(14 mm x 14                            |                                  |                                | 206                              | 206                              | 206                              | 206                              | 206                              |

| 324-ball caB0<br>(15 mm x 15                            |                                  |                                |                                  | 279                              | 279                              | 279                              |                                  |

| 400-ball caB0<br>(17 mm x 17                            |                                  |                                |                                  |                                  | 335                              | 335                              | 335                              |

| 484-ball caB0<br>(19 mm x 19                            |                                  |                                |                                  |                                  |                                  |                                  | 384                              |

1. Package is only available for E=1.2 V devices.

2. Package is only available for C=2.5 V/3.3 V devices.

## Introduction

MachXO3<sup>™</sup> device family is an Ultra-Low Density family that supports the most advanced programmable bridging and IO expansion. It has the breakthrough IO density and the lowest cost per IO. The device IO features have the integrated support for latest industry standard IO.

The MachXO3L/LF family of low power, instant-on, non-volatile PLDs has five devices with densities ranging from 640 to 9400 Look-Up Tables (LUTs). In addition to LUT-based, low-cost programmable logic these devices feature Embedded Block RAM (EBR), Distributed RAM, Phase Locked Loops (PLLs), pre-engineered source synchronous I/O support, advanced configuration support including dual-boot capability and hardened versions of commonly used functions such as SPI controller, I<sup>2</sup>C controller and timer/counter. MachXO3LF devices also support User Flash Memory (UFM). These features allow these devices to be used in low cost, high volume consumer and system applications.

The MachXO3L/LF devices are designed on a 65nm non-volatile low power process. The device architecture has several features such as programmable low swing differential I/Os and the ability to turn off I/O banks, on-chip PLLs

#### Table 2-4. PLL Signal Descriptions (Continued)

| Port Name     | I/O | Description                                                                                            |

|---------------|-----|--------------------------------------------------------------------------------------------------------|

| CLKOP         | 0   | Primary PLL output clock (with phase shift adjustment)                                                 |

| CLKOS         | 0   | Secondary PLL output clock (with phase shift adjust)                                                   |

| CLKOS2        | 0   | Secondary PLL output clock2 (with phase shift adjust)                                                  |

| CLKOS3        | 0   | Secondary PLL output clock3 (with phase shift adjust)                                                  |

| LOCK          | 0   | PLL LOCK, asynchronous signal. Active high indicates PLL is locked to input and feed-<br>back signals. |

| DPHSRC        | 0   | Dynamic Phase source – ports or WISHBONE is active                                                     |

| STDBY         | I   | Standby signal to power down the PLL                                                                   |

| RST           | I   | PLL reset without resetting the M-divider. Active high reset.                                          |

| RESETM        | I   | PLL reset - includes resetting the M-divider. Active high reset.                                       |

| RESETC        | I   | Reset for CLKOS2 output divider only. Active high reset.                                               |

| RESETD        | I   | Reset for CLKOS3 output divider only. Active high reset.                                               |

| ENCLKOP       | I   | Enable PLL output CLKOP                                                                                |

| ENCLKOS       | I   | Enable PLL output CLKOS when port is active                                                            |

| ENCLKOS2      | I   | Enable PLL output CLKOS2 when port is active                                                           |

| ENCLKOS3      | I   | Enable PLL output CLKOS3 when port is active                                                           |

| PLLCLK        | I   | PLL data bus clock input signal                                                                        |

| PLLRST        | I   | PLL data bus reset. This resets only the data bus not any register values.                             |

| PLLSTB        | I   | PLL data bus strobe signal                                                                             |

| PLLWE         | I   | PLL data bus write enable signal                                                                       |

| PLLADDR [4:0] | I   | PLL data bus address                                                                                   |

| PLLDATI [7:0] | ļ   | PLL data bus data input                                                                                |

| PLLDATO [7:0] | 0   | PLL data bus data output                                                                               |

| PLLACK        | 0   | PLL data bus acknowledge signal                                                                        |

## sysMEM Embedded Block RAM Memory

The MachXO3L/LF devices contain sysMEM Embedded Block RAMs (EBRs). The EBR consists of a 9-Kbit RAM, with dedicated input and output registers. This memory can be used for a wide variety of purposes including data buffering, PROM for the soft processor and FIFO.

#### sysMEM Memory Block

The sysMEM block can implement single port, dual port, pseudo dual port, or FIFO memories. Each block can be used in a variety of depths and widths as shown in Table 2-5.

state. The RPRST signal is used to reset the read pointer. The purpose of this reset is to retransmit the data that is in the FIFO. In these applications it is important to keep careful track of when a packet is written into or read from the FIFO.

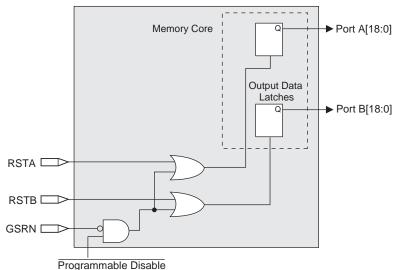

#### Memory Core Reset

The memory core contains data output latches for ports A and B. These are simple latches that can be reset synchronously or asynchronously. RSTA and RSTB are local signals, which reset the output latches associated with port A and port B respectively. The Global Reset (GSRN) signal resets both ports. The output data latches and associated resets for both ports are as shown in Figure 2-9.

#### Figure 2-9. Memory Core Reset

For further information on the sysMEM EBR block, please refer to TN1290, Memory Usage Guide for MachXO3 Devices.

#### EBR Asynchronous Reset

EBR asynchronous reset or GSR (if used) can only be applied if all clock enables are low for a clock cycle before the reset is applied and released a clock cycle after the reset is released, as shown in Figure 2-10. The GSR input to the EBR is always asynchronous.

#### Figure 2-10. EBR Asynchronous Reset (Including GSR) Timing Diagram

| Reset |  |

|-------|--|

| Clock |  |

| Clock |  |

If all clock enables remain enabled, the EBR asynchronous reset or GSR may only be applied and released after the EBR read and write clock inputs are in a steady state condition for a minimum of 1/f<sub>MAX</sub> (EBR clock). The reset release must adhere to the EBR synchronous reset setup time before the next active read or write clock edge.

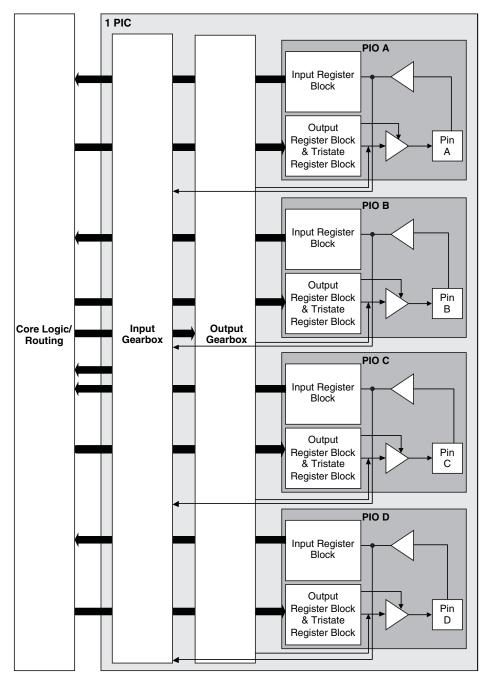

Figure 2-11. Group of Four Programmable I/O Cells

#### Figure 2-13. Input Gearbox

More information on the input gearbox is available in TN1281, Implementing High-Speed Interfaces with MachXO3 Devices.

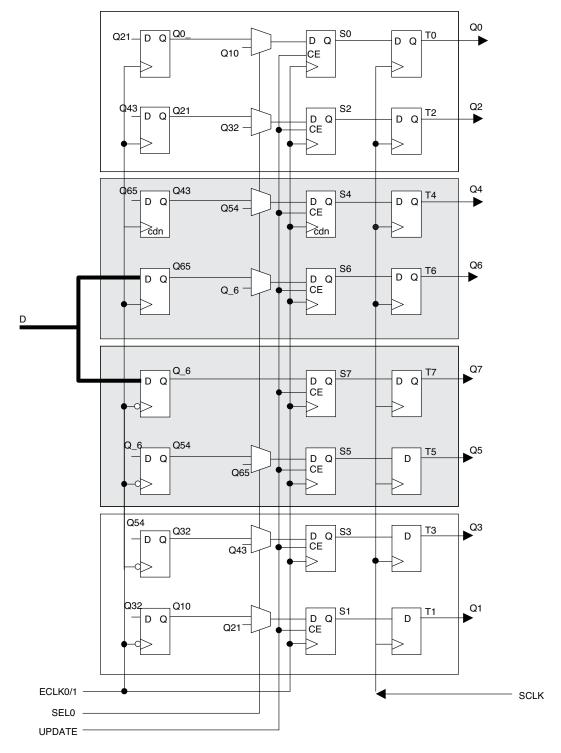

## Output Gearbox

Each PIC on the top edge has a built-in 8:1 output gearbox. Each of these output gearboxes may be programmed as a 7:1 serializer or as one ODDRX4 (8:1) gearbox or as two ODDRX2 (4:1) gearboxes. Table 2-10 shows the gearbox signals.

#### Table 2-10. Output Gearbox Signal List

| Name                       | I/O Type | Description                     |

|----------------------------|----------|---------------------------------|

| Q                          | Output   | High-speed data output          |

| D[7:0]                     | Input    | Low-speed data from device core |

| Video TX(7:1): D[6:0]      |          |                                 |

| GDDRX4(8:1): D[7:0]        |          |                                 |

| GDDRX2(4:1)(IOL-A): D[3:0] |          |                                 |

| GDDRX2(4:1)(IOL-C): D[7:4] |          |                                 |

| SCLK                       | Input    | Slow-speed system clock         |

| ECLK [1:0]                 | Input    | High-speed edge clock           |

| RST                        | Input    | Reset                           |

The gearboxes have three stage pipeline registers. The first stage registers sample the low-speed input data on the low-speed system clock. The second stage registers transfer data from the low-speed clock registers to the high-speed clock registers. The third stage pipeline registers controlled by high-speed edge clock shift and mux the high-speed data out to the sysIO buffer. Figure 2-14 shows the output gearbox block diagram.

## **Embedded Hardened IP Functions**

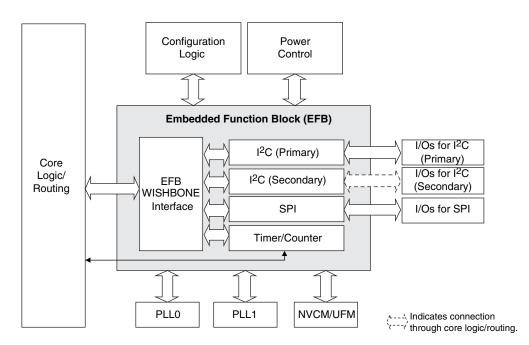

All MachXO3L/LF devices provide embedded hardened functions such as SPI, I<sup>2</sup>C and Timer/Counter. MachXO3LF devices also provide User Flash Memory (UFM). These embedded blocks interface through the WISHBONE interface with routing as shown in Figure 2-17.

#### Figure 2-17. Embedded Function Block Interface

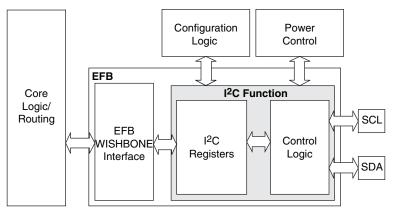

### Hardened I<sup>2</sup>C IP Core

Every MachXO3L/LF device contains two  $I^2C$  IP cores. These are the primary and secondary  $I^2C$  IP cores. Either of the two cores can be configured either as an  $I^2C$  master or as an  $I^2C$  slave. The only difference between the two IP cores is that the primary core has pre-assigned I/O pins whereas users can assign I/O pins for the secondary core.

When the IP core is configured as a master it will be able to control other devices on the  $I^2C$  bus through the interface. When the core is configured as the slave, the device will be able to provide I/O expansion to an  $I^2C$  Master. The  $I^2C$  cores support the following functionality:

- Master and Slave operation

- 7-bit and 10-bit addressing

- Multi-master arbitration support

- Up to 400 kHz data transfer speed

- General call support

- Interface to custom logic through 8-bit WISHBONE interface

#### Figure 2-18. PC Core Block Diagram

Table 2-14 describes the signals interfacing with the I<sup>2</sup>C cores.

Table 2-14. PC Core Signal Description

| Signal Name | I/O            | Description                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| i2c_scl     | Bi-directional | Bi-directional clock line of the I <sup>2</sup> C core. The signal is an output if the I <sup>2</sup> C core is in master mode. The signal is an input if the I <sup>2</sup> C core is in slave mode. MUST be routed directly to the pre-assigned I/O of the chip. Refer to the Pinout Information section of this document for detailed pad and pin locations of I <sup>2</sup> C ports in each MachXO3L/LF device.                |

| i2c_sda     | Bi-directional | Bi-directional data line of the I <sup>2</sup> C core. The signal is an output when data is transmitted from the I <sup>2</sup> C core. The signal is an input when data is received into the I <sup>2</sup> C core. MUST be routed directly to the pre-assigned I/O of the chip. Refer to the Pinout Information section of this document for detailed pad and pin locations of I <sup>2</sup> C ports in each MachXO3L/LF device. |

| i2c_irqo    | Output         | Interrupt request output signal of the I <sup>2</sup> C core. The intended usage of this signal is for it to be connected to the WISHBONE master controller (i.e. a microcontroller or state machine) and request an interrupt when a specific condition is met. These conditions are described with the I <sup>2</sup> C register definitions.                                                                                     |

| cfg_wake    | Output         | Wake-up signal – To be connected only to the power module of the MachXO3L/LF device. The signal is enabled only if the "Wakeup Enable" feature has been set within the EFB GUI, $I^2C$ Tab.                                                                                                                                                                                                                                         |

| cfg_stdby   | Output         | Stand-by signal – To be connected only to the power module of the MachXO3L/LF device. The signal is enabled only if the "Wakeup Enable" feature has been set within the EFB GUI, $I^2C$ Tab.                                                                                                                                                                                                                                        |

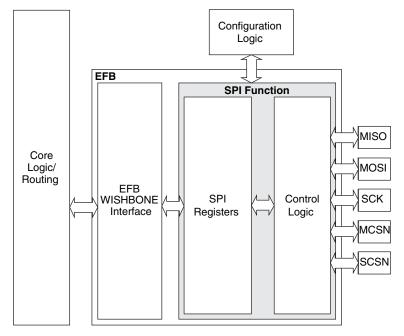

### Hardened SPI IP Core

Every MachXO3L/LF device has a hard SPI IP core that can be configured as a SPI master or slave. When the IP core is configured as a master it will be able to control other SPI enabled chips connected to the SPI bus. When the core is configured as the slave, the device will be able to interface to an external SPI master. The SPI IP core on MachXO3L/LF devices supports the following functions:

- Configurable Master and Slave modes

- Full-Duplex data transfer

- Mode fault error flag with CPU interrupt capability

- Double-buffered data register

- Serial clock with programmable polarity and phase

- LSB First or MSB First Data Transfer

- Interface to custom logic through 8-bit WISHBONE interface

There are some limitations on the use of the hardened user SPI. These are defined in the following technical notes:

- TN1087, Minimizing System Interruption During Configuration Using TransFR Technology (Appendix B)

- TN1293, Using Hardened Control Functions in MachXO3 Devices

#### Figure 2-19. SPI Core Block Diagram

Table 2-15 describes the signals interfacing with the SPI cores.

Table 2-15. SPI Core Signal Description

| Signal Name | I/O | Master/Slave | Description                                                                                                                                                                               |  |  |  |

|-------------|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| spi_csn[0]  | 0   | Master       | SPI master chip-select output                                                                                                                                                             |  |  |  |

| spi_csn[17] | 0   | Master       | Additional SPI chip-select outputs (total up to eight slaves)                                                                                                                             |  |  |  |

| spi_scsn    | I   | Slave        | SPI slave chip-select input                                                                                                                                                               |  |  |  |

| spi_irq     | 0   | Master/Slave | Interrupt request                                                                                                                                                                         |  |  |  |

| spi_clk     | I/O | Master/Slave | SPI clock. Output in master mode. Input in slave mode.                                                                                                                                    |  |  |  |

| spi_miso    | I/O | Master/Slave | SPI data. Input in master mode. Output in slave mode.                                                                                                                                     |  |  |  |

| spi_mosi    | I/O | Master/Slave | SPI data. Output in master mode. Input in slave mode.                                                                                                                                     |  |  |  |

| sn          | I   | Slave        | Configuration Slave Chip Select (active low), dedicated for selecting the Con-<br>figuration Logic.                                                                                       |  |  |  |

| cfg_stdby   | 0   | Master/Slave | Stand-by signal – To be connected only to the power module of the MachXO3L/LF device. The signal is enabled only if the "Wakeup Enable" feature has been set within the EFB GUI, SPI Tab. |  |  |  |

| cfg_wake    | О   | Master/Slave | Wake-up signal – To be connected only to the power module of the MachXO3L/LF device. The signal is enabled only if the "Wakeup Enable" feature has been set within the EFB GUI, SPI Tab.  |  |  |  |

For more details on these embedded functions, please refer to TN1293, Using Hardened Control Functions in MachXO3 Devices.

## **User Flash Memory (UFM)**

MachXO3LF devices provide a User Flash Memory block, which can be used for a variety of applications including storing a portion of the configuration image, initializing EBRs, to store PROM data or, as a general purpose user Flash memory. The UFM block connects to the device core through the embedded function block WISHBONE interface. Users can also access the UFM block through the JTAG, I2C and SPI interfaces of the device. The UFM block offers the following features:

- Non-volatile storage up to 256 kbits

- 100K write cycles

- Write access is performed page-wise; each page has 128 bits (16 bytes)

- Auto-increment addressing

- WISHBONE interface

For more information on the UFM, please refer to TN1293, Using Hardened Control Functions in MachXO3 Devices.

## **Standby Mode and Power Saving Options**

MachXO3L/LF devices are available in two options, the C and E devices. The C devices have a built-in voltage regulator to allow for 2.5 V V<sub>CC</sub> and 3.3 V V<sub>CC</sub> while the E devices operate at 1.2 V V<sub>CC</sub>.

MachXO3L/LF devices have been designed with features that allow users to meet the static and dynamic power requirements of their applications by controlling various device subsystems such as the bandgap, power-on-reset circuitry, I/O bank controllers, power guard, on-chip oscillator, PLLs, etc. In order to maximize power savings, MachXO3L/LF devices support a low power Stand-by mode.

In the stand-by mode the MachXO3L/LF devices are powered on and configured. Internal logic, I/Os and memories are switched on and remain operational, as the user logic waits for an external input. The device enters this mode when the standby input of the standby controller is toggled or when an appropriate I<sup>2</sup>C or JTAG instruction is issued by an external master. Various subsystems in the device such as the band gap, power-on-reset circuitry etc can be configured such that they are automatically turned "off" or go into a low power consumption state to save power when the device enters this state. Note that the MachXO3L/LF devices are powered on when in standby mode and all power supplies should remain in the Recommended Operating Conditions.

## TraceID

Each MachXO3L/LF device contains a unique (per device), TraceID that can be used for tracking purposes or for IP security applications. The TraceID is 64 bits long. Eight out of 64 bits are user-programmable, the remaining 56 bits are factory-programmed. The TraceID is accessible through the EFB WISHBONE interface and can also be accessed through the SPI, I<sup>2</sup>C, or JTAG interfaces.

## **Density Shifting**

The MachXO3L/LF family has been designed to enable density migration within the same package. Furthermore, the architecture ensures a high success rate when performing design migration from lower density devices to higher density devices. In many cases, it is also possible to shift a lower utilization design targeted for a high-density device to a lower density device. However, the exact details of the final resource utilization will impact the likely success in each case. When migrating from lower to higher density or higher to lower density, ensure to review all the power supplies and NC pins of the chosen devices. For more details refer to the MachXO3 migration files.

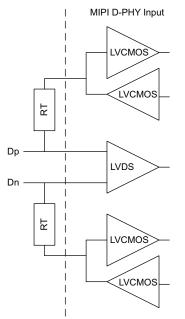

### MIPI D-PHY Emulation

MachXO3L/LF devices can support MIPI D-PHY unidirectional HS (High Speed) and bidirectional LP (Low Power) inputs and outputs via emulation. In conjunction with external resistors High Speed IOs use the LVDS25E buffer and Low Power IOs use the LVCMOS buffers. The scheme shown in Figure 3-4 is one possible solution for MIPI D-PHY Receiver implementation. The scheme shown in Figure 3-5 is one possible solution for MIPI D-PHY Transmitter implementation.

#### Figure 3-4. MIPI D-PHY Input Using External Resistors

Table 3-4. MIPI DC Conditions<sup>1</sup>

|                | Description                                          | Min. | Тур. | Max. | Units |

|----------------|------------------------------------------------------|------|------|------|-------|

| Receiver       |                                                      | 1    | 1    | 1    |       |

| External Termi | nation                                               |      |      |      |       |

| RT             | 1% external resistor with VCCIO=2.5 V                |      | 50   |      | Ohms  |

|                | 1% external resistor with VCCIO=3.3 V                |      | 50   | _    | Ohms  |

| High Speed     |                                                      |      |      |      |       |

| VCCIO          | VCCIO of the Bank with LVDS Emulated input<br>buffer | _    | 2.5  | _    | V     |

|                | VCCIO of the Bank with LVDS Emulated input<br>buffer | —    | 3.3  | —    | V     |

| VCMRX          | Common-mode voltage HS receive mode                  | 150  | 200  | 250  | mV    |

| VIDTH          | Differential input high threshold                    |      |      | 100  | mV    |

| VIDTL          | Differential input low threshold                     | -100 |      | —    | mV    |

| VIHHS          | Single-ended input high voltage                      |      |      | 300  | mV    |

| VILHS          | Single-ended input low voltage                       | 100  |      | —    | mV    |

| ZID            | Differential input impedance                         | 80   | 100  | 120  | Ohms  |

## DC and Switching Characteristics MachXO3 Family Data Sheet

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                  |                  | -6    |      | -5    |      |       |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------|-------|------|-------|------|-------|--|

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Description                                                      | Device           | Min.  | Max. | Min.  | Max. | Units |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                  | MachXO3L/LF-1300 | 2.87  | _    | 3.18  | —    | ns    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                  | MachXO3L/LF-2100 | 2.87  |      | 3.18  | —    | ns    |  |

| t <sub>SU_DELPLL</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Clock to Data Setup - PIO Input Register with Data Input Delay   | MachXO3L/LF-4300 | 2.96  |      | 3.28  | —    | ns    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | With Data input Dolay                                            | MachXO3L/LF-6900 | 3.05  | _    | 3.35  | —    | ns    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                  | MachXO3L/LF-9400 | 3.06  |      | 3.37  | —    | ns    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                  | MachXO3L/LF-1300 | -0.83 |      | -0.83 | —    | ns    |  |

| Terris and the second s | Clock to Data Hold - PIO Input Register with<br>Input Data Delay | MachXO3L/LF-2100 | -0.83 |      | -0.83 | —    | ns    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                  | MachXO3L/LF-4300 | -0.87 |      | -0.87 | —    | ns    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | input Data Dotay                                                 | MachXO3L/LF-6900 | -0.91 | —    | -0.91 | —    | ns    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                  | MachXO3L/LF-9400 | -0.93 | —    | -0.93 | —    | ns    |  |

## sysCONFIG Port Timing Specifications

| Symbol               | Parameter              |                                                         | Min. | Max. | Units |

|----------------------|------------------------|---------------------------------------------------------|------|------|-------|

| All Configuration Mo | des                    |                                                         |      |      |       |

| t <sub>PRGM</sub>    | PROGRAMN low pul       | se accept                                               | 55   | —    | ns    |

| t <sub>PRGMJ</sub>   | PROGRAMN low pul       | PROGRAMN low pulse rejection                            |      | 25   | ns    |

| t <sub>INITL</sub>   | INITN low time         | LCMXO3L/LF-640/<br>LCMXO3L/LF-1300                      | —    | 55   | us    |

|                      |                        | LCMXO3L/LF-1300<br>256-Ball Package/<br>LCMXO3L/LF-2100 | _    | 70   | us    |

|                      |                        | LCMXO3L/LF-2100<br>324-Ball Package/<br>LCMXO3-4300     | _    | 105  | us    |

|                      |                        | LCMXO3L/LF-4300<br>400-Ball Package/<br>LCMXO3-6900     | _    | 130  | us    |

|                      |                        | LCMXO3L/LF-9400C                                        |      | 175  | us    |

| t <sub>DPPINIT</sub> | PROGRAMN low to        | NITN low                                                |      | 150  | ns    |

| t <sub>DPPDONE</sub> | PROGRAMN low to I      | DONE low                                                | _    | 150  | ns    |

| t <sub>IODISS</sub>  | PROGRAMN low to        | /O disable                                              | _    | 120  | ns    |

| Slave SPI            |                        |                                                         |      |      |       |

| f <sub>MAX</sub>     | CCLK clock frequence   | CCLK clock frequency                                    |      | 66   | MHz   |

| t <sub>CCLKH</sub>   | CCLK clock pulse wi    | dth high                                                | 7.5  | —    | ns    |

| t <sub>CCLKL</sub>   | CCLK clock pulse wi    | dth low                                                 | 7.5  | —    | ns    |

| t <sub>STSU</sub>    | CCLK setup time        |                                                         | 2    | —    | ns    |

| t <sub>STH</sub>     | CCLK hold time         |                                                         | 0    | —    | ns    |

| t <sub>STCO</sub>    | CCLK falling edge to   | valid output                                            | _    | 10   | ns    |

| t <sub>STOZ</sub>    | CCLK falling edge to   | valid disable                                           |      | 10   | ns    |

| t <sub>STOV</sub>    | CCLK falling edge to   | valid enable                                            |      | 10   | ns    |

| t <sub>SCS</sub>     | Chip select high time  | )                                                       | 25   | —    | ns    |

| t <sub>SCSS</sub>    | Chip select setup tim  | e                                                       | 3    | —    | ns    |

| t <sub>SCSH</sub>    | Chip select hold time  | 1                                                       | 3    | —    | ns    |

| Master SPI           |                        |                                                         |      |      |       |

| f <sub>MAX</sub>     | MCLK clock frequence   | су                                                      |      | 133  | MHz   |

| t <sub>MCLKH</sub>   | MCLK clock pulse wi    | dth high                                                | 3.75 | —    | ns    |

| t <sub>MCLKL</sub>   | MCLK clock pulse wi    | dth low                                                 | 3.75 | —    | ns    |

| t <sub>STSU</sub>    | MCLK setup time        |                                                         | 5    | —    | ns    |

| t <sub>STH</sub>     | MCLK hold time         |                                                         | 1    | —    | ns    |

| t <sub>CSSPI</sub>   | INITN high to chip se  | elect low                                               | 100  | 200  | ns    |

| t <sub>MCLK</sub>    | INITN high to first MO | CLK edge                                                | 0.75 | 1    | us    |

## I<sup>2</sup>C Port Timing Specifications<sup>1, 2</sup>

| Symbol           | Parameter                   | Min. | Max. | Units |

|------------------|-----------------------------|------|------|-------|

| f <sub>MAX</sub> | Maximum SCL clock frequency | _    | 400  | kHz   |

1. MachXO3L/LF supports the following modes:

• Standard-mode (Sm), with a bit rate up to 100 kbit/s (user and configuration mode)

• Fast-mode (Fm), with a bit rate up to 400 kbit/s (user and configuration mode)

2. Refer to the  $I^2C$  specification for timing requirements.

## SPI Port Timing Specifications<sup>1</sup>

| Symbol           | Parameter                   | Min. | Max. | Units |

|------------------|-----------------------------|------|------|-------|

| f <sub>MAX</sub> | Maximum SCK clock frequency | —    | 45   | MHz   |

1. Applies to user mode only. For configuration mode timing specifications, refer to sysCONFIG Port Timing Specifications table in this data sheet.

## **Switching Test Conditions**

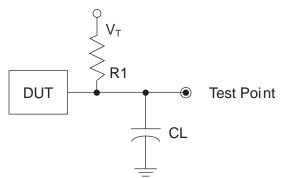

Figure 3-9 shows the output test load used for AC testing. The specific values for resistance, capacitance, voltage, and other test conditions are shown in Table 3-6.

#### Figure 3-9. Output Test Load, LVTTL and LVCMOS Standards

| Table 3-6. Test Fixture Required Components, | Non-Terminated Interfaces |

|----------------------------------------------|---------------------------|

|----------------------------------------------|---------------------------|

| Test Condition                                                                  | R1  | CL  | Timing Ref.               | VT              |

|---------------------------------------------------------------------------------|-----|-----|---------------------------|-----------------|

|                                                                                 | ø   | 0pF | LVTTL, LVCMOS 3.3 = 1.5 V | —               |

|                                                                                 |     |     | LVCMOS 2.5 = $V_{CCIO}/2$ | _               |

| LVTTL and LVCMOS settings (L -> H, H -> L)                                      |     |     | LVCMOS 1.8 = $V_{CCIO}/2$ | _               |

|                                                                                 |     |     | LVCMOS 1.5 = $V_{CCIO}/2$ |                 |

|                                                                                 |     |     | LVCMOS 1.2 = $V_{CCIO}/2$ | _               |

| LVTTL and LVCMOS 3.3 (Z -> H)                                                   |     | 0pF | 1.5                       | V <sub>OL</sub> |

| LVTTL and LVCMOS 3.3 (Z -> L)<br>Other LVCMOS (Z -> H)<br>Other LVCMOS (Z -> L) | 188 |     | 1.5                       | V <sub>OH</sub> |

|                                                                                 |     |     | V <sub>CCIO</sub> /2      | V <sub>OL</sub> |

|                                                                                 |     |     | V <sub>CCIO</sub> /2      | V <sub>OH</sub> |

| LVTTL + LVCMOS (H -> Z)                                                         | 1   |     | V <sub>OH</sub> - 0.15    | V <sub>OL</sub> |

| LVTTL + LVCMOS (L -> Z)                                                         |     |     | V <sub>OL</sub> - 0.15    | V <sub>OH</sub> |

Note: Output test conditions for all other interfaces are determined by the respective standards.

|                                                        | MachXO3L/LF-2100 |           |           |           |          |          |

|--------------------------------------------------------|------------------|-----------|-----------|-----------|----------|----------|

|                                                        | WLCSP49          | CSFBGA121 | CSFBGA256 | CSFBGA324 | CABGA256 | CABGA324 |

| General Purpose IO per Bank                            | 1                |           |           |           |          |          |

| Bank 0                                                 | 19               | 24        | 50        | 71        | 50       | 71       |

| Bank 1                                                 | 0                | 26        | 52        | 62        | 52       | 68       |

| Bank 2                                                 | 13               | 26        | 52        | 72        | 52       | 72       |

| Bank 3                                                 | 0                | 7         | 16        | 22        | 16       | 24       |

| Bank 4                                                 | 0                | 7         | 16        | 14        | 16       | 16       |

| Bank 5                                                 | 6                | 10        | 20        | 27        | 20       | 28       |

| Total General Purpose Single Ended IO                  | 38               | 100       | 206       | 268       | 206      | 279      |

| Differential IO per Bank                               | 1                |           |           |           |          |          |

| Bank 0                                                 | 10               | 12        | 25        | 36        | 25       | 36       |

| Bank 1                                                 | 0                | 13        | 26        | 30        | 26       | 34       |

| Bank 2                                                 | 6                | 13        | 26        | 36        | 26       | 36       |

| Bank 3                                                 | 0                | 3         | 8         | 10        | 8        | 12       |

| Bank 4                                                 | 0                | 3         | 8         | 6         | 8        | 8        |

| Bank 5                                                 | 3                | 5         | 10        | 13        | 10       | 14       |

| Total General Purpose Differential IO                  | 19               | 49        | 103       | 131       | 103      | 140      |

| Dual Function IO                                       | 25               | 33        | 33        | 37        | 33       | 37       |

| Number 7:1 or 8:1 Gearboxes                            | •                |           |           | •         | •        | •        |

| Number of 7:1 or 8:1 Output Gearbox Available (Bank 0) | 5                | 7         | 14        | 18        | 14       | 18       |

| Number of 7:1 or 8:1 Input Gearbox Available (Bank 2)  | 6                | 13        | 14        | 18        | 14       | 18       |

| High-speed Differential Outputs                        | •                |           |           | •         | •        | •        |

| Bank 0                                                 | 5                | 7         | 14        | 18        | 14       | 18       |

| VCCIO Pins                                             | 1                |           |           |           |          |          |

| Bank 0                                                 | 2                | 1         | 4         | 4         | 4        | 4        |

| Bank 1                                                 | 0                | 1         | 3         | 4         | 4        | 4        |

| Bank 2                                                 | 1                | 1         | 4         | 4         | 4        | 4        |

| Bank 3                                                 | 0                | 1         | 2         | 2         | 1        | 2        |

| Bank 4                                                 | 0                | 1         | 2         | 2         | 2        | 2        |

| Bank 5                                                 | 1                | 1         | 2         | 2         | 1        | 2        |

| VCC                                                    | 2                | 4         | 8         | 8         | 8        | 10       |

| GND                                                    | 4                | 10        | 24        | 16        | 24       | 16       |

| NC                                                     | 0                | 0         | 0         | 13        | 1        | 0        |

| Reserved for Configuration                             | 1                | 1         | 1         | 1         | 1        | 1        |

| Total Count of Bonded Pins                             | 49               | 121       | 256       | 324       | 256      | 324      |

| Part Number               | LUTs | Supply Voltage | Speed | Package             | Leads | Temp. |

|---------------------------|------|----------------|-------|---------------------|-------|-------|

| LCMXO3L-2100E-6MG324I     | 2100 | 1.2 V          | 6     | Halogen-Free csfBGA | 324   | IND   |

| LCMXO3L-2100C-5BG256C     | 2100 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 256   | СОМ   |

| LCMXO3L-2100C-6BG256C     | 2100 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 256   | COM   |

| LCMXO3L-2100C-5BG256I     | 2100 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 256   | IND   |

| LCMXO3L-2100C-6BG256I     | 2100 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 256   | IND   |

| LCMXO3L-2100C-5BG324C     | 2100 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 324   | COM   |

| LCMXO3L-2100C-6BG324C     | 2100 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 324   | СОМ   |

| LCMXO3L-2100C-5BG324I     | 2100 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 324   | IND   |

| LCMXO3L-2100C-6BG324I     | 2100 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 324   | IND   |

|                           |      |                |       | ·                   |       |       |

| Part Number               | LUTs | Supply Voltage | Speed | Package             | Leads | Temp. |

| LCMXO3L-4300E-5UWG81CTR   | 4300 | 1.2 V          | 5     | Halogen-Free WLCSP  | 81    | COM   |

| LCMXO3L-4300E-5UWG81CTR50 | 4300 | 1.2 V          | 5     | Halogen-Free WLCSP  | 81    | COM   |

| LCMXO3L-4300E-5UWG81CTR1K | 4300 | 1.2 V          | 5     | Halogen-Free WLCSP  | 81    | COM   |

| LCMXO3L-4300E-5UWG81ITR   | 4300 | 1.2 V          | 5     | Halogen-Free WLCSP  | 81    | IND   |

| LCMXO3L-4300E-5UWG81ITR50 | 4300 | 1.2 V          | 5     | Halogen-Free WLCSP  | 81    | IND   |

| LCMXO3L-4300E-5UWG81ITR1K | 4300 | 1.2 V          | 5     | Halogen-Free WLCSP  | 81    | IND   |

| LCMXO3L-4300E-5MG121C     | 4300 | 1.2 V          | 5     | Halogen-Free csfBGA | 121   | COM   |

| LCMXO3L-4300E-6MG121C     | 4300 | 1.2 V          | 6     | Halogen-Free csfBGA | 121   | COM   |

| LCMXO3L-4300E-5MG121I     | 4300 | 1.2 V          | 5     | Halogen-Free csfBGA | 121   | IND   |

| LCMXO3L-4300E-6MG121I     | 4300 | 1.2 V          | 6     | Halogen-Free csfBGA | 121   | IND   |

| LCMXO3L-4300E-5MG256C     | 4300 | 1.2 V          | 5     | Halogen-Free csfBGA | 256   | COM   |

| LCMXO3L-4300E-6MG256C     | 4300 | 1.2 V          | 6     | Halogen-Free csfBGA | 256   | COM   |

| LCMXO3L-4300E-5MG256I     | 4300 | 1.2 V          | 5     | Halogen-Free csfBGA | 256   | IND   |

| LCMXO3L-4300E-6MG256I     | 4300 | 1.2 V          | 6     | Halogen-Free csfBGA | 256   | IND   |

| LCMXO3L-4300E-5MG324C     | 4300 | 1.2 V          | 5     | Halogen-Free csfBGA | 324   | COM   |

| LCMXO3L-4300E-6MG324C     | 4300 | 1.2 V          | 6     | Halogen-Free csfBGA | 324   | COM   |

| LCMXO3L-4300E-5MG324I     | 4300 | 1.2 V          | 5     | Halogen-Free csfBGA | 324   | IND   |

| LCMXO3L-4300E-6MG324I     | 4300 | 1.2 V          | 6     | Halogen-Free csfBGA | 324   | IND   |

| LCMXO3L-4300C-5BG256C     | 4300 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 256   | COM   |

| LCMXO3L-4300C-6BG256C     | 4300 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 256   | COM   |

| LCMXO3L-4300C-5BG256I     | 4300 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 256   | IND   |

| LCMXO3L-4300C-6BG256I     | 4300 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 256   | IND   |

| LCMXO3L-4300C-5BG324C     | 4300 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 324   | COM   |

| LCMXO3L-4300C-6BG324C     | 4300 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 324   | СОМ   |

| LCMXO3L-4300C-5BG324I     | 4300 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 324   | IND   |

| LCMXO3L-4300C-6BG324I     | 4300 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 324   | IND   |

| LCMXO3L-4300C-5BG400C     | 4300 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 400   | СОМ   |

| LCMXO3L-4300C-6BG400C     | 4300 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 400   | СОМ   |

| LCMXO3L-4300C-5BG400I     | 4300 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 400   | IND   |

| LCMXO3L-4300C-6BG400I     | 4300 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 400   | IND   |

# MachXO3 Family Data Sheet Supplemental Information

#### January 2016

Advance Data Sheet DS1047

## For Further Information

A variety of technical notes for the MachXO3 family are available on the Lattice web site.

- TN1282, MachXO3 sysCLOCK PLL Design and Usage Guide

- TN1281, Implementing High-Speed Interfaces with MachXO3 Devices

- TN1280, MachXO3 sysIO Usage Guide

- TN1279, MachXO3 Programming and Configuration Usage Guide

- TN1074, PCB Layout Recommendations for BGA Packages

- TN1087, Minimizing System Interruption During Configuration Using TransFR Technology

- AN8066, Boundary Scan Testability with Lattice sysIO Capability

- MachXO3 Device Pinout Files

- Thermal Management document

- Lattice design tools

© 2016 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# MachXO3 Family Data Sheet Revision History

#### February 2017

Advance Data Sheet DS1047

| Date              | Version | Section                                                                                   | Change Summary                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |