# E · Clattile Semiconductor Corporation - LCMX03LF-6900C-6BG400C Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                            |

|--------------------------------|-----------------------------------------------------------------------------------|

| Number of LABs/CLBs            | 858                                                                               |

| Number of Logic Elements/Cells | 6864                                                                              |

| Total RAM Bits                 | 245760                                                                            |

| Number of I/O                  | 335                                                                               |

| Number of Gates                | -                                                                                 |

| Voltage - Supply               | 2.375V ~ 3.465V                                                                   |

| Mounting Type                  | Surface Mount                                                                     |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                                   |

| Package / Case                 | 400-LFBGA                                                                         |

| Supplier Device Package        | 400-CABGA (17x17)                                                                 |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lcmxo3lf-6900c-6bg400c |

|                                |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# MachXO3 Family Data Sheet Architecture

#### February 2017

Advance Data Sheet DS1047

### **Architecture Overview**

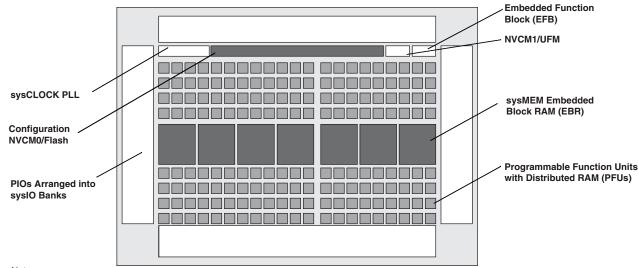

The MachXO3L/LF family architecture contains an array of logic blocks surrounded by Programmable I/O (PIO). All logic density devices in this family have sysCLOCK<sup>™</sup> PLLs and blocks of sysMEM Embedded Block RAM (EBRs). Figure 2-1 and Figure 2-2 show the block diagrams of the various family members.

Notes:

MachXO3L/LF-640 is similar to MachXO3L/LF-1300. MachXO3L/LF-640 has a lower LUT count.

MachXO3L devices have NVCM, MachXO3LF devices have Flash.

© 2017 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

### Modes of Operation

Each slice has up to four potential modes of operation: Logic, Ripple, RAM and ROM.

#### Logic Mode

In this mode, the LUTs in each slice are configured as 4-input combinatorial lookup tables. A LUT4 can have 16 possible input combinations. Any four input logic functions can be generated by programming this lookup table. Since there are two LUT4s per slice, a LUT5 can be constructed within one slice. Larger look-up tables such as LUT6, LUT7 and LUT8 can be constructed by concatenating other slices. Note LUT8 requires more than four slices.

#### **Ripple Mode**

Ripple mode supports the efficient implementation of small arithmetic functions. In Ripple mode, the following functions can be implemented by each slice:

- Addition 2-bit

- Subtraction 2-bit

- Add/subtract 2-bit using dynamic control

- Up counter 2-bit

- Down counter 2-bit

- Up/down counter with asynchronous clear

- Up/down counter with preload (sync)

- Ripple mode multiplier building block

- Multiplier support

- Comparator functions of A and B inputs

- A greater-than-or-equal-to B

- A not-equal-to B

- A less-than-or-equal-to B

Ripple mode includes an optional configuration that performs arithmetic using fast carry chain methods. In this configuration (also referred to as CCU2 mode) two additional signals, Carry Generate and Carry Propagate, are generated on a per-slice basis to allow fast arithmetic functions to be constructed by concatenating slices.

#### **RAM Mode**

In this mode, a 16x4-bit distributed single port RAM (SPR) can be constructed by using each LUT block in Slice 0 and Slice 1 as a 16x1-bit memory. Slice 2 is used to provide memory address and control signals.

MachXO3L/LF devices support distributed memory initialization.

The Lattice design tools support the creation of a variety of different size memories. Where appropriate, the software will construct these using distributed memory primitives that represent the capabilities of the PFU. Table 2-3 shows the number of slices required to implement different distributed RAM primitives. For more information about using RAM in MachXO3L/LF devices, please see TN1290, Memory Usage Guide for MachXO3 Devices.

#### Table 2-3. Number of Slices Required For Implementing Distributed RAM

|                                                          | SPR 16x4 | PDPR 16x4 |  |  |  |  |

|----------------------------------------------------------|----------|-----------|--|--|--|--|

| Number of slices                                         | 3        | 3         |  |  |  |  |

| Note: SPB = Single Port BAM, PDPB = Pseudo Dual Port BAM |          |           |  |  |  |  |

ote: SPR = Single Port RAM, PDPR = Pseudo Dual

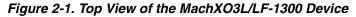

#### Figure 2-6. Secondary High Fanout Nets for MachXO3L/LF Devices

### sysCLOCK Phase Locked Loops (PLLs)

The sysCLOCK PLLs provide the ability to synthesize clock frequencies. All MachXO3L/LF devices have one or more sysCLOCK PLL. CLKI is the reference frequency input to the PLL and its source can come from an external I/O pin or from internal routing. CLKFB is the feedback signal to the PLL which can come from internal routing or an external I/O pin. The feedback divider is used to multiply the reference frequency and thus synthesize a higher frequency clock output.

The MachXO3L/LF sysCLOCK PLLs support high resolution (16-bit) fractional-N synthesis. Fractional-N frequency synthesis allows the user to generate an output clock which is a non-integer multiple of the input frequency. For more information about using the PLL with Fractional-N synthesis, please see TN1282, MachXO3 sysCLOCK PLL Design and Usage Guide.

Each output has its own output divider, thus allowing the PLL to generate different frequencies for each output. The output dividers can have a value from 1 to 128. The output dividers may also be cascaded together to generate low frequency clocks. The CLKOP, CLKOS, CLKOS2, and CLKOS3 outputs can all be used to drive the MachXO3L/LF clock distribution network directly or general purpose routing resources can be used.

The LOCK signal is asserted when the PLL determines it has achieved lock and de-asserted if a loss of lock is detected. A block diagram of the PLL is shown in Figure 2-7.

The setup and hold times of the device can be improved by programming a phase shift into the CLKOS, CLKOS2, and CLKOS3 output clocks which will advance or delay the output clock with reference to the CLKOP output clock.

state. The RPRST signal is used to reset the read pointer. The purpose of this reset is to retransmit the data that is in the FIFO. In these applications it is important to keep careful track of when a packet is written into or read from the FIFO.

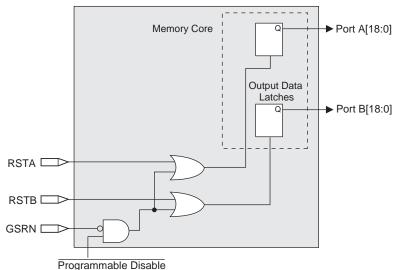

#### Memory Core Reset

The memory core contains data output latches for ports A and B. These are simple latches that can be reset synchronously or asynchronously. RSTA and RSTB are local signals, which reset the output latches associated with port A and port B respectively. The Global Reset (GSRN) signal resets both ports. The output data latches and associated resets for both ports are as shown in Figure 2-9.

#### Figure 2-9. Memory Core Reset

For further information on the sysMEM EBR block, please refer to TN1290, Memory Usage Guide for MachXO3 Devices.

#### EBR Asynchronous Reset

EBR asynchronous reset or GSR (if used) can only be applied if all clock enables are low for a clock cycle before the reset is applied and released a clock cycle after the reset is released, as shown in Figure 2-10. The GSR input to the EBR is always asynchronous.

#### Figure 2-10. EBR Asynchronous Reset (Including GSR) Timing Diagram

| Reset |  |

|-------|--|

| Clock |  |

| Clock |  |

If all clock enables remain enabled, the EBR asynchronous reset or GSR may only be applied and released after the EBR read and write clock inputs are in a steady state condition for a minimum of 1/f<sub>MAX</sub> (EBR clock). The reset release must adhere to the EBR synchronous reset setup time before the next active read or write clock edge.

If an EBR is pre-loaded during configuration, the GSR input must be disabled or the release of the GSR during device wake up must occur before the release of the device I/Os becoming active.

These instructions apply to all EBR RAM, ROM and FIFO implementations. For the EBR FIFO mode, the GSR signal is always enabled and the WE and RE signals act like the clock enable signals in Figure 2-10. The reset timing rules apply to the RPReset input versus the RE input and the RST input versus the WE and RE inputs. Both RST and RPReset are always asynchronous EBR inputs. For more details refer to TN1290, Memory Usage Guide for MachXO3 Devices.

Note that there are no reset restrictions if the EBR synchronous reset is used and the EBR GSR input is disabled.

## Programmable I/O Cells (PIC)

The programmable logic associated with an I/O is called a PIO. The individual PIO are connected to their respective sysIO buffers and pads. On the MachXO3L/LF devices, the PIO cells are assembled into groups of four PIO cells called a Programmable I/O Cell or PIC. The PICs are placed on all four sides of the device.

On all the MachXO3L/LF devices, two adjacent PIOs can be combined to provide a complementary output driver pair.

All PIO pairs can implement differential receivers. Half of the PIO pairs on the top edge of these devices can be configured as true LVDS transmit pairs. The PIO pairs on the bottom edge of these devices have on-chip differential termination and also provide PCI support.

### **Output Register Block**

The output register block registers signals from the core of the device before they are passed to the sysIO buffers.

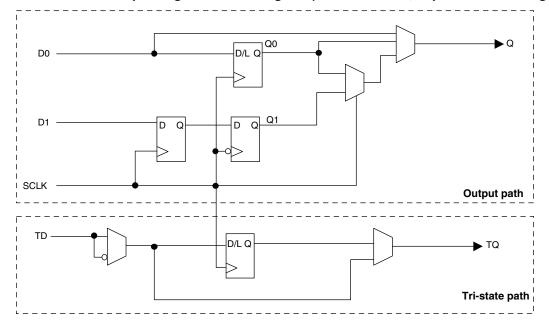

#### Left, Top, Bottom Edges

In SDR mode, D0 feeds one of the flip-flops that then feeds the output. The flip-flop can be configured as a D-type register or latch.

In DDR generic mode, D0 and D1 inputs are fed into registers on the positive edge of the clock. At the next falling edge the registered D1 input is registered into the register Q1. A multiplexer running off the same clock is used to switch the mux between the outputs of registers Q0 and Q1 that will then feed the output.

Figure 2-12 shows the output register block on the left, top and bottom edges.

Figure 2-12. MachXO3L/LF Output Register Block Diagram (PIO on the Left, Top and Bottom Edges)

### Tri-state Register Block

The tri-state register block registers tri-state control signals from the core of the device before they are passed to the sysIO buffers. The block contains a register for SDR operation. In SDR, TD input feeds one of the flip-flops that then feeds the output.

## Output Gearbox

Each PIC on the top edge has a built-in 8:1 output gearbox. Each of these output gearboxes may be programmed as a 7:1 serializer or as one ODDRX4 (8:1) gearbox or as two ODDRX2 (4:1) gearboxes. Table 2-10 shows the gearbox signals.

#### Table 2-10. Output Gearbox Signal List

| Name                       | I/O Type | Description                     |

|----------------------------|----------|---------------------------------|

| Q                          | Output   | High-speed data output          |

| D[7:0]                     | Input    | Low-speed data from device core |

| Video TX(7:1): D[6:0]      |          |                                 |

| GDDRX4(8:1): D[7:0]        |          |                                 |

| GDDRX2(4:1)(IOL-A): D[3:0] |          |                                 |

| GDDRX2(4:1)(IOL-C): D[7:4] |          |                                 |

| SCLK                       | Input    | Slow-speed system clock         |

| ECLK [1:0]                 | Input    | High-speed edge clock           |

| RST                        | Input    | Reset                           |

The gearboxes have three stage pipeline registers. The first stage registers sample the low-speed input data on the low-speed system clock. The second stage registers transfer data from the low-speed clock registers to the high-speed clock registers. The third stage pipeline registers controlled by high-speed edge clock shift and mux the high-speed data out to the sysIO buffer. Figure 2-14 shows the output gearbox block diagram.

## Hot Socketing

The MachXO3L/LF devices have been carefully designed to ensure predictable behavior during power-up and power-down. Leakage into I/O pins is controlled to within specified limits. This allows for easy integration with the rest of the system. These capabilities make the MachXO3L/LF ideal for many multiple power supply and hot-swap applications.

## **On-chip Oscillator**

Every MachXO3L/LF device has an internal CMOS oscillator. The oscillator output can be routed as a clock to the clock tree or as a reference clock to the sysCLOCK PLL using general routing resources. The oscillator frequency can be divided by internal logic. There is a dedicated programming bit and a user input to enable/disable the oscillator. The oscillator frequency ranges from 2.08 MHz to 133 MHz. The software default value of the Master Clock (MCLK) is nominally 2.08 MHz. When a different MCLK is selected during the design process, the following sequence takes place:

- 1. Device powers up with a nominal MCLK frequency of 2.08 MHz.

- 2. During configuration, users select a different master clock frequency.

- 3. The MCLK frequency changes to the selected frequency once the clock configuration bits are received.

- 4. If the user does not select a master clock frequency, then the configuration bitstream defaults to the MCLK frequency of 2.08 MHz.

Table 2-13 lists all the available MCLK frequencies.

#### Table 2-13. Available MCLK Frequencies

| MCLK (MHz, Nominal) | MCLK (MHz, Nominal) | MCLK (MHz, Nominal) |

|---------------------|---------------------|---------------------|

| 2.08 (default)      | 9.17                | 33.25               |

| 2.46                | 10.23               | 38                  |

| 3.17                | 13.3                | 44.33               |

| 4.29                | 14.78               | 53.2                |

| 5.54                | 20.46               | 66.5                |

| 7                   | 26.6                | 88.67               |

| 8.31                | 29.56               | 133                 |

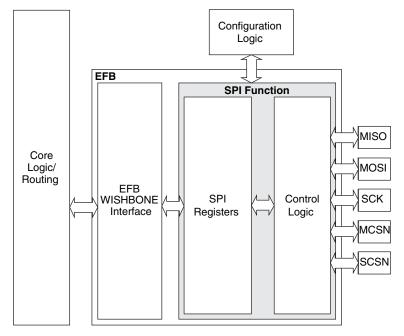

There are some limitations on the use of the hardened user SPI. These are defined in the following technical notes:

- TN1087, Minimizing System Interruption During Configuration Using TransFR Technology (Appendix B)

- TN1293, Using Hardened Control Functions in MachXO3 Devices

#### Figure 2-19. SPI Core Block Diagram

Table 2-15 describes the signals interfacing with the SPI cores.

Table 2-15. SPI Core Signal Description

| Signal Name | I/O | Master/Slave | Description                                                                                                                                                                               |

|-------------|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| spi_csn[0]  | 0   | Master       | SPI master chip-select output                                                                                                                                                             |

| spi_csn[17] | 0   | Master       | Additional SPI chip-select outputs (total up to eight slaves)                                                                                                                             |

| spi_scsn    | I   | Slave        | SPI slave chip-select input                                                                                                                                                               |

| spi_irq     | 0   | Master/Slave | Interrupt request                                                                                                                                                                         |

| spi_clk     | I/O | Master/Slave | SPI clock. Output in master mode. Input in slave mode.                                                                                                                                    |

| spi_miso    | I/O | Master/Slave | SPI data. Input in master mode. Output in slave mode.                                                                                                                                     |

| spi_mosi    | I/O | Master/Slave | SPI data. Output in master mode. Input in slave mode.                                                                                                                                     |

| sn          | I   | Slave        | Configuration Slave Chip Select (active low), dedicated for selecting the Con-<br>figuration Logic.                                                                                       |

| cfg_stdby   | 0   | Master/Slave | Stand-by signal – To be connected only to the power module of the MachXO3L/LF device. The signal is enabled only if the "Wakeup Enable" feature has been set within the EFB GUI, SPI Tab. |

| cfg_wake    | О   | Master/Slave | Wake-up signal – To be connected only to the power module of the MachXO3L/LF device. The signal is enabled only if the "Wakeup Enable" feature has been set within the EFB GUI, SPI Tab.  |

# **Configuration and Testing**

This section describes the configuration and testing features of the MachXO3L/LF family.

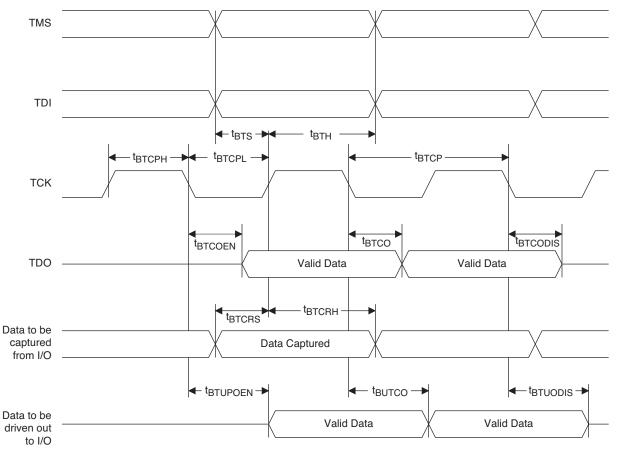

### IEEE 1149.1-Compliant Boundary Scan Testability

All MachXO3L/LF devices have boundary scan cells that are accessed through an IEEE 1149.1 compliant test access port (TAP). This allows functional testing of the circuit board, on which the device is mounted, through a serial scan path that can access all critical logic nodes. Internal registers are linked internally, allowing test data to be shifted in and loaded directly onto test nodes, or test data to be captured and shifted out for verification. The test access port consists of dedicated I/Os: TDI, TDO, TCK and TMS. The test access port shares its power supply with  $V_{CCIO}$  Bank 0 and can operate with LVCMOS3.3, 2.5, 1.8, 1.5, and 1.2 standards.

For more details on boundary scan test, see AN8066, Boundary Scan Testability with Lattice sysIO Capability and TN1087, Minimizing System Interruption During Configuration Using TransFR Technology.

### **Device Configuration**

All MachXO3L/LF devices contain two ports that can be used for device configuration. The Test Access Port (TAP), which supports bit-wide configuration and the sysCONFIG port which supports serial configuration through I<sup>2</sup>C or SPI. The TAP supports both the IEEE Standard 1149.1 Boundary Scan specification and the IEEE Standard 1532 In-System Configuration specification. There are various ways to configure a MachXO3L/LF device:

- 1. Internal NVCM/Flash Download

- 2. JTAG

- 3. Standard Serial Peripheral Interface (Master SPI mode) interface to boot PROM memory

- 4. System microprocessor to drive a serial slave SPI port (SSPI mode)

- 5. Standard I<sup>2</sup>C Interface to system microprocessor

Upon power-up, the configuration SRAM is ready to be configured using the selected sysCONFIG port. Once a configuration port is selected, it will remain active throughout that configuration cycle. The IEEE 1149.1 port can be activated any time after power-up by sending the appropriate command through the TAP port. Optionally the device can run a CRC check upon entering the user mode. This will ensure that the device was configured correctly.

The sysCONFIG port has 10 dual-function pins which can be used as general purpose I/Os if they are not required for configuration. See TN1279, MachXO3 Programming and Configuration Usage Guide for more information about using the dual-use pins as general purpose I/Os.

Lattice design software uses proprietary compression technology to compress bit-streams for use in MachXO3L/ LF devices. Use of this technology allows Lattice to provide a lower cost solution. In the unlikely event that this technology is unable to compress bitstreams to fit into the amount of on-chip NVCM/Flash, there are a variety of techniques that can be utilized to allow the bitstream to fit in the on-chip NVCM/Flash. For more details, refer to TN1279, MachXO3 Programming and Configuration Usage Guide.

The Test Access Port (TAP) has five dual purpose pins (TDI, TDO, TMS, TCK and JTAGENB). These pins are dual function pins - TDI, TDO, TMS and TCK can be used as general purpose I/O if desired. For more details, refer to TN1279, MachXO3 Programming and Configuration Usage Guide.

#### TransFR (Transparent Field Reconfiguration)

TransFR is a unique Lattice technology that allows users to update their logic in the field without interrupting system operation using a simple push-button solution. For more details refer to TN1087, Minimizing System Interruption During Configuration Using TransFR Technology for details.

# sysIO Recommended Operating Conditions

|                        |       | V <sub>CCIO</sub> (V) |       |      | V <sub>REF</sub> (V) |      |  |  |

|------------------------|-------|-----------------------|-------|------|----------------------|------|--|--|

| Standard               | Min.  | Тур.                  | Max.  | Min. | Тур.                 | Max. |  |  |

| LVCMOS 3.3             | 3.135 | 3.3                   | 3.465 | —    | —                    | —    |  |  |

| LVCMOS 2.5             | 2.375 | 2.5                   | 2.625 | —    | —                    | —    |  |  |

| LVCMOS 1.8             | 1.71  | 1.8                   | 1.89  | —    | —                    | —    |  |  |

| LVCMOS 1.5             | 1.425 | 1.5                   | 1.575 | —    | —                    | —    |  |  |

| LVCMOS 1.2             | 1.14  | 1.2                   | 1.26  | —    | —                    | —    |  |  |

| LVTTL                  | 3.135 | 3.3                   | 3.465 | —    | —                    | —    |  |  |

| LVDS25 <sup>1, 2</sup> | 2.375 | 2.5                   | 2.625 | —    | —                    | —    |  |  |

| LVDS33 <sup>1, 2</sup> | 3.135 | 3.3                   | 3.465 | —    | —                    | —    |  |  |

| LVPECL <sup>1</sup>    | 3.135 | 3.3                   | 3.465 | —    | —                    | —    |  |  |

| BLVDS <sup>1</sup>     | 2.375 | 2.5                   | 2.625 | —    | —                    | —    |  |  |

| MIPI <sup>3</sup>      | 2.375 | 2.5                   | 2.625 | —    | —                    | —    |  |  |

| MIPI_LP <sup>3</sup>   | 1.14  | 1.2                   | 1.26  | —    | —                    | _    |  |  |

| LVCMOS25R33            | 3.135 | 3.3                   | 3.6   | 1.1  | 1.25                 | 1.4  |  |  |

| LVCMOS18R33            | 3.135 | 3.3                   | 3.6   | 0.75 | 0.9                  | 1.05 |  |  |

| LVCMOS18R25            | 2.375 | 2.5                   | 2.625 | 0.75 | 0.9                  | 1.05 |  |  |

| LVCMOS15R33            | 3.135 | 3.3                   | 3.6   | 0.6  | 0.75                 | 0.9  |  |  |

| LVCMOS15R25            | 2.375 | 2.5                   | 2.625 | 0.6  | 0.75                 | 0.9  |  |  |

| LVCMOS12R334           | 3.135 | 3.3                   | 3.6   | 0.45 | 0.6                  | 0.75 |  |  |

| LVCMOS12R254           | 2.375 | 2.5                   | 2.625 | 0.45 | 0.6                  | 0.75 |  |  |

| LVCMOS10R334           | 3.135 | 3.3                   | 3.6   | 0.35 | 0.5                  | 0.65 |  |  |

| LVCMOS10R254           | 2.375 | 2.5                   | 2.625 | 0.35 | 0.5                  | 0.65 |  |  |

1. Inputs on-chip. Outputs are implemented with the addition of external resistors.

2. For the dedicated LVDS buffers.

3. Requires the addition of external resistors.

4. Supported only for inputs and BIDIs for -6 speed grade devices.

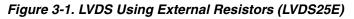

### LVDS Emulation

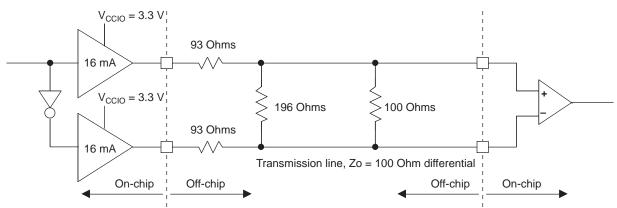

MachXO3L/LF devices can support LVDS outputs via emulation (LVDS25E). The output is emulated using complementary LVCMOS outputs in conjunction with resistors across the driver outputs on all devices. The scheme shown in Figure 3-1 is one possible solution for LVDS standard implementation. Resistor values in Figure 3-1 are industry standard values for 1% resistors.

Note: All resistors are ±1%.

#### Table 3-1. LVDS25E DC Conditions

#### **Over Recommended Operating Conditions**

| Parameter         | Description                 | Тур.  | Units |  |  |  |

|-------------------|-----------------------------|-------|-------|--|--|--|

| Z <sub>OUT</sub>  | Output impedance            | 20    | Ohms  |  |  |  |

| R <sub>S</sub>    | Driver series resistor      | 158   | Ohms  |  |  |  |

| R <sub>P</sub>    | Driver parallel resistor    | 140   | Ohms  |  |  |  |

| R <sub>T</sub>    | Receiver termination        | 100   | Ohms  |  |  |  |

| V <sub>OH</sub>   | Output high voltage         | 1.43  | V     |  |  |  |

| V <sub>OL</sub>   | Output low voltage          | 1.07  | V     |  |  |  |

| V <sub>OD</sub>   | Output differential voltage | 0.35  | V     |  |  |  |

| V <sub>CM</sub>   | Output common mode voltage  | 1.25  | V     |  |  |  |

| Z <sub>BACK</sub> | Back impedance              | 100.5 | Ohms  |  |  |  |

| I <sub>DC</sub>   | DC output current           | 6.03  | mA    |  |  |  |

### LVPECL

The MachXO3L/LF family supports the differential LVPECL standard through emulation. This output standard is emulated using complementary LVCMOS outputs in conjunction with resistors across the driver outputs on all the devices. The LVPECL input standard is supported by the LVDS differential input buffer. The scheme shown in Differential LVPECL is one possible solution for point-to-point signals.

#### Figure 3-3. Differential LVPECL

#### Table 3-3. LVPECL DC Conditions<sup>1</sup>

| Symbol            | Description                 | Nominal | Units |

|-------------------|-----------------------------|---------|-------|

| Z <sub>OUT</sub>  | Output impedance            | 20      | Ohms  |

| R <sub>S</sub>    | Driver series resistor      | 93      | Ohms  |

| R <sub>P</sub>    | Driver parallel resistor    | 196     | Ohms  |

| R <sub>T</sub>    | Receiver termination        | 100     | Ohms  |

| V <sub>OH</sub>   | Output high voltage         | 2.05    | V     |

| V <sub>OL</sub>   | Output low voltage          | 1.25    | V     |

| V <sub>OD</sub>   | Output differential voltage | 0.80    | V     |

| V <sub>CM</sub>   | Output common mode voltage  | 1.65    | V     |

| Z <sub>BACK</sub> | Back impedance              | 100.5   | Ohms  |

| I <sub>DC</sub>   | DC output current           | 12.11   | mA    |

#### **Over Recommended Operating Conditions**

1. For input buffer, see LVDS table.

For further information on LVPECL, BLVDS and other differential interfaces please see details of additional technical documentation at the end of the data sheet.

|           | Description                                                            | Min. | Тур. | Max. | Units |

|-----------|------------------------------------------------------------------------|------|------|------|-------|

| Low Power |                                                                        |      |      |      |       |

| VCCIO     | VCCIO of the Bank with LVCMOS12D 6 mA<br>drive bidirectional IO buffer |      | 1.2  |      | V     |

| VIH       | Logic 1 input voltage                                                  | —    | _    | 0.88 | V     |

| VIL       | Logic 0 input voltage, not in ULP State                                | 0.55 | _    | _    | V     |

| VHYST     | Input hysteresis                                                       | 25   | —    | —    | mV    |

1. Over Recommended Operating Conditions

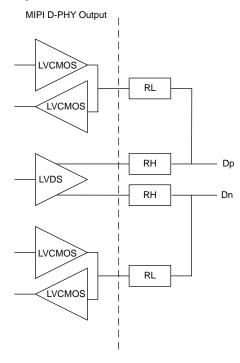

#### Figure 3-5. MIPI D-PHY Output Using External Resistors

# **JTAG Port Timing Specifications**

| Symbol               | Parameter                                                          | Min. | Max. | Units |

|----------------------|--------------------------------------------------------------------|------|------|-------|

| f <sub>MAX</sub>     | TCK clock frequency                                                |      | 25   | MHz   |

| t <sub>BTCPH</sub>   | TCK [BSCAN] clock pulse width high                                 | 20   | —    | ns    |

| t <sub>BTCPL</sub>   | TCK [BSCAN] clock pulse width low                                  | 20   | —    | ns    |

| t <sub>BTS</sub>     | TCK [BSCAN] setup time                                             | 10   | _    | ns    |

| t <sub>BTH</sub>     | TCK [BSCAN] hold time                                              | 8    | —    | ns    |

| t <sub>BTCO</sub>    | TAP controller falling edge of clock to valid output               |      | 10   | ns    |

| t <sub>BTCODIS</sub> | TAP controller falling edge of clock to valid disable              |      | 10   | ns    |

| t <sub>BTCOEN</sub>  | TAP controller falling edge of clock to valid enable               | _    | 10   | ns    |

| t <sub>BTCRS</sub>   | BSCAN test capture register setup time                             | 8    | —    | ns    |

| t <sub>BTCRH</sub>   | BSCAN test capture register hold time                              | 20   | —    | ns    |

| t <sub>BUTCO</sub>   | BSCAN test update register, falling edge of clock to valid output  | _    | 25   | ns    |

| t <sub>BTUODIS</sub> | BSCAN test update register, falling edge of clock to valid disable | _    | 25   | ns    |

| t <sub>BTUPOEN</sub> | BSCAN test update register, falling edge of clock to valid enable  | _    | 25   | ns    |

#### Figure 3-8. JTAG Port Timing Waveforms

# **Pin Information Summary**

|                                                        | MachXO3L/LF<br>-640 |         |           |           |          |

|--------------------------------------------------------|---------------------|---------|-----------|-----------|----------|

|                                                        | CSFBGA121           | WLCSP36 | CSFBGA121 | CSFBGA256 | CABGA256 |

| General Purpose IO per Bank                            | •                   | •       | •         | •         | •        |

| Bank 0                                                 | 24                  | 15      | 24        | 50        | 50       |

| Bank 1                                                 | 26                  | 0       | 26        | 52        | 52       |

| Bank 2                                                 | 26                  | 9       | 26        | 52        | 52       |

| Bank 3                                                 | 24                  | 4       | 24        | 16        | 16       |

| Bank 4                                                 | 0                   | 0       | 0         | 16        | 16       |

| Bank 5                                                 | 0                   | 0       | 0         | 20        | 20       |

| Total General Purpose Single Ended IO                  | 100                 | 28      | 100       | 206       | 206      |

| Differential IO per Bank                               |                     | 1       |           |           | L        |

| Bank 0                                                 | 12                  | 8       | 12        | 25        | 25       |

| Bank 1                                                 | 13                  | 0       | 13        | 26        | 26       |

| Bank 2                                                 | 13                  | 4       | 13        | 26        | 26       |

| Bank 3                                                 | 11                  | 2       | 11        | 8         | 8        |

| Bank 4                                                 | 0                   | 0       | 0         | 8         | 8        |

| Bank 5                                                 | 0                   | 0       | 0         | 10        | 10       |

| Total General Purpose Differential IO                  | 49                  | 14      | 49        | 103       | 103      |

| Dual Function IO                                       | 33                  | 25      | 33        | 33        | 33       |

| Number 7:1 or 8:1 Gearboxes                            |                     | I.      |           |           | I        |

| Number of 7:1 or 8:1 Output Gearbox Available (Bank 0) | 7                   | 3       | 7         | 14        | 14       |

| Number of 7:1 or 8:1 Input Gearbox Available (Bank 2)  | 7                   | 2       | 7         | 14        | 14       |

| High-speed Differential Outputs                        |                     | L       |           |           | L        |

| Bank 0                                                 | 7                   | 3       | 7         | 14        | 14       |

| VCCIO Pins                                             |                     | L       |           |           | L        |

| Bank 0                                                 | 1                   | 1       | 1         | 4         | 4        |

| Bank 1                                                 | 1                   | 0       | 1         | 3         | 4        |

| Bank 2                                                 | 1                   | 1       | 1         | 4         | 4        |

| Bank 3                                                 | 3                   | 1       | 3         | 2         | 1        |

| Bank 4                                                 | 0                   | 0       | 0         | 2         | 2        |

| Bank 5                                                 | 0                   | 0       | 0         | 2         | 1        |

| VCC                                                    | 4                   | 2       | 4         | 8         | 8        |

| GND                                                    | 10                  | 2       | 10        | 24        | 24       |

| NC                                                     | 0                   | 0       | 0         | 0         | 1        |

| Reserved for Configuration                             | 1                   | 1       | 1         | 1         | 1        |

| Total Count of Bonded Pins                             | 121                 | 36      | 121       | 256       | 256      |

|                                                        | MachXO3L/LF-2100 |           |           |           |          |          |

|--------------------------------------------------------|------------------|-----------|-----------|-----------|----------|----------|

|                                                        | WLCSP49          | CSFBGA121 | CSFBGA256 | CSFBGA324 | CABGA256 | CABGA324 |

| General Purpose IO per Bank                            | 1                |           |           |           |          |          |

| Bank 0                                                 | 19               | 24        | 50        | 71        | 50       | 71       |

| Bank 1                                                 | 0                | 26        | 52        | 62        | 52       | 68       |

| Bank 2                                                 | 13               | 26        | 52        | 72        | 52       | 72       |

| Bank 3                                                 | 0                | 7         | 16        | 22        | 16       | 24       |

| Bank 4                                                 | 0                | 7         | 16        | 14        | 16       | 16       |

| Bank 5                                                 | 6                | 10        | 20        | 27        | 20       | 28       |

| Total General Purpose Single Ended IO                  | 38               | 100       | 206       | 268       | 206      | 279      |

| Differential IO per Bank                               | 1                |           |           |           |          |          |

| Bank 0                                                 | 10               | 12        | 25        | 36        | 25       | 36       |

| Bank 1                                                 | 0                | 13        | 26        | 30        | 26       | 34       |

| Bank 2                                                 | 6                | 13        | 26        | 36        | 26       | 36       |

| Bank 3                                                 | 0                | 3         | 8         | 10        | 8        | 12       |

| Bank 4                                                 | 0                | 3         | 8         | 6         | 8        | 8        |

| Bank 5                                                 | 3                | 5         | 10        | 13        | 10       | 14       |

| Total General Purpose Differential IO                  | 19               | 49        | 103       | 131       | 103      | 140      |

| Dual Function IO                                       | 25               | 33        | 33        | 37        | 33       | 37       |

| Number 7:1 or 8:1 Gearboxes                            | •                |           |           | •         | •        | •        |

| Number of 7:1 or 8:1 Output Gearbox Available (Bank 0) | 5                | 7         | 14        | 18        | 14       | 18       |

| Number of 7:1 or 8:1 Input Gearbox Available (Bank 2)  | 6                | 13        | 14        | 18        | 14       | 18       |

| High-speed Differential Outputs                        | •                |           |           | •         | •        | •        |

| Bank 0                                                 | 5                | 7         | 14        | 18        | 14       | 18       |

| VCCIO Pins                                             | 1                |           |           |           |          |          |

| Bank 0                                                 | 2                | 1         | 4         | 4         | 4        | 4        |

| Bank 1                                                 | 0                | 1         | 3         | 4         | 4        | 4        |

| Bank 2                                                 | 1                | 1         | 4         | 4         | 4        | 4        |

| Bank 3                                                 | 0                | 1         | 2         | 2         | 1        | 2        |

| Bank 4                                                 | 0                | 1         | 2         | 2         | 2        | 2        |

| Bank 5                                                 | 1                | 1         | 2         | 2         | 1        | 2        |

| VCC                                                    | 2                | 4         | 8         | 8         | 8        | 10       |

| GND                                                    | 4                | 10        | 24        | 16        | 24       | 16       |

| NC                                                     | 0                | 0         | 0         | 13        | 1        | 0        |

| Reserved for Configuration                             | 1                | 1         | 1         | 1         | 1        | 1        |

| Total Count of Bonded Pins                             | 49               | 121       | 256       | 324       | 256      | 324      |

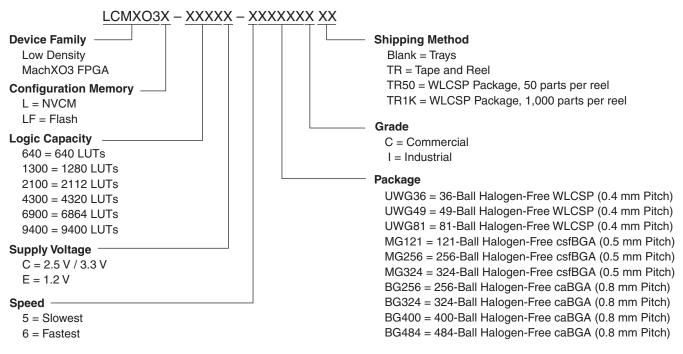

# MachXO3 Family Data Sheet Ordering Information

May 2016

Advance Data Sheet DS1047

# MachXO3 Part Number Description

## **Ordering Information**

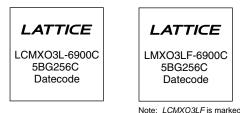

MachXO3L/LF devices have top-side markings as shown in the examples below, on the 256-Ball caBGA package with MachXO3-6900 device in Commercial Temperature in Speed Grade 5. Notice that for the MachXO3LF device, *LMXO3LF* is used instead of *LCMXO3LF* as in the Part Number.

with LMXO3LF

Note: Markings are abbreviated for small packages.

<sup>© 2016</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Part Number               | LUTs | Supply Voltage | Speed | Package             | Leads | Temp. |

|---------------------------|------|----------------|-------|---------------------|-------|-------|

| LCMXO3L-2100E-6MG324I     | 2100 | 1.2 V          | 6     | Halogen-Free csfBGA | 324   | IND   |

| LCMXO3L-2100C-5BG256C     | 2100 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 256   | СОМ   |

| LCMXO3L-2100C-6BG256C     | 2100 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 256   | COM   |

| LCMXO3L-2100C-5BG256I     | 2100 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 256   | IND   |

| LCMXO3L-2100C-6BG256I     | 2100 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 256   | IND   |

| LCMXO3L-2100C-5BG324C     | 2100 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 324   | COM   |

| LCMXO3L-2100C-6BG324C     | 2100 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 324   | COM   |

| LCMXO3L-2100C-5BG324I     | 2100 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 324   | IND   |

| LCMXO3L-2100C-6BG324I     | 2100 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 324   | IND   |

|                           |      |                |       | ·                   |       |       |

| Part Number               | LUTs | Supply Voltage | Speed | Package             | Leads | Temp. |

| LCMXO3L-4300E-5UWG81CTR   | 4300 | 1.2 V          | 5     | Halogen-Free WLCSP  | 81    | COM   |

| LCMXO3L-4300E-5UWG81CTR50 | 4300 | 1.2 V          | 5     | Halogen-Free WLCSP  | 81    | COM   |

| LCMXO3L-4300E-5UWG81CTR1K | 4300 | 1.2 V          | 5     | Halogen-Free WLCSP  | 81    | COM   |

| LCMXO3L-4300E-5UWG81ITR   | 4300 | 1.2 V          | 5     | Halogen-Free WLCSP  | 81    | IND   |

| LCMXO3L-4300E-5UWG81ITR50 | 4300 | 1.2 V          | 5     | Halogen-Free WLCSP  | 81    | IND   |

| LCMXO3L-4300E-5UWG81ITR1K | 4300 | 1.2 V          | 5     | Halogen-Free WLCSP  | 81    | IND   |

| LCMXO3L-4300E-5MG121C     | 4300 | 1.2 V          | 5     | Halogen-Free csfBGA | 121   | COM   |

| LCMXO3L-4300E-6MG121C     | 4300 | 1.2 V          | 6     | Halogen-Free csfBGA | 121   | COM   |

| LCMXO3L-4300E-5MG121I     | 4300 | 1.2 V          | 5     | Halogen-Free csfBGA | 121   | IND   |

| LCMXO3L-4300E-6MG121I     | 4300 | 1.2 V          | 6     | Halogen-Free csfBGA | 121   | IND   |

| LCMXO3L-4300E-5MG256C     | 4300 | 1.2 V          | 5     | Halogen-Free csfBGA | 256   | COM   |

| LCMXO3L-4300E-6MG256C     | 4300 | 1.2 V          | 6     | Halogen-Free csfBGA | 256   | COM   |

| LCMXO3L-4300E-5MG256I     | 4300 | 1.2 V          | 5     | Halogen-Free csfBGA | 256   | IND   |

| LCMXO3L-4300E-6MG256I     | 4300 | 1.2 V          | 6     | Halogen-Free csfBGA | 256   | IND   |

| LCMXO3L-4300E-5MG324C     | 4300 | 1.2 V          | 5     | Halogen-Free csfBGA | 324   | COM   |

| LCMXO3L-4300E-6MG324C     | 4300 | 1.2 V          | 6     | Halogen-Free csfBGA | 324   | COM   |

| LCMXO3L-4300E-5MG324I     | 4300 | 1.2 V          | 5     | Halogen-Free csfBGA | 324   | IND   |

| LCMXO3L-4300E-6MG324I     | 4300 | 1.2 V          | 6     | Halogen-Free csfBGA | 324   | IND   |

| LCMXO3L-4300C-5BG256C     | 4300 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 256   | COM   |

| LCMXO3L-4300C-6BG256C     | 4300 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 256   | COM   |

| LCMXO3L-4300C-5BG256I     | 4300 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 256   | IND   |

| LCMXO3L-4300C-6BG256I     | 4300 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 256   | IND   |

| LCMXO3L-4300C-5BG324C     | 4300 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 324   | COM   |

| LCMXO3L-4300C-6BG324C     | 4300 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 324   | СОМ   |

| LCMXO3L-4300C-5BG324I     | 4300 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 324   | IND   |

| LCMXO3L-4300C-6BG324I     | 4300 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 324   | IND   |

| LCMXO3L-4300C-5BG400C     | 4300 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 400   | СОМ   |

| LCMXO3L-4300C-6BG400C     | 4300 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 400   | СОМ   |

| LCMXO3L-4300C-5BG400I     | 4300 | 2.5 V / 3.3 V  | 5     | Halogen-Free caBGA  | 400   | IND   |

| LCMXO3L-4300C-6BG400I     | 4300 | 2.5 V / 3.3 V  | 6     | Halogen-Free caBGA  | 400   | IND   |

# MachXO3 Family Data Sheet Revision History

#### February 2017

Advance Data Sheet DS1047

| Date          | Version                                                         | Section                             | Change Summary                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|---------------|-----------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| February 2017 | February 2017 1.8 Architecture DC and Switching Characteristics |                                     | Updated Supported Standards section. Corrected "MDVS" to "MLDVS"<br>Table 2-11, Supported Input Standards.                                                                                                                                                                                                                                                                                                                    |  |  |

|               |                                                                 |                                     | Updated ESD Performance section. Added reference to the MachXO2<br>Product Family Qualification Summary document.                                                                                                                                                                                                                                                                                                             |  |  |

|               |                                                                 |                                     | Updated Static Supply Current – C/E Devices section.<br>Added footnote 7.                                                                                                                                                                                                                                                                                                                                                     |  |  |

|               |                                                                 |                                     | Updated MachXO3L/LF External Switching Characteristics – C/E<br>Devices section.<br>— Populated values for MachXO3L/LF-9400.<br>— Under 7:1 LVDS Outputs – GDDR71_TX.ECLK.7:1, corrected "t <sub>DVB</sub> "<br>to "t <sub>DIB</sub> " and "t <sub>DVA</sub> " to "t <sub>DIA</sub> " and revised their descriptions.<br>— Added Figure 3-6, Receiver GDDR71_RX Waveforms and Figure 3-7,<br>Transmitter GDDR71_TX Waveforms. |  |  |

|               |                                                                 | Pinout Information                  | Updated the Pin Information Summary section. Added MachXO3L/LF-<br>9600C packages.                                                                                                                                                                                                                                                                                                                                            |  |  |

| May 2016      | 1.7                                                             | DC and Switching<br>Characteristics | Updated Absolute Maximum Ratings section. Modified I/O Tri-state Volt-<br>age Applied and Dedicated Input Voltage Applied footnotes.                                                                                                                                                                                                                                                                                          |  |  |

|               |                                                                 |                                     | Updated sysIO Recommended Operating Conditions section.<br>— Added standards.<br>— Added V <sub>REF</sub> (V)<br>— Added footnote 4.                                                                                                                                                                                                                                                                                          |  |  |

|               |                                                                 |                                     | Updated sysIO Single-Ended DC Electrical Characteristics section.<br>Added I/O standards.                                                                                                                                                                                                                                                                                                                                     |  |  |

| Orderir       |                                                                 | Ordering Information                | Updated MachXO3L Ultra Low Power Commercial and Industrial Grade Devices, Halogen Free (RoHS) Packaging section. Added LCMXO3L-9400C part numbers.                                                                                                                                                                                                                                                                            |  |  |

|               |                                                                 |                                     | Updated MachXO3LF Ultra Low Power Commercial and Industrial Grade Devices, Halogen Free (RoHS) Packaging section. Added LCMXO3L-9400C part numbers.                                                                                                                                                                                                                                                                           |  |  |

<sup>© 2017</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.