# E · ) (Lattice Semiconductor Corporation - LCMXO3LF-6900E-5MG324C Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                                   |

|--------------------------------|-----------------------------------------------------------------------------------|

| Product Status                 | Active                                                                            |

| Number of LABs/CLBs            | 858                                                                               |

| Number of Logic Elements/Cells | 6864                                                                              |

| Total RAM Bits                 | 245760                                                                            |

| Number of I/O                  | 281                                                                               |

| Number of Gates                | -                                                                                 |

| Voltage - Supply               | 1.14V ~ 1.26V                                                                     |

| Mounting Type                  | Surface Mount                                                                     |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                                   |

| Package / Case                 | 324-VFBGA                                                                         |

| Supplier Device Package        | 324-CSFBGA (10x10)                                                                |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lcmxo3lf-6900e-5mg324c |

|                                |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **PFU Blocks**

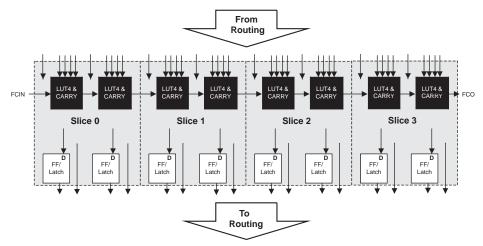

The core of the MachXO3L/LF device consists of PFU blocks, which can be programmed to perform logic, arithmetic, distributed RAM and distributed ROM functions. Each PFU block consists of four interconnected slices numbered 0 to 3 as shown in Figure 2-3. Each slice contains two LUTs and two registers. There are 53 inputs and 25 outputs associated with each PFU block.

### Figure 2-3. PFU Block Diagram

### Slices

Slices 0-3 contain two LUT4s feeding two registers. Slices 0-2 can be configured as distributed memory. Table 2-1 shows the capability of the slices in PFU blocks along with the operation modes they enable. In addition, each PFU contains logic that allows the LUTs to be combined to perform functions such as LUT5, LUT6, LUT7 and LUT8. The control logic performs set/reset functions (programmable as synchronous/ asynchronous), clock select, chip-select and wider RAM/ROM functions.

#### Table 2-1. Resources and Modes Available per Slice

|         | PFU Block               |                         |  |  |  |

|---------|-------------------------|-------------------------|--|--|--|

| Slice   | Resources               | Modes                   |  |  |  |

| Slice 0 | 2 LUT4s and 2 Registers | Logic, Ripple, RAM, ROM |  |  |  |

| Slice 1 | 2 LUT4s and 2 Registers | Logic, Ripple, RAM, ROM |  |  |  |

| Slice 2 | 2 LUT4s and 2 Registers | Logic, Ripple, RAM, ROM |  |  |  |

| Slice 3 | 2 LUT4s and 2 Registers | Logic, Ripple, ROM      |  |  |  |

Figure 2-4 shows an overview of the internal logic of the slice. The registers in the slice can be configured for positive/negative and edge triggered or level sensitive clocks. All slices have 15 inputs from routing and one from the carry-chain (from the adjacent slice or PFU). There are seven outputs: six for routing and one to carry-chain (to the adjacent PFU). Table 2-2 lists the signals associated with Slices 0-3.

| Port Name        | Description                 | Active State      |

|------------------|-----------------------------|-------------------|

| CLK              | Clock                       | Rising Clock Edge |

| CE               | Clock Enable                | Active High       |

| OCE <sup>1</sup> | Output Clock Enable         | Active High       |

| RST              | Reset                       | Active High       |

| BE <sup>1</sup>  | Byte Enable                 | Active High       |

| WE               | Write Enable                | Active High       |

| AD               | Address Bus                 | —                 |

| DI               | Data In                     | _                 |

| DO               | Data Out                    | _                 |

| CS               | Chip Select                 | Active High       |

| AFF              | FIFO RAM Almost Full Flag   | _                 |

| FF               | FIFO RAM Full Flag          | _                 |

| AEF              | FIFO RAM Almost Empty Flag  | _                 |

| EF               | FIFO RAM Empty Flag         | _                 |

| RPRST            | FIFO RAM Read Pointer Reset | _                 |

#### Table 2-6. EBR Signal Descriptions

1. Optional signals.

2. For dual port EBR primitives a trailing 'A' or 'B' in the signal name specifies the EBR port A or port B respectively.

3. For FIFO RAM mode primitive, a trailing 'R' or 'W' in the signal name specifies the FIFO read port or write port respectively.

4. For FIFO RAM mode primitive FULLI has the same function as CSW(2) and EMPTYI has the same function as CSR(2).

In FIFO mode, CLKW is the write port clock, CSW is the write port chip select, CLKR is the read port clock, CSR is the read port clock, CSR is the read port clock.

The EBR memory supports three forms of write behavior for single or dual port operation:

- 1. **Normal** Data on the output appears only during the read cycle. During a write cycle, the data (at the current address) does not appear on the output. This mode is supported for all data widths.

- 2. Write Through A copy of the input data appears at the output of the same port. This mode is supported for all data widths.

- 3. Read-Before-Write When new data is being written, the old contents of the address appears at the output.

#### **FIFO Configuration**

The FIFO has a write port with data-in, CEW, WE and CLKW signals. There is a separate read port with data-out, RCE, RE and CLKR signals. The FIFO internally generates Almost Full, Full, Almost Empty and Empty Flags. The Full and Almost Full flags are registered with CLKW. The Empty and Almost Empty flags are registered with CLKR. Table 2-7 shows the range of programming values for these flags.

#### Table 2-7. Programmable FIFO Flag Ranges

| Flag Name         | Programming Range                  |

|-------------------|------------------------------------|

| Full (FF)         | 1 to max (up to 2 <sup>N</sup> -1) |

| Almost Full (AF)  | 1 to Full-1                        |

| Almost Empty (AE) | 1 to Full-1                        |

| Empty (EF)        | 0                                  |

N = Address bit width.

The FIFO state machine supports two types of reset signals: RST and RPRST. The RST signal is a global reset that clears the contents of the FIFO by resetting the read/write pointer and puts the FIFO flags in their initial reset

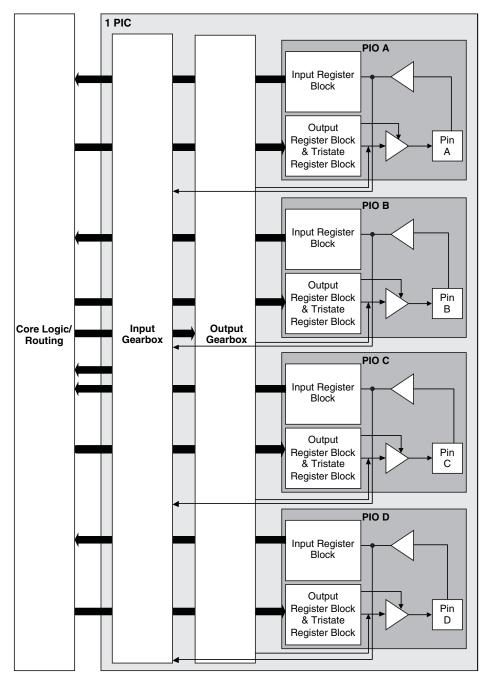

Figure 2-11. Group of Four Programmable I/O Cells

## PIO

The PIO contains three blocks: an input register block, output register block and tri-state register block. These blocks contain registers for operating in a variety of modes along with the necessary clock and selection logic.

| Table | 2-8. | ΡΙΟ | Signal | List |

|-------|------|-----|--------|------|

|       |      |     | e.ga.  |      |

| Pin Name | I/О Туре | Description                                         |

|----------|----------|-----------------------------------------------------|

| CE       | Input    | Clock Enable                                        |

| D        | Input    | Pin input from sysIO buffer.                        |

| INDD     | Output   | Register bypassed input.                            |

| INCK     | Output   | Clock input                                         |

| Q0       | Output   | DDR positive edge input                             |

| Q1       | Output   | Registered input/DDR negative edge input            |

| D0       | Input    | Output signal from the core (SDR and DDR)           |

| D1       | Input    | Output signal from the core (DDR)                   |

| TD       | Input    | Tri-state signal from the core                      |

| Q        | Output   | Data output signals to sysIO Buffer                 |

| TQ       | Output   | Tri-state output signals to sysIO Buffer            |

| SCLK     | Input    | System clock for input and output/tri-state blocks. |

| RST      | Input    | Local set reset signal                              |

### Input Register Block

The input register blocks for the PIOs on all edges contain delay elements and registers that can be used to condition high-speed interface signals before they are passed to the device core.

### Left, Top, Bottom Edges

Input signals are fed from the sysIO buffer to the input register block (as signal D). If desired, the input signal can bypass the register and delay elements and be used directly as a combinatorial signal (INDD), and a clock (INCK). If an input delay is desired, users can select a fixed delay. I/Os on the bottom edge also have a dynamic delay, DEL[4:0]. The delay, if selected, reduces input register hold time requirements when using a global clock. The input block allows two modes of operation. In single data rate (SDR) the data is registered with the system clock (SCLK) by one of the registers in the single data rate sync register block. In Generic DDR mode, two registers are used to sample the data on the positive and negative edges of the system clock (SCLK) signal, creating two data streams.

# sysIO Buffer

Each I/O is associated with a flexible buffer referred to as a sysIO buffer. These buffers are arranged around the periphery of the device in groups referred to as banks. The sysIO buffers allow users to implement a wide variety of standards that are found in today's systems including LVCMOS, TTL, PCI, LVDS, BLVDS, MLVDS and LVPECL.

Each bank is capable of supporting multiple I/O standards. In the MachXO3L/LF devices, single-ended output buffers, ratioed input buffers (LVTTL, LVCMOS and PCI), differential (LVDS) input buffers are powered using I/O supply voltage ( $V_{CCIO}$ ). Each sysIO bank has its own  $V_{CCIO}$ .

MachXO3L/LF devices contain three types of sysIO buffer pairs.

#### 1. Left and Right sysIO Buffer Pairs

The sysIO buffer pairs in the left and right banks of the device consist of two single-ended output drivers and two single-ended input buffers (for ratioed inputs such as LVCMOS and LVTTL). The I/O pairs on the left and right of the devices also have differential input buffers.

#### 2. Bottom sysIO Buffer Pairs

The sysIO buffer pairs in the bottom bank of the device consist of two single-ended output drivers and two single-ended input buffers (for ratioed inputs such as LVCMOS and LVTTL). The I/O pairs on the bottom also have differential input buffers. Only the I/Os on the bottom banks have programmable PCI clamps and differential input termination. The PCI clamp is enabled after  $V_{CC}$  and  $V_{CCIO}$  are at valid operating levels and the device has been configured.

#### 3. Top sysIO Buffer Pairs

The sysIO buffer pairs in the top bank of the device consist of two single-ended output drivers and two singleended input buffers (for ratioed inputs such as LVCMOS and LVTTL). The I/O pairs on the top also have differential I/O buffers. Half of the sysIO buffer pairs on the top edge have true differential outputs. The sysIO buffer pair comprising of the A and B PIOs in every PIC on the top edge have a differential output driver.

### Typical I/O Behavior During Power-up

The internal power-on-reset (POR) signal is deactivated when  $V_{CC}$  and  $V_{CCIO0}$  have reached  $V_{PORUP}$  level defined in the Power-On-Reset Voltage table in the DC and Switching Characteristics section of this data sheet. After the POR signal is deactivated, the FPGA core logic becomes active. It is the user's responsibility to ensure that all  $V_{CCIO}$  banks are active with valid input logic levels to properly control the output logic states of all the I/O banks that are critical to the application. The default configuration of the I/O pins in a blank device is tri-state with a weak pulldown to GND (some pins such as PROGRAMN and the JTAG pins have weak pull-up to  $V_{CCIO}$  as the default functionality). The I/O pins will maintain the blank configuration until  $V_{CC}$  and  $V_{CCIO}$  (for I/O banks containing configuration I/Os) have reached  $V_{PORUP}$  levels at which time the I/Os will take on the user-configured settings only after a proper download/configuration.

There are various ways a user can ensure that there are no spurious signals on critical outputs as the device powers up. These are discussed in more detail in TN1280, MachXO3 sysIO Usage Guide.

### **Supported Standards**

The MachXO3L/LF sysIO buffer supports both single-ended and differential standards. Single-ended standards can be further subdivided into LVCMOS, LVTTL, and PCI. The buffer supports the LVTTL, PCI, LVCMOS 1.2 V, 1.5 V, 1.8 V, 2.5 V, and 3.3 V standards. In the LVCMOS and LVTTL modes, the buffer has individually configurable options for drive strength, bus maintenance (weak pull-up, weak pull-down, bus-keeper latch or none) and open drain. BLVDS, MLVDS and LVPECL output emulation is supported on all devices. The MachXO3L/LF devices support on-chip LVDS output buffers on approximately 50% of the I/Os on the top bank. Differential receivers for LVDS, BLVDS, MLVDS and LVPECL are supported on all banks of MachXO3L/LF devices. PCI support is provided in the bottom bank of the MachXO3L/LF devices. Table 2-11 summarizes the I/O characteristics of the MachXO3L/LF PLDs.

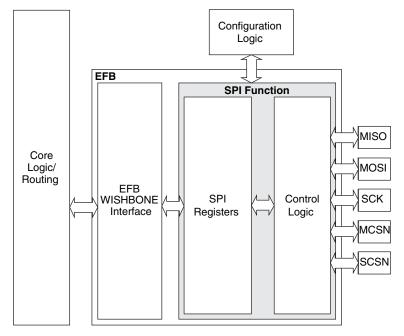

There are some limitations on the use of the hardened user SPI. These are defined in the following technical notes:

- TN1087, Minimizing System Interruption During Configuration Using TransFR Technology (Appendix B)

- TN1293, Using Hardened Control Functions in MachXO3 Devices

#### Figure 2-19. SPI Core Block Diagram

Table 2-15 describes the signals interfacing with the SPI cores.

Table 2-15. SPI Core Signal Description

| Signal Name | I/O | Master/Slave | Description                                                                                                                                                                               |

|-------------|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| spi_csn[0]  | 0   | Master       | SPI master chip-select output                                                                                                                                                             |

| spi_csn[17] | 0   | Master       | Additional SPI chip-select outputs (total up to eight slaves)                                                                                                                             |

| spi_scsn    | I   | Slave        | SPI slave chip-select input                                                                                                                                                               |

| spi_irq     | 0   | Master/Slave | Interrupt request                                                                                                                                                                         |

| spi_clk     | I/O | Master/Slave | SPI clock. Output in master mode. Input in slave mode.                                                                                                                                    |

| spi_miso    | I/O | Master/Slave | SPI data. Input in master mode. Output in slave mode.                                                                                                                                     |

| spi_mosi    | I/O | Master/Slave | SPI data. Output in master mode. Input in slave mode.                                                                                                                                     |

| sn          | I   | Slave        | Configuration Slave Chip Select (active low), dedicated for selecting the Con-<br>figuration Logic.                                                                                       |

| cfg_stdby   | 0   | Master/Slave | Stand-by signal – To be connected only to the power module of the MachXO3L/LF device. The signal is enabled only if the "Wakeup Enable" feature has been set within the EFB GUI, SPI Tab. |

| cfg_wake    | О   | Master/Slave | Wake-up signal – To be connected only to the power module of the MachXO3L/LF device. The signal is enabled only if the "Wakeup Enable" feature has been set within the EFB GUI, SPI Tab.  |

# MachXO3 Family Data Sheet DC and Switching Characteristics

#### February 2017

#### Advance Data Sheet DS1047

# Absolute Maximum Ratings<sup>1, 2, 3</sup>

|                                               | MachXO3L/LF E (1.2 V) | MachXO3L/LF C (2.5 V/3.3 V) |

|-----------------------------------------------|-----------------------|-----------------------------|

| Supply Voltage V <sub>CC</sub>                | –0.5 V to 1.32 V      | 0.5 V to 3.75 V             |

| Output Supply Voltage V <sub>CCIO</sub>       | –0.5 V to 3.75 V      | –0.5 V to 3.75 V            |

| I/O Tri-state Voltage Applied <sup>4, 5</sup> | –0.5 V to 3.75 V      | –0.5 V to 3.75 V            |

| Dedicated Input Voltage Applied <sup>4</sup>  | –0.5 V to 3.75 V      | –0.5 V to 3.75 V            |

| Storage Temperature (Ambient)                 | –55 °C to 125 °C      | –55 °C to 125 °C            |

| Junction Temperature (T <sub>J</sub> )        | –40 °C to 125 °C      | –40 °C to 125 °C            |

1. Stress above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

2. Compliance with the Lattice Thermal Management document is required.

3. All voltages referenced to GND.

4. Overshoot and undershoot of -2 V to (V<sub>IHMAX</sub> + 2) volts is permitted for a duration of <20 ns.

5. The dual function  $I^2C$  pins SCL and SDA are limited to -0.25 V to 3.75 V or to -0.3 V with a duration of <20 ns.

# **Recommended Operating Conditions**<sup>1</sup>

| Symbol                               | Symbol Parameter                            |       | Max.  | Units |

|--------------------------------------|---------------------------------------------|-------|-------|-------|

| V 1                                  | Core Supply Voltage for 1.2 V Devices       | 1.14  | 1.26  | V     |

| V <sub>CC</sub> <sup>1</sup>         | Core Supply Voltage for 2.5 V/3.3 V Devices | 2.375 | 3.465 | V     |

| V <sub>CCIO</sub> <sup>1, 2, 3</sup> | I/O Driver Supply Voltage                   |       | 3.465 | V     |

| t <sub>JCOM</sub>                    | Junction Temperature Commercial Operation   |       | 85    | °C    |

| t <sub>JIND</sub>                    | Junction Temperature Industrial Operation   | -40   | 100   | °C    |

1. Like power supplies must be tied together. For example, if V<sub>CCIO</sub> and V<sub>CC</sub> are both the same voltage, they must also be the same supply.

2. See recommended voltages by I/O standard in subsequent table.

3. V<sub>CCIO</sub> pins of unused I/O banks should be connected to the V<sub>CC</sub> power supply on boards.

# **Power Supply Ramp Rates**<sup>1</sup>

| Symbol            | Parameter                                       | Min. | Тур. | Max. | Units |

|-------------------|-------------------------------------------------|------|------|------|-------|

| t <sub>RAMP</sub> | Power supply ramp rates for all power supplies. | 0.01 |      | 100  | V/ms  |

1. Assumes monotonic ramp rates.

<sup>© 2017</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# sysIO Single-Ended DC Electrical Characteristics<sup>1, 2</sup>

| Input/Output        | V                     | IL                    | V                     | н        | V <sub>OL</sub> Max. | V <sub>OH</sub> Min.    | I <sub>OL</sub> Max. <sup>4</sup> | I <sub>OH</sub> Max.⁴ |

|---------------------|-----------------------|-----------------------|-----------------------|----------|----------------------|-------------------------|-----------------------------------|-----------------------|

| Standard            | Min. (V) <sup>3</sup> | Max. (V)              | Min. (V)              | Max. (V) | (V)                  | (V)                     | (mA)                              | (mA)                  |

|                     |                       |                       |                       |          |                      |                         | 4                                 | -4                    |

|                     |                       |                       |                       |          | 0.4                  | V <sub>CCIO</sub> - 0.4 | 8                                 | -8                    |

| LVCMOS 3.3<br>LVTTL | -0.3                  | 0.8                   | 2.0                   | 3.6      | 0.4                  | VCCIO - 0.4             | 12                                | -12                   |

|                     |                       |                       |                       |          |                      |                         | 16                                | -16                   |

|                     |                       |                       |                       |          | 0.2                  | V <sub>CCIO</sub> - 0.2 | 0.1                               | -0.1                  |

|                     |                       |                       |                       |          |                      |                         | 4                                 | -4                    |

|                     |                       |                       |                       |          | 0.4                  | V 0.4                   | 8                                 | -8                    |

| LVCMOS 2.5          | -0.3                  | 0.7                   | 1.7                   | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4 | 12                                | -12                   |

|                     |                       |                       |                       |          |                      |                         | 16                                | -16                   |

|                     |                       |                       |                       |          | 0.2                  | V <sub>CCIO</sub> - 0.2 | 0.1                               | -0.1                  |

|                     |                       |                       |                       |          |                      |                         | 4                                 | -4                    |

|                     | 0.0                   | 0.051/                | 0.051/                | 0.0      | 0.4                  | V <sub>CCIO</sub> - 0.4 | 8                                 | -8                    |

| LVCMOS 1.8          | -0.3                  | 0.35V <sub>CCIO</sub> | 0.65V <sub>CCIO</sub> | 3.6      |                      |                         | 12                                | -12                   |

|                     |                       |                       |                       |          | 0.2                  | V <sub>CCIO</sub> - 0.2 | 0.1                               | -0.1                  |

|                     |                       |                       |                       |          | 0.4                  | V 04                    | 4                                 | -4                    |

| LVCMOS 1.5          | -0.3                  | 0.35V <sub>CCIO</sub> | 0.65V <sub>CCIO</sub> | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4 | 8                                 | -8                    |

|                     |                       |                       |                       |          | 0.2                  | V <sub>CCIO</sub> - 0.2 | 0.1                               | -0.1                  |

|                     |                       |                       | 0.65V <sub>CCIO</sub> |          | 0.4                  | V 04                    | 4                                 | -2                    |

| LVCMOS 1.2          | -0.3                  | 0.35V <sub>CCIO</sub> |                       | 3.6      | 0.4                  | V <sub>CCIO</sub> - 0.4 | 8                                 | -6                    |

|                     |                       |                       |                       |          | 0.2                  | V <sub>CCIO</sub> - 0.2 | 0.1                               | -0.1                  |

| LVCMOS25R33         | -0.3                  | VREF-0.1              | VREF+0.1              | 3.6      | NA                   | NA                      | NA                                | NA                    |

| LVCMOS18R33         | -0.3                  | VREF-0.1              | VREF+0.1              | 3.6      | NA                   | NA                      | NA                                | NA                    |

| LVCMOS18R25         | -0.3                  | VREF-0.1              | VREF+0.1              | 3.6      | NA                   | NA                      | NA                                | NA                    |

| LVCMOS15R33         | -0.3                  | VREF-0.1              | VREF+0.1              | 3.6      | NA                   | NA                      | NA                                | NA                    |

| LVCMOS15R25         | -0.3                  | VREF-0.1              | VREF+0.1              | 3.6      | NA                   | NA                      | NA                                | NA                    |

| LVCMOS12R33         | -0.3                  | VREF-0.1              | VREF+0.1              | 3.6      | 0.40                 | NA Open<br>Drain        | 24, 16, 12,<br>8, 4               | NA Open<br>Drain      |

| LVCMOS12R25         | -0.3                  | VREF-0.1              | VREF+0.1              | 3.6      | 0.40                 | NA Open<br>Drain        | 16, 12, 8, 4                      | NA Open<br>Drain      |

| LVCMOS10R33         | -0.3                  | VREF-0.1              | VREF+0.1              | 3.6      | 0.40                 | NA Open<br>Drain        | 24, 16, 12,<br>8, 4               | NA Open<br>Drain      |

| LVCMOS10R25         | -0.3                  | VREF-0.1              | VREF+0.1              | 3.6      | 0.40                 | NA Open<br>Drain        | 16, 12, 8, 4                      | NA Open<br>Drain      |

|                     |                       |                       |                       |          |                      |                         |                                   |                       |

MachXO3L/LF devices allow LVCMOS inputs to be placed in I/O banks where V<sub>CCIO</sub> is different from what is specified in the applicable JEDEC specification. This is referred to as a ratioed input buffer. In a majority of cases this operation follows or exceeds the applicable JEDEC specification. The cases where MachXO3L/LF devices do not meet the relevant JEDEC specification are documented in the table below.

2. MachXO3L/LF devices allow for LVCMOS referenced I/Os which follow applicable JEDEC specifications. For more details about mixed mode operation please refer to please refer to TN1280, MachXO3 sysIO Usage Guide.

3. The dual function I<sup>2</sup>C pins SCL and SDA are limited to a  $V_{IL}$  min of -0.25 V or to -0.3 V with a duration of <10 ns.

4. For electromigration, the average DC current sourced or sinked by I/O pads between two consecutive VCCIO or GND pad connections, or between the last VCCIO or GND in an I/O bank and the end of an I/O bank, as shown in the Logic Signal Connections table (also shown as I/O grouping) shall not exceed a maximum of n \* 8 mA. "n" is the number of I/O pads between the two consecutive bank VCCIO or GND connections or between the last VCCIO and GND in a bank and the end of a bank. IO Grouping can be found in the Data Sheet Pin Tables, which can also be generated from the Lattice Diamond software.

# sysIO Differential Electrical Characteristics

The LVDS differential output buffers are available on the top side of the MachXO3L/LF PLD family.

### LVDS

| Parameter<br>Symbol               | Parameter Description                                      | Test Conditions                                                | Min.  | Тур.  | Max.  | Units |

|-----------------------------------|------------------------------------------------------------|----------------------------------------------------------------|-------|-------|-------|-------|

| V V                               | Input Voltage                                              | V <sub>CCIO</sub> = 3.3 V                                      | 0     | _     | 2.605 | V     |

| V <sub>INP</sub> V <sub>INM</sub> |                                                            | $V_{CCIO} = 2.5 V$                                             | 0     | _     | 2.05  | V     |

| V <sub>THD</sub>                  | Differential Input Threshold                               |                                                                | ±100  | _     |       | mV    |

| V                                 | Input Common Mode Voltage                                  | V <sub>CCIO</sub> = 3.3 V                                      | 0.05  |       | 2.6   | V     |

| V <sub>CM</sub>                   | Input Common Mode Voltage                                  | $V_{CCIO} = 2.5 V$                                             | 0.05  |       | 2.0   | V     |

| I <sub>IN</sub>                   | Input current                                              | Power on                                                       | _     | _     | ±10   | μA    |

| V <sub>OH</sub>                   | Output high voltage for V <sub>OP</sub> or V <sub>OM</sub> | R <sub>T</sub> = 100 Ohm                                       | _     | 1.375 | —     | V     |

| V <sub>OL</sub>                   | Output low voltage for V <sub>OP</sub> or V <sub>OM</sub>  | R <sub>T</sub> = 100 Ohm                                       | 0.90  | 1.025 | —     | V     |

| V <sub>OD</sub>                   | Output voltage differential                                | (V <sub>OP</sub> - V <sub>OM</sub> ), R <sub>T</sub> = 100 Ohm | 250   | 350   | 450   | mV    |

| ΔV <sub>OD</sub>                  | Change in V <sub>OD</sub> between high and low             |                                                                | _     | _     | 50    | mV    |

| V <sub>OS</sub>                   | Output voltage offset                                      | $(V_{OP} - V_{OM})/2, R_T = 100 \text{ Ohm}$                   | 1.125 | 1.20  | 1.395 | V     |

| ΔV <sub>OS</sub>                  | Change in V <sub>OS</sub> between H and L                  |                                                                | _     | _     | 50    | mV    |

| I <sub>OSD</sub>                  | Output short circuit current                               | V <sub>OD</sub> = 0 V driver outputs shorted                   | _     | —     | 24    | mA    |

### **Over Recommended Operating Conditions**

### BLVDS

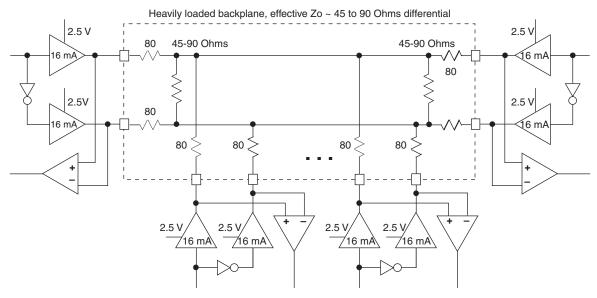

The MachXO3L/LF family supports the BLVDS standard through emulation. The output is emulated using complementary LVCMOS outputs in conjunction with resistors across the driver outputs. The input standard is supported by the LVDS differential input buffer. BLVDS is intended for use when multi-drop and bi-directional multi-point differential signaling is required. The scheme shown in Figure 3-2 is one possible solution for bi-directional multi-point differential signals.

#### Figure 3-2. BLVDS Multi-point Output Example

#### Table 3-2. BLVDS DC Conditions<sup>1</sup>

| <b>Over Recommended</b> | Operating | Conditions  |

|-------------------------|-----------|-------------|

|                         | oporating | 00110110110 |

|                     |                             | Non     |         |       |

|---------------------|-----------------------------|---------|---------|-------|

| Symbol              | Description                 | Zo = 45 | Zo = 90 | Units |

| Z <sub>OUT</sub>    | Output impedance            | 20      | 20      | Ohms  |

| R <sub>S</sub>      | Driver series resistance    | 80      | 80      | Ohms  |

| R <sub>TLEFT</sub>  | Left end termination        | 45      | 90      | Ohms  |

| R <sub>TRIGHT</sub> | Right end termination       | 45      | 90      | Ohms  |

| V <sub>OH</sub>     | Output high voltage         | 1.376   | 1.480   | V     |

| V <sub>OL</sub>     | Output low voltage          | 1.124   | 1.020   | V     |

| V <sub>OD</sub>     | Output differential voltage | 0.253   | 0.459   | V     |

| V <sub>CM</sub>     | Output common mode voltage  | 1.250   | 1.250   | V     |

| I <sub>DC</sub>     | DC output current           | 11.236  | 10.204  | mA    |

1. For input buffer, see LVDS table.

# MachXO3L/LF External Switching Characteristics – C/E Devices<sup>1, 2, 3, 4, 5, 6, 10</sup>

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -6                      |       |      |       | -5       |       |  |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------|------|-------|----------|-------|--|

| Parameter                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Device                  | Min.  | Max. | Min.  | Max.     | Units |  |

| Clocks                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | I                       |       |      |       |          |       |  |

| Primary Clo                        | ocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                         |       |      |       |          |       |  |

| f <sub>MAX_PRI</sub> <sup>7</sup>  | Frequency for Primary Clock Tree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | All MachXO3L/LF devices |       | 388  | —     | 323      | MHz   |  |

| t <sub>W_PRI</sub>                 | Clock Pulse Width for Primary Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | All MachXO3L/LF devices | 0.5   | _    | 0.6   |          | ns    |  |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MachXO3L/LF-1300        | _     | 867  | —     | 897      | ps    |  |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MachXO3L/LF-2100        |       | 867  | _     | 897      | ps    |  |

| t <sub>SKEW_PRI</sub>              | Primary Clock Skew Within a Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | MachXO3L/LF-4300        |       | 865  | _     | 892      | ps    |  |

| 0.12.1                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MachXO3L/LF-6900        |       | 902  | _     | 942      | ps    |  |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MachXO3L/LF-9400        | _     | 908  | _     | 950      | ps    |  |

| Edge Clock                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                         |       |      |       |          |       |  |

| f <sub>MAX_EDGE</sub> <sup>7</sup> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MachXO3L/LF             | _     | 400  | _     | 333      | MHz   |  |

| _                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                         |       |      |       |          |       |  |

| t <sub>PD</sub>                    | Best case propagation delay through one<br>LUT-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | All MachXO3L/LF devices | _     | 6.72 | _     | 6.96     | ns    |  |

| General I/O                        | Pin Parameters (Using Primary Clock with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | out PLL)                |       | I    |       |          | 1     |  |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MachXO3L/LF-1300        | —     | 7.46 | _     | 7.66     | ns    |  |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MachXO3L/LF-2100        | _     | 7.46 | —     | 7.66     | ns    |  |

| t <sub>CO</sub> Clock to Out       | Clock to Output - PIO Output Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | MachXO3L/LF-4300        | _     | 7.51 | _     | 7.71     | ns    |  |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MachXO3L/LF-6900        | _     | 7.54 | _     | 7.75     | ns    |  |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MachXO3L/LF-9400        | _     | 7.53 | _     | 7.83     | ns    |  |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MachXO3L/LF-1300        | -0.20 |      | -0.20 | —        | ns    |  |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MachXO3L/LF-2100        | -0.20 |      | -0.20 |          | ns    |  |

| t <sub>SU</sub>                    | Clock to Data Setup - PIO Input Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | MachXO3L/LF-4300        | -0.23 |      | -0.23 |          | ns    |  |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MachXO3L/LF-6900        | -0.23 | _    | -0.23 |          | ns    |  |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MachXO3L/LF-9400        | -0.24 | —    | -0.24 | —        | ns    |  |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MachXO3L/LF-1300        | 1.89  |      | 2.13  |          | ns    |  |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MachXO3L/LF-2100        | 1.89  |      | 2.13  |          | ns    |  |

| t <sub>H</sub>                     | Clock to Data Hold - PIO Input Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | MachXO3L/LF-4300        | 1.94  | _    | 2.18  | _        | ns    |  |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MachXO3L/LF-6900        | 1.98  |      | 2.23  |          | ns    |  |

|                                    | Image Clock         MachXO3L/LF-9400         908            see Clock         MachXO3L/LF          400            -LUT-Pin Propagation Delay         Best case propagation delay through one<br>LUT-4         All MachXO3L/LF devices          6.72            heral I/O Pin Parameters (Using Primary Clock without PLL)          6.72            Clock to Output - PIO Output Register         MachXO3L/LF-1300          7.46            MachXO3L/LF-4300          7.54             MachXO3L/LF-4300          7.53             MachXO3L/LF-9400          7.53          -         -0.20           MachXO3L/LF-4300          7.53          -         -0.20         -         -0.20         -         -0.20           MachXO3L/LF-4300         -0.23          -0.23         -         -0.23         -         -0.23           MachXO3L/LF-4300         -0.24         -         -0.24         -         -0.24           MachXO3L/LF-4300         -0.23         -         2.13         MachXO3L/LF-300         1.89         -         2.13< |                         | ns    |      |       |          |       |  |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MachXO3L/LF-1300        |       |      |       |          | ns    |  |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                         |       |      | 1.76  |          | ns    |  |

| t <sub>SU_DEL</sub>                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                         |       |      |       | _        | ns    |  |

| 00_DEE                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                         | 1.53  |      |       | _        | ns    |  |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                         |       |      |       | <u> </u> | ns    |  |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                         |       |      |       | _        | ns    |  |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                         |       |      |       | _        | ns    |  |