Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 13                                                                              |

| Program Memory Size        | 6KB (2K x 24)                                                                   |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 256 x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

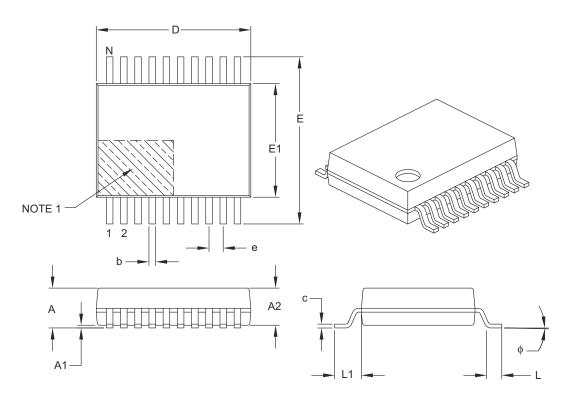

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 18-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs001-e-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

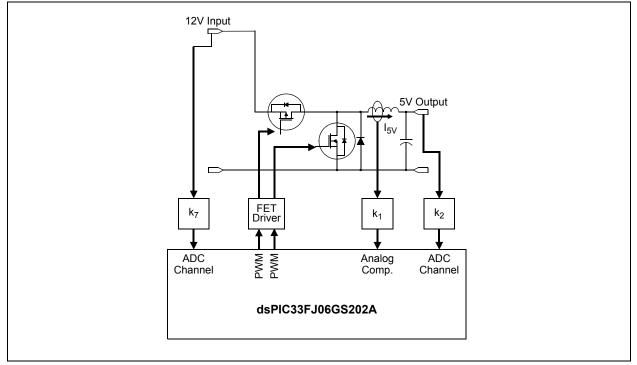

### FIGURE 2-6: SINGLE-PHASE SYNCHRONOUS BUCK CONVERTER

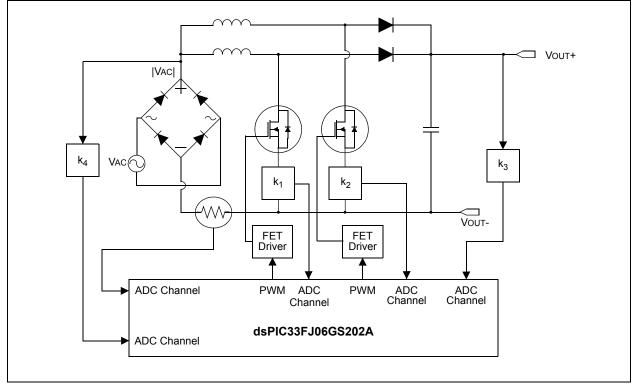

#### FIGURE 2-7: INTERLEAVED PFC

#### 4.2.5 X AND Y DATA SPACES

The core has two data spaces, X and Y. These data spaces can be considered either separate (for some DSP instructions), or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms, such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X data space is used by all instructions and supports all addressing modes. X data space has separate read and write data buses. The X read data bus is the read data path for all instructions that view data space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y data space is used in concert with the X data space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y data spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X data space.

All data memory writes, included in DSP instructions, view data space as combined X and Y address space. The boundary between the X and Y data spaces is device-dependent and is not user-programmable.

All Effective Addresses are 16 bits wide and point to bytes within the data space. Therefore, the data space address range is 64 Kbytes, or 32K words, though the implemented memory locations vary by device.

# 6.5 External Reset (EXTR)

The external Reset is generated by driving the MCLR pin low. The MCLR pin is a Schmitt trigger input with an additional glitch filter. Reset pulses that are longer than the minimum pulse width will generate a Reset. Refer to **Section 25.0 "Electrical Characteristics"** for minimum pulse width specifications. The external Reset (MCLR) pin (EXTR) bit in the Reset Control (RCON) register is set to indicate the MCLR Reset.

#### 6.5.1 EXTERNAL SUPERVISORY CIRCUIT

Many systems have external supervisory circuits that generate Reset signals to reset multiple devices in the system. This external Reset signal can be directly connected to the MCLR pin to reset the device when the rest of the system is reset.

#### 6.5.2 INTERNAL SUPERVISORY CIRCUIT

When using the internal power supervisory circuit to reset the device, the external Reset pin (MCLR) should be tied directly or resistively to VDD. In this case, the MCLR pin will not be used to generate a Reset. The external Reset pin (MCLR) does not have an internal pull-up and must not be left unconnected.

#### 6.6 Software RESET Instruction (SWR)

Whenever the RESET instruction is executed, the device will assert SYSRST, placing the device in a special Reset state. This Reset state will not re-initialize the clock. The clock source in effect prior to the RESET instruction will still remain. SYSRST is released at the next instruction cycle and the Reset vector fetch will commence.

The Software Reset (SWR) flag (instruction) in the Reset Control register (RCON<6>) is set to indicate the software Reset.

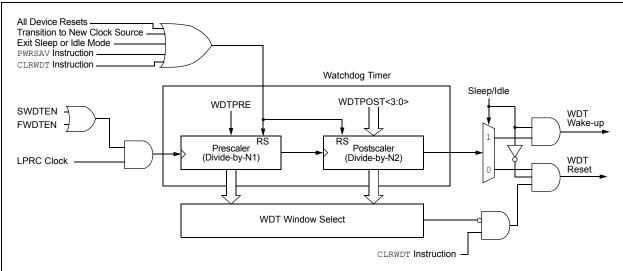

# 6.7 Watchdog Time-out Reset (WDTO)

Whenever a Watchdog Timer time-out occurs, the device will asynchronously assert SYSRST. The clock source will remain unchanged. A WDT time-out during Sleep or Idle mode will wake-up the processor, but will not reset the processor.

The Watchdog Timer Time-out (WDTO) flag in the Reset Control (RCON<4>) register is set to indicate the Watchdog Timer Reset. Refer to **Section 22.4 "Watchdog Timer (WDT)**" for more information on Watchdog Reset.

# 6.8 Trap Conflict Reset

If a lower priority hard trap occurs, while a higher priority trap is being processed, a hard Trap Conflict Reset occurs. The hard traps include exceptions of Priority Level 13 through Level 15, inclusive. The address error (Level 13) and oscillator error (Level 14) traps fall into this category.

The Trap Reset (TRAPR) flag in the Reset Control register (RCON<15>) is set to indicate the Trap Conflict Reset. Refer to **Section 7.0 "Interrupt Controller"** for more information on Trap Conflict Resets.

# 6.9 Illegal Condition Device Reset

An illegal condition device Reset occurs due to the following sources:

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

The illegal opcode or Uninitialized W Access Reset (IOPUWR) flag in the Reset Control register (RCON<14>) is set to indicate the illegal condition device Reset.

### 6.9.1 ILLEGAL OPCODE RESET

A device Reset is generated if the device attempts to execute an illegal opcode value that is fetched from program memory.

The Illegal Opcode Reset function can prevent the device from executing program memory sections that are used to store constant data. To take advantage of the Illegal Opcode Reset, use only the lower 16 bits of each program memory section to store the data values. The upper 8 bits should be programmed with 0x3F, which is an illegal opcode value.

#### 6.9.2 UNINITIALIZED W REGISTER RESET

Any attempt to use the uninitialized W register as an Address Pointer will Reset the device. The W register array (with the exception of W15) is cleared during all Resets and is considered uninitialized until written to.

| <b>REGISTER 7</b>                            | -9: IFS5:     | INTERRUPT        | FLAG STAT                    | US REGISTI       | ER 5             |                 |        |

|----------------------------------------------|---------------|------------------|------------------------------|------------------|------------------|-----------------|--------|

| R/W-0                                        | R/W-0         | U-0              | U-0                          | U-0              | U-0              | U-0             | U-0    |

| PWM2IF <sup>(1)</sup>                        | PWM1IF        |                  |                              | _                |                  |                 |        |

| bit 15                                       |               |                  |                              |                  |                  |                 | bit 8  |

| U-0                                          | U-0           | U-0              | U-0                          | U-0              | U-0              | U-0             | R/W-0  |

| _                                            |               |                  | _                            | _                | _                | _               | JTAGIF |

| bit 7                                        |               |                  |                              |                  |                  |                 | bit 0  |

| Logond:                                      |               |                  |                              |                  |                  |                 |        |

| Legend:<br>R = Readable bit W = Writable bit |               |                  |                              | l I = l Inimplei | mented bit, read | l as '0'        |        |

| -n = Value at F                              |               | '1' = Bit is set |                              | '0' = Bit is cle |                  | x = Bit is unkr | nown   |

|                                              |               |                  |                              |                  |                  |                 |        |

| bit 15                                       | PWM2IF: PV    | VM2 Interrupt F  | lag Status bit <sup>(*</sup> | 1)               |                  |                 |        |

|                                              |               | request has oc   |                              |                  |                  |                 |        |

|                                              | 0 = Interrupt | request has not  | occurred                     |                  |                  |                 |        |

| bit 14                                       | PWM1IF: PV    | VM1 Interrupt F  | ag Status bit                |                  |                  |                 |        |

|                                              | 1 = Interrupt | request has occ  | curred                       |                  |                  |                 |        |

|                                              | 0 = Interrupt | request has not  | t occurred                   |                  |                  |                 |        |

| bit 13-1                                     | Unimplemer    | nted: Read as '  | 0'                           |                  |                  |                 |        |

| bit 0                                        | JTAGIF: JTA   | G Interrupt Flag | g Status bit                 |                  |                  |                 |        |

|                                              |               | request has oc   | -                            |                  |                  |                 |        |

|                                              | •             | request has not  |                              |                  |                  |                 |        |

|                                              |               |                  |                              |                  |                  |                 |        |

Note 1: This bit is not implemented in dsPIC33FJ06GS001/101A devices.

| <b>REGISTER 7</b>    | REGISTER 7-17: IEC6: INTERRUPT ENABLE CONTROL REGISTER 6             |                                                                                                                |                                       |                  |                  |                       |       |  |  |  |  |  |

|----------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------|------------------|-----------------------|-------|--|--|--|--|--|

| R/W-0                | R/W-0                                                                | U-0                                                                                                            | U-0                                   | U-0              | U-0              | U-0                   | U-0   |  |  |  |  |  |

| ADCP1IE              | ADCP0IE                                                              |                                                                                                                | —                                     | —                | —                | —                     | _     |  |  |  |  |  |

| bit 15               |                                                                      |                                                                                                                |                                       |                  |                  |                       | bit 8 |  |  |  |  |  |

|                      |                                                                      |                                                                                                                |                                       |                  |                  |                       |       |  |  |  |  |  |

| R/W-0                | U-0                                                                  | U-0                                                                                                            | U-0                                   | U-0              | U-0              | R/W-0                 | U-0   |  |  |  |  |  |

| AC2IE <sup>(1)</sup> |                                                                      |                                                                                                                | —                                     | —                | —                | PWM4IE <sup>(2)</sup> | —     |  |  |  |  |  |

| bit 7                |                                                                      |                                                                                                                |                                       |                  |                  |                       | bit 0 |  |  |  |  |  |

|                      |                                                                      |                                                                                                                |                                       |                  |                  |                       |       |  |  |  |  |  |

| Legend:              |                                                                      |                                                                                                                |                                       |                  |                  |                       |       |  |  |  |  |  |

| R = Readable         | bit                                                                  | W = Writable                                                                                                   | bit                                   | U = Unimpler     | mented bit, read | l as '0'              |       |  |  |  |  |  |

| -n = Value at F      | POR                                                                  | '1' = Bit is set                                                                                               |                                       | '0' = Bit is cle | ared             | x = Bit is unkno      | wn    |  |  |  |  |  |

| bit 14               | 1 = Interrupt r<br>0 = Interrupt r<br>ADCP0IE: AE<br>1 = Interrupt r | DC Pair 1 Conv<br>request is enab<br>request is not e<br>DC Pair 0 Conv<br>request is enab<br>request is not e | led<br>nabled<br>ersion Done I<br>led | ·                |                  |                       |       |  |  |  |  |  |

| bit 13-8             | Unimplemen                                                           | ted: Read as '                                                                                                 | C                                     |                  |                  |                       |       |  |  |  |  |  |

| bit 7                |                                                                      |                                                                                                                |                                       |                  |                  |                       |       |  |  |  |  |  |

| bit 6-2              | Unimplemen                                                           | ted: Read as '                                                                                                 | )'                                    |                  |                  |                       |       |  |  |  |  |  |

| bit 1                | PWM4IE: PW                                                           | /M4 Interrupt E                                                                                                | nable bit <sup>(2)</sup>              |                  |                  |                       |       |  |  |  |  |  |

|                      |                                                                      | equest is enab<br>equest is not e                                                                              |                                       |                  |                  |                       |       |  |  |  |  |  |

| bit 0                | Unimplemen                                                           | ted: Read as '                                                                                                 | כי                                    |                  |                  |                       |       |  |  |  |  |  |

Note 1: This bit is not implemented in dsPIC33FJ06GS101A/102A devices.

2: This bit is not implemented in dsPIC33FJ06GS102A/202A devices.

| U-0          | R/W-1                   | R/W-0                                                        | R/W-0           | U-0               | U-0              | U-0                | U-0   |

|--------------|-------------------------|--------------------------------------------------------------|-----------------|-------------------|------------------|--------------------|-------|

| _            |                         | T2IP<2:0>                                                    |                 |                   |                  | —                  |       |

| bit 15       | 15                      |                                                              |                 |                   |                  |                    | bit 8 |

|              |                         |                                                              |                 |                   |                  |                    |       |

| U-0          | U-0                     | U-0                                                          | U-0             | U-0               | U-0              | U-0                | U-0   |

| —            | _                       |                                                              | —               | —                 | —                |                    | _     |

| bit 7        |                         |                                                              |                 |                   |                  |                    | bit 0 |

|              |                         |                                                              |                 |                   |                  |                    |       |

| Legend:      |                         |                                                              |                 |                   |                  |                    |       |

| R = Readab   | le bit                  | W = Writable                                                 | bit             | U = Unimplem      | nented bit, read | d as '0'           |       |

| -n = Value a | t POR                   | '1' = Bit is set                                             |                 | '0' = Bit is clea | ared             | x = Bit is unknown |       |

| 1.11.4 F     |                         |                                                              | - 1             |                   |                  |                    |       |

| bit 15       | -                       | nted: Read as '                                              |                 |                   |                  |                    |       |

| bit 14-12    | T2IP<2:0>: ⁻            | Fimer2 Interrupt                                             | Priority bits   |                   |                  |                    |       |

|              |                         |                                                              | high oct priori | ty interrupt)     |                  |                    |       |

|              | 111 = Interru           | ipt is Priority 7 (                                          | nignest phon    | ty interrupt)     |                  |                    |       |

|              | 111 = Interru<br>•      | ipt is Priority 7 (                                          | nignest priori  | ty interrupt)     |                  |                    |       |

|              | 111 = Interru<br>•<br>• | ipt is Priority 7 (                                          | nignest priori  | ty interrupt)     |                  |                    |       |

|              | •<br>•<br>001 = Interru | ipt is Priority 7(<br>ipt is Priority 1<br>ipt source is dis |                 | ty interrupt)     |                  |                    |       |

| U-0                         | U-0                                                                                          | U-0                                                                                                           | U-0                                                | U-0                                             | U-0              | U-0            | U-0   |  |

|-----------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------|------------------|----------------|-------|--|

| _                           |                                                                                              |                                                                                                               | _                                                  | _                                               |                  | _              | _     |  |

| bit 15                      |                                                                                              |                                                                                                               |                                                    |                                                 |                  |                | bit 8 |  |

| U-0                         | R/W-1                                                                                        | R/W-0                                                                                                         | R/W-0                                              | U-0                                             | R/W-1            | R/W-0          | R/W-0 |  |

| _                           | ADIP<2:0> — U1TXIP<2:0> <sup>(1)</sup>                                                       |                                                                                                               |                                                    |                                                 |                  |                |       |  |

| bit 7                       |                                                                                              |                                                                                                               |                                                    |                                                 | I                |                | bit 0 |  |

|                             |                                                                                              |                                                                                                               |                                                    |                                                 |                  |                |       |  |

| Legend:                     |                                                                                              |                                                                                                               |                                                    |                                                 |                  |                |       |  |

| R = Readabl                 | e bit                                                                                        | W = Writable                                                                                                  | bit                                                | U = Unimpler                                    | mented bit, read | d as '0'       |       |  |

| -n = Value at               | POR                                                                                          | '1' = Bit is set                                                                                              | 1                                                  | '0' = Bit is cle                                | ared             | x = Bit is unk | nown  |  |

| bit 6-4<br>bit 3<br>bit 2-0 | 111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>U1TXIP<2:0<br>111 = Interru | ADC1 Convers<br>upt is Priority 1<br>upt source is dis<br>nted: Read as<br>>: UART1 Tran<br>upt is Priority 1 | (highest priori<br>sabled<br>0'<br>smitter Interru | ty interrupt)<br>upt Priority bits <sup>(</sup> |                  |                |       |  |

Note 1: These bits are not implemented in the dsPIC33FJ06GS001 device.

| REGISTER 7-30: IPC24: INTERRUPT PRIORITY CONTROL REGISTER 24 |                       |                    |                 |                     |                  |                 |       |  |  |  |

|--------------------------------------------------------------|-----------------------|--------------------|-----------------|---------------------|------------------|-----------------|-------|--|--|--|

| U-0                                                          | U-0                   | U-0                | U-0             | U-0                 | U-0              | U-0             | U-0   |  |  |  |

|                                                              | —                     | —                  | _               | —                   | —                | —               | _     |  |  |  |

| bit 15                                                       |                       |                    |                 |                     |                  |                 | bit 8 |  |  |  |

|                                                              |                       |                    |                 |                     |                  |                 |       |  |  |  |

| U-0                                                          | R/W-1                 | R/W-1 R/W-0 R/W-0  |                 |                     | U-0              | U-0             | U-0   |  |  |  |

| _                                                            | PWM4IP <sup>(1)</sup> |                    |                 |                     | —                | —               |       |  |  |  |

| bit 7                                                        |                       |                    |                 |                     |                  |                 | bit 0 |  |  |  |

|                                                              |                       |                    |                 |                     |                  |                 |       |  |  |  |

| Legend:                                                      |                       |                    |                 |                     |                  |                 |       |  |  |  |

| R = Readable                                                 | bit                   | W = Writable       | bit             | U = Unimpler        | mented bit, read | l as '0'        |       |  |  |  |

| -n = Value at F                                              | OR                    | '1' = Bit is set   |                 | '0' = Bit is cle    | ared             | x = Bit is unkr | iown  |  |  |  |

|                                                              |                       |                    |                 |                     |                  |                 |       |  |  |  |

| bit 15-7                                                     | -                     | ted: Read as '     |                 |                     |                  |                 |       |  |  |  |

| bit 6-4                                                      | PWM4IP<2:0            | >: PWM4 Inter      | rupt Priority b | oits <sup>(1)</sup> |                  |                 |       |  |  |  |

|                                                              | 111 = Interrup        | ot is Priority 7 ( | highest priori  | ty)                 |                  |                 |       |  |  |  |

|                                                              | •                     |                    |                 |                     |                  |                 |       |  |  |  |

|                                                              | •                     |                    |                 |                     |                  |                 |       |  |  |  |

|                                                              | •                     |                    |                 |                     |                  |                 |       |  |  |  |

|                                                              | 001 = Interrup        | ot is Priority 1   |                 |                     |                  |                 |       |  |  |  |

|                                                              |                       | ot source is dis   | abled           |                     |                  |                 |       |  |  |  |

|                                                              |                       |                    |                 |                     |                  |                 |       |  |  |  |

#### Note 1: These bits are not implemented in dsPIC33FJ06GS102A/202A devices.

### **REGISTER 7-35: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER**

| U-0           | U-0                | U-0                                        | U-0            | R-0                                     | R-0          | R-0       | R-0   |  |

|---------------|--------------------|--------------------------------------------|----------------|-----------------------------------------|--------------|-----------|-------|--|

| —             | —                  | —                                          | —              |                                         | ILI          | R<3:0>    |       |  |

| bit 15        |                    |                                            |                |                                         |              |           | bit 8 |  |

|               |                    |                                            |                |                                         |              |           |       |  |

| U-0           | R-0                | R-0                                        | R-0            | R-0                                     | R-0          | R-0       | R-0   |  |

| —             |                    |                                            |                | VECNUM<6:0>                             |              |           |       |  |

| bit 7         |                    |                                            |                |                                         |              |           | bit 0 |  |

|               |                    |                                            |                |                                         |              |           |       |  |

| Legend:       |                    |                                            |                |                                         |              |           |       |  |

| R = Readable  | e bit              | W = Writable b                             | it             | U = Unimpleme                           | nted bit, re | ad as '0' |       |  |

| -n = Value at | POR                | '1' = Bit is set                           |                | '0' = Bit is cleared x = Bit is unknown |              |           |       |  |

|               |                    |                                            |                |                                         |              |           |       |  |

| bit 15-12     | Unimpleme          | nted: Read as '0'                          |                |                                         |              |           |       |  |

| bit 11-8      | ILR<3:0>: N        | lew CPU Interrupt                          | t Priority Lev | /el bits                                |              |           |       |  |

|               | 1111 = CPL         | J Interrupt Priority                       | Level is 15    |                                         |              |           |       |  |

|               | •                  |                                            |                |                                         |              |           |       |  |

|               | •                  |                                            |                |                                         |              |           |       |  |

|               | •<br>0001 = CPI    | J Interrupt Priority                       | l evel is 1    |                                         |              |           |       |  |

|               |                    | J Interrupt Priority                       |                |                                         |              |           |       |  |

| bit 7         | Unimpleme          | nted: Read as '0'                          |                |                                         |              |           |       |  |

| bit 6-0       | -                  | :0>: Vector Numb                           |                | ng Interrupt bits                       |              |           |       |  |

|               |                    | Interrupt vector pe                        |                | •                                       |              |           |       |  |

|               | •                  | ··· · · · · · · · · · ·                    | <b>J</b>       |                                         |              |           |       |  |

|               | •                  |                                            |                |                                         |              |           |       |  |

|               | •                  | Interruption                               | anding in Ne   | mbor 0                                  |              |           |       |  |

|               |                    | Interrupt vector pe<br>Interrupt vector pe | •              |                                         |              |           |       |  |

|               | - 0000000 <b>-</b> |                                            |                |                                         |              |           |       |  |

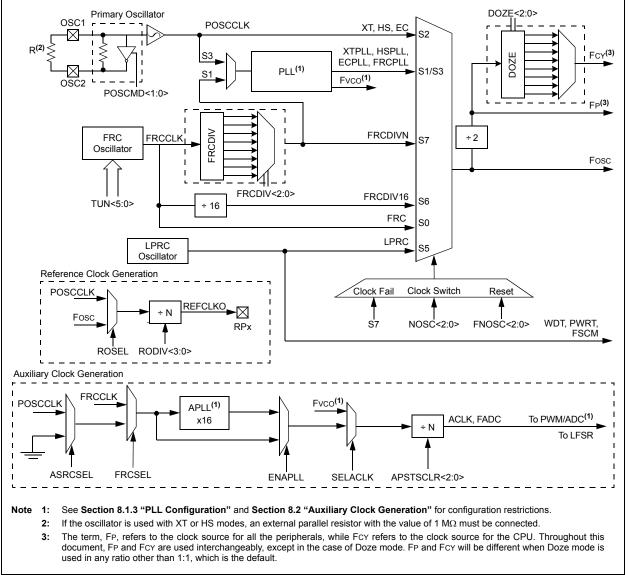

# 8.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS001/101A/102A/ 202A and dsPIC33FJ09GS302 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 42. "Oscillator (Part IV)" (DS70307) in the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The oscillator system provides:

- External and internal oscillator options as clock sources

- An on-chip Phase Lock Loop (PLL) to scale the internal operating frequency to the required system clock frequency

- An internal FRC oscillator that can also be used with the PLL, thereby allowing full-speed operation without any external clock generation hardware

- · Clock switching between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- An Oscillator Control register (OSCCON)

- Nonvolatile Configuration bits for main oscillator selection

- An auxiliary PLL for ADC and PWM

A simplified diagram of the oscillator system is shown in Figure 8-1.

# FIGURE 8-1: OSCILLATOR SYSTEM DIAGRAM

# 9.0 POWER-SAVING FEATURES

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS001/101A/102A/ 202A and dsPIC33FJ09GS302 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog Timer (WDT) and Power-Saving Modes" (DS70196) in the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

These devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. Devices can manage power consumption in four different ways:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- Software Controlled Doze mode

- Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

# 9.1 Clock Frequency and Clock Switching

These devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC<2:0> bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 8.0 "Oscillator Configuration"**.

# 9.2 Instruction-Based Power-Saving Modes

The devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAV instruction is shown in Example 9-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to wake-up.

#### 9.2.1 SLEEP MODE

The following occur in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals may continue to operate. This includes items, such as the Input Change Notification (ICN) on the I/O ports or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled.

The device will wake-up from Sleep mode on any of these events:

- · Any interrupt source that is individually enabled

- Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

#### EXAMPLE 9-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV#SLEEP\_MODE; Put the device into SLEEP modePWRSAV#IDLE\_MODE; Put the device into IDLE mode

#### 10.6.2.3 Virtual Pins

Four virtual RPn pins (RP32, RP33, RP34 and RP35) are supported, which are identical in functionality to all other RPn pins, with the exception of pinouts. These four pins are internal to the devices and are not connected to a physical device pin.

These pins provide a simple way for inter-peripheral connection without utilizing a physical pin. For example, the output of the analog comparator can be connected to RP32 and the PWM Fault input can be configured for RP32 as well. This configuration allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

# 10.6.3 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. dsPIC33F devices include three features to prevent alterations to the peripheral map:

- · Control register lock sequence

- Continuous state monitoring

- Configuration bit pin select lock

#### 10.6.3.1 Control Register Lock

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (OSCCON<6>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear IOLOCK, a specific command sequence must be executed:

- 1. Write 0x46 to OSCCON<7:0>.

- 2. Write 0x57 to OSCCON<7:0>.

- 3. Clear (or set) IOLOCK as a single operation.

Unlike the similar sequence with the oscillator's LOCK bit, IOLOCK remains in one state until changed. This allows all of the Peripheral Pin Selects to be configured with a single unlock sequence, followed by an update to all control registers, then locked with a second lock sequence.

#### 10.6.3.2 Continuous State Monitoring

In addition to being protected from direct writes, the contents of the RPINRx and RPORx registers are constantly monitored in hardware by shadow registers. If an unexpected change in any of the registers occurs (such as cell disturbances caused by ESD or other external events), a Configuration Mismatch Reset will be triggered.

#### 10.6.3.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPINRx and RPORx registers. The IOL1WAY (FOSC<5>) Configuration bit blocks the IOLOCK bit from being cleared, after it has been set once. If IOLOCK remains set, the register unlock procedure will not execute and the Peripheral Pin Select Control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session. Programming IOL1WAY allows user applications unlimited access (with the proper use of the unlock sequence) to the Peripheral Pin Select registers.

| U-0                   | U-0                         | R/W-1                                | R/W-1         | R/W-1            | R/W-1                 | R/W-1                      | R/W-1   |  |  |

|-----------------------|-----------------------------|--------------------------------------|---------------|------------------|-----------------------|----------------------------|---------|--|--|

| _                     | _                           |                                      |               |                  | R<5:0> <sup>(1)</sup> |                            |         |  |  |

| bit 15                |                             |                                      |               |                  |                       |                            | bit 8   |  |  |

|                       |                             |                                      |               |                  |                       |                            |         |  |  |

| U-0                   | U-0                         | R/W-1                                | R/W-1         | R/W-1            | R/W-1                 | R/W-1                      | R/W-1   |  |  |

| _                     | _                           |                                      |               | U1RXF            | R<5:0> <sup>(1)</sup> |                            |         |  |  |

| bit 7                 |                             |                                      |               |                  |                       |                            | bit (   |  |  |

| 1                     |                             |                                      |               |                  |                       |                            |         |  |  |

| Legend:<br>R = Readab | le hit                      | W = Writable                         | hit           | II = I Inimpler  | nented bit, read      | h as 'O'                   |         |  |  |

| -n = Value a          |                             | '1' = Bit is set                     |               | '0' = Bit is cle |                       | x = Bit is unkr            |         |  |  |

|                       |                             |                                      |               |                  | arcu                  |                            |         |  |  |

| bit 15-14             | Unimplemen                  | ted: Read as '                       | ∩ <b>'</b>    |                  |                       |                            |         |  |  |

| bit 13-8              | •                           |                                      |               |                  | a tha Carroona        | onding RPn Pin             | hita(1) |  |  |

| DIT 13-8              |                             | •                                    | TT Clear-to-S |                  | o the Correspo        | inding RPh Pin             | DIIS    |  |  |

|                       |                             | out tied to Vss                      | _             |                  |                       |                            |         |  |  |

|                       |                             | out tied to RP35                     |               |                  |                       |                            |         |  |  |

|                       |                             | out tied to RP34                     |               |                  |                       |                            |         |  |  |

|                       |                             | out tied to RP33<br>out tied to RP32 |               |                  |                       |                            |         |  |  |

|                       | 100000 <b>– III</b>         |                                      | <u>-</u>      |                  |                       |                            |         |  |  |

|                       | •                           |                                      |               |                  |                       |                            |         |  |  |

|                       | •                           |                                      |               |                  |                       |                            |         |  |  |

|                       | •                           |                                      |               |                  |                       |                            |         |  |  |

|                       | 00000 <b>= Inp</b>          | ut tied to RP0                       |               |                  |                       |                            |         |  |  |

| bit 7-6               | Unimplemen                  | nted: Read as '                      | 0'            |                  |                       |                            |         |  |  |

| bit 5-0               | U1RXR<5:0>                  | . Assign UART                        | 1 Receive (U  | 1RX) to the Co   | rresponding RI        | Pn Pin bits <sup>(1)</sup> |         |  |  |

|                       |                             | out tied to Vss                      | · ·           |                  |                       |                            |         |  |  |

|                       | 100011 = Input tied to RP35 |                                      |               |                  |                       |                            |         |  |  |

|                       |                             | out tied to RP34                     |               |                  |                       |                            |         |  |  |

|                       | 100001 <b>= In</b>          | out tied to RP33                     | 3             |                  |                       |                            |         |  |  |

|                       | 100000 <b>= In</b>          | out tied to RP32                     | 2             |                  |                       |                            |         |  |  |

|                       | •                           |                                      |               |                  |                       |                            |         |  |  |

|                       | •                           |                                      |               |                  |                       |                            |         |  |  |

|                       | •                           |                                      |               |                  |                       |                            |         |  |  |

|                       | 00000 <b>= Inn</b>          | ut tied to RP0                       |               |                  |                       |                            |         |  |  |

|                       | 00000 – m <b>p</b> t        |                                      |               |                  |                       |                            |         |  |  |

|                       |                             |                                      |               |                  |                       |                            |         |  |  |

#### REGISTER 10-7: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

**Note 1:** These bits are not implemented in the dsPIC33FJ06GS001 device.

# 13.1 Input Capture Registers

| U-0                  | U-0                         | R/W-0                                 | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | U-0              | U-0             | U-0                | U-0           |

|----------------------|-----------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|--------------------|---------------|

|                      | —                           | ICSIDL                                | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | —                | _               | —                  | _             |

| bit 15               |                             |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                 |                    | bit 8         |

| R/W-0                | R/W-0                       | R/W-0                                 | R-0, HC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R-0, HC          | R/W-0           | R/W-0              | R/W-0         |

| ICTMR <sup>(1)</sup> |                             | <1:0>                                 | ICOV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ICBNE            |                 | ICM<2:0>           | 10/00-0       |

| bit 7                |                             | \$1.02                                | 1007                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IODINE           |                 | 10101-2.02         | bit           |

|                      |                             |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                 |                    |               |

| Legend:              |                             | HC = Hardwar                          | e Clearable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                 |                    |               |

| R = Readat           | ole bit                     | W = Writable b                        | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | U = Unimple      | mented bit, re  | ead as '0'         |               |

| -n = Value a         | at POR                      | '1' = Bit is set                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | '0' = Bit is cle | eared           | x = Bit is unkn    | iown          |

| bit 15-14            | Unimplemer                  | ited: Read as '0                      | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |                 |                    |               |