Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | dsPIC                                                                          |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                          |

| Number of I/O              | 13                                                                             |

| Program Memory Size        | 6КВ (2К х 24)                                                                  |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 256 x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Through Hole                                                                   |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                        |

| Supplier Device Package    | 18-PDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs001-i-p |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

#### TABLE 4-34: PMD REGISTER MAP FOR dsPIC33FJ06GS001

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| PMD1        | 0770        | _      | _      | _      | T2MD   | T1MD   | _      | PWMMD  | -      | I2C1MD | _     | —     | —     |        | _     |       | ADCMD | 0000          |

| PMD3        | 0774        | _      | _      | _      | _      | _      | CMPMD  | _      | _      | _      | _     | _     | _     | _      | _     | _     | _     | 0000          |

| PMD4        | 0776        | _      | _      | _      |        | —      | _      |        |        | _      |       | —     | —     | REFOMD | _     | _     | _     | 0000          |

| PMD6        | 077A        | _      | _      | _      |        | PWM4MD | _      |        | PWM1MD | _      |       | —     | —     |        | _     | _     | _     | 0000          |

| PMD7        | 077C        | _      | _      | _      |        | —      | _      | CMPMD2 | CMPMD1 | _      | _     | _     | —     |        | _     | _     | _     | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-35: PMD REGISTER MAP FOR dsPIC33FJ06GS101A

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|--------|--------|--------|--------|--------|--------|-------|--------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| PMD1        | 0770        |        | —      |        | T2MD   | T1MD   | _      | PWMMD | -      | I2C1MD |       | U1MD  | _     | SPI1MD | _     | _     | ADCMD | 0000          |

| PMD2        | 0772        | _      | _      | _      |        | _      | _      |       | _      |        |       | —     | _     |        | _     |       | OC1MD | 0000          |

| PMD4        | 0776        | _      | _      | _      | _      | _      | _      | _     | _      | _      | _     |       | _     | REFOMD |       | _     | _     | 0000          |

| PMD6        | 077A        | —      | _      | -      |        | PWM4MD | _      | -     | PWM1MD |        |       | _     | —     |        | _     |       |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-36: PMD REGISTER MAP FOR dsPIC33FJ06GS102A

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| PMD1        | 0770        |        |        | _      | T2MD   | T1MD   | _      | PWMMD  | _      | I2C1MD | _     | U1MD  | _     | SPI1MD | _     | _     | ADCMD | 0000          |

| PMD2        | 0772        | _      | _      | _      | _      | _      | _      | _      | _      | _      |       | _     | _     | _      | _     | _     | OC1MD | 0000          |

| PMD4        | 0776        | _      | _      | _      | _      | _      | _      | _      | _      | _      |       | _     | _     | REFOMD | _     | _     | _     | 0000          |

| PMD6        | 077A        | _      | _      | _      | _      | _      | _      | PWM2MD | PWM1MD | _      | _     | —     | _     | -      | _     | —     | _     | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 6.10 Using the RCON Status Bits

The user application can read the Reset Control (RCON) register after any device Reset to determine the cause of the Reset.

| Note: | The status bits in the RCON register       |

|-------|--------------------------------------------|

|       | should be cleared after they are read so   |

|       | that the next RCON register value, after a |

|       | device Reset, will be meaningful.          |

#### TABLE 6-3: RESET FLAG BIT OPERATION

Flag Bit Set by: Cleared by: TRAPR (RCON<15>) Trap conflict event POR, BOR IOPWR (RCON<14>) POR, BOR Illegal opcode or uninitialized W register access or Security Reset CM (RCON<9>) **Configuration Mismatch** POR, BOR EXTR (RCON<7>) MCLR Reset POR SWR (RCON<6>) RESET instruction POR, BOR WDTO (RCON<4>) WDT time-out PWRSAV instruction, CLRWDT instruction, POR, BOR SLEEP (RCON<3>) PWRSAV #SLEEP instruction POR, BOR POR, BOR IDLE (RCON<2>) PWRSAV #IDLE instruction BOR (RCON<1>) POR, BOR POR (RCON<0>) POR

Note: All Reset flag bits can be set or cleared by user software.

Table 6-3 provides a summary of the Reset flag bit operation.

| REGISTER     | 7-13: IEC1:                                                                                        | INTERRUPT                           | ENABLE CO      | ONTROL RE               | GISTER 1             |                 |         |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------|-------------------------------------|----------------|-------------------------|----------------------|-----------------|---------|--|--|--|

| U-0          | U-0                                                                                                | R/W-0                               | U-0            | U-0                     | U-0                  | U-0             | U-0     |  |  |  |

| _            |                                                                                                    | INT2IE                              | —              | _                       | _                    | _               |         |  |  |  |

| bit 15       |                                                                                                    |                                     |                |                         | •                    |                 | bit 8   |  |  |  |

|              |                                                                                                    |                                     |                |                         |                      |                 |         |  |  |  |

| U-0          | U-0                                                                                                | U-0                                 | R/W-0          | R/W-0                   | R/W-0                | R/W-0           | R/W-0   |  |  |  |

| —            | _                                                                                                  | —                                   | INT1IE         | CNIE                    | AC1IE <sup>(1)</sup> | MI2C1IE         | SI2C1IE |  |  |  |

| bit 7        |                                                                                                    |                                     |                |                         |                      |                 | bit 0   |  |  |  |

|              |                                                                                                    |                                     |                |                         |                      |                 |         |  |  |  |

| Legend:      |                                                                                                    |                                     |                |                         |                      |                 |         |  |  |  |

| R = Readab   | le bit                                                                                             | W = Writable                        | bit            | U = Unimpler            | mented bit, read     | d as '0'        |         |  |  |  |

| -n = Value a | t POR                                                                                              | '1' = Bit is set                    |                | '0' = Bit is cle        | eared                | x = Bit is unkr | nown    |  |  |  |

|              |                                                                                                    |                                     |                |                         |                      |                 |         |  |  |  |

| bit 15-14    | -                                                                                                  | ted: Read as '                      |                |                         |                      |                 |         |  |  |  |

| bit 13       |                                                                                                    | rnal Interrupt 2                    |                |                         |                      |                 |         |  |  |  |

|              |                                                                                                    | request is enab<br>request is not e |                |                         |                      |                 |         |  |  |  |

| bit 12-5     |                                                                                                    | ited: Read as '                     |                |                         |                      |                 |         |  |  |  |

| bit 4        | -                                                                                                  | rnal Interrupt 1                    |                |                         |                      |                 |         |  |  |  |

| Dil 4        |                                                                                                    | request is enab                     |                |                         |                      |                 |         |  |  |  |

|              |                                                                                                    | request is not e                    |                |                         |                      |                 |         |  |  |  |

| bit 3        | CNIE: Input C                                                                                      | Change Notifica                     | tion Interrupt | Enable bit              |                      |                 |         |  |  |  |

|              |                                                                                                    | request is enab                     |                |                         |                      |                 |         |  |  |  |

|              | •                                                                                                  | request is not e                    |                |                         |                      |                 |         |  |  |  |

| bit 2        |                                                                                                    | og Comparator                       |                | able bit <sup>(1)</sup> |                      |                 |         |  |  |  |

|              | <ul> <li>1 = Interrupt request is enabled</li> <li>0 = Interrupt request is not enabled</li> </ul> |                                     |                |                         |                      |                 |         |  |  |  |

| bit 1        | •                                                                                                  | •                                   |                | aabla bit               |                      |                 |         |  |  |  |

|              | MI2C1IE: I2C1 Master Events Interrupt Enable bit<br>1 = Interrupt request is enabled               |                                     |                |                         |                      |                 |         |  |  |  |

|              | 0 = Interrupt request is not enabled                                                               |                                     |                |                         |                      |                 |         |  |  |  |

| bit 0        | SI2C1IE: I2C1 Slave Events Interrupt Enable bit                                                    |                                     |                |                         |                      |                 |         |  |  |  |

|              |                                                                                                    | request is enab                     | •              |                         |                      |                 |         |  |  |  |

|              | 0 = Interrupt r                                                                                    | request is not e                    | nabled         |                         |                      |                 |         |  |  |  |

|              |                                                                                                    |                                     |                |                         |                      |                 |         |  |  |  |

# **Note 1:** This bit is not implemented in dsPIC33FJ06GS101A/102A devices.

| <b>REGISTER 7</b>    | -17: IEC6: I                                                                                                                                                                                                                                                                                                                   | INTERRUPT                           | ENABLE CO |                                         | GISTER 6         |                       |       |  |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------|-----------------------------------------|------------------|-----------------------|-------|--|--|

| R/W-0                | R/W-0                                                                                                                                                                                                                                                                                                                          | U-0                                 | U-0       | U-0                                     | U-0              | U-0                   | U-0   |  |  |

| ADCP1IE              | ADCP0IE                                                                                                                                                                                                                                                                                                                        |                                     | —         | _                                       | —                | —                     | _     |  |  |

| bit 15               |                                                                                                                                                                                                                                                                                                                                |                                     |           |                                         |                  |                       | bit 8 |  |  |

|                      |                                                                                                                                                                                                                                                                                                                                |                                     |           |                                         |                  |                       |       |  |  |

| R/W-0                | U-0                                                                                                                                                                                                                                                                                                                            | U-0                                 | U-0       | U-0                                     | U-0              | R/W-0                 | U-0   |  |  |

| AC2IE <sup>(1)</sup> |                                                                                                                                                                                                                                                                                                                                |                                     | —         | —                                       |                  | PWM4IE <sup>(2)</sup> | —     |  |  |

| bit 7                |                                                                                                                                                                                                                                                                                                                                |                                     |           |                                         |                  |                       | bit 0 |  |  |

|                      |                                                                                                                                                                                                                                                                                                                                |                                     |           |                                         |                  |                       |       |  |  |

| Legend:              |                                                                                                                                                                                                                                                                                                                                |                                     |           |                                         |                  |                       |       |  |  |

| R = Readable         | bit                                                                                                                                                                                                                                                                                                                            | W = Writable                        | bit       | U = Unimpler                            | mented bit, read | l as '0'              |       |  |  |

| -n = Value at F      | POR                                                                                                                                                                                                                                                                                                                            | '1' = Bit is set                    |           | '0' = Bit is cleared x = Bit is unknown |                  |                       |       |  |  |

| bit 14               | <ul> <li>ADCP1IE: ADC Pair 1 Conversion Done Interrupt Enable bit</li> <li>1 = Interrupt request is enabled</li> <li>0 = Interrupt request is not enabled</li> <li>ADCP0IE: ADC Pair 0 Conversion Done Interrupt Enable bit</li> <li>1 = Interrupt request is enabled</li> <li>0 = Interrupt request is not enabled</li> </ul> |                                     |           |                                         |                  |                       |       |  |  |

| bit 13-8             | Unimplemen                                                                                                                                                                                                                                                                                                                     | ted: Read as '                      | C         |                                         |                  |                       |       |  |  |

| bit 7                | AC2IE: Analog Comparator 2 Interrupt Enable bit <sup>(1)</sup><br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                                                                                                                                                                     |                                     |           |                                         |                  |                       |       |  |  |

| bit 6-2              | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                     |                                     |           |                                         |                  |                       |       |  |  |

| bit 1                | PWM4IE: PWM4 Interrupt Enable bit <sup>(2)</sup>                                                                                                                                                                                                                                                                               |                                     |           |                                         |                  |                       |       |  |  |

|                      |                                                                                                                                                                                                                                                                                                                                | request is enab<br>request is not e |           |                                         |                  |                       |       |  |  |

| bit 0                | Unimplemen                                                                                                                                                                                                                                                                                                                     | ted: Read as '                      | כי        |                                         |                  |                       |       |  |  |

Note 1: This bit is not implemented in dsPIC33FJ06GS101A/102A devices.

2: This bit is not implemented in dsPIC33FJ06GS102A/202A devices.

#### **REGISTER 7-35: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER**

| U-0           | U-0                | U-0                                        | U-0                 | R-0               | R-0             | R-0       | R-0   |

|---------------|--------------------|--------------------------------------------|---------------------|-------------------|-----------------|-----------|-------|

| —             | —                  | —                                          | —                   |                   | ILI             | R<3:0>    |       |

| bit 15        |                    |                                            |                     |                   |                 |           | bit 8 |

|               |                    |                                            |                     |                   |                 |           |       |

| U-0           | R-0                | R-0                                        | R-0                 | R-0               | R-0             | R-0       | R-0   |

| —             |                    |                                            |                     | VECNUM<6:0>       |                 |           |       |

| bit 7         |                    |                                            |                     |                   |                 |           | bit 0 |

|               |                    |                                            |                     |                   |                 |           |       |

| Legend:       |                    |                                            |                     |                   |                 |           |       |

| R = Readable  | e bit              | W = Writable b                             | it                  | U = Unimpleme     | nted bit, re    | ad as '0' |       |

| -n = Value at | POR                |                                            | '0' = Bit is cleare | ed                | x = Bit is unkn | own       |       |

|               |                    |                                            |                     |                   |                 |           |       |

| bit 15-12     | Unimpleme          | nted: Read as '0'                          |                     |                   |                 |           |       |

| bit 11-8      | ILR<3:0>: ℕ        | lew CPU Interrupt                          | t Priority Lev      | /el bits          |                 |           |       |

|               | 1111 = CPL         | J Interrupt Priority                       | Level is 15         |                   |                 |           |       |

|               | •                  |                                            |                     |                   |                 |           |       |

|               | •                  |                                            |                     |                   |                 |           |       |

|               | •<br>0001 = CPI    | J Interrupt Priority                       | l evel is 1         |                   |                 |           |       |

|               |                    | J Interrupt Priority                       |                     |                   |                 |           |       |

| bit 7         | Unimpleme          | nted: Read as '0'                          |                     |                   |                 |           |       |

| bit 6-0       | -                  | :0>: Vector Numb                           |                     | ng Interrupt bits |                 |           |       |

|               |                    | Interrupt vector pe                        |                     | •                 |                 |           |       |

|               | •                  | ··· · · · · · · · · · ·                    | <b>J</b>            |                   |                 |           |       |

|               | •                  |                                            |                     |                   |                 |           |       |

|               | •                  | Interruption                               | anding in Ne        | mbor 0            |                 |           |       |

|               |                    | Interrupt vector pe<br>Interrupt vector pe | •                   |                   |                 |           |       |

|               | - 0000000 <b>-</b> |                                            |                     |                   |                 |           |       |

| R/W-0        | U-0                                                                              | R/W-0                               | R/W-0           | R/W-0            | R/W-0              | R/W-0           | R/W-0 |  |  |  |  |

|--------------|----------------------------------------------------------------------------------|-------------------------------------|-----------------|------------------|--------------------|-----------------|-------|--|--|--|--|

| ROON         |                                                                                  | ROSSLP                              | ROSEL           |                  | RODIV              | ′<3:0>(1)       |       |  |  |  |  |

| bit 15       |                                                                                  |                                     | 1               | l                |                    |                 | bit 8 |  |  |  |  |

|              |                                                                                  |                                     |                 |                  |                    |                 |       |  |  |  |  |

| U-0          | U-0                                                                              | U-0                                 | U-0             | U-0              | U-0                | U-0             | U-0   |  |  |  |  |

|              |                                                                                  | _                                   |                 | _                | —                  | _               |       |  |  |  |  |

| bit 7        |                                                                                  |                                     |                 |                  |                    |                 | bit 0 |  |  |  |  |

| Legend:      |                                                                                  |                                     |                 |                  |                    |                 |       |  |  |  |  |

| R = Readab   | ole bit                                                                          | W = Writable                        | bit             | U = Unimple      | mented bit, read   | d as '0'        |       |  |  |  |  |

| -n = Value a | at POR                                                                           | '1' = Bit is set                    |                 | '0' = Bit is cle | eared              | x = Bit is unkr | nown  |  |  |  |  |

|              |                                                                                  |                                     |                 |                  |                    |                 |       |  |  |  |  |

| bit 15       | ROON: Ref                                                                        | erence Oscillato                    | r Output Enab   | le bit           |                    |                 |       |  |  |  |  |

|              | 1 = Referen                                                                      | ce oscillator out                   | out is enabled  | on REFCLK0       | pin <sup>(2)</sup> |                 |       |  |  |  |  |

|              | 0 = Referen                                                                      | ce oscillator out                   | out is disabled | I                |                    |                 |       |  |  |  |  |

| bit 14       | Unimpleme                                                                        | Unimplemented: Read as '0'          |                 |                  |                    |                 |       |  |  |  |  |

| bit 13       | ROSSLP: R                                                                        | Reference Oscilla                   | tor Run in Sle  | ep bit           |                    |                 |       |  |  |  |  |

|              | 1 = Referen                                                                      | ce oscillator out                   | out continues   | to run in Sleep  | )                  |                 |       |  |  |  |  |

|              | 0 = Referen                                                                      | ce oscillator out                   | out is disabled | l in Sleep       |                    |                 |       |  |  |  |  |

| bit 12       | ROSEL: Re                                                                        | ference Oscillato                   | or Source Sele  | ect bit          |                    |                 |       |  |  |  |  |

|              |                                                                                  | or crystal used as clock used as th |                 |                  |                    |                 |       |  |  |  |  |

| bit 11-8     | <b>RODIV&lt;3:0&gt;:</b> Reference Oscillator Divider bits <sup>(1)</sup>        |                                     |                 |                  |                    |                 |       |  |  |  |  |

|              | 1111 = Reference clock divided by 32,768                                         |                                     |                 |                  |                    |                 |       |  |  |  |  |

|              | 1110 = Reference clock divided by 16,384                                         |                                     |                 |                  |                    |                 |       |  |  |  |  |

|              | 1101 = Reference clock divided by 8,192                                          |                                     |                 |                  |                    |                 |       |  |  |  |  |

|              | 1100 = Reference clock divided by 4,096                                          |                                     |                 |                  |                    |                 |       |  |  |  |  |

|              | 1011 = Reference clock divided by 2,048                                          |                                     |                 |                  |                    |                 |       |  |  |  |  |

|              | 1010 = Reference clock divided by 1,024<br>1001 = Reference clock divided by 512 |                                     |                 |                  |                    |                 |       |  |  |  |  |

|              |                                                                                  | erence clock divi                   |                 |                  |                    |                 |       |  |  |  |  |

|              |                                                                                  | erence clock divi                   |                 |                  |                    |                 |       |  |  |  |  |

|              |                                                                                  | erence clock divi                   |                 |                  |                    |                 |       |  |  |  |  |

|              | 0101 = Reference clock divided by 32<br>0100 = Reference clock divided by 16     |                                     |                 |                  |                    |                 |       |  |  |  |  |

|              |                                                                                  | erence clock divi                   |                 |                  |                    |                 |       |  |  |  |  |

|              |                                                                                  | erence clock divi                   | •               |                  |                    |                 |       |  |  |  |  |

|              |                                                                                  |                                     |                 |                  |                    |                 |       |  |  |  |  |

|              |                                                                                  | erence clock divi                   |                 |                  |                    |                 |       |  |  |  |  |

|              | 0001 = Refe                                                                      |                                     |                 |                  |                    |                 |       |  |  |  |  |

- **Note 1:** The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

- 2: This pin is remappable; refer to Section 10.6 "Peripheral Pin Select (PPS)" for more information.

### 8.6 Fail-Safe Clock Monitor (FSCM)

The Fail-Safe Clock Monitor (FSCM) allows the device to continue to operate, even in the event of an oscillator failure. The FSCM function is enabled by programming. If the FSCM function is enabled, the LPRC internal oscillator runs at all times (except during Sleep mode) and is not subject to control by the Watchdog Timer.

In the event of an oscillator failure, the FSCM generates a clock failure trap event and switches the system clock over to the FRC oscillator. Then, the application program can either attempt to restart the oscillator or execute a controlled shutdown. The trap can be treated as a warm Reset by simply loading the Reset address into the oscillator fail trap vector.

If the PLL multiplier is used to scale the system clock, the internal FRC is also multiplied by the same factor on clock failure. Essentially, the device switches to FRC with PLL on a clock failure.

#### 8.7 Pseudo-Random Generator

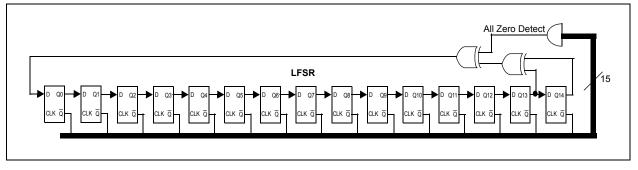

The pseudo-random generator is implemented with a 15-bit Linear Feedback Shift Register (LFSR), which is a shift register with a few exclusive OR gates. The shift register is clocked by the PWM clock and is a read-only register. The purpose of this feature is to provide the ability to randomly change the period or the active portion of the PWM.

A firmware routine can be used to read "n" random bits from the LFSR register and combine them, by either summing or performing another logical operation with the PWM period of the Duty Cycle registers. The result will be a PWM signal whose nominal period (or duty cycle) is the desired one, but whose effective value changes randomly. This capability will help in reducing the EMI/EMC emissions by spreading the power over a wider frequency range.

Figure 8-3 provides a block diagram of the LFSR.

# 9.5 PMD Control Registers

| U-0    | U-0 | U-0                 | R/W-0 | R/W-0                 | U-0 | R/W-0                | U-0   |

|--------|-----|---------------------|-------|-----------------------|-----|----------------------|-------|

| _      |     |                     | T2MD  | T1MD                  | _   | PWMMD <sup>(1)</sup> |       |

| bit 15 |     |                     |       |                       |     |                      | bit 8 |

|        |     |                     |       |                       |     |                      |       |

| R/W-0  | U-0 | R/W-0               | U-0   | R/W-0                 | U-0 | U-0                  | R/W-0 |

| I2C1MD | _   | U1MD <sup>(2)</sup> | _     | SPI1MD <sup>(2)</sup> | _   | —                    | ADCMD |

| bit 7  |     |                     |       |                       |     |                      | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                                             |

|-----------|--------------------------------------------------------------------------------------------------------|

| bit 12    | T2MD: Timer2 Module Disable bit                                                                        |

|           | 1 = Timer2 module is disabled                                                                          |

|           | 0 = Timer2 module is enabled                                                                           |

| bit 11    | T1MD: Timer1 Module Disable bit                                                                        |

|           | 1 = Timer1 module is disabled                                                                          |

|           | 0 = Timer1 module is enabled                                                                           |

| bit 10    | Unimplemented: Read as '0'                                                                             |

| bit 9     | <b>PWMMD:</b> PWM Module Disable bit <sup>(1)</sup>                                                    |

|           | 1 = PWM module is disabled                                                                             |

|           | 0 = PWM module is enabled                                                                              |

| bit 8     | Unimplemented: Read as '0'                                                                             |

| bit 7     | I2C1MD: I2C1 Module Disable bit                                                                        |

|           | 1 = I2C1 module is disabled                                                                            |

| 1.11.0    | 0 = I2C1 module is enabled                                                                             |

| bit 6     | Unimplemented: Read as '0'                                                                             |

| bit 5     | U1MD: UART1 Module Disable bit <sup>(2)</sup>                                                          |

|           | 1 = UART1 module is disabled<br>0 = UART1 module is enabled                                            |

| h:t 4     |                                                                                                        |

| bit 4     | Unimplemented: Read as '0'                                                                             |

| bit 3     | SPI1MD: SPI1 Module Disable bit <sup>(2)</sup>                                                         |

|           | 1 = SPI1 module is disabled<br>0 = SPI1 module is enabled                                              |

| bit 2-1   | Unimplemented: Read as '0'                                                                             |

|           | ADCMD: ADC Module Disable bit                                                                          |

| bit 0     |                                                                                                        |

|           | 1 = ADC module is disabled<br>0 = ADC module is enabled                                                |

|           |                                                                                                        |

| Note 1:   | Once the PWM module is re-enabled (PWMMD is set to '1' and then set to '0'), all PWM registers must be |

| 11010 11  |                                                                                                        |

- **Note 1:** Once the PWM module is re-enabled (PWMMD is set to '1' and then set to '0'), all PWM registers must be re-initialized.

- 2: This bit is not implemented in the dsPIC33FJ06GS001 device.

# 11.1 Timer1 Control Register

| R/W-0         | U-0                                                                                                   | R/W-0            | U-0           | U-0              | U-0              | U-0             | U-0 |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------|------------------|---------------|------------------|------------------|-----------------|-----|--|--|--|

| TON           |                                                                                                       | TSIDL            |               |                  |                  |                 | —   |  |  |  |

| bit 15        |                                                                                                       |                  |               |                  |                  | 1               | bit |  |  |  |

|               |                                                                                                       |                  |               |                  |                  |                 |     |  |  |  |

| U-0           | R/W-0                                                                                                 | R/W-0            | R/W-0         | U-0              | R/W-0            | R/W-0           | U-0 |  |  |  |

| —             | TGATE                                                                                                 | TCKP             | S<1:0>        |                  | TSYNC            | TCS             |     |  |  |  |

| bit 7         |                                                                                                       |                  |               |                  |                  |                 | bit |  |  |  |

|               |                                                                                                       |                  |               |                  |                  |                 |     |  |  |  |

| Legend:       | - 1-14                                                                                                |                  | L 14          |                  |                  | l (0'           |     |  |  |  |

| R = Readabl   |                                                                                                       | W = Writable     |               | -                | mented bit, read |                 |     |  |  |  |

| -n = Value at | POR                                                                                                   | '1' = Bit is set |               | '0' = Bit is cle | eared            | x = Bit is unkn | own |  |  |  |

|               |                                                                                                       | 0.1.1            |               |                  |                  |                 |     |  |  |  |

| bit 15        | TON: Timer1                                                                                           |                  |               |                  |                  |                 |     |  |  |  |

|               | 1 = Starts 16<br>0 = Stops 16                                                                         |                  |               |                  |                  |                 |     |  |  |  |

| bit 14        | -                                                                                                     | nted: Read as '  | ∩'            |                  |                  |                 |     |  |  |  |

| bit 13        | -                                                                                                     |                  |               |                  |                  |                 |     |  |  |  |

|               | <b>TSIDL:</b> Stop in Idle Mode bit<br>1 = Discontinues module operation when device enters Idle mode |                  |               |                  |                  |                 |     |  |  |  |

|               |                                                                                                       | s module opera   |               |                  |                  |                 |     |  |  |  |

| bit 12-7      | Unimplemented: Read as '0'                                                                            |                  |               |                  |                  |                 |     |  |  |  |

| bit 6         | TGATE: Time                                                                                           | er1 Gated Time   | Accumulatio   | n Enable bit     |                  |                 |     |  |  |  |

|               | <u>When TCS = 1:</u><br>This bit is ignored.                                                          |                  |               |                  |                  |                 |     |  |  |  |

|               | When TCS = 0:                                                                                         |                  |               |                  |                  |                 |     |  |  |  |

|               | 1 = Gated time accumulation is enabled                                                                |                  |               |                  |                  |                 |     |  |  |  |

|               |                                                                                                       | ne accumulatio   |               |                  |                  |                 |     |  |  |  |

| bit 5-4       |                                                                                                       | Timer1 Input     | Clock Presca  | ale Select bits  |                  |                 |     |  |  |  |

|               | 11 = 1:256<br>10 = 1:64                                                                               |                  |               |                  |                  |                 |     |  |  |  |

|               | 01 = 1:8                                                                                              |                  |               |                  |                  |                 |     |  |  |  |

|               | 00 = 1:1                                                                                              |                  |               |                  |                  |                 |     |  |  |  |

| bit 3         | Unimplemer                                                                                            | nted: Read as '  | 0'            |                  |                  |                 |     |  |  |  |

| bit 2         | TSYNC: Time                                                                                           | er1 External Cl  | ock Input Syr | hchronization S  | elect bit        |                 |     |  |  |  |

|               | When TCS =                                                                                            |                  |               |                  |                  |                 |     |  |  |  |

|               |                                                                                                       | nizes external o |               | innut            |                  |                 |     |  |  |  |

|               | When TCS =                                                                                            | synchronize e    |               | input            |                  |                 |     |  |  |  |

|               | This bit is ign                                                                                       |                  |               |                  |                  |                 |     |  |  |  |

| bit 1         | •                                                                                                     | Clock Source     | Select bit    |                  |                  |                 |     |  |  |  |

|               |                                                                                                       | clock from T1C   |               | risina edae)     |                  |                 |     |  |  |  |

|               |                                                                                                       |                  |               |                  |                  |                 |     |  |  |  |

|               | 0 = Internal c                                                                                        |                  | P (* * *      | 5 - 5 - 7        |                  |                 |     |  |  |  |

#### REGISTER 11-1: T1CON: TIMER1 CONTROL REGISTER

### REGISTER 15-11: DTRx: PWMx DEAD-TIME REGISTER

bit 7

| U-0    | U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|--------|-------|-------|

| —      | —     |       |       | DTR   | <13:8> |       |       |

| bit 15 |       |       |       |       |        |       | bit 8 |

|        |       |       |       |       |        |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

| hit | 0 |

|-----|---|

|     |   |

| Legend:           |                  |                        |                    |  |

|-------------------|------------------|------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

bit 15-14Unimplemented: Read as '0'bit 13-0DTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

#### REGISTER 15-12: ALTDTRx: PWMx ALTERNATE DEAD-TIME REGISTER

| U-0             | U-0   | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

| —               | _     |                  |       | ALTDT             | Rx<13:8>        |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| R/W-U           | R/W-U | R/W-U            |       |                   | R/W-U           | R/W-U           | K/W-U |

|                 |       |                  | ALTD  | FR <7:0>          |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | oit   | U = Unimplen      | nented bit, rea | ad as '0'       |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 ALTDTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

#### 16.1 SPI Helpful Tips

- 1. In Frame mode, if there is a possibility that the master may not be initialized before the slave:

- a) If FRMPOL (SPIxCON2<13>) = 1, use a pull-down resistor on SSx.

- b) If FRMPOL = 0, use a pull-up resistor on  $\frac{1}{SSx}$ .

| Note: | This                  | insures | that  | the       | first | fr | ame |

|-------|-----------------------|---------|-------|-----------|-------|----|-----|

|       | transr                | nission | after | initializ | ation | is | not |

|       | shifted or corrupted. |         |       |           |       |    |     |

- 2. In Non-Framed 3-Wire mode, (i.e., not using SSx from a master):

- a) If CKP (SPIxCON1<6>) = 1, always place a pull-up resistor on SSx.

- b) If CKP = <u>0</u>, always place a pull-down resistor on SSx.

- **Note:** This will insure that during power-up and initialization the master/slave will not lose Sync due to an errant SCK transition that would cause the slave to accumulate data shift errors for both transmit and receive appearing as corrupted data.

- FRMEN (SPIxCON2<15>) = 1 and SSEN (SPIxCON1<7>) = 1 are exclusive and invalid. In Frame mode, SCKx is continuous and the Frame Sync pulse is active on the SSx pin, which indicates the start of a data frame.

- Note: Not all third-party devices support Frame mode timing. Refer to the SPI electrical characteristics for details.

- In Master mode only, set the SMP bit (SPIxCON1<9>) to a '1' for the fastest SPI data rate possible. The SMP bit can only be set at the same time or after the MSTEN bit (SPIxCON1<5>) is set.

To avoid invalid slave read data to the master, the user's master software must ensure enough time for slave software to fill its write buffer before the user application initiates a master write/read cycle. It is always advisable to preload the SPIxBUF Transmit register in advance of the next master transaction cycle. SPIxBUF is transferred to the SPI Shift register and is empty once the data transmission begins.

### 16.2 SPI Resources

Many useful resources related to SPI are provided on the Microchip web site (www.microchip.com).

#### 16.2.1 KEY RESOURCES

- Section 18. "Serial Peripheral Interface (SPI)" (DS70206)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related *"dsPIC33F/PIC24H Family Reference Manual"* Sections

- · Development Tools

# REGISTER 18-1: U1MODE: UART1 MODE REGISTER (CONTINUED)

| bit 4   | URXINV: Receive Polarity Inversion bit <sup>(3)</sup>                                                                                                                              |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = U1RX Idle state is '0'                                                                                                                                                         |

|         | 0 = U1RX Idle state is '1'                                                                                                                                                         |

| bit 3   | BRGH: High Baud Rate Enable bit <sup>(3)</sup>                                                                                                                                     |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul> |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits <sup>(3)</sup>                                                                                                                          |

|         | 11 = 9-bit data, no parity                                                                                                                                                         |

|         | 10 = 8-bit data, odd parity                                                                                                                                                        |

|         | 01 = 8-bit data, even parity                                                                                                                                                       |

|         | 00 = 8-bit data, no parity                                                                                                                                                         |

| bit 0   | STSEL: Stop Bit Selection bit <sup>(3)</sup>                                                                                                                                       |

|         | 1 = Two Stop bits                                                                                                                                                                  |

|         | 0 = One Stop bit                                                                                                                                                                   |

|         |                                                                                                                                                                                    |

- **Note 1:** Refer to **Section 17. "UART**" (DS70188) in the *"dsPIC33F/PIC24H Family Reference Manual"* for information on enabling the UART module for receive or transmit operation.

- **2:** This feature is only available for the 16x BRG mode (BRGH = 0).

- 3: This bit is not available in the dsPIC33FJ06GS001 device.

| TABLE 22-3: 0 | ISPIC33F CONFIGURATION BITS DESCRIPTION                                                                       |

|---------------|---------------------------------------------------------------------------------------------------------------|

| Bit Field     | Description                                                                                                   |

| GCP           | General Segment Code-Protect bit                                                                              |

|               | 1 = User program memory is not code-protected                                                                 |

|               | 0 = Code protection is enabled for the entire program memory space                                            |

| GWRP          | General Segment Write-Protect bit                                                                             |

|               | 1 = User program memory is not write-protected                                                                |

|               | 0 = User program memory is write-protected                                                                    |

| IESO          | Two-Speed Oscillator Start-up Enable bit                                                                      |

|               | 1 = Start up device with FRC, then automatically switch to the user-selected oscillator source                |

|               | when ready                                                                                                    |

|               | 0 = Start up device with user-selected oscillator source                                                      |

| FNOSC<2:0>    | Oscillator Selection bits                                                                                     |

|               | 111 = Fast RC Oscillator with divide-by-N (FRCDIVN)                                                           |

|               | 110 = Reserved; do not use                                                                                    |

|               | 101 = Low-Power RC Oscillator (LPRC)<br>100 = Reserved; do not use                                            |

|               | 011 = Primary Oscillator with PLL module (MS + PLL, EC + PLL)                                                 |

|               | 010 = Primary Oscillator (MS, HS, EC)                                                                         |

|               | 001 = Fast RC Oscillator with divide-by-N with PLL module                                                     |

|               | (FRCDIVN + PLL)                                                                                               |

|               | 000 = Fast RC Oscillator (FRC)                                                                                |

| FCKSM<1:0>    | Clock Switching Mode bits                                                                                     |

|               | 1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled                                         |

|               | 01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled                                          |

|               | 00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                           |

| IOL1WAY       | Peripheral Pin Select Configuration bit                                                                       |

|               | 1 = Allow only one reconfiguration                                                                            |

|               | 0 = Allow multiple reconfigurations                                                                           |

| OSCIOFNC      | OSC2 Pin Function bit (except in MS and HS modes)                                                             |

|               | 1 = OSC2 is the clock output                                                                                  |

|               | 0 = OSC2 is the general purpose digital I/O pin                                                               |

| POSCMD<1:0>   | Primary Oscillator Mode Select bits                                                                           |

|               | <ul><li>11 = Primary Oscillator is disabled</li><li>10 = HS Crystal Oscillator mode (10 MHz-32 MHz)</li></ul> |

|               | 01 = MS Crystal Oscillator mode (3 MHz-10 MHz)                                                                |

|               | 00 = EC (External Clock) mode (DC-32 MHz)                                                                     |

| FWDTEN        | Watchdog Timer Enable bit                                                                                     |

|               | 1 = Watchdog Timer is always enabled (LPRC oscillator cannot be disabled; clearing the SWDTEN                 |

|               | bit in the RCON register will have no effect)                                                                 |

|               | 0 = Watchdog Timer is enabled/disabled by user software (LPRC can be disabled by clearing                     |

|               | the SWDTEN bit in the RCON register)                                                                          |

| WDTPRE        | Watchdog Timer Prescaler bit                                                                                  |

|               | 1 = 1:128                                                                                                     |

|               | 0 = 1:32                                                                                                      |

| WDTPOST<3:0>  | Watchdog Timer Postscaler bits                                                                                |

|               | 1111 <b>= 1</b> :32,768                                                                                       |

|               | 1110 <b>= 1:16,384</b>                                                                                        |

|               | •                                                                                                             |

|               | •                                                                                                             |

|               | •                                                                                                             |

|               | 0001 = 1:2                                                                                                    |

|               | 0000 = 1:1                                                                                                    |

# TABLE 22-3: dsPIC33F CONFIGURATION BITS DESCRIPTION

| Base<br>Instr<br># | Assembly<br>Mnemonic | Assembly Syntax   |                                     | Description                                                             | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|-------------------|-------------------------------------|-------------------------------------------------------------------------|---------------|----------------|--------------------------|

| 48                 | MPY                  | MPY<br>Wm*Wn,Ac   | cc,Wx,Wxd,Wy,Wyd                    | Multiply Wm by Wn to Accumulator                                        | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | MPY<br>Wm*Wm,Ac   | cc,Wx,Wxd,Wy,Wyd                    | Square Wm to Accumulator                                                | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 49                 | MPY.N                | MPY.N<br>Wm*Wn,Ac | cc,Wx,Wxd,Wy,Wyd                    | -(Multiply Wm by Wn) to Accumulator                                     | 1             | 1              | None                     |

| 50                 | MSC                  | MSC               | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd<br>,<br>AWB | Multiply and Subtract from Accumulator                                  | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 51                 | MUL                  | MUL.SS            | Wb,Ws,Wnd                           | {Wnd + 1, Wnd} = signed(Wb) * signed(Ws)                                | 1             | 1              | None                     |

|                    |                      | MUL.SU            | Wb,Ws,Wnd                           | {Wnd + 1, Wnd} = signed(Wb) * unsigned(Ws)                              | 1             | 1              | None                     |

|                    |                      | MUL.US            | Wb,Ws,Wnd                           | {Wnd + 1, Wnd} = unsigned(Wb) * signed(Ws)                              | 1             | 1              | None                     |

|                    |                      | MUL.UU            | Wb,Ws,Wnd                           | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(Ws)                         | 1             | 1              | None                     |

|                    |                      | MUL.SU            | Wb,#lit5,Wnd                        | {Wnd + 1, Wnd} = signed(Wb) * unsigned(lit5)                            | 1             | 1              | None                     |

|                    |                      | MUL.UU            | Wb,#lit5,Wnd                        | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(lit5)                       | 1             | 1              | None                     |

|                    |                      | MUL               | f                                   | W3:W2 = f * WREG                                                        | 1             | 1              | None                     |

| 52                 | NEG                  | NEG               | Acc                                 | Negate Accumulator                                                      | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | NEG               | f                                   | $f = \overline{f} + 1$                                                  | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | NEG               | f,WREG                              | WREG = $\overline{f}$ + 1                                               | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | NEG               | Ws,Wd                               | $Wd = \overline{Ws} + 1$                                                | 1             | 1              | C,DC,N,OV,Z              |

| 53                 | NOP                  | NOP               |                                     | No Operation                                                            | 1             | 1              | None                     |

|                    |                      | NOPR              |                                     | No Operation                                                            | 1             | 1              | None                     |

| 54                 | POP                  | POP               | f                                   | Pop f from Top-of-Stack (TOS)                                           | 1             | 1              | None                     |

|                    |                      | POP               | Wdo                                 | Pop from Top-of-Stack (TOS) to Wdo                                      | 1             | 1              | None                     |

|                    |                      | POP.D             | Wnd                                 | Pop from Top-of-Stack (TOS) to<br>W(nd):W(nd + 1)                       | 1             | 2              | None                     |

|                    |                      | POP.S             |                                     | Pop Shadow Registers                                                    | 1             | 1              | All                      |

| 55                 | PUSH                 | PUSH              | f                                   | Push f to Top-of-Stack (TOS)                                            | 1             | 1              | None                     |

|                    |                      | PUSH              | Wso                                 | Push Wso to Top-of-Stack (TOS)                                          | 1             | 1              | None                     |

|                    |                      | PUSH.D            | Wns                                 | Push W(ns):W(ns + 1) to Top-of-Stack (TOS)                              | 1             | 2              | None                     |