Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 13                                                                               |

| Program Memory Size        | 6KB (2K x 24)                                                                    |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 256 x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

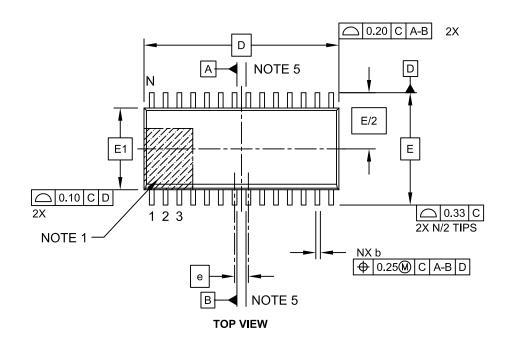

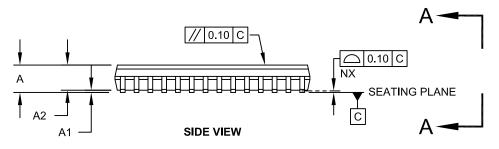

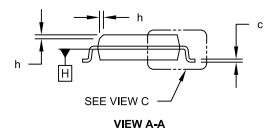

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 18-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs001t-e-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

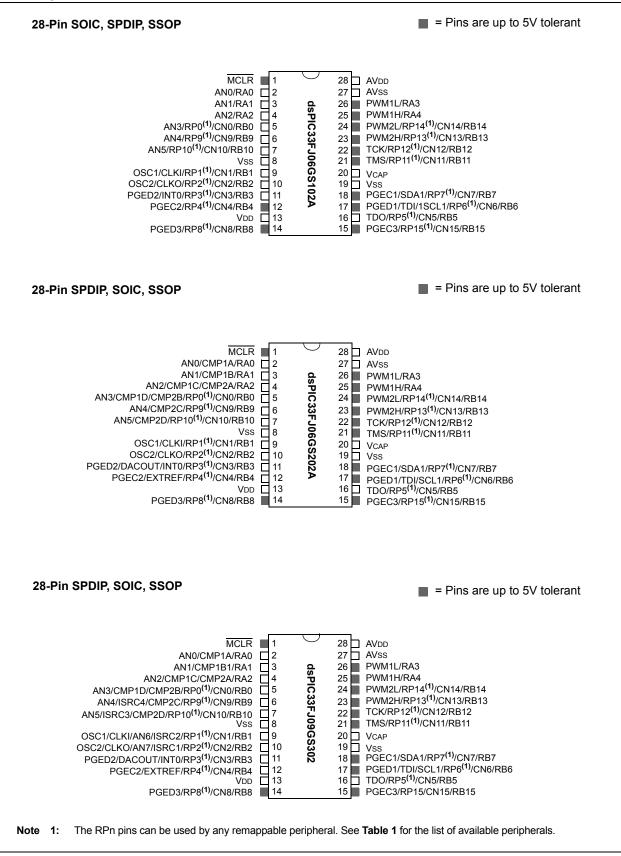

#### **Pin Diagrams (Continued)**

#### 2.5 ICSP<sup>™</sup> Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins, are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and Input Voltage High (VIH) and Input Voltage Low (VIL) pin requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins), programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>TM</sup>.

For more information on MPLAB ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site (www.microchip.com):

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS51765)

- "Multi-Tool Design Advisory" (DS51764)

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator User's Guide" (DS51616)

- *"Using MPLAB<sup>®</sup> REAL ICE™"* (poster) (DS51749)

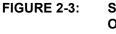

#### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

NOTES:

## 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS001/101A/102A/ 202A and dsPIC33FJ09GS302 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 2.** "CPU" (DS70204) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The CPU module has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for DSP. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space. The actual amount of program memory implemented varies from device to device. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

The dsPIC33FJ06GS001/101A/102A/202A and dsPIC33FJ09GS302 devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can serve as a Data, Address or Address Offset register. The sixteenth working register (W15) operates as a software Stack Pointer (SP) for interrupts and calls.

There are two classes of instruction: MCU and DSP. These two instruction classes are seamlessly integrated into a single CPU. The instruction set includes many addressing modes and is designed for optimum C compiler efficiency. For most instructions, the devices are capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing A + B = C operations to be executed in a single cycle.

A block diagram of the CPU is shown in Figure 3-1, and the programmer's model is shown in Figure 3-2.

## 3.1 Data Addressing Overview

The data space can be addressed as 32K words or 64 Kbytes and is split into two blocks, referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear data space. Certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y data space boundary is device-specific.

Overhead-free circular buffers (Modulo Addressing mode) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. Furthermore, the X AGU Circular Addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms.

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K program word boundary defined by the 8-bit Program Space Visibility Page (PSVPAG) register. The program-to-data space mapping feature lets any instruction access program space as if it were data space.

## 3.2 DSP Engine Overview

The DSP engine features a high-speed, 17-bit by 17-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bidirectional barrel shifter. The barrel shifter is capable of shifting a 40-bit value up to 16 bits, right or left, in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been designed for optimal realtime performance. The MAC instruction and other associated instructions can concurrently fetch two data operands from memory while multiplying two W registers and accumulating and optionally saturating the result in the same cycle. This instruction functionality requires that the RAM data space be split for these instructions and linear for all others. Data space partitioning is achieved in a transparent and flexible manner through dedicating certain working registers to each address space.

#### TABLE 4-16: I2C1 REGISTER MAP

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8                        | Bit 7 | Bit 6 | Bit 5 | Bit 4    | Bit 3    | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|---------|--------|---------|--------|--------|--------|--------|------------------------------|-------|-------|-------|----------|----------|-------|-------|-------|---------------|

| I2C1RCV     | 0200        | _       | _      |         | —      | —      | —      | —      | _                            |       |       |       | Receive  | Register |       |       |       | 0000          |

| I2C1TRN     | 0202        | _       |        | _       | _      | -      | _      | _      | _                            |       |       |       | Transmit | Register |       |       |       | OOFF          |

| I2C1BRG     | 0204        | _       |        | _       | _      | -      | _      | _      | Baud Rate Generator Register |       |       |       |          |          |       |       | 0000  |               |

| I2C1CON     | 0206        | I2CEN   |        | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN                         | GCEN  | STREN | ACKDT | ACKEN    | RCEN     | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT    | 0208        | ACKSTAT | TRSTAT | _       | _      | -      | BCL    | GCSTAT | ADD10                        | IWCOL | I2COV | D_A   | Р        | S        | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD     | 020A        | _       |        | _       | _      | -      | _      |        | Address Register             |       |       |       |          |          |       |       | 0000  |               |

| I2C1MSK     | 020C        | —       | _      |         | —      | _      | _      |        | AMSK<9:0>                    |       |       |       |          |          |       | 0000  |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-17: UART1 REGISTER MAP FOR dsPiC33FJ06GS101A, dsPiC33FJ06GS102A, dsPiC33FJ06GS202A AND dsPiC33FJ09GS302

| SFR Name | SFR<br>Addr | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8                           | Bit 7  | Bit 6  | Bit 5 | Bit 4       | Bit 3   | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|----------|-------------|----------|--------|----------|--------|--------|--------|-------|---------------------------------|--------|--------|-------|-------------|---------|-------|--------|-------|---------------|

| U1MODE   | 0220        | UARTEN   | —      | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0                            | WAKE   | LPBACK | ABAUD | URXINV      | BRGH    | PDSEI | _<1:0> | STSEL | 0000          |

| U1STA    | 0222        | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT                            | URXISE | L<1:0> | ADDEN | RIDLE       | PERR    | FERR  | OERR   | URXDA | 0110          |

| U1TXREG  | 0224        | _        | _      | -        | _      | _      | _      | -     |                                 |        |        | UART  | Transmit Re | egister |       |        |       | XXXX          |

| U1RXREG  | 0226        | _        | _      | -        | _      | _      | _      | -     | UART Receive Register 0         |        |        |       |             |         |       |        | 0000  |               |

| U1BRG    | 0228        |          | -      |          |        | •      |        | B     | Baud Rate Generator Prescaler 0 |        |        |       |             |         |       | 0000   |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

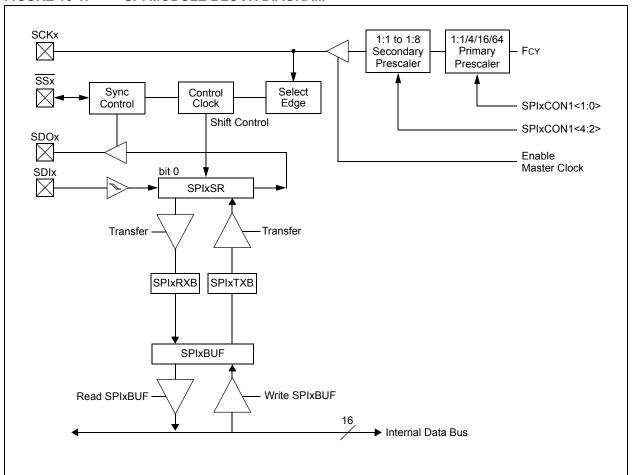

#### TABLE 4-18:SPI1 REGISTER MAP FOR dsPIC33FJ06GS101A, dsPIC33FJ06GS102A, dsPIC33FJ06GS202A AND dsPIC33FJ09GS302

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8       | Bit 7       | Bit 6       | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------------|--------|--------|---------|--------|--------|--------|-----------|-------------|-------------|-------------|-------|-------|-----------|-------|--------|--------|---------------|

| SPI1STAT | 0240        | SPIEN  | _      | SPISIDL |        |        |        |           | _           |             | SPIROV      | _     | _     | _         | _     | SPITBF | SPIRBF | 0000          |

| SPI1CON1 | 0242        | _      | _      | _       | DISSCK | DISSDO | MODE16 | SMP       | CKE         | SSEN        | CKP         | MSTEN |       | SPRE<2:0> |       | PPRE   | <1:0>  | 0000          |

| SPI1CON2 | 0244        | FRMEN  | SPIFSD | FRMPOL  |        | _      | _      | _         | _           | _           | _           | _     | _     | _         | _     | FRMDLY | _      | 0000          |

| SPI1BUF  | 0248        |        |        |         |        |        |        | SPI1 Tran | smit and Re | ceive Buffe | er Register |       |       |           |       |        |        | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-32: SYSTEM CONTROL REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13    | Bit 12 | Bit 11 | Bit 10                                       | Bit 9  | Bit 8 | Bit 7   | Bit 6  | Bit 5  | Bit 4    | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets       |

|----------|-------------|--------|--------|-----------|--------|--------|----------------------------------------------|--------|-------|---------|--------|--------|----------|-------|-------|-------|-------|---------------------|

| RCON     | 0740        | TRAPR  | IOPUWR | _         |        | —      | _                                            | СМ     | VREGS | EXTR    | SWR    | SWDTEN | WDTO     | SLEEP | IDLE  | BOR   | POR   | <sub>XXXX</sub> (1) |

| OSCCON   | 0742        | _      | (      | COSC<2:0> |        | —      | ١                                            | NOSC<2 | :0>   | CLKLOCK | IOLOCK | LOCK   | _        | CF    | —     | _     | OSWEN | <sub>0300</sub> (2) |

| CLKDIV   | 0744        | ROI    | [      | DOZE<2:0> |        | DOZEN  | DOZEN FRCDIV<2:0> PLLPOST<1:0> — PLLPRE<4:0> |        |       |         |        |        | 3040     |       |       |       |       |                     |

| PLLFBD   | 0746        | _      | _      | _         | _      | _      |                                              |        |       |         |        | PL     | LDIV<8:0 | >     |       |       |       | 0030                |

| OSCTUN   | 0748        | _      | _      | _         | _      | _      |                                              |        | _     | _       | _      |        |          | TUN   | <5:0> |       |       | 0000                |

| LFSR     | 074C        | _      |        |           |        |        |                                              |        |       | LFSR<1  | 4:0>   |        |          |       |       |       |       | 0000                |

| REFOCON  | 074E        | ROON   | _      | ROSSLP    | ROSEL  |        | RODI                                         | V<3:0> |       | _       | _      | _      | _        | _     | _     | _     | _     | 0000                |

| ACLKCON  | 0750        | ENAPLL | APLLCK | SELACLK   | _      | —      | APS                                          | STSCLR | <2:0> | ASRCSEL | FRCSEL | _      | _        | _     | _     | _     | —     | 0000                |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The RCON register Reset values are dependent on the type of Reset.

2: The OSCCON register Reset values are dependent on the FOSCx Configuration bits and on type of Reset.

#### TABLE 4-33: NVM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1  | Bit 0 | All<br>Resets   |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|--------|-------|--------|-------|-----------------|

| NVMCON    | 0760 | WR     | WREN   | WRERR  | —      | _      | —      | _     | _     | _     | ERASE | _     | —     |        | NVMOF | P<3:0> |       | 0000 <b>(1)</b> |

| NVMKEY    | 0766 | —      | _      | _      | —      | _      | _      | _     | _     |       |       |       | NVMKE | Y<7:0> |       |        |       | 0000            |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Reset value shown is for POR only. Value on other Reset states is dependent on the state of memory write or erase operations at the time of Reset.

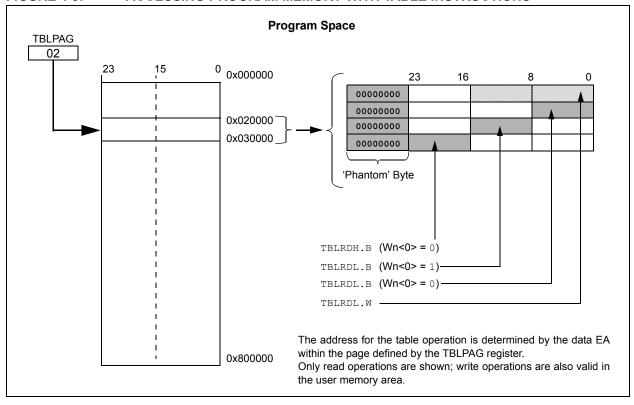

#### 4.7.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>)

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when byte select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom byte', will always be '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address, in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

Similarly, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in Section 5.0 "Flash Program Memory".

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

## FIGURE 4-9: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

# FIGURE 7-1: dsPIC33FJ06GS001/101A/102A/202A and dsPIC33FJ09GS302 INTERRUPT VECTOR TABLE

| 1                                 | Depet como Instruction            |                   |                                                        |

|-----------------------------------|-----------------------------------|-------------------|--------------------------------------------------------|

|                                   | Reset - GOTO Instruction          | 0x000000          |                                                        |

|                                   | Reset – GOTO Address              | 0x000002          |                                                        |

|                                   | Reserved                          | 0x000004          |                                                        |

|                                   | Oscillator Fail Trap Vector       | _                 |                                                        |

|                                   | Address Error Trap Vector         | _                 |                                                        |

|                                   | Stack Error Trap Vector           |                   |                                                        |

|                                   | Math Error Trap Vector            | _                 |                                                        |

|                                   | Reserved                          |                   |                                                        |

|                                   | Reserved                          |                   |                                                        |

|                                   | Reserved                          |                   |                                                        |

|                                   | Interrupt Vector 0                | 0x000014          |                                                        |

|                                   | Interrupt Vector 1                |                   |                                                        |

|                                   | ~                                 | _                 |                                                        |

|                                   | ~                                 | _                 |                                                        |

|                                   | ~                                 |                   |                                                        |

|                                   | Interrupt Vector 52               | 0x00007C          | Interrupt Vector Table (IVT) <sup>(1)</sup>            |

| >                                 | Interrupt Vector 53               | 0x00007E          | ,                                                      |

| brit                              | Interrupt Vector 54               | 0x000080          |                                                        |

| L re                              | ~                                 | _                 |                                                        |

| er                                | ~                                 | -                 |                                                        |

| Drd                               | Interrupt Vector 116              | 0x0000FC          |                                                        |

| Decreasing Natural Order Priority | Interrupt Vector 117              | 0x0000FC          |                                                        |

| fr                                |                                   | 0x000100          |                                                        |

| Za                                | Reserved<br>Reserved              | 0x000100          |                                                        |

| bu                                | Reserved                          | 0x000102          |                                                        |

| asi                               | Oscillator Fail Trap Vector       | _                 |                                                        |

| e c                               | Address Error Trap Vector         |                   |                                                        |

| De                                | Stack Error Trap Vector           |                   |                                                        |

| _                                 | Math Error Trap Vector            |                   |                                                        |

|                                   | Reserved                          | _                 |                                                        |

|                                   | Reserved                          |                   |                                                        |

|                                   | Reserved                          | -                 |                                                        |

|                                   | Interrupt Vector 0                | 0x000114          |                                                        |

|                                   | Interrupt Vector 1                |                   |                                                        |

|                                   | ~                                 |                   |                                                        |

|                                   | ~                                 | 1                 |                                                        |

|                                   | ~                                 | 1                 | Alternate Interrupt Vector Table (AIVT) <sup>(1)</sup> |

|                                   | Interrupt Vector 52               | 0x00017C          | ,                                                      |

|                                   | Interrupt Vector 53               | 0x00017E          |                                                        |

|                                   | Interrupt Vector 54               | 0x000180          |                                                        |

|                                   | ~                                 |                   |                                                        |

|                                   | ~                                 |                   |                                                        |

|                                   | ~                                 | ]                 |                                                        |

|                                   | Interrupt Vector 116              |                   |                                                        |

| ↓ I                               | Interrupt Vector 117              | 0x0001FE          |                                                        |

| V                                 | Start of Code                     | 0x000200          |                                                        |

|                                   |                                   |                   |                                                        |

|                                   |                                   |                   |                                                        |

| Note de O                         | Table 7 4 families list of image  |                   |                                                        |

| Note 1: See                       | Table 7-1 for the list of impleme | ented interrupt v | ectors.                                                |

|                                   |                                   |                   |                                                        |

## dsPIC33FJ06GS001/101A/102A/202A and dsPIC33FJ09GS302

| U-0          | U-0                                                                                                                       | U-0             | U-0            | U-0              | U-0                        | U-0                    | U-0                    |  |  |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|------------------|----------------------------|------------------------|------------------------|--|--|--|--|--|

| _            | _                                                                                                                         | _               | _              | _                | —                          | _                      | —                      |  |  |  |  |  |

| bit 15       | ·                                                                                                                         |                 |                |                  |                            | ·                      | bit 8                  |  |  |  |  |  |

|              |                                                                                                                           |                 |                |                  |                            |                        |                        |  |  |  |  |  |

| U-0          | U-0                                                                                                                       | U-0             | R/W-0          | U-0              | U-0                        | R/W-0                  | R/W-0                  |  |  |  |  |  |

| _            | —                                                                                                                         |                 | ADCP6IF        | —                | —                          | ADCP3IF <sup>(1)</sup> | ADCP2IF <sup>(2)</sup> |  |  |  |  |  |

| bit 7        |                                                                                                                           |                 |                |                  |                            |                        | bit 0                  |  |  |  |  |  |

|              |                                                                                                                           |                 |                |                  |                            |                        |                        |  |  |  |  |  |

| Legend:      |                                                                                                                           |                 |                |                  |                            |                        |                        |  |  |  |  |  |

| R = Readat   | = Readable bit W = Writable bit U = Unimplemented bit, read as '0'                                                        |                 |                |                  |                            |                        |                        |  |  |  |  |  |

| -n = Value a | at POR                                                                                                                    | '1' = Bit is se | t              | '0' = Bit is cle | cleared x = Bit is unknown |                        |                        |  |  |  |  |  |

|              |                                                                                                                           |                 |                |                  |                            |                        |                        |  |  |  |  |  |

| bit 15-5     | Unimplemen                                                                                                                | ted: Read as    | 'O'            |                  |                            |                        |                        |  |  |  |  |  |

| bit 4        | ADCP6IF: A                                                                                                                | DC Pair 6 Con   | version Done I | nterrupt Flag S  | Status bit                 |                        |                        |  |  |  |  |  |

|              | 1 = Interrupt                                                                                                             | request has o   | curred         |                  |                            |                        |                        |  |  |  |  |  |

|              | 0 = Interrupt                                                                                                             | request has no  | ot occurred    |                  |                            |                        |                        |  |  |  |  |  |

| bit 3-2      | Unimplemen                                                                                                                | ted: Read as    | '0'            |                  |                            |                        |                        |  |  |  |  |  |

| bit 1        | ADCP3IF: A                                                                                                                | DC Pair 3 Con   | version Done I | nterrupt Flag S  | Status bit <sup>(1)</sup>  |                        |                        |  |  |  |  |  |

|              | 1 = Interrupt                                                                                                             | request has o   | curred         |                  |                            |                        |                        |  |  |  |  |  |

|              | 0 = Interrupt                                                                                                             | request has no  | ot occurred    |                  |                            |                        |                        |  |  |  |  |  |

| bit 0        | ADCP2IF: AI                                                                                                               | DC Pair 2 Con   | version Done I | nterrupt Flag S  | Status bit <sup>(2)</sup>  |                        |                        |  |  |  |  |  |

|              | <b>ADCP2IF:</b> ADC Pair 2 Conversion Done Interrupt Flag Status bit <sup>(2)</sup><br>1 = Interrupt request has occurred |                 |                |                  |                            |                        |                        |  |  |  |  |  |

|              | 0 = Interrupt request has not occurred                                                                                    |                 |                |                  |                            |                        |                        |  |  |  |  |  |

- Note 1: This bit is not implemented in dsPIC33FJ06GS102A/202A devices.

- 2: This bit is not implemented in dsPIC33FJ06GS001/101A devices.

#### 10.2 Open-Drain Configuration

In addition to the PORT, LAT and TRIS registers for data control, some digital only port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (for example, 5V), on any desired 5V tolerant pins, by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

Refer to the **"Pin Diagrams"** section for the available pins and their functionality.

#### 10.3 Configuring Analog Port Pins

The ADPCFG and TRIS registers control the operation of the Analog-to-Digital port pins. The port pins that are to function as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The ADPCFG register has a default value of 0x0000; therefore, all pins that share ANx functions are analog (not digital) by default.

When the PORT register is read, all pins configured as analog input channels will read as cleared (a low level).

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin, defined as a digital input (including the ANx pins), can cause the input buffer to consume current that exceeds the device specifications.

#### 10.4 I/O Port Write/Read Timing

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP. An example is shown in Example 10-1.

## 10.5 Input Change Notification

The Input Change Notification function of the I/O ports allows devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States (COS), even in Sleep mode when the clocks are disabled. Depending on the device pin count, up to 16 external signals (CNx pin) can be selected (enabled) for generating an interrupt request on a Change-of-State.

Four control registers are associated with the CN module. The CNEN1 register contains the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pin.

Each CN pin also has a weak pull-up connected to it. The pull-ups act as a current source connected to the pin and eliminate the need for external resistors when the push button or keypad devices are connected. The pull-ups are enabled separately, using the CNPU1 register, which contains the control bits for each of the CN pins. Setting any of the control bits enables the weak pull-ups for the corresponding pins.

**Note:** Pull-ups on change notification pins should always be disabled when the port pin is configured as a digital output.

| MOV  | 0xFF00, W0 | ; Configure PORTB<15:8> as inputs |

|------|------------|-----------------------------------|

| MOV  | W0, TRISBB | ; and PORTB<7:0> as outputs       |

| NOP  |            | ; Delay 1 cycle                   |

| BTSS | PORTB, #13 | ; Next Instruction                |

EXAMPLE 10-1: PORT WRITE/READ EXAMPLE

| R/W-0                 | R/W-0                                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-0                                                                                                                                                                                                                                                                                                                                              | U-0                                                                                                                                                                                             | U-0                                                         | U-0             | U-0          |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------|--------------|

|                       | TRGDI                                                                                                                                                                                                                                                                        | V<3:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                    | —                                                                                                                                                                                               |                                                             | _               |              |

| bit 15                |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                 |                                                             |                 | bit          |

| R/W-0                 | U-0                                                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-0                                                                                                                                                                                                                                                                                                                                              | R/W-0                                                                                                                                                                                           | R/W-0                                                       | R/W-0           | R/W-0        |

| DTM <sup>(1)</sup>    |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                    | TRGS                                                                                                                                                                                            | TRT<5:0>                                                    |                 |              |

| bit 7                 |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                 |                                                             |                 | bit          |

| Legend:               |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                 |                                                             |                 |              |

| R = Readable          | bit                                                                                                                                                                                                                                                                          | W = Writable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit                                                                                                                                                                                                                                                                                                                                                | U = Unimple                                                                                                                                                                                     | mented bit, read                                            | 1 as '0'        |              |

| -n = Value at F       | POR                                                                                                                                                                                                                                                                          | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                    | '0' = Bit is cle                                                                                                                                                                                | ared                                                        | x = Bit is unkr | nown         |

| bit 15-12<br>bit 11-8 | 1111 = Trigg<br>1100 = Trigg<br>1100 = Trigg<br>1001 = Trigg<br>1010 = Trigg<br>1000 = Trigg<br>1000 = Trigg<br>0111 = Trigg<br>0110 = Trigg<br>0101 = Trigg<br>0100 = Trigg<br>0011 = Trigg<br>0010 = Trigg<br>0010 = Trigg<br>0001 = Trigg<br>0001 = Trigg<br>0000 = Trigg | >: Trigger # Ou<br>yer output for ev<br>yer output for ev yer output for ev<br>yer output for ev yer output for ev yer output | very 16th trigg<br>very 15th trigg<br>very 15th trigg<br>very 13th trigg<br>very 12th trigg<br>very 12th trigg<br>very 10th trigg<br>very 9th trigge<br>very 8th trigge<br>very 6th trigge<br>very 5th trigge<br>very 3th trigge<br>very 3th trigge<br>very 3th trigge<br>very 3th trigge<br>very 3th trigge<br>very 3th trigge<br>very 2nd trigge | er event<br>er event<br>er event<br>er event<br>er event<br>er event<br>r event<br>r event<br>r event<br>r event<br>r event<br>r event<br>r event<br>r event<br>r event<br>er event<br>er event |                                                             |                 |              |

| bit 7                 |                                                                                                                                                                                                                                                                              | rigger Mode bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                 |                                                             |                 |              |