#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuns                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 13                                                                               |

| Program Memory Size        | 6KB (2K x 24)                                                                    |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 256 x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 20-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs001t-e-ss |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 4 MHz < FIN < 8 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside of this range, the application must start up in the FRC mode first. The default PLL settings after a POR, with an oscillator frequency outside of this range, will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLDBF to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

## 2.8 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 3 or REAL ICE is selected as a debugger, it automatically initializes all of the Analog-to-Digital input pins (ANx) as "digital" pins, by setting all bits in the ADPCFG register.

The bits in the registers that correspond to the Analog-to-Digital pins that are initialized by MPLAB ICD 3 or REAL ICE, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain Analog-to-Digital pins as analog input pins during the debug session, the user application must clear the corresponding bits in the ADPCFG register during initialization of the ADC module.

When MPLAB ICD 3 or REAL ICE is used as a programmer, the user application firmware must correctly configure the ADPCFG register. Automatic initialization of these registers is only done during debugger operation. Failure to correctly configure the register(s) will result in all Analog-to-Digital pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

## 2.9 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

## 2.10 Typical Application Connection Examples

Examples of typical application connections are shown in Figure 2-4 through Figure 2-8.

## 3.4 CPU Control Registers

| R-0                  | R-0                                               | R/C-0                                  | R/C-0             | R-0                    | R/C-0                | R -0             | R/W-0         |

|----------------------|---------------------------------------------------|----------------------------------------|-------------------|------------------------|----------------------|------------------|---------------|

| OA                   | OB                                                | SA <sup>(1)</sup>                      | SB <sup>(1)</sup> | OAB                    | SAB <sup>(1,4)</sup> | DA               | DC            |

| bit 15               |                                                   |                                        |                   |                        | •                    |                  | bit 8         |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup>                              | R/W-0 <sup>(3)</sup>                   | R-0               | R/W-0                  | R/W-0                | R/W-0            | R/W-0         |

|                      | IPL<2:0> <sup>(2)</sup>                           |                                        | RA                | N                      | OV                   | Z                | С             |

| bit 7                |                                                   |                                        |                   |                        |                      |                  | bit (         |

| Legend:              |                                                   |                                        |                   |                        |                      |                  |               |

| C = Clearab          | le bit                                            | R = Readable                           | e bit             | U = Unimple            | mented bit, read     | as '0'           |               |

| S = Settable         | bit                                               | W = Writable                           | bit               | -n = Value at          | POR                  |                  |               |

| '1' = Bit is se      | et                                                | '0' = Bit is clea                      | ared              | x = Bit is unk         | nown                 |                  |               |

| bit 15               | OA: Accumul                                       | lator A Overflow                       | v Status bit      |                        |                      |                  |               |

|                      |                                                   | ator A overflowe                       |                   |                        |                      |                  |               |

| 1.1.4.4              |                                                   | ator A has not c                       |                   |                        |                      |                  |               |

| bit 14               |                                                   | lator B Overflow<br>ator B overflowe   |                   |                        |                      |                  |               |

|                      |                                                   | ator B has not c                       |                   |                        |                      |                  |               |

| bit 13               | SA: Accumul                                       | ator A Saturatio                       | on 'Sticky' Sta   | tus bit <sup>(1)</sup> |                      |                  |               |

|                      | 1 = Accumula                                      | ator A is saturat<br>ator A is not sat | ed or has bee     |                        | some time            |                  |               |

| bit 12               | SB: Accumul                                       | ator B Saturatio                       | on 'Sticky' Sta   | tus bit <sup>(1)</sup> |                      |                  |               |

|                      |                                                   | ator B is saturat<br>ator B is not sat |                   | en saturated at        | some time            |                  |               |

| bit 11               | <b>0AB:</b> 0A    0                               | DB Combined A                          | ccumulator O      | verflow Status         | bit                  |                  |               |

|                      | 1 = Accumula                                      | ators A or B hav                       | ve overflowed     |                        |                      |                  |               |

| bit 10               | <b>SAB:</b> SA    S                               | B Combined A                           | ccumulator 'St    | icky' Status bit       | (1,4)                |                  |               |

|                      | 1 = Accumula                                      |                                        | saturated or      | have been sat          | urated at some       | time in the past | t             |

| bit 9                | DA: DO Loop                                       | Active bit                             |                   |                        |                      |                  |               |

|                      | 1 = DO <b>loop ir</b>                             |                                        |                   |                        |                      |                  |               |

|                      | -                                                 | ot in progress                         |                   |                        |                      |                  |               |

| bit 8                |                                                   | U Half Carry/B                         |                   |                        |                      |                  |               |

|                      | of the res                                        | sult occurred                          |                   | -                      | data) or 8th low-o   |                  |               |

|                      | •                                                 | -out from the 4 the result occur       |                   | bit (for byte-siz      | ed data) or 8th      | low-order bit (1 | for word-size |

| Note 1: ⊤            | his bit can be rea                                | ad or cleared (n                       | ot set).          |                        |                      |                  |               |

| L                    | he IPL<2:0> bits<br>evel (IPL). The v<br>PL3 = 1. |                                        |                   |                        |                      |                  |               |

|                      |                                                   |                                        |                   |                        |                      |                  |               |

#### REGISTER 3-1: SR: CPU STATUS REGISTER

**3:** The IPL<2:0> Status bits are read-only when NSTDIS = 1 (INTCON1<15>).

**4:** Clearing this bit will clear SA and SB.

| TABLE 4-21: HIGH-SPEED 10-BIT ADC REGISTER MAP FOR dSPIC33FJ06GS102A AND dSPIC33FJ06GS202A |             |        |                                                                  |        |         |        |        |       |        |               |       |         |                 |                       |       |       |       |              |

|--------------------------------------------------------------------------------------------|-------------|--------|------------------------------------------------------------------|--------|---------|--------|--------|-------|--------|---------------|-------|---------|-----------------|-----------------------|-------|-------|-------|--------------|

| SFR Name                                                                                   | SFR<br>Addr | Bit 15 | Bit 14                                                           | Bit 13 | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7         | Bit 6 | Bit 5   | Bit 4           | Bit 3                 | Bit 2 | Bit 1 | Bit 0 | All<br>Reset |

| ADCON                                                                                      | 0300        | ADON   | _                                                                | ADSIDL | SLOWCLK | _      | GSWTRG | —     | FORM   | EIE           | ORDER | SEQSAMP | ASYNCSAMP       | ASYNCSAMP — ADCS<2:0> |       |       | 0003  |              |

| ADPCFG                                                                                     | 0302        | _      | —                                                                | _      | —       | _      | —      | _     | _      | —             |       | PCFG5   | PCFG4           | PCFG3                 | PCFG2 | PCFG1 | PCFG0 | 0000         |

| ADSTAT                                                                                     | 0306        | _      | —                                                                | _      | —       | _      | —      |       | _      | —             | P6RDY | —       | —               | _                     | P2RDY | P1RDY | P0RDY | 0000         |

| ADBASE                                                                                     | 0308        |        | ADBASE<15:1> —                                                   |        |         |        |        |       |        |               |       |         |                 |                       | 0000  |       |       |              |

| ADCPC0                                                                                     | 030A        | IRQEN1 | RQEN1 PEND1 SWTRG1 TRGSRC1<4:0> IRQEN0 PEND0 SWTRG0 TRGSRC0<4:0> |        |         |        |        |       |        |               |       |         |                 | 0000                  |       |       |       |              |

| ADCPC1                                                                                     | 030C        | _      | —                                                                | _      | _       | _      | —      |       | _      | IRQEN2        | PEND2 | SWTRG2  | 52 TRGSRC2<4:0> |                       |       |       |       | 0000         |

| ADCPC3                                                                                     | 0310        | _      |                                                                  |        |         |        |        |       |        | 0000          |       |         |                 |                       |       |       |       |              |

| ADCBUF0                                                                                    | 0320        |        |                                                                  |        |         |        |        |       | ADC D  | ata Buffer 0  | )     |         |                 |                       |       |       |       | XXXX         |

| ADCBUF1                                                                                    | 0322        |        |                                                                  |        |         |        |        |       | ADC D  | ata Buffer 1  |       |         |                 |                       |       |       |       | XXXX         |

| ADCBUF2                                                                                    | 0324        |        |                                                                  |        |         |        |        |       | ADC D  | ata Buffer 2  | 2     |         |                 |                       |       |       |       | XXXX         |

| ADCBUF3                                                                                    | 0326        |        |                                                                  |        |         |        |        |       | ADC D  | ata Buffer 3  | 3     |         |                 |                       |       |       |       | XXXX         |

| ADCBUF4                                                                                    | 0328        |        |                                                                  |        |         |        |        |       | ADC D  | ata Buffer 4  | ļ     |         |                 |                       |       |       |       | XXXX         |

| ADCBUF5                                                                                    | 032A        |        |                                                                  |        |         |        |        |       | ADC D  | ata Buffer 5  | 5     |         |                 |                       |       |       |       | XXXX         |

| ADCBUF12                                                                                   | 0338        |        |                                                                  |        |         |        |        |       | ADC Da | ata Buffer 12 | 2     |         |                 |                       |       |       |       | XXXX         |

| ADCBUF13                                                                                   | 033A        |        |                                                                  |        |         |        |        |       | ADC Da | ata Buffer 1  | 3     |         |                 |                       |       |       |       | XXXX         |

## TABLE 4-21: HIGH-SPEED 10-BIT ADC REGISTER MAP FOR dsPIC33FJ06GS102A AND dsPIC33FJ06GS202A

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

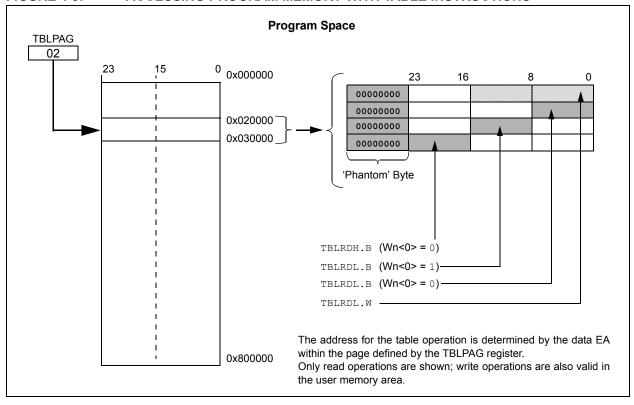

### 4.7.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>)

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when byte select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom byte', will always be '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address, in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

Similarly, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in Section 5.0 "Flash Program Memory".

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

## FIGURE 4-9: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

# **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 1 BOR: Brown-out Reset Flag bit

- 1 = A Brown-out Reset has occurred

- 0 = A Brown-out Reset has not occurred

#### bit 0 POR: Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

## REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 2 | STKERR: Stack Error Trap Status bit                |

|-------|----------------------------------------------------|

|       | 1 = Stack error trap has occurred                  |

|       | 0 = Stack error trap has not occurred              |

| bit 1 | <b>OSCFAIL:</b> Oscillator Failure Trap Status bit |

|       | 1 = Oscillator failure trap has occurred           |

|       | 0 = Oscillator failure trap has not occurred       |

| bit 0 | Unimplemented: Read as '0'                         |

© 2011-2012 Microchip Technology Inc.

| REGISTER 7-13: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1 |                 |                                     |                |                         |                      |                 |         |  |  |  |  |  |

|----------------------------------------------------------|-----------------|-------------------------------------|----------------|-------------------------|----------------------|-----------------|---------|--|--|--|--|--|

| U-0                                                      | U-0             | R/W-0                               | U-0            | U-0                     | U-0                  | U-0             | U-0     |  |  |  |  |  |

| _                                                        |                 | INT2IE                              | —              | _                       | _                    | _               |         |  |  |  |  |  |

| bit 15                                                   |                 |                                     |                |                         | •                    |                 | bit 8   |  |  |  |  |  |

|                                                          |                 |                                     |                |                         |                      |                 |         |  |  |  |  |  |

| U-0                                                      | U-0             | U-0                                 | R/W-0          | R/W-0                   | R/W-0                | R/W-0           | R/W-0   |  |  |  |  |  |

| —                                                        | _               | —                                   | INT1IE         | CNIE                    | AC1IE <sup>(1)</sup> | MI2C1IE         | SI2C1IE |  |  |  |  |  |

| bit 7                                                    |                 |                                     |                |                         |                      |                 | bit 0   |  |  |  |  |  |

|                                                          |                 |                                     |                |                         |                      |                 |         |  |  |  |  |  |

| Legend:                                                  |                 |                                     |                |                         |                      |                 |         |  |  |  |  |  |

| R = Readab                                               | le bit          | W = Writable                        | bit            | U = Unimpler            | mented bit, read     | d as '0'        |         |  |  |  |  |  |

| -n = Value a                                             | t POR           | '1' = Bit is set                    |                | '0' = Bit is cle        | eared                | x = Bit is unkr | unknown |  |  |  |  |  |

|                                                          |                 |                                     |                |                         |                      |                 |         |  |  |  |  |  |

| bit 15-14                                                | -               | ted: Read as '                      |                |                         |                      |                 |         |  |  |  |  |  |

| bit 13                                                   |                 | rnal Interrupt 2                    |                |                         |                      |                 |         |  |  |  |  |  |

|                                                          |                 | request is enab<br>request is not e |                |                         |                      |                 |         |  |  |  |  |  |

| bit 12-5                                                 |                 | ited: Read as '                     |                |                         |                      |                 |         |  |  |  |  |  |

| bit 4                                                    | -               | rnal Interrupt 1                    |                |                         |                      |                 |         |  |  |  |  |  |

| Dil 4                                                    |                 | request is enab                     |                |                         |                      |                 |         |  |  |  |  |  |

|                                                          |                 | request is not e                    |                |                         |                      |                 |         |  |  |  |  |  |

| bit 3                                                    | CNIE: Input C   | Change Notifica                     | tion Interrupt | Enable bit              |                      |                 |         |  |  |  |  |  |

|                                                          |                 | request is enab                     |                |                         |                      |                 |         |  |  |  |  |  |

|                                                          | •               | request is not e                    |                |                         |                      |                 |         |  |  |  |  |  |

| bit 2                                                    |                 | og Comparator                       |                | able bit <sup>(1)</sup> |                      |                 |         |  |  |  |  |  |

|                                                          |                 | request is enab                     |                |                         |                      |                 |         |  |  |  |  |  |

| bit 1                                                    | •               | request is not e<br>21 Master Even  |                | aabla bit               |                      |                 |         |  |  |  |  |  |

|                                                          |                 | request is enab                     | -              |                         |                      |                 |         |  |  |  |  |  |

|                                                          |                 | request is enab                     |                |                         |                      |                 |         |  |  |  |  |  |

| bit 0                                                    | •               | 1 Slave Events                      |                | able bit                |                      |                 |         |  |  |  |  |  |

|                                                          |                 | request is enab                     | •              |                         |                      |                 |         |  |  |  |  |  |

|                                                          | 0 = Interrupt r | request is not e                    | nabled         |                         |                      |                 |         |  |  |  |  |  |

|                                                          |                 |                                     |                |                         |                      |                 |         |  |  |  |  |  |

# **Note 1:** This bit is not implemented in dsPIC33FJ06GS101A/102A devices.

| REGISTER      | 9-5: PMD6   | : PERIPHER                       | AL MODULE      | E DISABLE C             | ONTROL RE       | GISTER 6              |        |

|---------------|-------------|----------------------------------|----------------|-------------------------|-----------------|-----------------------|--------|

| U-0           | U-0         | U-0                              | U-0            | R/W-0                   | U-0             | R/W-0                 | R/W-0  |

| _             | _           | —                                |                | PWM4MD <sup>(1)</sup>   | —               | PWM2MD <sup>(2)</sup> | PWM1MD |

| bit 15        |             |                                  |                |                         |                 |                       | bit 8  |

| U-0           | U-0         | U-0                              | U-0            | U-0                     | U-0             | U-0                   | U-0    |

|               |             |                                  |                | <u> </u>                |                 |                       |        |

| bit 7         |             |                                  |                |                         |                 |                       | bit 0  |

| Legend:       |             |                                  |                |                         |                 |                       |        |

| R = Readable  | e bit       | W = Writable                     | bit            | U = Unimplem            | ented bit, read | d as '0'              |        |

| -n = Value at | POR         | '1' = Bit is set                 |                | '0' = Bit is clea       | ared            | x = Bit is unkn       | own    |

| bit 15-12     | Unimplomon  | ted: Read as '                   | ۰,             |                         |                 |                       |        |

| bit 11        | •           | NM Generator                     |                | able bit(1)             |                 |                       |        |

|               | 1 = PWM Ger | nerator 4 modu<br>nerator 4 modu | le is disabled |                         |                 |                       |        |

| bit 10        | Unimplement | ted: Read as '                   | )'             |                         |                 |                       |        |

| bit 9         | PWM2MD: PV  | WM Generator                     | 2 Module Disa  | able bit <sup>(2)</sup> |                 |                       |        |

|               | ±           | nerator 2 modu<br>nerator 2 modu |                |                         |                 |                       |        |

| bit 8         | PWM1MD: PV  | WM Generator                     | 1 Module Disa  | able bit                |                 |                       |        |

|               |             | nerator 1 modu<br>nerator 1 modu |                |                         |                 |                       |        |

| bit 7-0       | Unimplement | ted: Read as '                   | )'             |                         |                 |                       |        |

**Note 1:** This bit is not implemented in dsPIC33FJ06GS102A/202A devices.

**2:** This bit is not implemented in dsPIC33FJ06GS001/101A devices.

| REGISTER 9-     | ·7: PMD | 8: PERIPHER      | AL MODULE | DISABLE C                          | ON I ROL RE      | GISTER 8             |       |  |  |  |

|-----------------|---------|------------------|-----------|------------------------------------|------------------|----------------------|-------|--|--|--|

| U-0             | U-0     | U-0              | U-0       | U-0                                | U-0              | U-0                  | U-0   |  |  |  |

| —               | _       | —                | —         | —                                  | —                | —                    | —     |  |  |  |

| bit 15          |         |                  | •         |                                    |                  | · · ·                | bit 8 |  |  |  |

|                 |         |                  |           |                                    |                  |                      |       |  |  |  |

| U-0             | U-0     | U-0              | U-0       | U-0                                | U-0              | R/W-0                | U-0   |  |  |  |

| —               |         | —                | —         | —                                  | _                | CCSMD <sup>(1)</sup> |       |  |  |  |

| bit 7           |         |                  |           |                                    |                  |                      | bit 0 |  |  |  |

|                 |         |                  |           |                                    |                  |                      |       |  |  |  |

| Legend:         |         |                  |           |                                    |                  |                      |       |  |  |  |

| R = Readable I  | bit     | W = Writable     | bit       | U = Unimplemented bit, read as '0' |                  |                      |       |  |  |  |

| -n = Value at P | OR      | '1' = Bit is set |           | '0' = Bit is clea                  | x = Bit is unkno | wn                   |       |  |  |  |

|                 |         |                  |           |                                    |                  |                      |       |  |  |  |

## REGISTER 9-7: PMD8: PERIPHERAL MODULE DISABLE CONTROL REGISTER 8

bit 15-2 Unimplemented: Read as '0'

bit 1 CCSMD: Constant Current Source Module Disable bit<sup>(1)</sup>

1 = Constant current source module is disabled

0 = Constant current source module is enabled

bit 0 Unimplemented: Read as '0'

Note 1: This bit is not implemented in dsPIC33FJ06GS101A/102A/202A devices.

### **10.9** Peripheral Pin Select Registers

The following registers are implemented for remappable peripheral configuration:

- 15 Input Remappable Peripheral Registers

- 19 Output Remappable Peripheral Registers

- Note: Input and output register values can only be changed if IOLOCK (OSCCON<6>) = 0. See Section 10.6.3.1 "Control Register Lock" for a specific command sequence.

Not all Output Remappable Peripheral registers are implemented on all devices. See the register description of the specific register for further details.

### REGISTER 10-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0    | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1  | R/W-1 | R/W-1 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | INT1  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

|        |     |       |       |       |        |       |       |

| U-0    | U-0 | U-0   | U-0   | U-0   | U-0    | U-0   | U-0   |

| _      | _   | _     | _     | _     | _      | _     |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 7

bit 7-0

bit 13-8 INT1R<5:0>: Assign External Interrupt 1 (INTR1) to the Corresponding RPn Pin bits

| INT IN CONF. / Congri External III |

|------------------------------------|

| 111111 = Input tied to Vss         |

| 100011 = Input tied to RP35        |

| 100010 = Input tied to RP34        |

| 100001 = Input tied to RP33        |

| 100000 = Input tied to RP32        |

| •                                  |

| •                                  |

| •                                  |

| 00000 = Input tied to RP0          |

| Unimplemented: Read as '0'         |

bit 0

#### REGISTER 16-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- - 00 = Primary prescale 64:1

- Note 1: This bit is not used in Framed SPI modes. Program this bit to '0' for the Framed SPI modes (FRMEN = 1).

- 2: Do not set both Primary and Secondary prescalers to a value of 1:1.

- **3:** This bit must be cleared when FRMEN = 1.

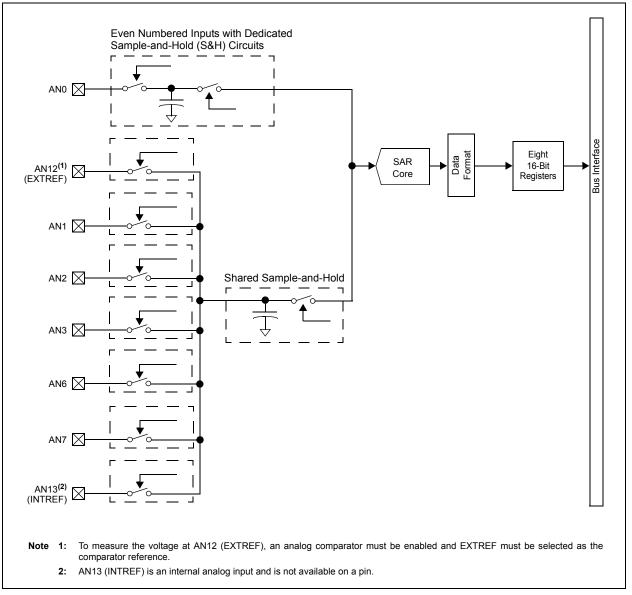

#### FIGURE 19-1: ADC BLOCK DIAGRAM FOR THE dsPIC33FJ06GS001 DEVICE

## TABLE 22-1: CONFIGURATION FLASH BYTES FOR dsPIC33FJ06GS001/101A/X02A DEVICES

| Address | Name    | Bits 23-8 | Bit 7                   | Bit 6  | Bit 5   | Bit 4                   | Bit 3 | Bit 2        | Bit 1      | Bit 0   |  |

|---------|---------|-----------|-------------------------|--------|---------|-------------------------|-------|--------------|------------|---------|--|

| 000FF0  | FICD    | _         | Reserved <sup>(1)</sup> | _      | JTAGEN  | Reserved <sup>(2)</sup> |       | _            | — ICS<1:0> |         |  |

| 000FF4  | FWDT    | —         | FWDTEN                  | —      | PLLKEN  | WDTPRE                  |       | WDTPOST<3:0> |            |         |  |

| 000FF6  | FOSC    | —         | FCKS                    | M<1:0> | IOL1WAY | —                       | —     | OSCIOFNC     | POSCM      | ID<1:0> |  |

| 000FF8  | FOSCSEL | —         | IESO                    | —      | —       | —                       | —     | FNOSC<2:0>   |            |         |  |

| 000FFA  | FGS     |           |                         |        | _       | —                       | _     |              | GCP        | GWRP    |  |

**Legend:** — = unimplemented, read as '1'.

Note 1: This bit is reserved for use by development tools.

2: This bit is reserved; program as '0'.

#### TABLE 22-2: CONFIGURATION FLASH BYTES FOR dsPIC33FJ09GS302 DEVICES

| Address | Name    | Bits 23-8 | Bit 7                   | Bit 6   | Bit 5   | Bit 4                   | Bit 3      | Bit 2        | Bit 1       | Bit 0 |  |

|---------|---------|-----------|-------------------------|---------|---------|-------------------------|------------|--------------|-------------|-------|--|

| 0017F0  | FICD    |           | Reserved <sup>(1)</sup> |         | JTAGEN  | Reserved <sup>(2)</sup> | _          | — ICS<1:0>   |             | :1:0> |  |

| 0017F4  | FWDT    | _         | FWDTEN                  | —       | PLLKEN  | WDTPRE                  |            | WDTPOST<3:0> |             |       |  |

| 0017F6  | FOSC    | _         | FCKS                    | //<1:0> | IOL1WAY | —                       | — OSCIOFNC |              | POSCMD<1:0> |       |  |

| 0017F8  | FOSCSEL | —         | IESO                    | —       | —       | —                       | —          | FNOSC<2:0>   |             |       |  |

| 0017FA  | FGS     | —         | —                       | —       |         | —                       | —          | —            | GCP         | GWRP  |  |

**Legend:** — = unimplemented, read as '1'.

**Note 1:** This bit is reserved for use by development tools.

2: This bit is reserved; program as '0'.

| TABLE 22-3: 0 | ISPIC33F CONFIGURATION BITS DESCRIPTION                                                                       |

|---------------|---------------------------------------------------------------------------------------------------------------|

| Bit Field     | Description                                                                                                   |

| GCP           | General Segment Code-Protect bit                                                                              |

|               | 1 = User program memory is not code-protected                                                                 |

|               | 0 = Code protection is enabled for the entire program memory space                                            |

| GWRP          | General Segment Write-Protect bit                                                                             |

|               | 1 = User program memory is not write-protected                                                                |

|               | 0 = User program memory is write-protected                                                                    |

| IESO          | Two-Speed Oscillator Start-up Enable bit                                                                      |

|               | 1 = Start up device with FRC, then automatically switch to the user-selected oscillator source                |

|               | when ready                                                                                                    |

|               | 0 = Start up device with user-selected oscillator source                                                      |

| FNOSC<2:0>    | Oscillator Selection bits                                                                                     |

|               | 111 = Fast RC Oscillator with divide-by-N (FRCDIVN)                                                           |

|               | 110 = Reserved; do not use                                                                                    |

|               | 101 = Low-Power RC Oscillator (LPRC)<br>100 = Reserved; do not use                                            |

|               | 011 = Primary Oscillator with PLL module (MS + PLL, EC + PLL)                                                 |

|               | 010 = Primary Oscillator (MS, HS, EC)                                                                         |

|               | 001 = Fast RC Oscillator with divide-by-N with PLL module                                                     |

|               | (FRCDIVN + PLL)                                                                                               |

|               | 000 = Fast RC Oscillator (FRC)                                                                                |

| FCKSM<1:0>    | Clock Switching Mode bits                                                                                     |

|               | 1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled                                         |

|               | 01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled                                          |

|               | 00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                           |

| IOL1WAY       | Peripheral Pin Select Configuration bit                                                                       |

|               | 1 = Allow only one reconfiguration                                                                            |

|               | 0 = Allow multiple reconfigurations                                                                           |

| OSCIOFNC      | OSC2 Pin Function bit (except in MS and HS modes)                                                             |

|               | 1 = OSC2 is the clock output                                                                                  |

|               | 0 = OSC2 is the general purpose digital I/O pin                                                               |

| POSCMD<1:0>   | Primary Oscillator Mode Select bits                                                                           |

|               | <ul><li>11 = Primary Oscillator is disabled</li><li>10 = HS Crystal Oscillator mode (10 MHz-32 MHz)</li></ul> |

|               | 01 = MS Crystal Oscillator mode (3 MHz-10 MHz)                                                                |

|               | 00 = EC (External Clock) mode (DC-32 MHz)                                                                     |

| FWDTEN        | Watchdog Timer Enable bit                                                                                     |

|               | 1 = Watchdog Timer is always enabled (LPRC oscillator cannot be disabled; clearing the SWDTEN                 |

|               | bit in the RCON register will have no effect)                                                                 |

|               | 0 = Watchdog Timer is enabled/disabled by user software (LPRC can be disabled by clearing                     |

|               | the SWDTEN bit in the RCON register)                                                                          |

| WDTPRE        | Watchdog Timer Prescaler bit                                                                                  |

|               | 1 = 1:128                                                                                                     |

|               | 0 = 1:32                                                                                                      |

| WDTPOST<3:0>  | Watchdog Timer Postscaler bits                                                                                |

|               | 1111 = 1:32,768                                                                                               |

|               | 1110 <b>= 1:16,384</b>                                                                                        |

|               | •                                                                                                             |

|               | •                                                                                                             |

|               | •                                                                                                             |

|               | 0001 = 1:2                                                                                                    |

|               | 0000 = 1:1                                                                                                    |

## TABLE 22-3: dsPIC33F CONFIGURATION BITS DESCRIPTION

### 25.1 DC Characteristics

|                | Voo Bango                | Tomp Bongo            | Maximum MIPS                                            |

|----------------|--------------------------|-----------------------|---------------------------------------------------------|

| Characteristic | VDD Range<br>(in Volts)  | Temp Range<br>(in °C) | dsPIC33FJ06GS001/101A/102A/202A<br>and dsPIC33FJ09GS302 |

|                | VBOR-3.6V <sup>(1)</sup> | -40°C to +85°C        | 40                                                      |

| —              | VBOR-3.6V <sup>(1)</sup> | -40°C to +125°C       | 40                                                      |

**Note 1:** Overall functional device operation at VBORMIN < VDD < VDDMIN is tested but not characterized. All device analog modules, such as the ADC, etc., will function but with degraded performance below VDDMIN. Refer to Parameter BO10 in Table 25-11 for BOR values.

### TABLE 25-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                            | Symbol | Min. | Тур.        | Max. | Unit |

|---------------------------------------------------------------------------------------------------|--------|------|-------------|------|------|

| Industrial Temperature Devices                                                                    |        |      |             |      |      |

| Operating Junction Temperature Range                                                              | TJ     | -40  | _           | +125 | °C   |

| Operating Ambient Temperature Range                                                               | TA     | -40  | _           | +85  | °C   |

| Extended Temperature Devices                                                                      |        |      |             |      |      |

| Operating Junction Temperature Range                                                              | TJ     | -40  | —           | +140 | °C   |

| Operating Ambient Temperature Range                                                               | TA     | -40  | —           | +125 | °C   |

| Power Dissipation<br>Internal Chip Power Dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$        | PD     | I    | PINT + PI/c | D    | W    |

| I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} \times IOH) + \Sigma (VOL \times IOL)$ |        |      |             |      |      |

| Maximum Allowed Power Dissipation                                                                 | PDMAX  | (    | TJ — TA)/θJ | IA   | W    |

### TABLE 25-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                           | Symbol | Тур. | Max. | Unit | Notes |

|------------------------------------------|--------|------|------|------|-------|

| Package Thermal Resistance, 18-Pin SOIC  | θJA    | 57   |      | °C/W | 1     |

| Package Thermal Resistance, 18-pin PDIP  | θJA    | 66   | -    | °C/W | 1     |

| Package Thermal Resistance, 20-pin SSOP  | θJA    | 64   | —    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin QFN-S | θJA    | 34   |      | °C/W | 1     |

| Package Thermal Resistance, 28-pin SSOP  | θJA    | 71   | -    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SOIC  | θJA    | 47   | _    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SPDIP | θJA    | 45   |      | °C/W | 1     |

| Package Thermal Resistance, 36-Pin VTLA  | θJA    | 29   | _    | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

| AC CHARACTERISTICS |                                                                 | $\begin{array}{ll} \mbox{Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |       |                                                                 |                |  |  |

|--------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-----------------------------------------------------------------|----------------|--|--|

| Param.             | Characteristic                                                  | Min.                                                                                                                                                                                                                                                                         | Тур. | Max. | Units | Conditions                                                      |                |  |  |

|                    | Internal FRC Accuracy @ FRC Frequency = 7.37 MHz <sup>(1)</sup> |                                                                                                                                                                                                                                                                              |      |      |       |                                                                 |                |  |  |

| F20a               | FRC                                                             | -2                                                                                                                                                                                                                                                                           | _    | +2   | %     | $-40^\circ C \le T A \le +85^\circ C$                           | VDD = 3.0-3.6V |  |  |

| F20b               | FRC                                                             | -5                                                                                                                                                                                                                                                                           | _    | +5   | %     | $-40^{\circ}C \leq TA \leq +125^{\circ}C \qquad VDD = 3.0-3.6V$ |                |  |  |

#### TABLE 25-19: AC CHARACTERISTICS: INTERNAL FRC ACCURACY

**Note 1:** Frequency is calibrated at +25°C and 3.3V. TUNx bits can be used to compensate for temperature drift.

### TABLE 25-20: INTERNAL LPRC ACCURACY

| AC CHARACTERISTICS |                                  | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |      |       |                                        |                |  |

|--------------------|----------------------------------|------------------------------------------------------|------|------|-------|----------------------------------------|----------------|--|

| Param.             | Characteristic                   | Min.                                                 | Тур. | Max. | Units | Conditions                             |                |  |

|                    | LPRC @ 32.768 kHz <sup>(1)</sup> |                                                      |      |      |       |                                        |                |  |

| F21a               | LPRC                             | -20                                                  | _    | +20  | %     | $-40^{\circ}C \le TA \le +85^{\circ}C$ | VDD = 3.0-3.6V |  |

| F21b               | LPRC                             | -70                                                  | _    | +70  | %     | $-40^\circ C \le T A \le +125^\circ C$ | VDD = 3.0-3.6V |  |

**Note 1:** The change of LPRC frequency as VDD changes.

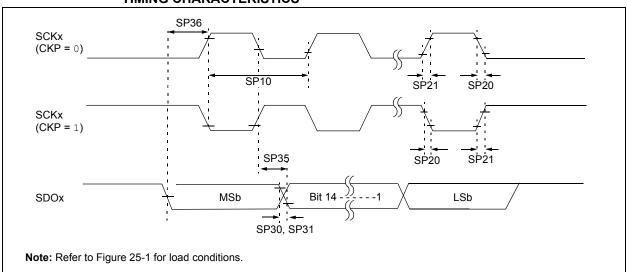

#### FIGURE 25-12: SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 1) TIMING CHARACTERISTICS

### TABLE 25-30: SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                              |     | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industria $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |     |       |                                      |  |

|--------------------|-----------------------|----------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|--------------------------------------|--|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                | Min | Тур <sup>(2)</sup>                                                                                                                                                                                  | Max | Units | Conditions                           |  |

| SP10               | TscP                  | Maximum SCKx Frequency                       | —   |                                                                                                                                                                                                     | 15  | MHz   | See Note 3                           |  |

| SP20               | TscF                  | SCKx Output Fall Time                        | —   | _                                                                                                                                                                                                   | _   | ns    | See Parameter DO32 and <b>Note 4</b> |  |

| SP21               | TscR                  | SCKx Output Rise Time                        | —   | _                                                                                                                                                                                                   | _   | ns    | See Parameter DO31 and <b>Note 4</b> |  |

| SP30               | TdoF                  | SDOx Data Output Fall Time                   | —   | —                                                                                                                                                                                                   | _   | ns    | See Parameter DO32 and <b>Note 4</b> |  |

| SP31               | TdoR                  | SDOx Data Output Rise Time                   | —   |                                                                                                                                                                                                     | _   | ns    | See Parameter DO31 and <b>Note 4</b> |  |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge    | —   | 6                                                                                                                                                                                                   | 20  | ns    |                                      |  |

| SP36               | TdiV2scH,<br>TdiV2scL | SDOx Data Output Setup to<br>First SCKx Edge | 30  | —                                                                                                                                                                                                   | _   | ns    |                                      |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

**2:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 66.7 ns. Therefore, the clock generated in master mode must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

NOTES:

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 157                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| RPOR0 (Peripheral Pin Select Output 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 168                                                                                             |

| RPOR1 (Peripheral Pin Select Output 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 168                                                                                             |

| RPOR16 (Peripheral Pin Select Output 16)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                 |

| RPOR17 (Peripheral Pin Select Output 17)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                 |

| RPOR2 (Peripheral Pin Select Output 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 169                                                                                             |

| RPOR3 (Peripheral Pin Select Output 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                 |

| RPOR4 (Peripheral Pin Select Output 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                 |

| RPOR5 (Peripheral Pin Select Output 5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                 |

| RPOR6 (Peripheral Pin Select Output 6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                 |

| RPOR7 (Peripheral Pin Select Output 7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 171                                                                                             |

| SDCx (PWMx Secondary Duty Cycle)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                 |

| SEVTCMP (PWM Special Event Compare)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                 |

| SPHASEx (PWMx Secondary Phase Shift)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 194                                                                                             |

| SPIxCON1 (SPIx Control 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 208                                                                                             |

| SPIxCON2 (SPIx Control 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                 |

| SPIxSTAT (SPIx Status and Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                 |

| SR (CPU STATUS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                 |

| SR (CPU Status)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                 |

| STRIGx (PWMx Secondary Trigger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                 |

| Compare Value)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                 |

| T1CON (Timer1 Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                 |

| T2CON (Timer2 Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                 |

| TRGCONx (PWMx Trigger Control)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 196                                                                                             |

| TRIGx (PWMx Primary Trigger Compare Value)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                 |

| U1MODE (UART1 Mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                 |