#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

XH

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 13                                                                              |

| Program Memory Size        | 6KB (2K x 24)                                                                   |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 256 x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 18-PDIP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs101a-e-p |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

#### TABLE 4-34: PMD REGISTER MAP FOR dsPIC33FJ06GS001

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| PMD1        | 0770        | _      | _      | _      | T2MD   | T1MD   | _      | PWMMD  | -      | I2C1MD | _     | —     | —     |        | _     |       | ADCMD | 0000          |

| PMD3        | 0774        | _      | _      | _      | _      | _      | CMPMD  | _      | _      | _      | _     | _     | _     | _      | _     | _     | _     | 0000          |

| PMD4        | 0776        | _      | _      | _      |        | —      | _      |        |        | _      |       | —     | —     | REFOMD | _     | _     | _     | 0000          |

| PMD6        | 077A        | _      | _      | _      |        | PWM4MD | _      |        | PWM1MD | _      |       | —     | —     |        | _     | _     | _     | 0000          |

| PMD7        | 077C        | _      | _      | _      |        | —      | _      | CMPMD2 | CMPMD1 | _      | _     | _     | —     |        | _     | _     | _     | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-35: PMD REGISTER MAP FOR dsPIC33FJ06GS101A

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|--------|--------|--------|--------|--------|--------|-------|--------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| PMD1        | 0770        |        | —      |        | T2MD   | T1MD   | _      | PWMMD | -      | I2C1MD |       | U1MD  | _     | SPI1MD | _     | _     | ADCMD | 0000          |

| PMD2        | 0772        | _      | _      | _      |        | _      | _      |       | _      |        |       | —     | _     |        | _     |       | OC1MD | 0000          |

| PMD4        | 0776        | _      | _      | _      | _      | _      | _      | _     | _      | _      | _     |       | _     | REFOMD |       | _     | _     | 0000          |

| PMD6        | 077A        | —      | _      | -      |        | PWM4MD | _      | -     | PWM1MD |        |       | _     | —     |        | _     |       |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-36: PMD REGISTER MAP FOR dsPIC33FJ06GS102A

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| PMD1        | 0770        |        |        | _      | T2MD   | T1MD   | _      | PWMMD  | _      | I2C1MD | _     | U1MD  | _     | SPI1MD | _     | _     | ADCMD | 0000          |

| PMD2        | 0772        | _      | _      | _      | _      | _      | _      | _      | _      | _      |       | _     | _     | _      | _     | _     | OC1MD | 0000          |

| PMD4        | 0776        | _      | _      | _      | _      | _      | _      | _      | _      | _      |       | _     | _     | REFOMD | _     | _     | _     | 0000          |

| PMD6        | 077A        | _      | _      | _      | _      | _      | _      | PWM2MD | PWM1MD | _      | _     | —     | _     | -      | _     | —     | _     | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS001/101A/102A/ 202A and dsPIC33FJ09GS302 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 41. "Interrupts (Part IV)" (DS70300) in the "dsPIC33F/ PIC24H Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the CPU. The controller has the following features:

- Up to eight processor exceptions and software traps

- Seven user-selectable priority levels

- Interrupt Vector Table (IVT) with up to 118 vectors

- A unique vector for each interrupt or exception source

- Fixed priority within a specified user priority level

- Alternate Interrupt Vector Table (AIVT) for debug support

- Fixed interrupt entry and return latencies

### 7.1 Interrupt Vector Table

The Interrupt Vector Table (IVT) is shown in Figure 7-1. The IVT resides in program memory, starting at location, 000004h. The IVT contains 126 vectors, consisting of eight non-maskable trap vectors, plus up to 118 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR). Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 will take priority over interrupts at any other vector address.

The devices implement up to 28 unique interrupts and four non-maskable traps. These are summarized in Table 7-1.

#### 7.1.1 ALTERNATE INTERRUPT VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT) is located after the IVT, as shown in Figure 7-1. Access to the AIVT is provided by the ALTIVT control bit (INTCON2<15>). If the ALTIVT bit is set, all interrupt and exception processes use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors.

The AIVT supports debugging by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time. If the AIVT is not needed, the AIVT should be programmed with the same addresses used in the IVT.

#### 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. A device clears its registers in response to a Reset, which forces the PC to zero. The digital signal controller then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT and AIVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

| <b>REGISTER 7</b>                     | -1: SR: C               | PU STATUS I          | REGISTER          | )              |                  |        |       |

|---------------------------------------|-------------------------|----------------------|-------------------|----------------|------------------|--------|-------|

| R-0                                   | R-0                     | R/C-0                | R/C-0             | R-0            | R/C-0            | R-0    | R/W-0 |

| OA                                    | OB                      | SA                   | SB                | OAB            | SAB              | DA     | DC    |

| bit 15                                |                         |                      |                   |                |                  |        | bit 8 |

|                                       |                         |                      |                   |                |                  |        |       |

| R/W-0 <sup>(3)</sup>                  | R/W-0 <sup>(3)</sup>    | R/W-0 <sup>(3)</sup> | R-0               | R/W-0          | R/W-0            | R/W-0  | R/W-0 |

|                                       | IPL<2:0> <sup>(2)</sup> |                      | RA                | N              | OV               | Z      | С     |

| bit 7                                 |                         |                      |                   |                |                  |        | bit 0 |

|                                       |                         |                      |                   |                |                  |        |       |

| Legend:                               |                         | C = Clearable        | bit               | U = Unimpler   | nented bit, read | as '0' |       |

| R = Readable bit W = Writable bit     |                         | bit                  | -n = Value at POR |                |                  |        |       |

| '1' = Bit is set '0' = Bit is cleared |                         |                      | ared              | x = Bit is unk | nown             |        |       |

### (4)

bit 7-5 IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2,3)</sup>

111 = CPU Interrupt Priority Level is 7 (15), user interrupts are disabled

- 110 = CPU Interrupt Priority Level is 6 (14)

- 101 = CPU Interrupt Priority Level is 5 (13)

- 100 = CPU Interrupt Priority Level is 4 (12)

- 011 = CPU Interrupt Priority Level is 3 (11)

- 010 = CPU Interrupt Priority Level is 2 (10) 001 = CPU Interrupt Priority Level is 1 (9)

- 000 = CPU Interrupt Priority Level is 0 (8)

- Note 1: For complete register details, see Register 3-1.

#### 2: The IPL<2:0> bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL3 = 1. User interrupts are disabled when IPL3 = 1.

3: The IPL<2:0> status bits are read-only when NSTDIS (INTCON1<15>) = 1.

#### CORCON: CORE CONTROL REGISTER<sup>(1)</sup> **REGISTER 7-2:**

|         |       | •••••         |        |                     |       |         |       |

|---------|-------|---------------|--------|---------------------|-------|---------|-------|

| U-0     | U-0   | U-0           | R/W-0  | R/W-0               | R-0   | R-0     | R-0   |

| _       | —     | _             | US     | EDT                 |       | DL<2:0> |       |

| bit 15  |       |               |        |                     |       |         | bit 8 |

|         |       |               |        |                     |       |         |       |

| R/W-0   | R/W-0 | R/W-1         | R/W-0  | R/C-0               | R/W-0 | R/W-0   | R/W-0 |

| SATA    | SATB  | SATDW         | ACCSAT | IPL3 <sup>(2)</sup> | PSV   | RND     | IF    |

| bit 7   |       |               |        |                     |       |         | bit 0 |

|         |       |               |        |                     |       |         |       |

| Legend: |       | C = Clearable | e bit  |                     |       |         |       |

|         |       |               |        |                     |       |         |       |

| R = Readable bit    | W = Writable bit    | -n = Value at POR           | '1' = Bit is set |

|---------------------|---------------------|-----------------------------|------------------|

| 0' = Bit is cleared | 'x = Bit is unknown | U = Unimplemented bit, read | 1 as '0'         |

|                     |                     |                             |                  |

IPL3: CPU Interrupt Priority Level Status bit 3(2) bit 3

- 1 = CPU Interrupt Priority Level is greater than 7

- 0 = CPU Interrupt Priority Level is 7 or less

#### Note 1: For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

| U-0          | U-0                                                                                        | R/W-0                                | U-0             | U-0                          | U-0                 | U-0             | U-0     |  |  |  |

|--------------|--------------------------------------------------------------------------------------------|--------------------------------------|-----------------|------------------------------|---------------------|-----------------|---------|--|--|--|

| —            |                                                                                            | INT2IF                               |                 |                              |                     |                 | _       |  |  |  |

| bit 15       |                                                                                            |                                      |                 |                              |                     |                 | bit 8   |  |  |  |

|              |                                                                                            |                                      |                 |                              |                     |                 |         |  |  |  |

| U-0          | U-0                                                                                        | U-0                                  | R/W-0           | R/W-0                        | R/W-0               | R/W-0           | R/W-0   |  |  |  |

| —            | —                                                                                          | —                                    | INT1IF          | CNIF                         | AC1IF <sup>(1</sup> | MI2C1IF         | SI2C1IF |  |  |  |

| bit 7        |                                                                                            |                                      |                 |                              |                     |                 | bit     |  |  |  |

| Legend:      |                                                                                            |                                      |                 |                              |                     |                 |         |  |  |  |

| R = Readab   | le bit                                                                                     | W = Writable                         | bit             | U = Unimpler                 | mented bit, read    | 1 as '0'        |         |  |  |  |

| -n = Value a |                                                                                            | '1' = Bit is set                     |                 | '0' = Bit is cle             |                     | x = Bit is unki | าดพท    |  |  |  |

|              |                                                                                            |                                      |                 |                              |                     |                 | -       |  |  |  |

| bit 15-14    | Unimplemen                                                                                 | ted: Read as '                       | 0'              |                              |                     |                 |         |  |  |  |

| bit 13       | INT2IF: External Interrupt 2 Flag Status bit                                               |                                      |                 |                              |                     |                 |         |  |  |  |

|              |                                                                                            | request has oc                       |                 |                              |                     |                 |         |  |  |  |

|              | •                                                                                          | request has no                       |                 |                              |                     |                 |         |  |  |  |

| bit 12-5     | -                                                                                          | ited: Read as '                      |                 |                              |                     |                 |         |  |  |  |

| bit 4        |                                                                                            | rnal Interrupt 1                     | •               | t                            |                     |                 |         |  |  |  |

|              |                                                                                            | request has oc<br>request has no     |                 |                              |                     |                 |         |  |  |  |

| bit 3        | -                                                                                          | Change Notifica                      |                 | Flag Status hit              |                     |                 |         |  |  |  |

| bit 0        |                                                                                            | request has oc                       |                 | r lag Olalas bit             |                     |                 |         |  |  |  |

|              |                                                                                            | request has no                       |                 |                              |                     |                 |         |  |  |  |

| bit 2        | AC1IF: Analo                                                                               | og Comparator                        | 1 Interrupt Fla | ig Status bit <sup>(1)</sup> |                     |                 |         |  |  |  |

|              |                                                                                            | request has oc                       |                 |                              |                     |                 |         |  |  |  |

|              | 0 = Interrupt request has not occurred                                                     |                                      |                 |                              |                     |                 |         |  |  |  |

| bit 1        | MI2C1IF: I2C1 Master Events Interrupt Flag Status bit                                      |                                      |                 |                              |                     |                 |         |  |  |  |

|              |                                                                                            | request has oc                       |                 |                              |                     |                 |         |  |  |  |

|              | -                                                                                          | = Interrupt request has not occurred |                 |                              |                     |                 |         |  |  |  |

| oit O        | SI2C1IF: I2C1 Slave Events Interrupt Flag Status bit<br>1 = Interrupt request has occurred |                                      |                 |                              |                     |                 |         |  |  |  |

| bit 0        |                                                                                            |                                      |                 |                              |                     |                 |         |  |  |  |

Note 1: This bit is not implemented in dsPIC33FJ06GS101A/102A devices.

| U-0                               | U-0           | U-0                                    | U-0             | U-0                                     | U-0                          | U-0          | U-0   |  |  |  |  |

|-----------------------------------|---------------|----------------------------------------|-----------------|-----------------------------------------|------------------------------|--------------|-------|--|--|--|--|

| _                                 | _             | _                                      |                 | _                                       |                              | —            | —     |  |  |  |  |

| bit 15                            |               |                                        |                 |                                         |                              |              | bit 8 |  |  |  |  |

| U-0                               | R/W-1         | R/W-0                                  | R/W-0           | U-0                                     | R/W-1                        | R/W-0        | R/W-0 |  |  |  |  |

| _                                 |               | ADCP3IP<2:0>                           | 1)              |                                         |                              | DCP2IP<2:0>( | 2)    |  |  |  |  |

| bit 7                             |               |                                        |                 |                                         |                              |              | bit 0 |  |  |  |  |

|                                   |               |                                        |                 |                                         |                              |              |       |  |  |  |  |

| Legend:                           |               |                                        |                 |                                         |                              |              |       |  |  |  |  |

| R = Readabl                       | e bit         | W = Writable                           | bit             | U = Unimpler                            | nented bit, read             | d as '0'     |       |  |  |  |  |

| n = Value at POR '1' = Bit is set |               |                                        |                 | '0' = Bit is cleared x = Bit is unknown |                              |              |       |  |  |  |  |

|                                   |               |                                        |                 |                                         |                              |              |       |  |  |  |  |

| bit 15-7                          | Unimplemer    | nted: Read as '                        | 0'              |                                         |                              |              |       |  |  |  |  |

| bit 6-4                           | ADCP3IP<2:    | : <b>0&gt;:</b> ADC Pair 3             | B Conversion    | Done Interrupt I                        | Priority bits <sup>(1)</sup> |              |       |  |  |  |  |

|                                   | 111 = Interru | pt is Priority 7                       | (highest priori | ty interrupt)                           |                              |              |       |  |  |  |  |

|                                   | •             |                                        |                 |                                         |                              |              |       |  |  |  |  |

|                                   | •             |                                        |                 |                                         |                              |              |       |  |  |  |  |

|                                   |               | ipt is Priority 1<br>ipt source is dis | abled           |                                         |                              |              |       |  |  |  |  |

| bit 3                             | Unimplemer    | nted: Read as '                        | 0'              |                                         |                              |              |       |  |  |  |  |

| bit 2-0                           | ADCP2IP<2:    | : <b>0&gt;:</b> ADC Pair 2             | 2 Conversion    | Done Interrupt I                        | Priority bits <sup>(2)</sup> |              |       |  |  |  |  |

|                                   | 111 = Interru | pt is Priority 7                       | (highest priori | ty interrupt)                           |                              |              |       |  |  |  |  |

|                                   | •             |                                        |                 |                                         |                              |              |       |  |  |  |  |

|                                   | •             |                                        |                 |                                         |                              |              |       |  |  |  |  |

|                                   |               | 001 = Interrupt is Priority 1          |                 |                                         |                              |              |       |  |  |  |  |

|                                   | 001 = Interru | pt is Priority 1                       |                 |                                         |                              |              |       |  |  |  |  |

- **Note 1:** These bits are not implemented in dsPIC33FJ06GS102A/202A devices.

- **2**: These bits are not implemented in dsPIC33FJ06GS001/101A devices.

| REGISTER 9                         | -3: PMD3 | 3: PERIPHER | AL MODULE | DISABLE C                               | ONTROL RE            | GISTER 3 |       |  |

|------------------------------------|----------|-------------|-----------|-----------------------------------------|----------------------|----------|-------|--|

| U-0                                | U-0      | U-0         | U-0       | U-0                                     | R/W-0                | U-0      | U-0   |  |

| —                                  | —        | —           | —         | —                                       | CMPMD <sup>(1)</sup> | —        | —     |  |

| bit 15                             |          |             |           |                                         |                      |          | bit 8 |  |

|                                    |          |             |           |                                         |                      |          |       |  |

| U-0                                | U-0      | U-0         | U-0       | U-0                                     | U-0                  | U-0      | U-0   |  |

| _                                  |          | —           |           |                                         |                      | _        | —     |  |

| bit 7                              |          |             |           |                                         |                      |          | bit 0 |  |

|                                    |          |             |           |                                         |                      |          |       |  |

| Legend:                            |          |             |           |                                         |                      |          |       |  |

| R = Readable bit W = Writable bit  |          |             | bit       | U = Unimplemented bit, read as '0'      |                      |          |       |  |

| -n = Value at POR (1' = Bit is set |          |             |           | '0' = Bit is cleared x = Bit is unknown |                      |          |       |  |

#### DECISTED 0 2. AL MODULE DISABLE CONTROL DECISTED 2 DMD2. DE

| bit 15-11 | <b>Unimplemented:</b> | Read as '0' | , |

|-----------|-----------------------|-------------|---|

|           |                       |             |   |

| bit 10  | CMPMD: Analog Comparator Module Disable bit <sup>(1)</sup> |

|---------|------------------------------------------------------------|

|         | 1 = Analog comparator module is disabled                   |

|         | 0 = Analog comparator module is enabled                    |

| bit 9-0 | Unimplemented: Read as '0'                                 |

Note 1: This bit is not implemented in dsPIC33FJ06GS101A/102A devices.

#### **REGISTER 9-4:** PMD4: PERIPHERAL MODULE DISABLE CONTROL REGISTER 4

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/W-0  | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|--------|-----|-----|-------|

| —     | —   | —   | —   | REFOMD | —   | —   | —     |

| bit 7 |     |     |     |        |     |     | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | id as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-4 | Unimplemented: Read as '0'                           |

|----------|------------------------------------------------------|

| bit 3    | REFOMD: Reference Clock Generator Module Disable bit |

|          | 1 = Reference clock generator module is disabled     |

|          | 0 = Reference clock generator module is enabled      |

| bit 2-0  | Unimplemented: Read as '0'                           |

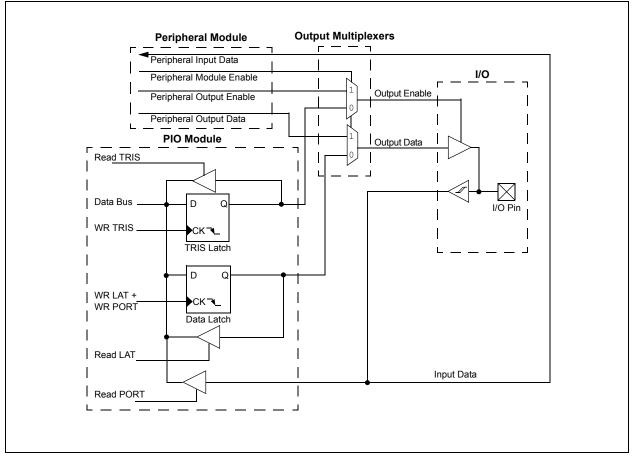

#### FIGURE 10-1: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

#### 12.2 Timer2 Control Register

#### REGISTER 12-1: T2CON: TIMER2 CONTROL REGISTER

| R/W-0                 | U-0                                 | R/W-0                        | U-0           | U-0               | U-0             | U-0             | U-0   |

|-----------------------|-------------------------------------|------------------------------|---------------|-------------------|-----------------|-----------------|-------|

| TON                   |                                     | TSIDL                        | —             | _                 | _               | _               |       |

| bit 15                | ·                                   |                              |               |                   |                 |                 | bit 8 |

|                       |                                     |                              |               |                   |                 |                 |       |

| U-0                   | R/W-0                               | R/W-0                        | R/W-0         | U-0               | U-0             | R/W-0           | U-0   |

| —                     | TGATE                               | TCKPS                        | S<1:0>        | —                 |                 | TCS             | —     |

| bit 7                 |                                     |                              |               |                   |                 |                 | bit ( |

| Levende               |                                     |                              |               |                   |                 |                 |       |

| Legend:<br>R = Readat | alo hit                             | W = Writable                 | hit           |                   | nented bit, rea | d as '0'        |       |

|                       |                                     |                              | DIL           | -                 |                 |                 |       |

| -n = Value a          | al POR                              | '1' = Bit is set             |               | '0' = Bit is cle  | ared            | x = Bit is unkn | own   |

| bit 15                | TON: Timerx                         | On hit                       |               |                   |                 |                 |       |

|                       | 1 = Starts 16-                      |                              |               |                   |                 |                 |       |

|                       | 0 = Stops 16-                       |                              |               |                   |                 |                 |       |

| bit 14                | Unimplemen                          | ted: Read as '               | ) <b>'</b>    |                   |                 |                 |       |

| bit 13                | TSIDL: Stop                         | in Idle Mode bit             |               |                   |                 |                 |       |

|                       | 1 = Discontin                       | ues timer opera              | ation when de | evice enters Idle | e mode          |                 |       |

|                       | 0 = Continue                        | s timer operatio             | n in Idle moo | le                |                 |                 |       |

| bit 12-7              | Unimplemen                          | ted: Read as '               | כי            |                   |                 |                 |       |

| bit 6                 | TGATE: Time                         | erx Gated Time               | Accumulatio   | n Enable bit      |                 |                 |       |

|                       | When TCS =                          |                              |               |                   |                 |                 |       |

|                       | This bit is ign                     |                              |               |                   |                 |                 |       |

|                       | <u>When TCS =</u> $1 = Cotod times$ | <u>0:</u><br>ne accumulatior | ia anablad    |                   |                 |                 |       |

|                       |                                     | ne accumulation              |               |                   |                 |                 |       |

| bit 5-4               | TCKPS<1:0>                          | : Timerx Input               | Clock Presca  | le Select bits    |                 |                 |       |

|                       | 11 = 1:256 pi                       |                              |               |                   |                 |                 |       |

|                       | 10 = 1:64 pre                       |                              |               |                   |                 |                 |       |

|                       | 01 = 1:8 pres                       |                              |               |                   |                 |                 |       |

|                       | 00 = 1:1 pres                       |                              |               |                   |                 |                 |       |

| bit 3-2               | •                                   | ted: Read as '               |               |                   |                 |                 |       |

| bit 1                 |                                     | Clock Source S               |               |                   |                 |                 |       |

|                       |                                     | clock from T2C               | K pin         |                   |                 |                 |       |

|                       |                                     |                              |               |                   |                 |                 |       |

| bit 0                 |                                     | lock (Fosc/2)                |               |                   |                 |                 |       |

| REGISTER 15-7: | PDCx: PWMx GENERATOR DUTY CYCLE REGISTER <sup>(1)</sup> |

|----------------|---------------------------------------------------------|

|                |                                                         |

| R/W-0                              | R/W-0 | R/W-0          | R/W-0 | R/W-0                 | R/W-0           | R/W-0           | R/W-0 |

|------------------------------------|-------|----------------|-------|-----------------------|-----------------|-----------------|-------|

|                                    |       |                | PDCx  | <15:8> <sup>(2)</sup> |                 |                 |       |

| bit 15                             |       |                |       |                       |                 |                 | bit 8 |

|                                    |       |                |       |                       |                 |                 |       |

| R/W-0                              | R/W-0 | R/W-0          | R/W-0 | R/W-0                 | R/W-0           | R/W-0           | R/W-0 |

|                                    |       |                | PDC   | <7:0> <sup>(2)</sup>  |                 |                 |       |

| bit 7                              |       |                |       |                       |                 |                 | bit 0 |

|                                    |       |                |       |                       |                 |                 |       |

| Legend:                            |       |                |       |                       |                 |                 |       |

| R = Readable                       | bit   | W = Writable b | bit   | U = Unimpler          | mented bit, rea | d as '0'        |       |

| -n = Value at POR '1' = Bit is set |       |                |       | '0' = Bit is cle      | ared            | x = Bit is unki | nown  |

bit 15-0 PDCx<15:0>: PWMx Generator # Duty Cycle Value bits<sup>(2)</sup>

- **Note 1:** In Independent PWM mode, the PDCx register controls the PWMxH duty cycle only. In Complementary, Redundant and Push-Pull PWM modes, the PDCx register controls the duty cycle of both the PWMxH and PWMxL. The smallest pulse width that can be generated on the PWM output corresponds to a value of 0x0009, while the maximum pulse width generated corresponds to a value of Period-0x0008.

- 2: As the duty cycle gets closer to 0% or 100% of the PWM period (0 ns-40 ns, depending on the mode of operation), the PWM duty cycle resolution will degrade from 1 LSB to 3 LSBs.

| R/W-0                              | R/W-0 | R/W-0          | R/W-0 | R/W-0                 | R/W-0           | R/W-0           | R/W-0 |

|------------------------------------|-------|----------------|-------|-----------------------|-----------------|-----------------|-------|

|                                    |       |                | SDCx  | <15:8> <sup>(2)</sup> |                 |                 |       |

| bit 15                             |       |                |       |                       |                 |                 | bit 8 |

|                                    |       |                |       |                       |                 |                 |       |

| R/W-0                              | R/W-0 | R/W-0          | R/W-0 | R/W-0                 | R/W-0           | R/W-0           | R/W-0 |

|                                    |       |                | SDC>  | <7:0> <sup>(2)</sup>  |                 |                 |       |

| bit 7                              |       |                |       |                       |                 |                 | bit 0 |

|                                    |       |                |       |                       |                 |                 |       |

| Legend:                            |       |                |       |                       |                 |                 |       |

| R = Readable                       | bit   | W = Writable b | oit   | U = Unimpler          | mented bit, rea | ad as '0'       |       |

| -n = Value at POR '1' = Bit is set |       |                |       | '0' = Bit is cle      | ared            | x = Bit is unkr | nown  |

#### REGISTER 15-8: SDCx: PWMx SECONDARY DUTY CYCLE REGISTER<sup>(1)</sup>

bit 15-0 SDCx<15:0>: Secondary Duty Cycle for PWMxL Output Pin bits<sup>(2)</sup>

- **Note 1:** The SDCx register is used in Independent PWM mode only. When used in Independent PWM mode, the SDCx register controls the PWMxL duty cycle. The smallest pulse width that can be generated on the PWM output corresponds to a value of 0x0009, while the maximum pulse width generated corresponds to a value of Period-0x0008.

- 2: As the duty cycle gets closer to 0% or 100% of the PWM period (0 ns-40 ns, depending on the mode of operation), the PWM duty cycle resolution will degrade from 1 LSB to 3 LSBs.

NOTES:

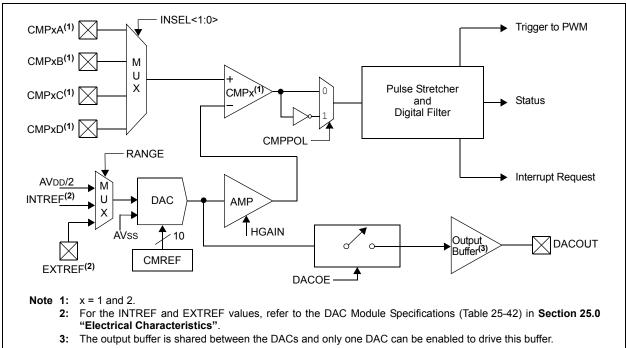

### 20.0 HIGH-SPEED ANALOG COMPARATOR

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS001/101A/102A/ 202A and dsPIC33FJ09GS302 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 45. "High-Speed Analog Comparator" (DS70296) in the "dsPIC33F/PIC24H Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The high-speed analog comparator module monitors current and/or voltage transients that may be too fast for the CPU and ADC to capture.

#### 20.1 Features Overview

The SMPS comparator module offers the following major features:

- · Eight selectable comparator inputs

- · Up to two analog comparators

- · 10-bit DAC for each analog comparator

- · Programmable output polarity

- Interrupt generation capability

- DACOUT pin to provide DAC output

- DACOUT amplifier (1x, 1.8x)

- Selectable hysteresis

- · DAC has three ranges of operation:

- AVDD/2

- Internal Reference (INTREF)

- External Reference (EXTREF)

- · ADC sample and convert trigger capability

- · Disable capability reduces power consumption

- · Functional support for PWM module:

- PWM duty cycle control

- PWM period control

- PWM Fault detect

#### 20.2 Module Description

Figure 20-1 shows a functional block diagram of one analog comparator from the high-speed analog comparator module. The analog comparator provides high-speed operation with a typical delay of 20 ns. The comparator has a typical offset voltage of  $\pm 5$  mV. The negative input of the comparator is always connected to the DAC circuit. The positive input of the comparator is connected to an analog multiplexer that selects the desired source pin.

The analog comparator input pins are typically shared with pins used by the Analog-to-Digital Converter (ADC) module. Both the comparator and the ADC can use the same pins at the same time. This capability enables a user to measure an input voltage with the ADC and detect voltage transients with the comparator.

FIGURE 20-1: HIGH-SPEED ANALOG COMPARATOR MODULE BLOCK DIAGRAM

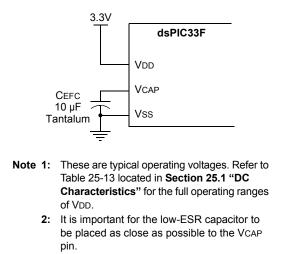

#### 22.2 On-Chip Voltage Regulator

The devices power their core digital logic at a nominal 2.5V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. When the regulator is enabled, a low-ESR (less than 5 ohms) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (Figure 22-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 25-13, located in **Section 25.1 "DC Characteristics"**.

**Note:** It is important for the low-ESR capacitor to be placed as close as possible to the VCAP pin.

On a POR, it takes approximately 20 µs for the on-chip voltage regulator to generate an output voltage. During this time, designated as TSTARTUP, code execution is disabled. TSTARTUP is applied every time the device resumes operation after any power-down.

#### FIGURE 22-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR<sup>(1,2,3)</sup>

**3:** Typical VCAP pin voltage = 2.5V when  $VDD \ge VDDMIN$ .

#### 22.3 Brown-out Reset (BOR)

The Brown-out Reset (BOR) module is based on an internal voltage reference circuit. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse which resets the device. The BOR selects the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).

If an oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until the OST expires. If the PLL is used, the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the PWRT time-out (TPWRT) is applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of, TFSCM = 100, is applied. The total delay in this case is TFSCM.

The BOR status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle modes and resets the device should VDD fall below the BOR threshold voltage.

#### 22.5 JTAG Interface

A JTAG interface is implemented, which supports boundary scan device testing, as well as in-circuit programming. Detailed information on this interface will be provided in future revisions of this document.

#### 22.6 In-Circuit Serial Programming

dsPIC33FJ06GS001/101A/102A/202A The and dsPIC33FJ09GS302 family of digital signal controllers can be serially programmed while in the end application circuit. This is done with two lines for clock and data, and three other lines for power, ground and the programming sequence. Serial programming allows customers to manufacture boards with unprogrammed devices and then program the digital signal controller just before shipping the product. Serial programming also allows the most recent firmware or a custom firmware to be programmed. Refer to the "dsPIC33F/PIC24H Flash Programming Specification" (DS70152) for details about In-Circuit Serial Programming (ICSP<sup>™</sup>).

Any of the three pairs of programming clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- · PGEC3 and PGED3

#### 22.7 In-Circuit Debugger

The dsPIC33FJ06GS001/101A/102A/202A and dsPIC33FJ09GS302 devices provide simple debugging functionality through the PGECx (Emulation/ Debug Clock) and PGEDx (Emulation/Debug Data) pin functions.

Any of the three pairs of debugging clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- · PGEC3 and PGED3

To use the in-circuit debugger function of the device, the design must implement ICSP connections to  $\overline{MCLR}$ , VDD, Vss and the PGECx/PGEDx pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins.

#### 24.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows® programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit<sup>™</sup> 2 enables in-circuit debugging on most PIC® microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

#### 24.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

#### 24.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

| DC CHARA  | ACTERISTICS            |      | Standard | Operating Co<br>temperature | <b>V to 3.6V (unless otherwise stated)</b><br>+85°C for Industrial<br>+125°C for Extended |                                |

|-----------|------------------------|------|----------|-----------------------------|-------------------------------------------------------------------------------------------|--------------------------------|

| Param.    | Typical <sup>(1)</sup> | Max. | Units    |                             |                                                                                           | Conditions                     |

| Operating | Current (IDD)          | (2)  |          |                             |                                                                                           |                                |

| DC20d     | 15                     | 23   | mA       | -40°C                       |                                                                                           |                                |

| DC20a     | 15                     | 23   | mA       | +25°C                       | 3.3V                                                                                      | 10 MIPS                        |

| DC20b     | 15                     | 23   | mA       | +85°C                       | 3.3V                                                                                      | TO MIPS                        |

| DC20c     | 15                     | 23   | mA       | +125°C                      |                                                                                           |                                |

| DC21d     | 23                     | 34   | mA       | -40°C                       |                                                                                           |                                |

| DC21a     | 23                     | 34   | mA       | +25°C                       | 0.01/                                                                                     | 16 MIPS <sup>(3)</sup>         |

| DC21b     | 23                     | 34   | mA       | +85°C                       | - 3.3V                                                                                    | 16 MIPS(*)                     |

| DC21c     | 23                     | 34   | mA       | +125°C                      |                                                                                           |                                |

| DC22d     | 25                     | 38   | mA       | -40°C                       |                                                                                           |                                |

| DC22a     | 25                     | 38   | mA       | +25°C                       | 2.21/                                                                                     | 20 MIPS <sup>(3)</sup>         |

| DC22b     | 25                     | 38   | mA       | +85°C                       | - 3.3V                                                                                    | 20 MIPS(*)                     |

| DC22c     | 25                     | 38   | mA       | +125°C                      |                                                                                           |                                |

| DC23d     | 34                     | 51   | mA       | -40°C                       |                                                                                           |                                |

| DC23a     | 34                     | 51   | mA       | +25°C                       | 3.3V                                                                                      | 30 MIPS <sup>(3)</sup>         |

| DC23b     | 34                     | 51   | mA       | +85°C                       | - 3.3V                                                                                    | 30 MIPS(*)                     |

| DC23c     | 34                     | 51   | mA       | +125°C                      |                                                                                           |                                |

| DC24d     | 43                     | 64   | mA       | -40°C                       |                                                                                           |                                |

| DC24a     | 43                     | 64   | mA       | +25°C                       | 2 2)/                                                                                     | 40 MIPS <sup>(3)</sup>         |

| DC24b     | 43                     | 64   | mA       | +85°C                       | - 3.3V                                                                                    | 40 MIP 5 9                     |

| DC24c     | 43                     | 64   | mA       | +125°C                      |                                                                                           |                                |

| DC25d     | 83                     | 125  | mA       | -40°C                       |                                                                                           | 40 MIPS                        |

| DC25a     | 83                     | 125  | mA       | +25°C                       | 3.3V                                                                                      | See Note 2, except PWM and ADC |

| DC25b     | 83                     | 125  | mA       | +85°C                       | J.JV                                                                                      | are operating at maximum speed |

| DC25c     | 83                     | 125  | mA       | +125°C                      |                                                                                           | (PTCON2 = 0x0000)              |

#### TABLE 25-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

2: IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

- Oscillator is configured in EC mode, OSC1 is driven with external square wave from rail-to-rail

- CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD; WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (PMDx bits are all zeroed)

- CPU is executing while (1) statement

- **3:** These parameters are characterized but not tested in manufacturing.

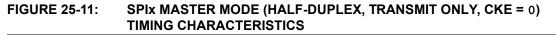

| AC CHARAG            | CTERISTICS                               |                                             | Standard Operating<br>(unless otherwise<br>Operating temperate | <b>stated)</b><br>ure -40°C ≤ <sup>™</sup> |     |     |

|----------------------|------------------------------------------|---------------------------------------------|----------------------------------------------------------------|--------------------------------------------|-----|-----|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)                     | СКЕ                                        | СКР | SMP |

| 15 MHz               | Table 25-30                              | _                                           | _                                                              | 0,1                                        | 0,1 | 0,1 |

| 9 MHz                | _                                        | Table 25-31                                 | —                                                              | 1                                          | 0,1 | 1   |

| 9 MHz                | —                                        | Table 25-32                                 | —                                                              | 0                                          | 0,1 | 1   |

| 15 MHz               | _                                        | —                                           | Table 25-33                                                    | 1                                          | 0   | 0   |

| 11 MHz               | —                                        | —                                           | Table 25-34                                                    | 1                                          | 1   | 0   |

| 15 MHz               | _                                        | —                                           | Table 25-35                                                    | 0                                          | 1   | 0   |

| 11 MHz               | _                                        | —                                           | Table 25-36                                                    | 0                                          | 0   | 0   |

#### TABLE 25-29: SPIx MAXIMUM DATA/CLOCK RATE SUMMARY

| AC CHA | RACTERI | STICS             |                           | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Indus $-40^{\circ}C \le TA \le +125^{\circ}C$ for External |      |       |                                             |  |

|--------|---------|-------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|---------------------------------------------|--|

| Param. | Symbol  | Charac            | teristic                  | Min.                                                                                                                                                                                            | Max. | Units | Conditions                                  |  |

| IS10   | TLO:SCL | Clock Low Time    | 100 kHz mode              | 4.7                                                                                                                                                                                             | —    | μS    | Device must operate at a minimum of 1.5 MHz |  |

|        |         |                   | 400 kHz mode              | 1.3                                                                                                                                                                                             | —    | μS    | Device must operate at a minimum of 10 MHz  |  |

|        |         |                   | 1 MHz mode <sup>(1)</sup> | 0.5                                                                                                                                                                                             |      | μS    |                                             |  |

| IS11   | THI:SCL | Clock High Time   | 100 kHz mode              | 4.0                                                                                                                                                                                             | —    | μS    | Device must operate at a minimum of 1.5 MHz |  |

|        |         |                   | 400 kHz mode              | 0.6                                                                                                                                                                                             | —    | μS    | Device must operate at a minimum of 10 MHz  |  |

|        |         |                   | 1 MHz mode <sup>(2)</sup> | 0.5                                                                                                                                                                                             |      | μS    |                                             |  |

| IS20   | TF:SCL  | SDA1 and SCL1     | 100 kHz mode              | _                                                                                                                                                                                               | 300  | ns    | CB is specified to be from                  |  |

|        |         | Fall Time         | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                     | 300  | ns    | 10 pF to 400 pF                             |  |

|        |         |                   | 1 MHz mode <sup>(2)</sup> | —                                                                                                                                                                                               | 100  | ns    |                                             |  |

| IS21   | TR:SCL  | SDA1 and SCL1     | 100 kHz mode              | —                                                                                                                                                                                               | 1000 | ns    | CB is specified to be from                  |  |

|        |         | Rise Time         | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                     | 300  | ns    | 10 pF to 400 pF                             |  |

|        |         |                   | 1 MHz mode <sup>(2)</sup> | —                                                                                                                                                                                               | 300  | ns    |                                             |  |

| IS25   | TSU:DAT | Data Input        | 100 kHz mode              | 250                                                                                                                                                                                             |      | ns    |                                             |  |

|        |         | Setup Time        | 400 kHz mode              | 100                                                                                                                                                                                             |      | ns    |                                             |  |

|        |         |                   | 1 MHz mode <sup>(2)</sup> | 100                                                                                                                                                                                             |      | ns    |                                             |  |

| IS26   | THD:DAT | Data Input        | 100 kHz mode              | 0                                                                                                                                                                                               |      | μs    |                                             |  |

|        |         | Hold Time         | 400 kHz mode              | 0                                                                                                                                                                                               | 0.9  | μs    |                                             |  |

|        |         |                   | 1 MHz mode <sup>(2)</sup> | 0                                                                                                                                                                                               | 0.3  | μS    |                                             |  |

| IS30   | TSU:STA | Start Condition   | 100 kHz mode              | 4.7                                                                                                                                                                                             |      | μS    | Only relevant for Repeated                  |  |

|        |         | Setup Time        | 400 kHz mode              | 0.6                                                                                                                                                                                             |      | μS    | Start condition                             |  |

|        |         |                   | 1 MHz mode <sup>(2)</sup> | 0.25                                                                                                                                                                                            |      | μS    |                                             |  |

| IS31   | THD:STA | Start Condition   | 100 kHz mode              | 4.0                                                                                                                                                                                             |      | μS    | After this period, the first                |  |

|        |         | Hold Time         | 400 kHz mode              | 0.6                                                                                                                                                                                             |      | μS    | clock pulse is generated                    |  |

|        |         |                   | 1 MHz mode <sup>(2)</sup> | 0.25                                                                                                                                                                                            |      | μS    |                                             |  |

| IS33   | Tsu:sto | Stop Condition    | 100 kHz mode              | 4.7                                                                                                                                                                                             |      | μS    |                                             |  |

|        |         | Setup Time        | 400 kHz mode              | 0.6                                                                                                                                                                                             |      | μS    |                                             |  |

|        |         |                   | 1 MHz mode <sup>(2)</sup> | 0.6                                                                                                                                                                                             |      | μS    |                                             |  |

| IS34   | THD:STO | Stop Condition    | 100 kHz mode              | 4000                                                                                                                                                                                            |      | ns    |                                             |  |

|        |         | Hold Time         | 400 kHz mode              | 600                                                                                                                                                                                             |      | ns    |                                             |  |

|        |         |                   | 1 MHz mode <sup>(2)</sup> | 250                                                                                                                                                                                             |      | ns    |                                             |  |

| IS40   | TAA:SCL | Output Valid      | 100 kHz mode              | 0                                                                                                                                                                                               | 3500 | ns    |                                             |  |

|        |         | From Clock        | 400 kHz mode              | 0                                                                                                                                                                                               | 1000 | ns    |                                             |  |

|        |         |                   | 1 MHz mode <sup>(2)</sup> | 0                                                                                                                                                                                               | 350  | ns    |                                             |  |

| IS45   | TBF:SDA | Bus Free Time     | 100 kHz mode              | 4.7                                                                                                                                                                                             |      | μS    | Time the bus must be free                   |  |

|        |         |                   | 400 kHz mode              | 1.3                                                                                                                                                                                             |      | μS    | before a new transmission                   |  |

|        |         |                   | 1 MHz mode <sup>(2)</sup> | 0.5                                                                                                                                                                                             |      | μS    | can start                                   |  |

| IS50   | Св      | Bus Capacitive Lo | ading                     |                                                                                                                                                                                                 | 400  | pF    |                                             |  |

#### TABLE 25-38: I2C1 BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

Note 1: Maximum pin capacitance = 10 pF for all I2C1 pins (for 1 MHz mode only).

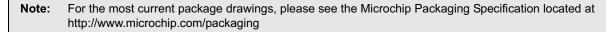

# 28-Lead Plastic Quad Flat, No Lead Package (MM) – 6x6x0.9 mm Body [QFN-S] with 0.40 mm Contact Length

|                            | MILLIMETERS |          |      |      |  |

|----------------------------|-------------|----------|------|------|--|

| Dimensio                   | n Limits    | MIN      | NOM  | MAX  |  |

| Contact Pitch              | E           | 0.65 BSC |      |      |  |