#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

XE

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 13                                                                              |

| Program Memory Size        | 6KB (2K x 24)                                                                   |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 256 x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 18-PDIP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs101a-i-p |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

NOTES:

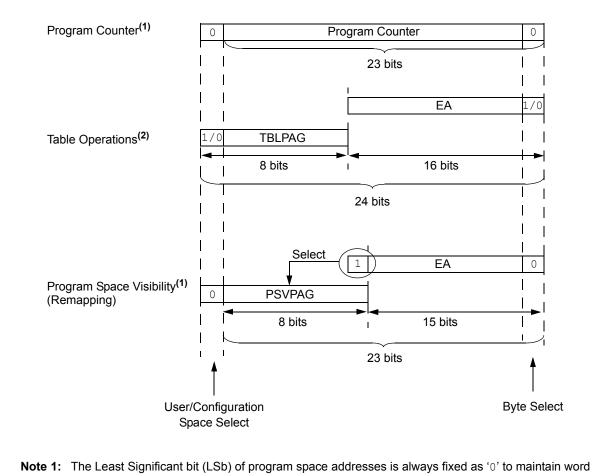

#### FIGURE 4-8: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

- alignment of data in the program and data spaces.

- 2: Table operations are not required to be word-aligned. Table read operations are permitted in the configuration memory space.

## 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS001/101A/ 102A/202A and dsPIC33FJ09GS302 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Programming" (DS70191) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

These devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming™ (ICSP™) programming capability

- Run-Time Self-Programming (RTSP)

ICSP allows a dsPIC33FJ06GS001/101A/102A/202A and dsPIC33FJ09GS302 device to be serially programmed while in the end application circuit. This is done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx), and three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the digital signal controller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (table read) and TBLWT (table write) instructions. With RTSP, the user application can write a single program memory word at a time, and erase program memory in blocks or 'pages' of 512 instructions (1536 bytes) at a time.

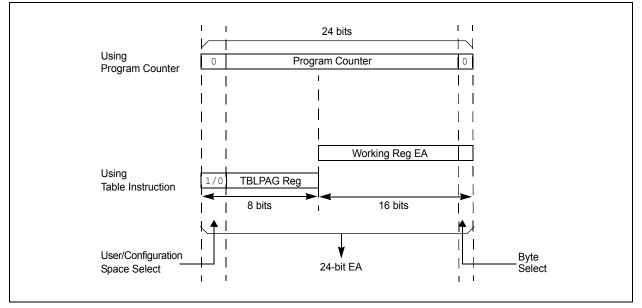

## 5.1 Table Instructions and Flash Programming

Regardless of the method used, all programming of Flash memory is done with the table read and table write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

## 6.0 RESETS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS001/101A/102A/ 202A and dsPIC33FJ09GS302 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 8.** "**Reset**" (DS70192) in the "*dsPIC33F/PIC24H Family Reference Manual*", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

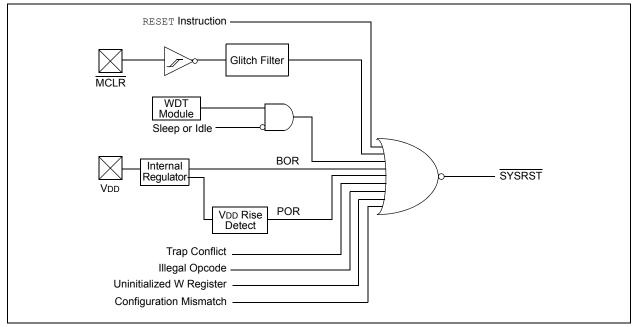

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- · POR: Power-on Reset

- · BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: Software RESET Instruction

- WDTO: Watchdog Timer Reset

- · CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- · IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

#### FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state, and some are unaffected.

Note: Refer to the specific peripheral section or Section 3.0 "CPU" of this data sheet for register Reset states.

All types of device Reset sets a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits (except for the POR (RCON<0> bit) that are set. The user application can set or clear any bit, at any time, during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

| <b>REGISTER 7</b>    | -17: IEC6: I                                                         | INTERRUPT                                                                                                      | ENABLE CO                             |                         | GISTER 6         |                       |       |

|----------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------|------------------|-----------------------|-------|

| R/W-0                | R/W-0                                                                | U-0                                                                                                            | U-0                                   | U-0                     | U-0              | U-0                   | U-0   |

| ADCP1IE              | ADCP0IE                                                              |                                                                                                                | —                                     | —                       | —                | —                     | _     |

| bit 15               |                                                                      |                                                                                                                |                                       |                         |                  |                       | bit 8 |

|                      |                                                                      |                                                                                                                |                                       |                         |                  |                       |       |

| R/W-0                | U-0                                                                  | U-0                                                                                                            | U-0                                   | U-0                     | U-0              | R/W-0                 | U-0   |

| AC2IE <sup>(1)</sup> |                                                                      |                                                                                                                | —                                     | —                       | —                | PWM4IE <sup>(2)</sup> | —     |

| bit 7                |                                                                      |                                                                                                                |                                       |                         |                  |                       | bit 0 |

|                      |                                                                      |                                                                                                                |                                       |                         |                  |                       |       |

| Legend:              |                                                                      |                                                                                                                |                                       |                         |                  |                       |       |

| R = Readable         | bit                                                                  | W = Writable                                                                                                   | bit                                   | U = Unimpler            | mented bit, read | l as '0'              |       |

| -n = Value at F      | POR                                                                  | '1' = Bit is set                                                                                               |                                       | '0' = Bit is cle        | ared             | x = Bit is unkno      | wn    |

| bit 14               | 1 = Interrupt r<br>0 = Interrupt r<br>ADCP0IE: AE<br>1 = Interrupt r | DC Pair 1 Conv<br>request is enab<br>request is not e<br>DC Pair 0 Conv<br>request is enab<br>request is not e | led<br>nabled<br>ersion Done I<br>led | ·                       |                  |                       |       |

| bit 13-8             | Unimplemen                                                           | ted: Read as '                                                                                                 | C                                     |                         |                  |                       |       |

| bit 7                | 1 = Interrupt r                                                      | og Comparator<br>request is enab<br>request is not e                                                           | led .                                 | able bit <sup>(1)</sup> |                  |                       |       |

| bit 6-2              | Unimplemen                                                           | ted: Read as '                                                                                                 | )'                                    |                         |                  |                       |       |

| bit 1                | PWM4IE: PW                                                           | /M4 Interrupt E                                                                                                | nable bit <sup>(2)</sup>              |                         |                  |                       |       |

|                      |                                                                      | request is enab<br>request is not e                                                                            |                                       |                         |                  |                       |       |

| bit 0                | Unimplemen                                                           | ted: Read as '                                                                                                 | כי                                    |                         |                  |                       |       |

Note 1: This bit is not implemented in dsPIC33FJ06GS101A/102A devices.

2: This bit is not implemented in dsPIC33FJ06GS102A/202A devices.

| <b>REGISTER 7-2</b> | 28: IPC20 | : INTERRUPT      | <b>PRIORITY</b> | CONTROL F        | REGISTER 20      |                 |       |

|---------------------|-----------|------------------|-----------------|------------------|------------------|-----------------|-------|

| U-0                 | U-0       | U-0              | U-0             | U-0              | U-0              | U-0             | U-0   |

| —                   |           | —                | —               | —                | —                | —               | —     |

| bit 15              |           |                  |                 |                  |                  |                 | bit 8 |

|                     |           |                  |                 |                  |                  |                 |       |

| U-0                 | U-0       | U-0              | U-0             | U-0              | R/W-1            | R/W-0           | R/W-0 |

| —                   | _         | —                | _               | —                |                  | JTAGIP<2:0>     |       |

| bit 7               |           |                  |                 |                  |                  |                 | bit 0 |

|                     |           |                  |                 |                  |                  |                 |       |

| Legend:             |           |                  |                 |                  |                  |                 |       |

| R = Readable b      | it        | W = Writable     | bit             | U = Unimpler     | mented bit, read | l as '0'        |       |

| -n = Value at PC    | DR        | '1' = Bit is set |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|                     |           |                  |                 |                  |                  |                 |       |

| bit 15-3 | Unimplemented: Read as '0'                                 |

|----------|------------------------------------------------------------|

| bit 2-0  | JTAGIP<2:0>: JTAG Interrupt Priority bits                  |

|          | 111 = Interrupt is Priority 7 (highest priority interrupt) |

|          | •                                                          |

|          | •                                                          |

|          | •                                                          |

|          | 001 = Interrupt is Priority 1                              |

000 = Interrupt source is disabled

#### 10.6.2.3 Virtual Pins

Four virtual RPn pins (RP32, RP33, RP34 and RP35) are supported, which are identical in functionality to all other RPn pins, with the exception of pinouts. These four pins are internal to the devices and are not connected to a physical device pin.

These pins provide a simple way for inter-peripheral connection without utilizing a physical pin. For example, the output of the analog comparator can be connected to RP32 and the PWM Fault input can be configured for RP32 as well. This configuration allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

# 10.6.3 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. dsPIC33F devices include three features to prevent alterations to the peripheral map:

- · Control register lock sequence

- Continuous state monitoring

- Configuration bit pin select lock

## 10.6.3.1 Control Register Lock

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (OSCCON<6>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear IOLOCK, a specific command sequence must be executed:

- 1. Write 0x46 to OSCCON<7:0>.

- 2. Write 0x57 to OSCCON<7:0>.

- 3. Clear (or set) IOLOCK as a single operation.

Unlike the similar sequence with the oscillator's LOCK bit, IOLOCK remains in one state until changed. This allows all of the Peripheral Pin Selects to be configured with a single unlock sequence, followed by an update to all control registers, then locked with a second lock sequence.

### 10.6.3.2 Continuous State Monitoring

In addition to being protected from direct writes, the contents of the RPINRx and RPORx registers are constantly monitored in hardware by shadow registers. If an unexpected change in any of the registers occurs (such as cell disturbances caused by ESD or other external events), a Configuration Mismatch Reset will be triggered.

### 10.6.3.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPINRx and RPORx registers. The IOL1WAY (FOSC<5>) Configuration bit blocks the IOLOCK bit from being cleared, after it has been set once. If IOLOCK remains set, the register unlock procedure will not execute and the Peripheral Pin Select Control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session. Programming IOL1WAY allows user applications unlimited access (with the proper use of the unlock sequence) to the Peripheral Pin Select registers.

| U-0                | U-0                                                                                                                       | R/W-1                                                                                                                                                                      | R/W-1                              | R/W-1                       | R/W-1            | R/W-1           | R/W-1 |

|--------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------------|------------------|-----------------|-------|

| _                  | —                                                                                                                         |                                                                                                                                                                            |                                    | FLT7                        | R<5:0>           |                 |       |

| bit 15             |                                                                                                                           |                                                                                                                                                                            |                                    |                             |                  |                 | bit 8 |

|                    |                                                                                                                           |                                                                                                                                                                            |                                    |                             |                  |                 |       |

| U-0                | U-0                                                                                                                       | R/W-1                                                                                                                                                                      | R/W-1                              | R/W-1                       | R/W-1            | R/W-1           | R/W-1 |

| _                  | —                                                                                                                         |                                                                                                                                                                            |                                    | FLT6                        | R<5:0>           |                 |       |

| bit 7              |                                                                                                                           |                                                                                                                                                                            |                                    |                             |                  |                 | bit ( |

| Legend:            |                                                                                                                           |                                                                                                                                                                            |                                    |                             |                  |                 |       |

| R = Readab         | le bit                                                                                                                    | W = Writable I                                                                                                                                                             | oit                                | U = Unimplen                | nented bit, read | d as '0'        |       |

| -n = Value a       | t POR                                                                                                                     | '1' = Bit is set                                                                                                                                                           |                                    | '0' = Bit is clea           |                  | x = Bit is unkr | nown  |

|                    |                                                                                                                           |                                                                                                                                                                            |                                    |                             |                  |                 |       |

| bit 15-14          | Unimpleme                                                                                                                 | nted: Read as '(                                                                                                                                                           | )'                                 |                             |                  |                 |       |

| bit 13-8           | •                                                                                                                         | : Assign PWM F                                                                                                                                                             |                                    | =I T7) to the Co            | orresponding R   | Pn Pin hits     |       |

|                    |                                                                                                                           | put tied to Vss                                                                                                                                                            |                                    |                             | incoponding is   |                 |       |

|                    |                                                                                                                           | put tied to RP35                                                                                                                                                           |                                    |                             |                  |                 |       |

|                    |                                                                                                                           |                                                                                                                                                                            |                                    |                             |                  |                 |       |

|                    | 100010 <b>= ln</b>                                                                                                        | put tied to RP34                                                                                                                                                           |                                    |                             |                  |                 |       |

|                    |                                                                                                                           | put tied to RP34<br>put tied to RP33                                                                                                                                       |                                    |                             |                  |                 |       |

|                    | 100001 <b>= In</b>                                                                                                        |                                                                                                                                                                            | 1                                  |                             |                  |                 |       |

|                    | 100001 <b>= In</b>                                                                                                        | put tied to RP33                                                                                                                                                           | 1                                  |                             |                  |                 |       |

|                    | 100001 <b>= In</b>                                                                                                        | put tied to RP33                                                                                                                                                           | 1                                  |                             |                  |                 |       |

|                    | 100001 <b>= In</b>                                                                                                        | put tied to RP33                                                                                                                                                           | 1                                  |                             |                  |                 |       |

|                    | 100001 = In<br>100000 = In<br>•                                                                                           | put tied to RP33<br>put tied to RP32                                                                                                                                       | 1                                  |                             |                  |                 |       |

| bit 7-6            | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>00000 = Inp                                                                  | put tied to RP33<br>put tied to RP32<br>ut tied to RP0                                                                                                                     |                                    |                             |                  |                 |       |

| bit 7-6            | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | put tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0                                                                                                 | ;<br>;<br>;                        | ELT6) to the Co             | prresponding P   | PDn Din hite    |       |

| bit 7-6<br>bit 5-0 | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | put tied to RP33<br>put tied to RP32<br>ut tied to RP0<br><b>nted:</b> Read as '0<br>:: Assign PWM F                                                                       | ;<br>;<br>;                        | FLT6) to the Co             | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | put tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss                                                            | <sub>)</sub> ,<br>Fault Input 6 (I | FLT6) to the Co             | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | put tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35                                        | ) <sup>)</sup><br>Fault Input 6 (I | FLT6) to the Co             | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34                     | ) <sup>)</sup><br>Fault Input 6 (I | <sup>-</sup> LT6) to the Co | orresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33 | o'<br>Fault Input 6 (I             | <sup>-</sup> LT6) to the Co | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34                     | o'<br>Fault Input 6 (I             | <sup>-</sup> LT6) to the Co | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33 | o'<br>Fault Input 6 (I             | <sup>-</sup> LT6) to the Co | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33 | o'<br>Fault Input 6 (I             | FLT6) to the Co             | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33 | o'<br>Fault Input 6 (I             | <sup>=</sup> LT6) to the Co | prresponding R   | Pn Pin bits     |       |

## REGISTER 10-13: RPINR32: PERIPHERAL PIN SELECT INPUT REGISTER 32

## REGISTER 15-4: SEVTCMP: PWM SPECIAL EVENT COMPARE REGISTER

| R/W-0  | R/W-0 | R/W-0        | R/W-0  | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|--------------|--------|-----------|-------|-------|-------|

|        |       |              | SEVTCM | IP <15:8> |       |       |       |

| bit 15 |       |              |        |           |       |       | bit 8 |

| R/W-0  | R/W-0 | R/W-0        | R/W-0  | R/W-0     | U-0   | U-0   | U-0   |

|        | SE    | EVTCMP <7:3> | •      |           | _     | —     | _     |

| bit 7  |       |              |        |           |       |       | bit 0 |

| Legena:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-3 SEVTCMP<15:3>: Special Event Compare Count Value bits bit 2-0 Unimplemented: Read as '0'

### REGISTER 15-5: MDC: PWM MASTER DUTY CYCLE REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                  | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------------|-----------------|-----------------|-------|

|                 |       |                  | MDC<  | 15:8> <sup>(1,2)</sup> |                 |                 |       |

| bit 15          |       |                  |       |                        |                 |                 | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                  | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | MDC   | <7:0> <sup>(1,2)</sup> |                 |                 |       |

| bit 7           |       |                  |       |                        |                 |                 | bit 0 |

|                 |       |                  |       |                        |                 |                 |       |

| Legend:         |       |                  |       |                        |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | oit   | U = Unimplen           | nented bit, rea | nd as '0'       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle       | ared            | x = Bit is unki | nown  |

bit 15-0 MDC<15:0>: Master PWM Duty Cycle Value bits<sup>(1,2)</sup>

**Note 1:** The smallest pulse width that can be generated on the PWM output corresponds to a value of 0x0009, while the maximum pulse width generated corresponds to a value of Period – 0x0008.

2: As the duty cycle gets closer to 0% or 100% of the PWM period (0 ns-40 ns, depending on the mode of operation), the PWM duty cycle resolution will degrade from 1 LSb to 3 LSbs.

## REGISTER 15-9: PHASEX: PWMx PRIMARY PHASE SHIFT REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0   | R/W-0                  | R/W-0  | R/W-0 | R/W-0  |

|--------|-------|-------|---------|------------------------|--------|-------|--------|

| 10000  | 10000 | 10000 | -       | -                      | 1000 0 | 10000 | 1000 0 |

|        |       |       | PHASEx• | <15:8> <b>(1,2)</b>    |        |       |        |

| bit 15 |       |       |         |                        |        |       | bit 8  |

|        |       |       |         |                        |        |       |        |

| R/W-0  | R/W-0 | R/W-0 | R/W-0   | R/W-0                  | R/W-0  | R/W-0 | R/W-0  |

|        |       |       | PHASEx  | <7:0> <sup>(1,2)</sup> |        |       |        |

| bit 7  |       |       |         |                        |        |       | bit 0  |

|        |       |       |         |                        |        |       |        |

|        |       |       |         |                        |        |       |        |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0 **PHASEx<15:0>:** PWMx Phase Shift Value or Independent Time Base Period for PWM Generator bits<sup>(1,2)</sup>

**Note 1:** If the ITB (PWMCONx<9>) bit = 0, the following applies based on the mode of operation:

- Complementary, Redundant and Push-Pull Output mode (PMOD<1:0> (IOCONx<11:10>) = 00, 01 or 10), PHASEx<15:0> = Phase shift value for PWMxH and PWMxL outputs.

- True Independent Output mode PMOD<1:0> (IOCONx<11:10>) = 11), PHASEx<15:0> = Phase shift value for PWMxL only.

**2:** If the ITB (PWMCONx<9>) bit = 1, the following applies based on the mode of operation:

• Complementary, Redundant and Push-Pull Output mode (PMOD<1:0> (IOCONx<11:10>) = 00, 01 or 10), PHASEx<15:0> = Independent time base period value for PWMxH and PWMxL.

- True Independent Output mode PMOD<1:0> (IOCONx<11:10>) = 11), PHASEx<15:0> = Independent time base period value for PWMxL only.

- The smallest pulse width that can be generated on the PWM output corresponds to a value of 0x0008, while the maximum pulse width generated corresponds to a value of Period-0x0008.

| R/W-0      | R/W-0                                                                       | R/W-0                      | R/W-0           | R/W-0            | R/W-0                              | R/W-0                | R/W-0          |

|------------|-----------------------------------------------------------------------------|----------------------------|-----------------|------------------|------------------------------------|----------------------|----------------|

| IFLTMO     | D                                                                           | C                          | LSRC<4:0>(      | 2,3)             |                                    | CLPOL <sup>(1)</sup> | CLMOD          |

| bit 15     |                                                                             |                            |                 |                  |                                    |                      | bit 8          |

| R/W-0      | R/W-0                                                                       | R/W-0                      | R/W-0           | R/W-0            | R/W-0                              | R/W-0                | R/W-0          |

|            | FL                                                                          | _TSRC<4:0> <sup>(2,3</sup> | )               |                  | FLTPOL <sup>(1)</sup>              | FLTMO                | D<1:0>         |

| bit 7      |                                                                             |                            |                 |                  |                                    |                      | bit (          |

| Legend:    |                                                                             |                            |                 |                  |                                    |                      |                |

| R = Reada  | able bit                                                                    | W = Writable               | bit             | U = Unimple      | mented bit, read                   | d as '0'             |                |

| -n = Value | at POR                                                                      | '1' = Bit is set           |                 | '0' = Bit is cle | eared                              | x = Bit is unkr      | nown           |

| bit 15     | IFLTMOD: In                                                                 | dependent Fau              | lt Mode Enat    | ole bit          |                                    |                      |                |

|            |                                                                             |                            |                 |                  | LTDAT<1> to P<br>1:0> bits are not |                      |                |

|            | 0 = Normal                                                                  | Fault mode: Cu             | irrent-limit fe | ature maps Cl    | _DAT<1:0> bits > to the PWMxH      | to the PWMxH         | l and PWMxI    |

| bit 14-10  |                                                                             |                            | •               |                  | ect for PWMx # (                   |                      | •              |

|            | 11111 <b>= Res</b>                                                          |                            | 0               |                  |                                    |                      |                |

|            | •                                                                           |                            |                 |                  |                                    |                      |                |

|            | •                                                                           |                            |                 |                  |                                    |                      |                |

|            | •                                                                           |                            |                 |                  |                                    |                      |                |

|            | 01000 <b>= Res</b>                                                          | served                     |                 |                  |                                    |                      |                |

|            | 00111 <b>= Fau</b><br>00110 <b>= Fau</b>                                    |                            |                 |                  |                                    |                      |                |

|            | 00110 <b>– Fau</b>                                                          |                            |                 |                  |                                    |                      |                |

|            | 00100 <b>= Fau</b>                                                          |                            |                 |                  |                                    |                      |                |

|            | 00011 <b>= Fau</b>                                                          |                            |                 |                  |                                    |                      |                |

|            | 00010 <b>= Fau</b>                                                          | ılt 3                      |                 |                  |                                    |                      |                |

|            | 00001 <b>= Fau</b>                                                          |                            |                 |                  |                                    |                      |                |

|            | 00000 <b>= Fau</b>                                                          | ılt 1                      |                 |                  |                                    |                      |                |

| bit 9      | CLPOL: Curr                                                                 | rent-Limit Polari          | ty for PWMx     | Generator # b    | it <sup>(1)</sup>                  |                      |                |

|            | 1 = The select                                                              | cted current-lim           | it source is a  | ctive-low        |                                    |                      |                |

|            | 0 = The selec                                                               | cted current-lim           | it source is a  | ctive-high       |                                    |                      |                |

| bit 8      | CLMOD: Cur                                                                  | rrent-Limit Mode           | e Enable bit f  | or PWMx Gene     | erator # bit                       |                      |                |

|            | 1 = Current-li                                                              | imit function is e         | enabled         |                  |                                    |                      |                |

|            | 0 = Current-li                                                              | imit function is c         | lisabled        |                  |                                    |                      |                |

|            | These bits should yield unpredictable                                       | -                          | ly when PTE     | N = 0. Changir   | ng the clock sele                  | ection during op     | eration will   |

|            | When Independer<br>mode (CLSRC<4:<br>unused Fault sour                      | 0> = b0000), th            | e Fault Cont    | rol Source Sel   | ect bits (FLTSR                    | C<4:0>) should       | be set to an   |

| 3:         | When Independer<br>(FLTSRC<4:0> = 1<br>unused current-lin<br>PWMxL outputs. | b0000 <b>), the Cu</b> i   | rrent-Limit Co  | ontrol Source S  | elect bits (CLSF                   | RC<4:0>) shoul       | d be set to an |

## REGISTER 15-15: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER

| U-0                 | U-0            | U-0                                  | R/W-0            | R/W-0                                   | R/W-0              | R/W-0           | R/W-0              |

|---------------------|----------------|--------------------------------------|------------------|-----------------------------------------|--------------------|-----------------|--------------------|

| —                   | _              |                                      | DISSCK           | DISSDO                                  | MODE16             | SMP             | CKE <sup>(1)</sup> |

| pit 15              |                |                                      |                  |                                         |                    |                 | bit                |

|                     | DAMO           | DAMA                                 | DAMA             | DAALO                                   | DAMA               | DAMA            | <b>D</b> 444 0     |

| R/W-0               | R/W-0          | R/W-0                                | R/W-0            | R/W-0                                   | R/W-0              | R/W-0           | R/W-0              |

| SSEN <sup>(3)</sup> | CKP            | MSTEN                                |                  | SPRE<2:0> <sup>(2</sup>                 | -)                 | PPRE<           | :1:0> <b>(2)</b>   |

| pit 7               |                |                                      |                  |                                         |                    |                 | bit                |

| _egend:             |                |                                      |                  |                                         |                    |                 |                    |

| R = Readable        | bit            | W = Writable                         | bit              | U = Unimpler                            | nented bit, read   | as '0'          |                    |

| n = Value at l      | POR            | '1' = Bit is set                     | :                | '0' = Bit is cle                        | ared               | x = Bit is unkr | iown               |

|                     |                |                                      |                  |                                         |                    |                 |                    |

| oit 15-13           | Unimplemen     | ted: Read as '                       | 0'               |                                         |                    |                 |                    |

| oit 12              | DISSCK: Dis    | able SCKx Pin                        | bit (SPI Maste   | er modes only)                          |                    |                 |                    |

|                     | 1 = Internal S | SPI clock is disa                    | abled; pin func  | tions as I/O                            |                    |                 |                    |

|                     | 0 = Internal S | SPI clock is ena                     | bled             |                                         |                    |                 |                    |

| pit 11              |                | able SDOx Pin                        |                  |                                         |                    |                 |                    |

|                     |                | ,                                    | · · ·            | unctions as I/O                         | )                  |                 |                    |

|                     | •              | is controlled b                      | •                |                                         |                    |                 |                    |

| oit 10              |                | ord/Byte Comm                        |                  |                                         |                    |                 |                    |

|                     |                | ication is word-<br>ication is byte- |                  |                                         |                    |                 |                    |

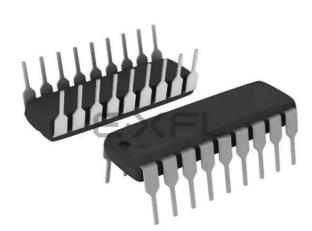

| oit 9               |                | ata Input Sam                        |                  |                                         |                    |                 |                    |

|                     | Master mode    |                                      |                  |                                         |                    |                 |                    |

|                     |                | <u>.</u><br>a is sampled at          | end of data o    | utput time                              |                    |                 |                    |

|                     |                | a is sampled at                      |                  |                                         |                    |                 |                    |

|                     | Slave mode:    |                                      |                  |                                         |                    |                 |                    |

|                     |                |                                      |                  | n Slave mode.                           |                    |                 |                    |

| oit 8               |                | lock Edge Sele                       |                  | <b>,</b> ,,                             |                    |                 | 1.11.02            |

|                     |                |                                      |                  |                                         | clock state to Idl |                 |                    |

| oit 7               |                | Select Enable                        |                  |                                         |                    |                 |                    |

|                     |                | s used for Slav                      |                  |                                         |                    |                 |                    |

|                     | ·              |                                      |                  | controlled by po                        | ort function       |                 |                    |

| oit 6               |                | Polarity Select                      |                  | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                    |                 |                    |

|                     |                | •                                    |                  | /e state is a lov                       | v level            |                 |                    |

|                     | 0 = Idle state | for clock is a lo                    | ow level; active | e state is a higł                       | n level            |                 |                    |

| oit 5               | MSTEN: Mas     | ster Mode Enat                       | ole bit          |                                         |                    |                 |                    |

|                     | 1 = Master m   | ode                                  |                  |                                         |                    |                 |                    |

|                     | 0 = Slave mo   |                                      |                  |                                         |                    |                 |                    |

## REGISTER 16-2: SPIXCON1: SPIX CONTROL REGISTER 1

- bit to '0' for the Framed SPI modes (FRMEN = SPI modes. Pr JYI ⊥).

- **2:** Do not set both Primary and Secondary prescalers to a value of 1:1.

- 3: This bit must be cleared when FRMEN = 1.

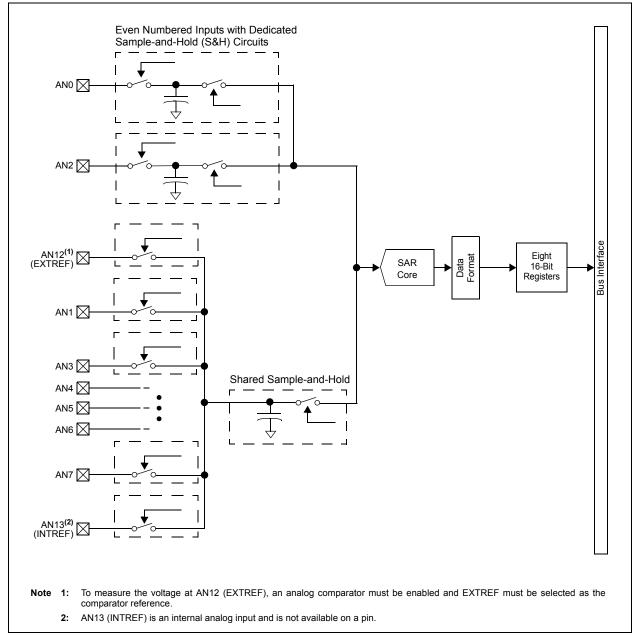

### FIGURE 19-5: ADC BLOCK DIAGRAM FOR dsPIC33FJ09GS302 DEVICE

| DC CHARACTERISTICS |        |                                                                                                                                             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |            |        |                                                                                                                                        |  |

|--------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------|------------|--------|----------------------------------------------------------------------------------------------------------------------------------------|--|

| Param.             | Symbol | Characteristic                                                                                                                              | Min.                                                  | Typ. <sup>(1)</sup> | Max.       | Units  | Conditions                                                                                                                             |  |

|                    | VIL    | Input Low Voltage                                                                                                                           |                                                       |                     |            |        |                                                                                                                                        |  |

| DI10               |        | I/O Pins                                                                                                                                    | Vss                                                   |                     | 0.2 VDD    | V      |                                                                                                                                        |  |

| DI15               |        | MCLR                                                                                                                                        | Vss                                                   |                     | 0.2 VDD    | V      |                                                                                                                                        |  |

| DI16               |        | I/O Pins with OSC1                                                                                                                          | Vss                                                   |                     | 0.2 VDD    | V      |                                                                                                                                        |  |

| DI18               |        | SDA1, SCL1                                                                                                                                  | Vss                                                   |                     | 0.3 VDD    | V      | SMBus disabled                                                                                                                         |  |

| DI19               |        | SDA1, SCL1                                                                                                                                  | Vss                                                   |                     | 0.8        | V      | SMBus enabled                                                                                                                          |  |

|                    | Vih    | Input High Voltage                                                                                                                          |                                                       |                     |            |        |                                                                                                                                        |  |

| DI20<br>DI21       |        | I/O Pins Not 5V Tolerant <sup>(4)</sup><br>I/O Pins 5V Tolerant <sup>(4)</sup>                                                              | 0.7 VDD<br>0.7 VDD                                    |                     | Vdd<br>5.5 | V<br>V |                                                                                                                                        |  |

| DI28<br>DI29       |        | SDA1, SCL1<br>SDA1, SCL1                                                                                                                    | 0.7 VDD<br>2.1                                        | _                   | 5.5<br>5.5 | V<br>V | SMBus disabled<br>SMBus enabled                                                                                                        |  |

| DI30               | ICNPU  | CNx Pull-up Current                                                                                                                         | _                                                     | 250                 | _          | μA     | VDD = 3.3V, VPIN = VSS                                                                                                                 |  |

| DI50               | lır.   | Input Leakage Current <sup>(2,3,4)</sup><br>I/O Pins:<br>4x Sink Driver Pins<br>RA0-RA2, RB0-RB2, RB5-RB10,<br>RB15<br>16x Sink Driver Pins | _                                                     |                     | ±2         | μΑ     | $Vss \le VPIN \le VDD,$ Pin at high-impedance                                                                                          |  |

|                    |        | RA3, RA4, RB3, RB4, RB11-RB14                                                                                                               | -                                                     | _                   | ±8         | μA     | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance                                                                                       |  |

| DI55               |        | MCLR                                                                                                                                        | _                                                     | —                   | ±2         | μA     | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                                                               |  |

| DI56               |        | OSC1                                                                                                                                        | —                                                     | _                   | ±2         | μA     | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &X{\sf T} \text{ and } H{\sf S} \text{ modes} \end{split}$ |  |

## TABLE 25-9: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

Note 1: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: See the "Pin Diagrams" section for the list of 5V tolerant I/O pins.

- **5**: VIL source < (VSS 0.3); characterized but not tested.

- **6:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V; characterized but not tested.

- 7: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 8: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

- **9:** Any number and/or combination of I/O pins, not excluded under IICL or IICH conditions, are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit; characterized but not tested.

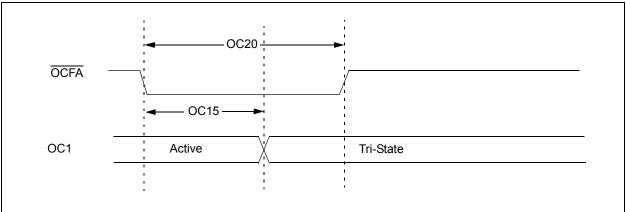

## FIGURE 25-8: OC/PWM MODULE TIMING CHARACTERISTICS

## TABLE 25-27: SIMPLE OC/PWM MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                  | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |          |       |            |  |  |

|--------------------|--------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|-------|------------|--|--|

| Param.             | Symbol | Characteristic <sup>(1)</sup>    | Min.                                                                                                                                                                                                                                                                                    | Тур. | Max.     | Units | Conditions |  |  |

| OC15               | Tfd    | Fault Input to PWM I/O<br>Change | —                                                                                                                                                                                                                                                                                       | _    | Tcy + 20 | ns    |            |  |  |

| OC20               | TFLT   | Fault Input Pulse Width          | Tcy + 20                                                                                                                                                                                                                                                                                | _    | _        | ns    |            |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

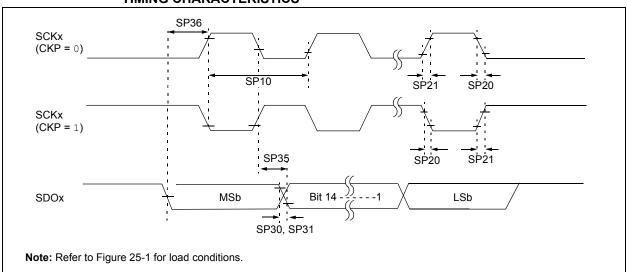

### FIGURE 25-12: SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 1) TIMING CHARACTERISTICS

## TABLE 25-30: SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY) TIMING REQUIREMENTS

|              |                       |                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                    |     |       |                                      |  |

|--------------|-----------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------------------------|--|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                | Min                                                                                                                                                                                                                                                                                   | Тур <sup>(2)</sup> | Max | Units | Conditions                           |  |

| SP10         | TscP                  | Maximum SCKx Frequency                       | —                                                                                                                                                                                                                                                                                     |                    | 15  | MHz   | See Note 3                           |  |

| SP20         | TscF                  | SCKx Output Fall Time                        | —                                                                                                                                                                                                                                                                                     | _                  | _   | ns    | See Parameter DO32 and <b>Note 4</b> |  |

| SP21         | TscR                  | SCKx Output Rise Time                        | —                                                                                                                                                                                                                                                                                     | _                  | _   | ns    | See Parameter DO31 and <b>Note 4</b> |  |

| SP30         | TdoF                  | SDOx Data Output Fall Time                   | —                                                                                                                                                                                                                                                                                     | —                  | _   | ns    | See Parameter DO32 and <b>Note 4</b> |  |

| SP31         | TdoR                  | SDOx Data Output Rise Time                   | —                                                                                                                                                                                                                                                                                     |                    | _   | ns    | See Parameter DO31 and <b>Note 4</b> |  |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge    | —                                                                                                                                                                                                                                                                                     | 6                  | 20  | ns    |                                      |  |

| SP36         | TdiV2scH,<br>TdiV2scL | SDOx Data Output Setup to<br>First SCKx Edge | 30                                                                                                                                                                                                                                                                                    | —                  | _   | ns    |                                      |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

**2:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 66.7 ns. Therefore, the clock generated in master mode must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.