Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 13                                                                                |

| Program Memory Size        | 6KB (2K x 24)                                                                     |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 256 x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 6x10b                                                                         |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

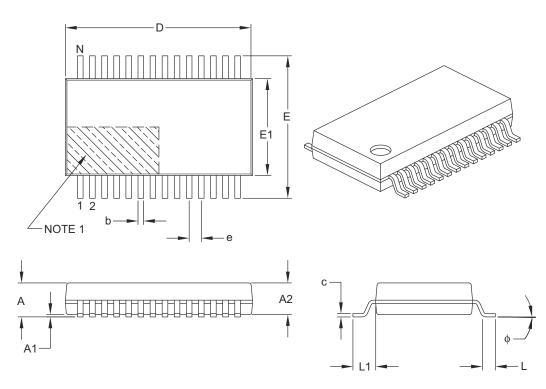

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                                    |

| Supplier Device Package    | 18-SOIC                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs101at-e-so |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

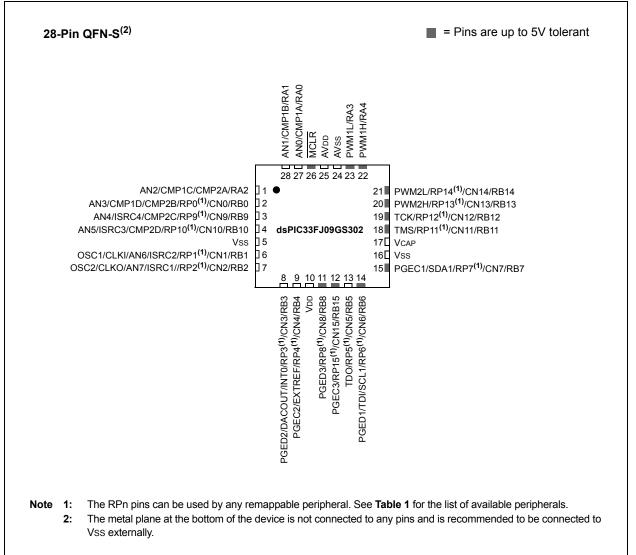

### **Pin Diagrams (Continued)**

### 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS001/101A/102A/ 202A and dsPIC33FJ09GS302 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

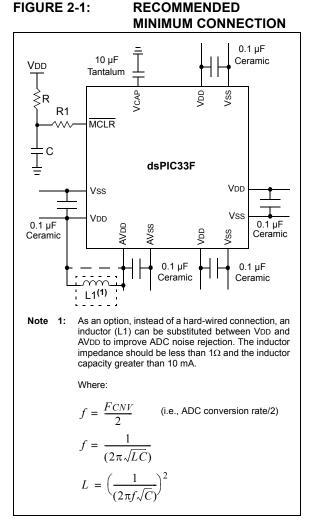

### 2.1 Basic Connection Requirements

Getting started with the dsPIC33FJ06GS001/101A/ 102A/202A and dsPIC33FJ09GS302 family of 16-bit Digital Signal Controllers (DSCs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins, regardless if ADC module is not used

- (see Section 2.2 "Decoupling Capacitors")

VCAP

- (see Section 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming™ (ICSP™) and debugging purposes (see Section 2.5 "ICSP™ Pins")

- OSC1 and OSC2 pins when external oscillator source is used (see Section 2.6 "External Oscillator Pins")

### 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS, is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, upward of tens of MHz, add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible; for example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

### 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device; typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

### 2.3 Capacitor on Internal Voltage Regulator (VCAP)

A low-ESR (<0.5 Ohms) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD, and must have a capacitor between 4.7  $\mu$ F and 10  $\mu$ F, 16V connected to ground. The type can be ceramic or tantalum. Refer to **Section 25.0 "Electrical Characteristics"** for additional information.

The placement of this capacitor should be close to the VCAP. It is recommended that the trace length not exceed one-quarter inch (6 mm). Refer to **Section 22.2** "**On-Chip Voltage Regulator**" for details.

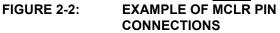

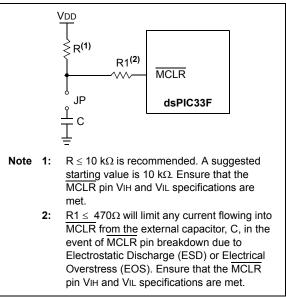

### 2.4 Master Clear (MCLR) Pin

The  $\overline{\text{MCLR}}$  pin provides for two specific device functions:

- Device Reset

- Device Programming and Debugging

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor, C, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations.

Place the components shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

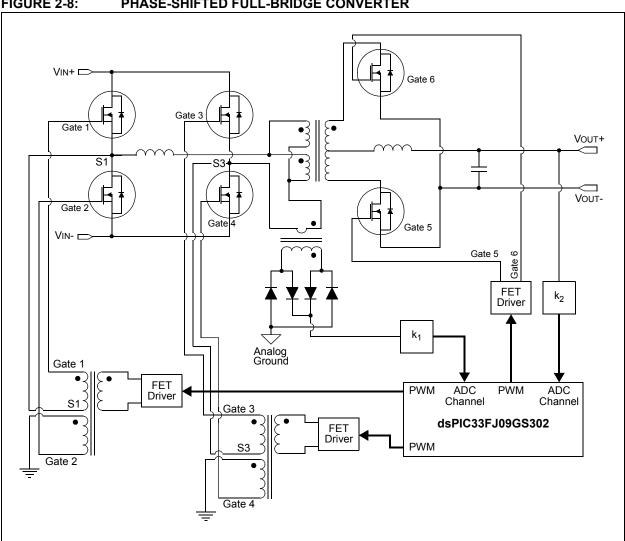

FIGURE 2-8: PHASE-SHIFTED FULL-BRIDGE CONVERTER

| REGISTER 7      | -3: INTCO                                                                                                                                     | N1: INTERR                           |                  | ROL REGISTE                         | ER 1            |                 |       |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------|-------------------------------------|-----------------|-----------------|-------|

| R/W-0           | R/W-0                                                                                                                                         | R/W-0                                | R/W-0            | R/W-0                               | R/W-0           | R/W-0           | R/W-0 |

| NSTDIS          | OVAERR                                                                                                                                        | OVBERR                               | COVAERR          | COVBERR                             | OVATE           | OVBTE           | COVTE |

| bit 15          |                                                                                                                                               |                                      |                  |                                     |                 |                 | bit   |

| R/W-0           | R/W-0                                                                                                                                         | U-0                                  | R/W-0            | R/W-0                               | R/W-0           | R/W-0           | U-0   |

| SFTACERR        | DIV0ERR                                                                                                                                       | _                                    | MATHERR          | ADDRERR                             | STKERR          | OSCFAIL         | _     |

| bit 7           |                                                                                                                                               |                                      | I                |                                     |                 |                 | bit   |

| Legend:         |                                                                                                                                               |                                      |                  |                                     |                 |                 |       |

| R = Readable    | bit                                                                                                                                           | W = Writable                         | bit              | U = Unimplem                        | ented bit, read | 1 as '0'        |       |

| -n = Value at F | POR                                                                                                                                           | '1' = Bit is set                     |                  | '0' = Bit is clea                   |                 | x = Bit is unkn | iown  |

|                 |                                                                                                                                               |                                      |                  |                                     |                 |                 |       |

| bit 15          | NSTDIS: Inte                                                                                                                                  | rrupt Nesting E                      | isable bit       |                                     |                 |                 |       |

|                 |                                                                                                                                               | nesting is disat                     |                  |                                     |                 |                 |       |

| L:+ 4 4         |                                                                                                                                               | nesting is enab                      |                  | 1                                   |                 |                 |       |

| bit 14          |                                                                                                                                               | cumulator A O caused by ove          |                  | •                                   |                 |                 |       |

|                 |                                                                                                                                               | not caused by                        |                  |                                     |                 |                 |       |

| bit 13          | •                                                                                                                                             | cumulator B O                        |                  |                                     |                 |                 |       |

|                 |                                                                                                                                               | caused by ove                        |                  | 0                                   |                 |                 |       |

|                 | 0 = Trap was                                                                                                                                  | not caused by                        | overflow of A    | ccumulator B                        |                 |                 |       |

| bit 12          |                                                                                                                                               |                                      |                  | Overflow Trap F                     | •               |                 |       |

|                 |                                                                                                                                               |                                      |                  | flow of Accumu                      |                 |                 |       |

| bit 11          | <b>COVBERR:</b> Accumulator B Catastrophic Overflow Trap Flag bit                                                                             |                                      |                  |                                     |                 |                 |       |

|                 |                                                                                                                                               |                                      |                  | flow of Accumu                      |                 |                 |       |

| bit 10          | -                                                                                                                                             | umulator A Ove                       | -                |                                     |                 |                 |       |

|                 | 1 = Trap over<br>0 = Trap is dis                                                                                                              | flow of Accum<br>sabled              | ulator A         |                                     |                 |                 |       |

| bit 9           | •                                                                                                                                             | umulator B Ove                       | erflow Trap En   | able bit                            |                 |                 |       |

|                 |                                                                                                                                               | flow of Accum                        | -                |                                     |                 |                 |       |

| bit 8           | •                                                                                                                                             | astrophic Overf                      | low Trap Enat    | ole bit                             |                 |                 |       |

|                 |                                                                                                                                               | atastrophic ove                      | •                | mulator A or B i                    | s enabled       |                 |       |

| bit 7           | •                                                                                                                                             | Shift Accumula                       | ator Error Statu | us bit                              |                 |                 |       |

|                 |                                                                                                                                               |                                      |                  | alid accumulator<br>invalid accumul |                 |                 |       |

| bit 6           | <ul> <li>0 = Math error trap was not caused by an invalid accumulator shift</li> <li>DIV0ERR: Divide-by-Zero Error Trap Status bit</li> </ul> |                                      |                  |                                     |                 |                 |       |

|                 |                                                                                                                                               | or trap was cau                      | -                |                                     |                 |                 |       |

|                 |                                                                                                                                               | or trap was not                      | •                | ivide-by-zero                       |                 |                 |       |

| bit 5           | Unimplemen                                                                                                                                    | ted: Read as '                       | 0'               |                                     |                 |                 |       |

| bit 4           |                                                                                                                                               | Math Error Trap                      |                  |                                     |                 |                 |       |

|                 |                                                                                                                                               | or trap has occu                     |                  |                                     |                 |                 |       |

| hit 2           |                                                                                                                                               | or trap has not (                    |                  |                                     |                 |                 |       |

| bit 3           |                                                                                                                                               | Address Error T                      | -                |                                     |                 |                 |       |

|                 |                                                                                                                                               | error trap has c<br>error trap has r |                  |                                     |                 |                 |       |

#### INTCOMA, INTERDURT CONTROL DECISTER A

| REGISTER      | 7-5: IFS0: I                                                | INTERRUPT                        | FLAG STAT             | US REGIST                    | ER 0                          |                        |               |

|---------------|-------------------------------------------------------------|----------------------------------|-----------------------|------------------------------|-------------------------------|------------------------|---------------|

| U-0           | U-0                                                         | R/W-0                            | R/W-0                 | R/W-0                        | R/W-0                         | R/W-0                  | U-0           |

|               | —                                                           | ADIF                             | U1TXIF <sup>(1)</sup> | U1RXIF <sup>(1)</sup>        | SPI1IF <sup>(1)</sup>         | SPI1EIF <sup>(1)</sup> |               |

| oit 15        |                                                             |                                  |                       |                              |                               |                        | bit           |

|               | 11.0                                                        | 11.0                             | 11.0                  |                              |                               |                        |               |

| R/W-0         | U-0                                                         | U-0                              | U-0                   | R/W-0                        | R/W-0<br>OC1IF <sup>(1)</sup> | R/W-0                  | R/W-0         |

| T2IF<br>bit 7 | —                                                           | _                                |                       | T1IF                         | UC IIF."                      | ICTIF <sup>(-)</sup>   | INT0IF<br>bit |

|               |                                                             |                                  |                       |                              |                               |                        |               |

| Legend:       |                                                             |                                  |                       |                              |                               |                        |               |

| R = Readable  | e bit                                                       | W = Writable                     | bit                   | U = Unimpler                 | mented bit, rea               | d as '0'               |               |

| -n = Value at | POR                                                         | '1' = Bit is se                  | t                     | '0' = Bit is cle             | ared                          | x = Bit is unkno       | own           |

| bit 15-14     | Unimplemen                                                  | ted: Read as                     | 0'                    |                              |                               |                        |               |

| bit 13        | -                                                           |                                  |                       | nterrupt Flag S              | Status bit                    |                        |               |

|               | 1 = Interrupt i                                             | request has oc<br>request has no | curred                |                              |                               |                        |               |

| bit 12        |                                                             | RT1 Transmitte                   |                       | g Status bit <sup>(1)</sup>  |                               |                        |               |

|               |                                                             | request has oc                   |                       | ,                            |                               |                        |               |

|               |                                                             | request has no                   |                       |                              |                               |                        |               |

| oit 11        | U1RXIF: UAF                                                 | RT1 Receiver I                   | nterrupt Flag S       | Status bit <sup>(1)</sup>    |                               |                        |               |

|               |                                                             | request has oc<br>request has no |                       |                              |                               |                        |               |

| bit 10        | SPI1IF: SPI1 Event Interrupt Flag Status bit <sup>(1)</sup> |                                  |                       |                              |                               |                        |               |

|               |                                                             | request has oc<br>request has no |                       |                              |                               |                        |               |

| bit 9         | SPI1EIF: SPI                                                | 1 Error Interru                  | pt Flag Status        | bit <sup>(1)</sup>           |                               |                        |               |

|               |                                                             | request has oc<br>request has no |                       |                              |                               |                        |               |

| bit 8         | Unimplemen                                                  | ted: Read as                     | 0'                    |                              |                               |                        |               |

| bit 7         | T2IF: Timer2                                                | Interrupt Flag                   | Status bit            |                              |                               |                        |               |

|               |                                                             | request has oc<br>request has no |                       |                              |                               |                        |               |

| bit 6-4       | Unimplemen                                                  | ted: Read as                     | 0'                    |                              |                               |                        |               |

| bit 3         | T1IF: Timer1                                                | Interrupt Flag                   | Status bit            |                              |                               |                        |               |

|               | •                                                           | request has oc<br>request has no |                       |                              |                               |                        |               |

| bit 2         | -                                                           | -                                |                       | upt Flag Status              | s bit <sup>(1)</sup>          |                        |               |

|               | 1 = Interrupt                                               | request has oc<br>request has no | curred                | apt hag oldide               |                               |                        |               |

| bit 1         | -                                                           | -                                |                       | -lag Status bit <sup>(</sup> | 2)                            |                        |               |

|               |                                                             | request has oc<br>request has no |                       |                              |                               |                        |               |

| bit 0         | -                                                           | rnal Interrupt 0                 |                       | t                            |                               |                        |               |

|               | 1 = Interrupt ı                                             | request has oc<br>request has no | curred                |                              |                               |                        |               |

| Note 1: Th    | nis bit is not impl                                         | emented in the                   | ASPIC33F IOF          | GS001 device                 | 4                             |                        |               |

|               | no bit io not impl                                          |                                  |                       |                              | ·•                            |                        |               |

### REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0

### 10.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS001/101A/102A/ 202A and dsPIC33FJ09GS302 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 10.** "I/O Ports" (DS70193) in the "dsPIC33F/PIC24H Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

All of the device pins (except VDD, VSS, MCLR and OSC1/CLKI) are shared among the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

### 10.1 Parallel I/O (PIO) Ports

Generally a parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 10-1 shows how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

### 10.6.2.3 Virtual Pins

Four virtual RPn pins (RP32, RP33, RP34 and RP35) are supported, which are identical in functionality to all other RPn pins, with the exception of pinouts. These four pins are internal to the devices and are not connected to a physical device pin.

These pins provide a simple way for inter-peripheral connection without utilizing a physical pin. For example, the output of the analog comparator can be connected to RP32 and the PWM Fault input can be configured for RP32 as well. This configuration allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

# 10.6.3 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. dsPIC33F devices include three features to prevent alterations to the peripheral map:

- · Control register lock sequence

- Continuous state monitoring

- Configuration bit pin select lock

### 10.6.3.1 Control Register Lock

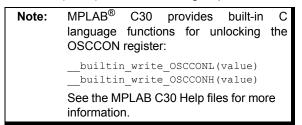

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (OSCCON<6>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear IOLOCK, a specific command sequence must be executed:

- 1. Write 0x46 to OSCCON<7:0>.

- 2. Write 0x57 to OSCCON<7:0>.

- 3. Clear (or set) IOLOCK as a single operation.

Unlike the similar sequence with the oscillator's LOCK bit, IOLOCK remains in one state until changed. This allows all of the Peripheral Pin Selects to be configured with a single unlock sequence, followed by an update to all control registers, then locked with a second lock sequence.

### 10.6.3.2 Continuous State Monitoring

In addition to being protected from direct writes, the contents of the RPINRx and RPORx registers are constantly monitored in hardware by shadow registers. If an unexpected change in any of the registers occurs (such as cell disturbances caused by ESD or other external events), a Configuration Mismatch Reset will be triggered.

### 10.6.3.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPINRx and RPORx registers. The IOL1WAY (FOSC<5>) Configuration bit blocks the IOLOCK bit from being cleared, after it has been set once. If IOLOCK remains set, the register unlock procedure will not execute and the Peripheral Pin Select Control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session. Programming IOL1WAY allows user applications unlimited access (with the proper use of the unlock sequence) to the Peripheral Pin Select registers.

### 13.1 Input Capture Registers

| U-0                  | U-0                         | R/W-0                                                                                     | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | U-0              | U-0             | U-0                | U-0           |  |  |  |  |

|----------------------|-----------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|--------------------|---------------|--|--|--|--|

|                      | —                           | ICSIDL                                                                                    | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | —                | _               | —                  | _             |  |  |  |  |

| bit 15               |                             |                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                 |                    | bit 8         |  |  |  |  |

| R/W-0                | R/W-0                       | R/W-0                                                                                     | R-0, HC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R-0, HC          | R/W-0           | R/W-0              | R/W-0         |  |  |  |  |

| ICTMR <sup>(1)</sup> |                             | <1:0>                                                                                     | ICOV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ICBNE            |                 | ICM<2:0>           | 10/00-0       |  |  |  |  |

| bit 7                |                             | \$1.02                                                                                    | 1007                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IODINE           |                 | 10101-2.02         | bit           |  |  |  |  |

|                      |                             |                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                 |                    |               |  |  |  |  |

| Legend:              |                             | HC = Hardwar                                                                              | e Clearable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                 |                    |               |  |  |  |  |

| R = Readat           | ole bit                     | W = Writable b                                                                            | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | U = Unimple      | mented bit, re  | ead as '0'         |               |  |  |  |  |

| -n = Value a         | at POR                      | '1' = Bit is set                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | '0' = Bit is cle | eared           | x = Bit is unkn    | iown          |  |  |  |  |

| bit 15-14            | Unimplemer                  | ited: Read as '0                                                                          | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |                 |                    |               |  |  |  |  |

| bit 13               | -                           | t Capture Modu                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Control bit      |                 |                    |               |  |  |  |  |

|                      | •                           | ture module hal                                                                           | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |                 |                    |               |  |  |  |  |

|                      | 0 = Input cap               | ture module cor                                                                           | ntinues to opera                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ate in CPU Idle  | mode            |                    |               |  |  |  |  |

| bit 12-8             | Unimplemer                  | ted: Read as '0                                                                           | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |                 |                    |               |  |  |  |  |

| bit 7                | ICTMR: Inpu                 | t Capture Timer                                                                           | Select bit <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  |                 |                    |               |  |  |  |  |

|                      | 1 = TMR2 co<br>0 = Reserved | ntents are captu<br>I                                                                     | ired on capture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | e event          |                 |                    |               |  |  |  |  |

| bit 6-5              | ICI<1:0>: Se                | lect Number of (                                                                          | Captures per In                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | terrupt bits     |                 |                    |               |  |  |  |  |

|                      |                             | t on every fourth                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | t                |                 |                    |               |  |  |  |  |