Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 13                                                                                |

| Program Memory Size        | 6КВ (2К х 24)                                                                     |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 256 x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 6x10b                                                                         |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                                    |

| Supplier Device Package    | 20-SSOP                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs101at-e-ss |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

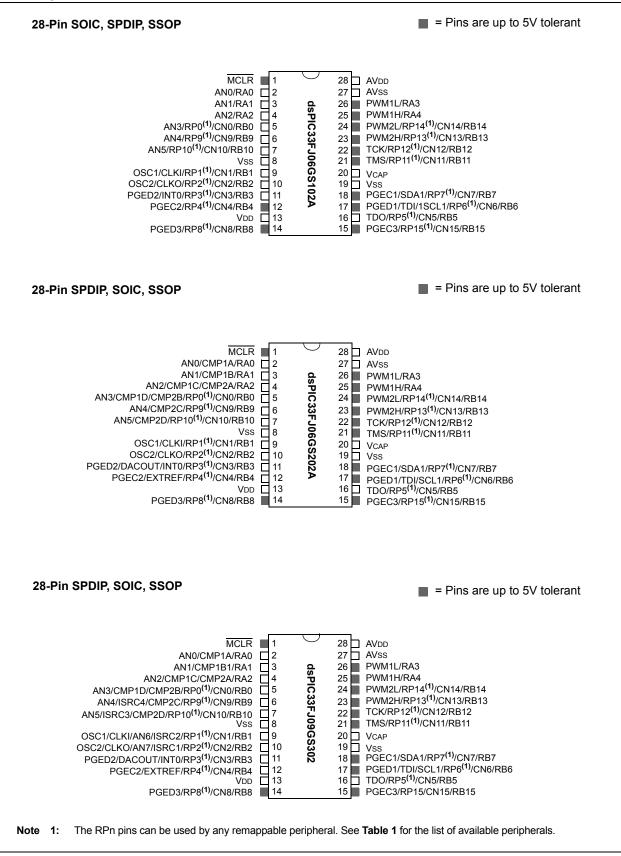

### **Pin Diagrams (Continued)**

### TABLE 4-16: I2C1 REGISTER MAP

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9                        | Bit 8            | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3    | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|---------|--------|---------|--------|--------|--------|------------------------------|------------------|-------|-------|-------|---------|----------|-------|-------|-------|---------------|

| I2C1RCV     | 0200        | _       | _      |         | —      | —      | —      | —                            | _                |       |       |       | Receive | Register |       |       |       | 0000          |

| I2C1TRN     | 0202        | _       |        | _       | _      | -      | _      | — — Transmit Register        |                  |       |       |       |         |          |       | OOFF  |       |               |

| I2C1BRG     | 0204        | _       |        | _       | _      | -      | _      | Baud Rate Generator Register |                  |       |       |       |         |          | 0000  |       |       |               |

| I2C1CON     | 0206        | I2CEN   |        | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                       | SMEN             | GCEN  | STREN | ACKDT | ACKEN   | RCEN     | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT    | 0208        | ACKSTAT | TRSTAT | _       | _      | -      | BCL    | GCSTAT                       | ADD10            | IWCOL | I2COV | D_A   | Р       | S        | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD     | 020A        | _       |        | _       | _      | -      | _      |                              | Address Register |       |       |       |         |          |       |       | 0000  |               |

| I2C1MSK     | 020C        | —       | _      |         | —      | _      | _      |                              |                  |       |       | AMSK  | <9:0>   |          |       |       |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-17: UART1 REGISTER MAP FOR dsPiC33FJ06GS101A, dsPiC33FJ06GS102A, dsPiC33FJ06GS202A AND dsPiC33FJ09GS302

| SFR Name | SFR<br>Addr | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8       | Bit 7        | Bit 6   | Bit 5 | Bit 4       | Bit 3   | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|----------|-------------|----------|--------|----------|--------|--------|--------|-------|-------------|--------------|---------|-------|-------------|---------|-------|--------|-------|---------------|

| U1MODE   | 0220        | UARTEN   | —      | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0        | WAKE         | LPBACK  | ABAUD | URXINV      | BRGH    | PDSEI | _<1:0> | STSEL | 0000          |

| U1STA    | 0222        | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT        | URXISE       | L<1:0>  | ADDEN | RIDLE       | PERR    | FERR  | OERR   | URXDA | 0110          |

| U1TXREG  | 0224        | _        | _      | -        | _      | _      | _      |       |             |              |         | UART  | Transmit Re | egister |       |        |       | XXXX          |

| U1RXREG  | 0226        | _        | _      | -        | _      | _      | _      | -     |             |              |         | UART  | Receive Re  | egister |       |        |       | 0000          |

| U1BRG    | 0228        |          | -      |          |        | •      |        | B     | aud Rate Ge | enerator Pre | escaler |       |             |         |       |        |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-18:SPI1 REGISTER MAP FOR dsPIC33FJ06GS101A, dsPIC33FJ06GS102A, dsPIC33FJ06GS202A AND dsPIC33FJ09GS302

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8       | Bit 7       | Bit 6       | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------------|--------|--------|---------|--------|--------|--------|-----------|-------------|-------------|-------------|-------|-------|-----------|-------|--------|--------|---------------|

| SPI1STAT | 0240        | SPIEN  | _      | SPISIDL |        |        |        |           | _           |             | SPIROV      | _     | _     | _         | _     | SPITBF | SPIRBF | 0000          |

| SPI1CON1 | 0242        | _      | _      | _       | DISSCK | DISSDO | MODE16 | SMP       | CKE         | SSEN        | CKP         | MSTEN |       | SPRE<2:0> |       | PPRE   | <1:0>  | 0000          |

| SPI1CON2 | 0244        | FRMEN  | SPIFSD | FRMPOL  |        | _      | _      | _         | _           | _           | _           | _     | _     | _         | _     | FRMDLY | _      | 0000          |

| SPI1BUF  | 0248        |        |        |         |        |        |        | SPI1 Tran | smit and Re | ceive Buffe | er Register |       |       |           |       |        |        | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-37: PMD REGISTER MAP FOR dsPIC33FJ06GS202A

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| PMD1        | 0770        | _      | —      | _      | T2MD   | T1MD   | —      | PWMMD  | —      | I2C1MD |       | U1MD  | —     | SPI1MD | _     | _     | ADCMD | 0000          |

| PMD2        | 0772        |        | _      | _      | _      | _      | _      | _      | IC1MD  | _      | _     | _     | _     | _      | _     | _     | OC1MD | 0000          |

| PMD3        | 0774        | _      |        |        |        |        | CMPMD  | _      | —      |        |       | —     | —     | —      |       |       | —     | 0000          |

| PMD4        | 0776        | _      |        |        |        |        | _      | _      | —      |        |       | —     | —     | REFOMD |       |       | —     | 0000          |

| PMD6        | 077A        | _      |        |        |        |        | _      | PWM2MD | PWM1MD |        |       | —     | —     | —      |       |       | —     | 0000          |

| PMD7        | 077C        | _      | _      | _      | _      |        | _      | CMP2MD | CMP1MD |        |       | _     | _     | _      |       | _     | —     | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-38: PMD REGISTER MAP FOR dsPIC33FJ09GS302

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| PMD1        | 0770        | -      | _      | _      | T2MD   | T1MD   | _      | PWMMD  | —      | I2C1MD | _     | U1MD  | -     | SPI1MD | —     | -     | ADCMD | 0000          |

| PMD2        | 0772        |        | _      | _      | _      | _      | _      | _      | IC1MD  | _      | _     | —     | _     | _      | _     | _     | OC1MD | 0000          |

| PMD3        | 0774        |        | _      | _      | _      | _      | CMPMD  | _      | _      | _      | _     | —     | _     | _      | _     | _     | _     | 0000          |

| PMD4        | 0776        |        | _      | _      | _      | _      | _      | _      | _      | _      | _     | —     | _     | REFOMD | _     | _     | _     | 0000          |

| PMD6        | 077A        |        | _      | _      | _      | PWM4MD | _      | PWM2MD | PWM1MD | _      | _     | —     | _     | _      | _     | _     | _     | 0000          |

| PMD7        | 077C        |        | _      | _      | _      | _      | _      | CMP2MD | CMP1MD | _      | _     | —     | _     | _      | _     | _     | _     | 0000          |

| PMD8        | 077E        | _      |        | _      |        | —      | —      | —      | —      | —      |       | —     |       | —      | -     | CCSMD | _     | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| U-0          | U-0           | U-0             | U-0            | U-0              | U-0                       | U-0                    | U-0                    |

|--------------|---------------|-----------------|----------------|------------------|---------------------------|------------------------|------------------------|

| _            | _             | _               | _              | _                | —                         | _                      | —                      |

| bit 15       | ·             |                 |                |                  |                           | ·                      | bit 8                  |

|              |               |                 |                |                  |                           |                        |                        |

| U-0          | U-0           | U-0             | R/W-0          | U-0              | U-0                       | R/W-0                  | R/W-0                  |

| _            | —             |                 | ADCP6IF        | —                | —                         | ADCP3IF <sup>(1)</sup> | ADCP2IF <sup>(2)</sup> |

| bit 7        |               |                 |                |                  |                           |                        | bit 0                  |

|              |               |                 |                |                  |                           |                        |                        |

| Legend:      |               |                 |                |                  |                           |                        |                        |

| R = Readat   | ole bit       | W = Writable    | bit            | U = Unimplei     | mented bit, rea           | ad as '0'              |                        |

| -n = Value a | at POR        | '1' = Bit is se | t              | '0' = Bit is cle | eared                     | x = Bit is unkr        | nown                   |

|              |               |                 |                |                  |                           |                        |                        |

| bit 15-5     | Unimplemen    | ted: Read as    | 'O'            |                  |                           |                        |                        |

| bit 4        | ADCP6IF: A    | DC Pair 6 Con   | version Done I | nterrupt Flag S  | Status bit                |                        |                        |

|              | 1 = Interrupt | request has o   | curred         |                  |                           |                        |                        |

|              | 0 = Interrupt | request has no  | ot occurred    |                  |                           |                        |                        |

| bit 3-2      | Unimplemen    | ted: Read as    | '0'            |                  |                           |                        |                        |

| bit 1        | ADCP3IF: A    | DC Pair 3 Con   | version Done I | nterrupt Flag S  | Status bit <sup>(1)</sup> |                        |                        |

|              | 1 = Interrupt | request has o   | curred         |                  |                           |                        |                        |

|              | 0 = Interrupt | request has no  | ot occurred    |                  |                           |                        |                        |

| bit 0        | ADCP2IF: AI   | DC Pair 2 Con   | version Done I | nterrupt Flag S  | Status bit <sup>(2)</sup> |                        |                        |

|              | 1 = Interrupt | request has o   | curred         |                  |                           |                        |                        |

|              |               | request has no  |                |                  |                           |                        |                        |

- Note 1: This bit is not implemented in dsPIC33FJ06GS102A/202A devices.

- 2: This bit is not implemented in dsPIC33FJ06GS001/101A devices.

| REGISTER      | 9-5: PMD6   | : PERIPHER                       | AL MODULE      | E DISABLE C             | ONTROL RE       | GISTER 6              |        |

|---------------|-------------|----------------------------------|----------------|-------------------------|-----------------|-----------------------|--------|

| U-0           | U-0         | U-0                              | U-0            | R/W-0                   | U-0             | R/W-0                 | R/W-0  |

| _             | _           | —                                |                | PWM4MD <sup>(1)</sup>   | —               | PWM2MD <sup>(2)</sup> | PWM1MD |

| bit 15        |             |                                  |                |                         |                 |                       | bit 8  |

| U-0           | U-0         | U-0                              | U-0            | U-0                     | U-0             | U-0                   | U-0    |

|               |             |                                  |                | <u> </u>                |                 |                       |        |

| bit 7         |             |                                  |                |                         |                 |                       | bit 0  |

| Legend:       |             |                                  |                |                         |                 |                       |        |

| R = Readable  | e bit       | W = Writable                     | bit            | U = Unimplem            | ented bit, read | d as '0'              |        |

| -n = Value at | POR         | '1' = Bit is set                 |                | '0' = Bit is clea       | ared            | x = Bit is unkn       | own    |

| bit 15-12     | Unimplomon  | ted: Read as '                   | ۰,             |                         |                 |                       |        |

| bit 11        | •           | NM Generator                     |                | able bit(1)             |                 |                       |        |

|               | 1 = PWM Ger | nerator 4 modu<br>nerator 4 modu | le is disabled |                         |                 |                       |        |

| bit 10        | Unimplement | ted: Read as '                   | )'             |                         |                 |                       |        |

| bit 9         | PWM2MD: PV  | WM Generator                     | 2 Module Disa  | able bit <sup>(2)</sup> |                 |                       |        |

|               | ±           | nerator 2 modu<br>nerator 2 modu |                |                         |                 |                       |        |

| bit 8         | PWM1MD: PV  | WM Generator                     | 1 Module Disa  | able bit                |                 |                       |        |

|               |             | nerator 1 modu<br>nerator 1 modu |                |                         |                 |                       |        |

| bit 7-0       | Unimplement | ted: Read as '                   | )'             |                         |                 |                       |        |

**Note 1:** This bit is not implemented in dsPIC33FJ06GS102A/202A devices.

**2:** This bit is not implemented in dsPIC33FJ06GS001/101A devices.

### **10.9** Peripheral Pin Select Registers

The following registers are implemented for remappable peripheral configuration:

- 15 Input Remappable Peripheral Registers

- 19 Output Remappable Peripheral Registers

- Note: Input and output register values can only be changed if IOLOCK (OSCCON<6>) = 0. See Section 10.6.3.1 "Control Register Lock" for a specific command sequence.

Not all Output Remappable Peripheral registers are implemented on all devices. See the register description of the specific register for further details.

### REGISTER 10-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0    | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1  | R/W-1 | R/W-1 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | INT1  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

|        |     |       |       |       |        |       |       |

| U-0    | U-0 | U-0   | U-0   | U-0   | U-0    | U-0   | U-0   |

| _      | _   | _     | _     | _     | _      | _     |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 7

bit 7-0

bit 13-8 INT1R<5:0>: Assign External Interrupt 1 (INTR1) to the Corresponding RPn Pin bits

| INT IN CONF. / Congri External III |

|------------------------------------|

| 111111 = Input tied to Vss         |

| 100011 = Input tied to RP35        |

| 100010 = Input tied to RP34        |

| 100001 = Input tied to RP33        |

| 100000 = Input tied to RP32        |

| •                                  |

| •                                  |

| •                                  |

| 00000 = Input tied to RP0          |

| Unimplemented: Read as '0'         |

bit 0

### REGISTER 10-18: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP5F  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP4F  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                               |

|-----------|--------------------------------------------------------------------------|

| bit 13-8  | RP5R<5:0>: Peripheral Output Function is Assigned to RP5 Output Pin bits |

|           | (see Table 10-2 for peripheral function numbers)                         |

| bit 7-6   | Unimplemented: Read as '0'                                               |

| bit 5-0   | RP4R<5:0>: Peripheral Output Function is Assigned to RP4 Output Pin bits |

|           | (see Table 10-2 for peripheral function numbers)                         |

### REGISTER 10-19: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP7   | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP6F  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

| bit 13-8 | RP7R<5:0>: Peripheral Output Function is Assigned to RP7 Output Pin bits |

|----------|--------------------------------------------------------------------------|

|          | (see Table 10-2 for peripheral function numbers)                         |

| bit 7-6  | Unimplemented: Read as '0'                                               |

|          |                                                                          |

bit 5-0 **RP6R<5:0>:** Peripheral Output Function is Assigned to RP6 Output Pin bits (see Table 10-2 for peripheral function numbers)

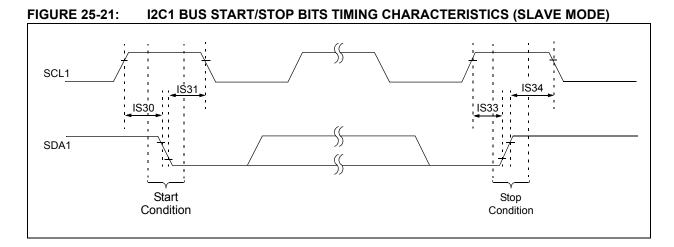

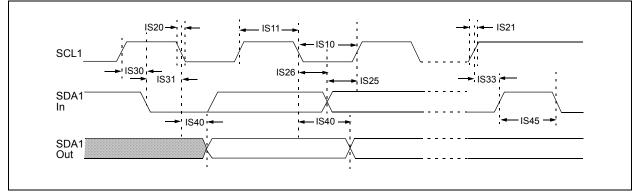

## 17.2 I<sup>2</sup>C Registers

I2C1CON and I2C1STAT are control and status registers, respectively. The I2C1CON register is readable and writable. The lower six bits of I2C1STAT are read-only. The remaining bits of the I2CSTAT are read/write:

- I2C1RSR is the shift register used for shifting data internal to the module and the user application has no access to it

- I2C1RCV is the receive buffer and the register to which data bytes are written, or from which data bytes are read

- I2C1TRN is the transmit register to which bytes are written during a transmit operation

- The I2C1ADD register holds the slave address

- A status bit, ADD10, indicates 10-Bit Address mode

- The I2C1BRG acts as the Baud Rate Generator (BRG) reload value

In receive operations, I2C1RSR and I2C1RCV together form a double-buffered receiver. When I2C1RSR receives a complete byte, it is transferred to I2C1RCV, and an interrupt pulse is generated.

## REGISTER 17-1: I2C1CON: I2C1 CONTROL REGISTER

| R/W-0  | U-0 | R/W-0   | R/W-1, HC | R/W-0  | R/W-0 | R/W-0  | R/W-0 |

|--------|-----|---------|-----------|--------|-------|--------|-------|

| I2CEN  | —   | I2CSIDL | SCLREL    | IPMIEN | A10M  | DISSLW | SMEN  |

| bit 15 |     |         |           |        |       |        | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0, HC |

|-------|-------|-------|-----------|-----------|-----------|-----------|-----------|

| GCEN  | STREN | ACKDT | ACKEN     | RCEN      | PEN       | RSEN      | SEN       |

| bit 7 |       |       |           |           |           |           | bit 0     |

| Legend:           | HC = Hardware Clearable bit |                             |                    |

|-------------------|-----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared        | x = Bit is unknown |

| I2CEN: I2C1 Enable bit                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>1 = Enables the I2C1 module and configures the SDA1 and SCL1 pins as serial port pins</li> <li>0 = Disables the I2C1 module; all I<sup>2</sup>C pins are controlled by port functions</li> </ul>                   |

| Unimplemented: Read as '0'                                                                                                                                                                                                  |

| I2CSIDL: Stop in Idle Mode bit                                                                                                                                                                                              |

| <ul> <li>1 = Discontinues module operation when device enters an Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul>                                                                                  |

| SCLREL: SCL1 Release Control bit (when operating as I <sup>2</sup> C slave)                                                                                                                                                 |

| 1 = Releases SCL1 clock<br>0 = Holds SCL1 clock low (clock stretch)                                                                                                                                                         |

| <u>If STREN = 1:</u><br>Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware is clear<br>at beginning of slave transmission. Hardware is clear at end of slave reception. |

| <u>If STREN = 0:</u><br>Bit is R/S (i.e., software can only write '1' to release clock). Hardware is clear at beginning of slave transmission.                                                                              |

| IPMIEN: Intelligent Peripheral Management Interface (IPMI) Enable bit                                                                                                                                                       |

| <ul><li>1 = IPMI mode is enabled; all addresses Acknowledged</li><li>0 = IPMI mode is disabled</li></ul>                                                                                                                    |

| A10M: 10-Bit Slave Address bit                                                                                                                                                                                              |

| <ul> <li>1 = I2C1ADD is a 10-bit slave address</li> <li>0 = I2C1ADD is a 7-bit slave address</li> </ul>                                                                                                                     |

| DISSLW: Disable Slew Rate Control bit                                                                                                                                                                                       |

| 1 = Slew rate control is disabled                                                                                                                                                                                           |

| 0 = Slew rate control is enabled                                                                                                                                                                                            |

|                                                                                                                                                                                                                             |

## REGISTER 18-1: U1MODE: UART1 MODE REGISTER (CONTINUED)

| bit 4   | URXINV: Receive Polarity Inversion bit <sup>(3)</sup><br>1 = U1RX Idle state is '0'<br>0 = U1RX Idle state is '1'                                             |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | <ul> <li>BRGH: High Baud Rate Enable bit<sup>(3)</sup></li> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> </ul>         |

|         | 0 = BRG generates 16 clocks per bit period (16 baud clock, Standard mode)                                                                                     |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits <sup>(3)</sup>                                                                                                     |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul> |

| bit 0   | <b>STSEL:</b> Stop Bit Selection bit <sup>(3)</sup><br>1 = Two Stop bits<br>0 = One Stop bit                                                                  |

- **Note 1:** Refer to **Section 17. "UART**" (DS70188) in the *"dsPIC33F/PIC24H Family Reference Manual"* for information on enabling the UART module for receive or transmit operation.

- **2:** This feature is only available for the 16x BRG mode (BRGH = 0).

- 3: This bit is not available in the dsPIC33FJ06GS001 device.

## **19.4 ADC Control Registers**

The ADC module uses the following control and status registers:

- ADCON: ADC Control Register

- ADSTAT: ADC Status Register

- ADBASE: ADC Base Register(1)

- ADPCFG: ADC Port Configuration Register

- ADCPC0: ADC Convert Pair Control Register 0

- ADCPC1: ADC Convert Pair Control Register 1

- ADCPC3: ADC Convert Pair Control Register 3(1)

The ADCON register controls the operation of the ADC module. The ADSTAT register displays the status of the conversion processes. The ADPCFG register configures the port pins as analog inputs or as digital I/Os. The ADCPCx registers control the triggering of the ADC conversions. See Register 19-1 through Register 19-7 for detailed bit configurations.

**Note:** A unique feature of the ADC module is its ability to sample inputs in an asynchronous manner. Individual Sample-and-Hold circuits can be triggered independently of each other.

## REGISTER 19-1: ADCON: ADC CONTROL REGISTER

| R/W-0  | U-0 | R/W-0  | R/W-0                  | U-0 | R/W-0  | U-0 | R/W-0               |

|--------|-----|--------|------------------------|-----|--------|-----|---------------------|

| ADON   | —   | ADSIDL | SLOWCLK <sup>(1)</sup> | —   | GSWTRG | -   | FORM <sup>(1)</sup> |

| bit 15 |     |        |                        |     |        |     | bit 8               |

| R/W-0              | R/W-0                | R/W-0                  | R/W-0                    | U-0 | R/W-0 | R/W-1        | R/W-1 |

|--------------------|----------------------|------------------------|--------------------------|-----|-------|--------------|-------|

| EIE <sup>(1)</sup> | ORDER <sup>(1)</sup> | SEQSAMP <sup>(1)</sup> | ASYNCSAMP <sup>(1)</sup> | _   |       | ADCS<2:0>(1) |       |

| bit 7              |                      |                        |                          |     |       |              | bit 0 |

| Legend:           |          |                                                                    |                                                                           |                    |  |  |

|-------------------|----------|--------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------|--|--|

| R = Reada         | ıble bit | W = Writable bit                                                   | U = Unimplemented bit, read as '0'                                        |                    |  |  |

| -n = Value at POR |          | '1' = Bit is set                                                   | '0' = Bit is cleared                                                      | x = Bit is unknown |  |  |

| bit 15            | 1 = ADC  | ADC Operating Mode bit<br>module is operating<br>module is off     |                                                                           |                    |  |  |

| bit 14            | Unimple  | mented: Read as '0'                                                |                                                                           |                    |  |  |

| bit 13            | ADSIDL   | : Stop in Idle Mode bit                                            |                                                                           |                    |  |  |

|                   |          | ontinues module operation wh<br>inues module operation in Idle     |                                                                           |                    |  |  |

| bit 12            | SLOWC    | LK: Enable Slow Clock Divide                                       | r bit <sup>(1)</sup>                                                      |                    |  |  |

|                   |          | c is clocked by the auxiliary PL<br>c is clocked by the primary PL | , ,                                                                       |                    |  |  |

| bit 11            | Unimple  | mented: Read as '0'                                                |                                                                           |                    |  |  |

| bit 10            | GSWTR    | G: Global Software Trigger bit                                     |                                                                           |                    |  |  |

|                   | ADCPCx   | • · · ·                                                            | rigger conversions if selected by<br>ared by the user prior to initiating |                    |  |  |

| bit 9             | Unimple  | mented: Read as '0'                                                |                                                                           |                    |  |  |

Note 1: This control bit can only be changed while the ADC is disabled (ADON = 0).

| REGISTER      | 19-5: ADCP                                            | CU: ADC CO                                             | NVERT PA                                          | IR CONTROL                                   | REGISTER (       | <b>)</b>          |           |

|---------------|-------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------|----------------------------------------------|------------------|-------------------|-----------|

| R/W-0         | R/W-0                                                 | R/W-0                                                  | R/W-0                                             | R/W-0                                        | R/W-0            | R/W-0             | R/W-0     |

| IRQEN1        | PEND1                                                 | SWTRG1                                                 |                                                   |                                              | TRGSRC1<4:0      | )>                |           |

| bit 15        |                                                       |                                                        |                                                   |                                              |                  |                   | bit       |

| R/W-0         | R/W-0                                                 | R/W-0                                                  | R/W-0                                             | R/W-0                                        | R/W-0            | R/W-0             | R/W-0     |

| IRQEN0        | PEND0                                                 | SWTRG0                                                 |                                                   |                                              | TRGSRC0<4:0      | )>                |           |

| bit 7         |                                                       |                                                        |                                                   |                                              |                  |                   | bit       |

| Legend:       |                                                       |                                                        |                                                   |                                              |                  |                   |           |

| R = Readabl   | e bit                                                 | W = Writable                                           | bit                                               | U = Unimplei                                 | mented bit, read | d as '0'          |           |

| -n = Value at |                                                       | '1' = Bit is set                                       |                                                   | '0' = Bit is cle                             |                  | x = Bit is unkr   | nown      |

|               |                                                       |                                                        |                                                   |                                              |                  |                   |           |

| bit 15        |                                                       |                                                        |                                                   | sted conversion                              | of channels Al   | N3 and AN2 is o   | completed |

| bit 14        |                                                       | ding Conversio                                         | on Status 1 bi                                    | t                                            |                  |                   |           |

|               | 1 = Conversi                                          | -                                                      |                                                   | 2 is pending; se                             | et when selecte  | d trigger is asse | erted     |

| bit 13        |                                                       | oftware Trigger                                        | 1 bit                                             |                                              |                  |                   |           |

|               | 1 = Starts co<br>This bit is au                       | onversion of AN                                        | I3 and AN2 (i<br>ared by hardv                    | f selected by the<br>vare when the F         |                  |                   |           |

| hit 10 0      |                                                       |                                                        |                                                   | ation hita                                   |                  |                   |           |

| bit 12-8      | Selects trigge                                        | 4:0>: Trigger 1<br>er source for co<br>ner2 period mat | onversion of a                                    | analog channels                              | AN3 and AN2.     |                   |           |

|               | •                                                     | ·                                                      |                                                   |                                              |                  |                   |           |

|               | •                                                     |                                                        |                                                   |                                              |                  |                   |           |

|               | •<br>11011 <b>= Res</b><br>11010 <b>= PW</b>          | served<br>/M Generator 4                               | current-limit                                     | ADC trigger                                  |                  |                   |           |

|               | 11001 <b>= Res</b>                                    | served                                                 |                                                   |                                              |                  |                   |           |

|               |                                                       | /M Generator 2<br>/M Generator 1<br>served             |                                                   |                                              |                  |                   |           |

|               | •                                                     |                                                        |                                                   |                                              |                  |                   |           |

|               | •                                                     |                                                        |                                                   |                                              |                  |                   |           |

|               |                                                       | M Generator 4                                          | secondary tr                                      | igger is selecte                             | d                |                   |           |

|               | 10000 = Res<br>01111 = PW                             |                                                        | secondarv tr                                      | igger is selecte                             | d                |                   |           |

|               |                                                       |                                                        |                                                   | igger is selected                            |                  |                   |           |

|               | 01101 <b>= Res</b><br>01100 <b>= Tim</b>              | served<br>ner1 period mat                              | ch                                                |                                              |                  |                   |           |

|               | •                                                     |                                                        |                                                   |                                              |                  |                   |           |

|               | 00110 = Res<br>00101 = PW<br>00100 = PW<br>00011 = PW | M Generator 4                                          | primary trigg<br>primary trigg<br>nt Trigger is s | er is selected<br>er is selected<br>selected |                  |                   |           |

|               | 00001 <b>= Ind</b> i                                  | ividual software<br>conversion is e                    | trigger is se                                     |                                              |                  |                   |           |

## REGISTER 19-5: ADCPC0: ADC CONVERT PAIR CONTROL REGISTER 0

**Note 1:** The trigger source must be set as a global software trigger prior to setting this bit to '1'. If other conversions are in progress, then conversion will be performed when the conversion resources are available.

| REGISTER 19-7: ADCPC3: ADC CONVERT PAIR CONTROL REGISTER 3 <sup>(1)</sup> |               |                  |              |                  |                |                 |             |  |  |

|---------------------------------------------------------------------------|---------------|------------------|--------------|------------------|----------------|-----------------|-------------|--|--|

| U-0                                                                       | U-0           | U-0              | U-0          | U-0              | U-0            | U-0             | U-0         |  |  |

| —                                                                         | —             | —                | _            | —                | —              | —               | —           |  |  |

| bit 15                                                                    |               |                  |              |                  |                |                 | bit 8       |  |  |

| R/W-0                                                                     | R/W-0         | R/W-0            | R/W-0        | R/W-0            | R/W-0          | R/W-0           | R/W-0       |  |  |

| IRQEN6                                                                    | PEND6         | SWTRG6           |              |                  | TRGSRC6<4      | :0>             |             |  |  |

| bit 7                                                                     |               |                  |              |                  |                |                 | bit 0       |  |  |

|                                                                           |               |                  |              |                  |                |                 |             |  |  |

| Legend:                                                                   |               |                  |              |                  |                |                 |             |  |  |

| R = Readable                                                              | bit           | W = Writable b   | bit          | U = Unimplei     | mented bit, re | ad as '0'       |             |  |  |

| -n = Value at F                                                           | POR           | '1' = Bit is set |              | '0' = Bit is cle | eared          | x = Bit is unkr | nown        |  |  |

|                                                                           |               |                  |              |                  |                |                 |             |  |  |

| bit 15-8                                                                  | Unimplemen    | ted: Read as '0  | ,            |                  |                |                 |             |  |  |

| bit 7                                                                     | IRQEN6: Inte  | rrupt Request E  | nable 6 bit  |                  |                |                 |             |  |  |

|                                                                           | 1 = Enable IR | Q generation w   | hen requeste | ed conversion o  | of channels AN | N13 and AN12 i  | s completed |  |  |

## ADADAA ADA AANNEDT DAID AANTDAL DEGIATED A(1)

|       | 0 = IRQ is not generated                                                                                                                                                                                                                        |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | <b>PEND6:</b> Pending Conversion Status 6 bit<br>1 = Conversion of channels AN13 and AN 12 is pending; set when selected trigger is asserted<br>0 = Conversion is complete                                                                      |

| bit 5 | SWTRG6: Software Trigger 6 bit                                                                                                                                                                                                                  |

|       | <ul> <li>1 = Starts conversion of AN13 (INTREF) and AN12 (EXTREF) if selected by TRGSRC bits<sup>(2)</sup></li> <li>This bit is automatically cleared by hardware when the PEND6 bit is set.</li> <li>0 = Conversion has not started</li> </ul> |

Note 1: If other conversions are in progress, conversion will be performed when the conversion resources are available.

2: AN13 is internally connected to Vref in all devices. AN12 is internally connected to the EXTREF pin in the dsPIC33FJ06001/202A and dsPIC33FJ09GS302 devices. The dsPIC33FJ06GS101A/102A devices not have an EXTREF pin; therefore, any data read on the corresponding AN12 input will be invalid.

### **REGISTER 19-7:** ADCPC3: ADC CONVERT PAIR CONTROL REGISTER 3<sup>(1)</sup> (CONTINUED)

```

bit 4-0

TRGSRC6<4:0>: Trigger 6 Source Selection bits

Selects trigger source for conversion of analog channels AN13 and AN12.

11111 = Timer2 period match

11011 = Reserved

11010 = PWM Generator 4 current-limit ADC trigger

11001 = Reserved

11000 = PWM Generator 2 current-limit ADC trigger

10111 = PWM Generator 1 current-limit ADC trigger

10110 = Reserved

10010 = Reserved

10001 = PWM Generator 4 secondary trigger is selected

10000 = Reserved

01111 = PWM Generator 2 secondary trigger is selected

01110 = PWM Generator 1 secondary trigger is selected

01101 = Reserved

```

01101 = Timer1 period match 01100 = Timer1 period match 01000 = Reserved 00111 = PWM Generator 4 primary trigger is selected 00101 = PWM Generator 2 primary trigger is selected 00100 = PWM Generator 1 primary trigger is selected 00011 = PWM Special Event Trigger is selected 00011 = Global software trigger is selected 00001 = Individual software trigger is selected

00000 = No conversion is enabled

- **Note 1:** If other conversions are in progress, conversion will be performed when the conversion resources are available.

- 2: AN13 is internally connected to Vref in all devices. AN12 is internally connected to the EXTREF pin in the dsPIC33FJ06001/202A and dsPIC33FJ09GS302 devices. The dsPIC33FJ06GS101A/102A devices not have an EXTREF pin; therefore, any data read on the corresponding AN12 input will be invalid.

| U-0                                                                    | U-0 | U-0 | U-0             | U-0              | U-0      | U-0 | U-0    |

|------------------------------------------------------------------------|-----|-----|-----------------|------------------|----------|-----|--------|

| —                                                                      |     | —   | _               | —                | _        | —   | —      |

| bit 23                                                                 |     |     |                 |                  |          |     | bit 16 |

|                                                                        |     |     |                 |                  |          |     |        |

| U-0                                                                    | U-0 | U-0 | U-0             | U-0              | U-0      | U-0 | U-0    |

| —                                                                      | _   | —   | —               | —                | —        |     | —      |

| bit 15                                                                 |     |     |                 |                  |          |     | bit 8  |

|                                                                        |     |     |                 |                  |          |     |        |

| U-0                                                                    | U-0 | R-0 | R-0             | R-0              | R-0      | R-0 | R-0    |

| _                                                                      | _   |     |                 | CCSC             |          |     |        |

| bit 7                                                                  |     |     |                 |                  |          |     | bit 0  |

|                                                                        |     |     |                 |                  |          |     |        |

| Legend:                                                                |     |     |                 |                  |          |     |        |

| R = Readable bit W = Writable bit                                      |     |     | U = Unimplei    | mented bit, read | 1 as '0' |     |        |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unk |     |     | x = Bit is unkr | nown             |          |     |        |

### REGISTER 22-1: CONSTANT CURRENT SOURCE CALIBRATION REGISTER

bit 23-6 Unimplemented: Read as '0'

bit 5-0 CCSCAL<5:0>: Constant Current Source Calibration bits

The value of these bits must be copied into the ISRCCAL<5:0> bits (ISRCCON<5:0>). Refer to the Current Source Control register (Register 21-1) in **Section 21.0** "**Constant Current Source**".

## 25.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33FJ06GS001/101A/102A/202A and dsPIC33FJ09GS302 electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

## Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias                                                     | 40°C to +125°C        |

|------------------------------------------------------------------------------------|-----------------------|

| Storage temperature                                                                | 65°C to +150°C        |

| Voltage on VDD with respect to Vss                                                 | -0.3V to +4.0V        |

| Voltage on any pin that is not 5V tolerant, with respect to Vss <sup>(3)</sup>     | -0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss, when $V_{DD} \ge 3.0 V^{(3)}$  | -0.3V to +5.6V        |

| Voltage on any 5V tolerant pin with respect to Vss, when VDD < 3.0V <sup>(3)</sup> | 0.3V to (VDD + 0.3V)  |

| Maximum current out of Vss pin                                                     |                       |

| Maximum current into VDD pin <sup>(2)</sup>                                        |                       |

| Maximum current sourced/sunk by any 4x I/O pin                                     |                       |

| Maximum current sourced/sunk by any 16x I/O pin                                    | 45 mA                 |

| Maximum current sunk by all ports                                                  |                       |

| Maximum current sourced by all ports <sup>(2)</sup>                                | 200mA                 |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 25-2).

- 3: See the "Pin Diagrams" section for 5V tolerant pins.

| DC CHARA  | ACTERISTICS            | 8    | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V (unless otherwise s otherwise s -40°C \leq TA \leq +85°C for Industrial -40°C \leq TA \leq +125°C for Extended \end{array}$ |        |        |                                |  |  |

|-----------|------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------------------------------|--|--|

| Param.    | Typical <sup>(1)</sup> | Max. | Units                                                                                                                                                                                           |        |        | Conditions                     |  |  |

| Operating | Current (IDD)          | (2)  |                                                                                                                                                                                                 |        |        |                                |  |  |

| DC20d     | 15                     | 23   | mA                                                                                                                                                                                              | -40°C  |        |                                |  |  |

| DC20a     | 15                     | 23   | mA                                                                                                                                                                                              | +25°C  | 3.3V   | 10 MIPS                        |  |  |

| DC20b     | 15                     | 23   | mA                                                                                                                                                                                              | +85°C  | 3.3V   | TO MIPS                        |  |  |

| DC20c     | 15                     | 23   | mA                                                                                                                                                                                              | +125°C |        |                                |  |  |

| DC21d     | 23                     | 34   | mA                                                                                                                                                                                              | -40°C  |        |                                |  |  |

| DC21a     | 23                     | 34   | mA                                                                                                                                                                                              | +25°C  | 0.01/  | 16 MIPS <sup>(3)</sup>         |  |  |

| DC21b     | 23                     | 34   | mA                                                                                                                                                                                              | +85°C  | - 3.3V | 16 MIPS(*)                     |  |  |

| DC21c     | 23                     | 34   | mA                                                                                                                                                                                              | +125°C |        |                                |  |  |

| DC22d     | 25                     | 38   | mA                                                                                                                                                                                              | -40°C  |        |                                |  |  |

| DC22a     | 25                     | 38   | mA                                                                                                                                                                                              | +25°C  | 2.21/  | 20 MIPS <sup>(3)</sup>         |  |  |

| DC22b     | 25                     | 38   | mA                                                                                                                                                                                              | +85°C  | - 3.3V | 20 MIPS(*)                     |  |  |

| DC22c     | 25                     | 38   | mA                                                                                                                                                                                              | +125°C |        |                                |  |  |

| DC23d     | 34                     | 51   | mA                                                                                                                                                                                              | -40°C  |        |                                |  |  |

| DC23a     | 34                     | 51   | mA                                                                                                                                                                                              | +25°C  | 3.3V   | 30 MIPS <sup>(3)</sup>         |  |  |

| DC23b     | 34                     | 51   | mA                                                                                                                                                                                              | +85°C  | - 3.3V | 30 MIPS(*)                     |  |  |

| DC23c     | 34                     | 51   | mA                                                                                                                                                                                              | +125°C |        |                                |  |  |

| DC24d     | 43                     | 64   | mA                                                                                                                                                                                              | -40°C  |        |                                |  |  |

| DC24a     | 43                     | 64   | mA                                                                                                                                                                                              | +25°C  | 2 2)/  | 40 MIPS <sup>(3)</sup>         |  |  |

| DC24b     | 43                     | 64   | mA                                                                                                                                                                                              | +85°C  | - 3.3V | 40 MIP 5 9                     |  |  |

| DC24c     | 43                     | 64   | mA                                                                                                                                                                                              | +125°C |        |                                |  |  |

| DC25d     | 83                     | 125  | mA                                                                                                                                                                                              | -40°C  |        | 40 MIPS                        |  |  |

| DC25a     | 83                     | 125  | mA                                                                                                                                                                                              | +25°C  | 3.3V   | See Note 2, except PWM and ADC |  |  |

| DC25b     | 83                     | 125  | mA                                                                                                                                                                                              | +85°C  | J.JV   | are operating at maximum speed |  |  |

| DC25c     | 83                     | 125  | mA                                                                                                                                                                                              | +125°C |        | (PTCON2 = 0x0000)              |  |  |

### TABLE 25-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

2: IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

- Oscillator is configured in EC mode, OSC1 is driven with external square wave from rail-to-rail

- CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD; WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (PMDx bits are all zeroed)

- CPU is executing while (1) statement

- **3:** These parameters are characterized but not tested in manufacturing.

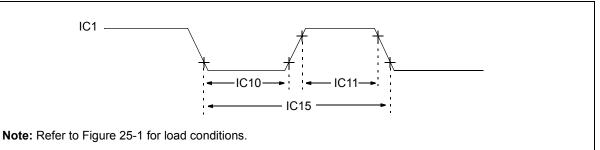

### FIGURE 25-6: INPUT CAPTURE (CAP1) TIMING CHARACTERISTICS

### TABLE 25-25: INPUT CAPTURE TIMING REQUIREMENTS

| AC CHARACTERISTICS                          |      |                     |                | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |      |       |                                  |  |

|---------------------------------------------|------|---------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----------------------------------|--|

| Param. Symbol Characteristic <sup>(1)</sup> |      |                     |                | Min.                                                                                                                                                                                                 | Max. | Units | Conditions                       |  |

| IC10 TccL IC1 Input Low Time                |      | No prescaler        | 0.5 Tcy + 20   | _                                                                                                                                                                                                    | ns   |       |                                  |  |

|                                             |      |                     | With prescaler | 10                                                                                                                                                                                                   |      | ns    |                                  |  |

| IC11                                        | TccH | IC1 Input High Time | No prescaler   | 0.5 Tcy + 20                                                                                                                                                                                         | _    | ns    |                                  |  |

|                                             |      |                     | With prescaler | 10                                                                                                                                                                                                   | _    | ns    |                                  |  |

| IC15                                        | TccP | IC1 Input Period    | ·              | (Tcy + 40)/N                                                                                                                                                                                         | —    | ns    | N = prescale value<br>(1, 4, 16) |  |

Note 1: These parameters are characterized but not tested in manufacturing.

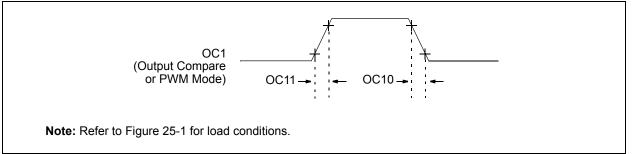

### FIGURE 25-7: OUTPUT COMPARE MODULE (OC1) TIMING CHARACTERISTICS

### TABLE 25-26: OUTPUT COMPARE MODULE TIMING REQUIREMENTS

|        |                                                           |                               | $\begin{array}{ll} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |                    |            |

|--------|-----------------------------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|--------------------|------------|

| Param. | Symbol                                                    | Characteristic <sup>(1)</sup> | Min.                                                                                                                                                                                                                                                                                     | Тур. | Max. | Units              | Conditions |

| OC10   | TccF                                                      | OC1 Output Fall Time          | — — — ns See Parameter DO32                                                                                                                                                                                                                                                              |      |      |                    |            |

| OC11   | OC11 TccR OC1 Output Rise Time — — — ns See Parameter DO3 |                               |                                                                                                                                                                                                                                                                                          |      |      | See Parameter DO31 |            |

Note 1: These parameters are characterized but not tested in manufacturing.

NOTES:

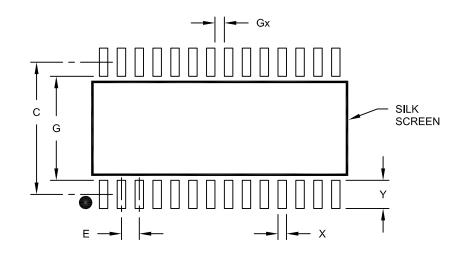

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## **RECOMMENDED LAND PATTERN**

|                          | Units           |      |      |      |  |  |

|--------------------------|-----------------|------|------|------|--|--|

| Dimensio                 | n Limits        | MIN  | NOM  | MAX  |  |  |

| Contact Pitch            | Contact Pitch E |      |      |      |  |  |

| Contact Pad Spacing      | С               |      | 9.40 |      |  |  |

| Contact Pad Width (X28)  | Х               |      |      | 0.60 |  |  |

| Contact Pad Length (X28) | Y               |      |      | 2.00 |  |  |

| Distance Between Pads    | Gx              | 0.67 |      |      |  |  |

| Distance Between Pads    | G               | 7.40 |      |      |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A