Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

ХF

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 6KB (2K x 24)                                                                    |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 256 x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

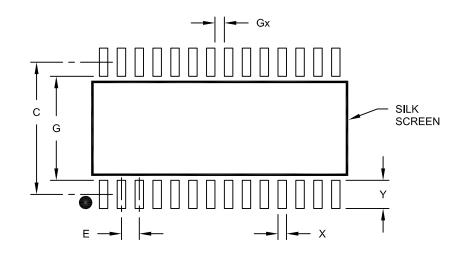

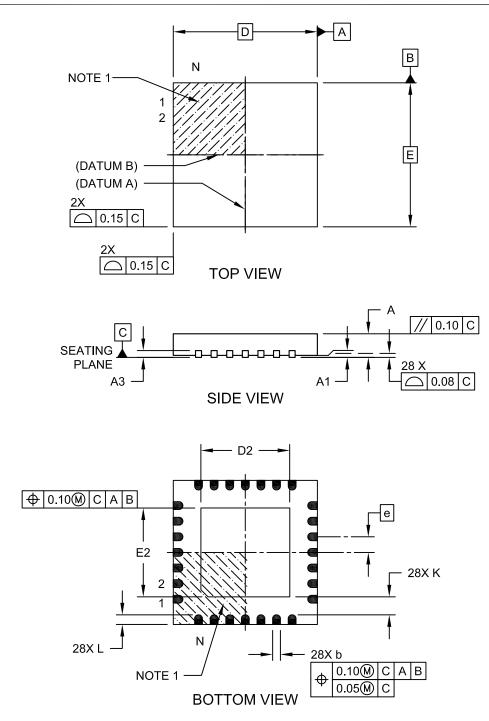

| Mounting Type              | Through Hole                                                                     |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                          |

| Supplier Device Package    | 28-SPDIP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs102a-e-sp |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.6.1 MULTIPLIER

The 17-bit x 17-bit multiplier is capable of signed or unsigned operation and can multiplex its output using a scaler to support either 1.31 fractional (Q31) or 32-bit integer results. Unsigned operands are zero-extended into the 17th bit of the multiplier input value. Signed operands are sign-extended into the 17th bit of the multiplier input value. The output of the 17-bit x 17-bit multiplier/scaler is a 33-bit value that is sign-extended to 40 bits. Integer data is inherently represented as a signed 2's complement value, where the Most Significant bit (MSb) is defined as a sign bit. The range of an N-bit 2's complement integer is  $-2^{N-1}$  to  $2^{N-1} - 1$ .

- For a 16-bit integer, the data range is -32768 (0x8000) to 32767 (0x7FFF) including 0

- For a 32-bit integer, the data range is

-2,147,483,648 (0x8000 0000) to 2,147,483,647 (0x7FFF FFFF)

When the multiplier is configured for fractional multiplication, the data is represented as a 2's complement fraction, where the MSb is defined as a sign bit and the radix point is implied to lie just after the sign bit (QX format). The range of an N-bit 2's complement fraction with this implied radix point is -1.0 to  $(1 - 2^{1-N})$ . For a 16-bit fraction, the Q15 data range is -1.0 (0x8000) to 0.999969482 (0x7FFF) including 0 and has a precision of 3.01518x10<sup>-5</sup>. In Fractional mode, the 16 x 16 multiply operation generates a 1.31 product that has a precision of 4.65661 x 10<sup>-10</sup>.

The same multiplier is used to support the MCU multiply instructions, which include integer 16-bit signed, unsigned and mixed-sign multiply operations.

The MUL instruction can be directed to use byte or word-sized operands. Byte operands will direct a 16-bit result, and word operands will direct a 32-bit result to the specified register(s) in the W array.

# 3.6.2 DATA ACCUMULATORS AND ADDER/SUBTRACTER

The data accumulator consists of a 40-bit adder/ subtracter with automatic sign extension logic. It can select one of two accumulators (A or B) as its preaccumulation source and post-accumulation destination. For the ADD and LAC instructions, the data to be accumulated or loaded can be optionally scaled using the barrel shifter prior to accumulation.

# 3.6.2.1 Adder/Subtracter, Overflow and Saturation

The adder/subtracter is a 40-bit adder with an optional zero input into one side, and either true or complement data into the other input.

- In the case of addition, the Carry/Borrow input is active-high and the other input is true data (not complemented)

- In the case of subtraction, the Carry/Borrow input is active-low and the other input is complemented

The adder/subtracter generates Overflow Status bits, SA/SB and OA/OB, which are latched and reflected in the STATUS register:

- Overflow from bit 39: This is a catastrophic overflow in which the sign of the accumulator is destroyed

- Overflow into guard bits, 32 through 39: This is a recoverable overflow. This bit is set whenever all the guard bits are not identical to each other.

The adder has an additional saturation block that controls accumulator data saturation, if selected. It uses the result of the adder, the Overflow Status bits described previously and the SAT<A:B> (CORCON<7:6>) and ACCSAT (CORCON<4>) mode control bits to determine when and to what value to saturate.

Six STATUS register bits support saturation and overflow:

- · OA: ACCA overflowed into guard bits

- OB: ACCB overflowed into guard bits

- SA: ACCA saturated (bit 31 overflow and saturation) or

ACCA overflowed into guard bits and saturated (bit 39 overflow and saturation)

SB: ACCB saturated (bit 31 overflow and saturation)

ACCB overflowed into guard bits and saturated (bit 39 overflow and saturation)

- · OAB: Logical OR of OA and OB

- · SAB: Logical OR of SA and SB

The OA and OB bits are modified each time data passes through the adder/subtracter. When set, they indicate that the most recent operation has overflowed into the accumulator guard bits (bits 32 through 39). The OA and OB bits can also optionally generate an arithmetic warning trap when set and the corresponding Overflow Trap Enable bits (OVATE, OVBTE) in the INTCON1 register are set (refer to **Section 7.0 "Interrupt Controller"**). This allows the user application to take immediate action, for example, to correct system gain.

The SA and SB bits are modified each time data passes through the adder/subtracter, but can only be cleared by the user application. When set, they indicate that the accumulator has overflowed its maximum range (bit 31 for 32-bit saturation or bit 39 for 40-bit saturation) and will be saturated (if saturation is enabled). When saturation is not enabled, SA and SB default to bit 39 overflow and thus, indicate that a catastrophic overflow has occurred. If the COVTE bit in the INTCON1 register is set, SA and SB bits will generate an arithmetic warning trap when saturation is disabled.

#### 4.2.5 X AND Y DATA SPACES

The core has two data spaces, X and Y. These data spaces can be considered either separate (for some DSP instructions), or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms, such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X data space is used by all instructions and supports all addressing modes. X data space has separate read and write data buses. The X read data bus is the read data path for all instructions that view data space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y data space is used in concert with the X data space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y data spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X data space.

All data memory writes, included in DSP instructions, view data space as combined X and Y address space. The boundary between the X and Y data spaces is device-dependent and is not user-programmable.

All Effective Addresses are 16 bits wide and point to bytes within the data space. Therefore, the data space address range is 64 Kbytes, or 32K words, though the implemented memory locations vary by device.

#### **Flash Memory Control Registers** 5.5

| bit 15       Invariant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/SO-0            | R/W-0                       | R/W-0                          | U-0                                   | U-0                         | U-0                | U-0                    | U-0           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------|--------------------------------|---------------------------------------|-----------------------------|--------------------|------------------------|---------------|

| U-0       R/W-0       U-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         Image: Image                                                                                                                                                                                                                                                                                                        | WR <sup>(1)</sup> | WREN <sup>(1)</sup>         | WRERR <sup>(1)</sup>           | _                                     | —                           | _                  | _                      | _             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | bit 15            |                             | · · ·                          |                                       |                             |                    | ·                      | bit 8         |

| -         ERASE <sup>(1)</sup> -         NVMOP<3:0::         1.2           bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | U-0               | R/W-0                       | U-0                            | U-0                                   | R/W-0                       | R/W-0              | R/W-0                  | R/W-0         |

| bit 7       bit 7         Legend:       SO = Settable Only bit         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       WR: Write Control bit <sup>(1)</sup> 1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the b cleared by hardware once operation is complete. This bit can only be set (not cleared) in software once operation is complete and inactive         bit 14       WREN: Write Enable bit <sup>(1)</sup> 1 = Enables Flash program/erase operations         o = Inhibits Flash program/erase operations       o = Inhibits Flash program/erase operations         bit 13       WRERR: Write Sequence Error Flag bit <sup>(1)</sup> 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation sepecified by NVMOP<3:0> on the next WR command         bit 6       ERASE: Erase/Program Enable bit <sup>(1)</sup> 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         bit 5-4       Unimplemented: Read as '0'         bit 3-0       NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1:       1111 = No operation         1011 = No operation       0010 = Memory page erase operation         0011 = No oper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                 |                             | _                              | _                                     |                             | NVMOP              | <3:0> <sup>(1,2)</sup> | -             |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       WR: Write Control bit <sup>(1)</sup> 1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the bic cleared by hardware once operation is complete. This bit can only be set (not cleared) in software one operation is complete and inactive         bit 14       WREN: Write Enable bit <sup>(1)</sup> 1 = Enables Flash program/erase operations         0 = Inhibits Flash program/erase operations       0 = Inhibits Flash program/erase operations         bit 13       WRERR: Write Sequence Error Flag bit <sup>(1)</sup> 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation selectified by NVMOP<3:0> on the next WR command         0 = Performs the program operation Select bits <sup>(1,2)</sup> If ERASE = 1:         1111 = No operation         1010 = Erase general segment         0011 = Memory page erase operation         0011 = No operation         0011 = Reserved         If ERASE = 0:         11111 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 7             |                             |                                |                                       |                             |                    |                        | bit           |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       WR: Write Control bit <sup>(1)</sup> 1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the bic cleared by hardware once operation is complete. This bit can only be set (not cleared) in software once operation is complete and inactive         bit 14       WREN: Write Enable bit <sup>(1)</sup> 1 = Enables Flash program/erase operations         0 = Inhibits Flash program/erase operations       0 = Inhibits Flash program/erase operations         bit 13       WRERR: Write Sequence Error Flag bit <sup>(1)</sup> 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         0 = Depration       1101 = Erase general segment         0101 = No operation       1101 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Legend:           |                             | SO = Settab                    | le Only bit                           |                             |                    |                        |               |

| bit 15 WR: Write Control bit <sup>(1)</sup><br>1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the b<br>cleared by hardware once operation is complete. This bit can only be set (not cleared) in softwa<br>0 = Program or erase operation is complete and inactive<br>bit 14 WREN: Write Enable bit <sup>(1)</sup><br>1 = Enables Flash program/erase operations<br>0 = Inhibits Flash program/erase operations<br>bit 13 WRERR: Write Sequence Error Flag bit <sup>(1)</sup><br>1 = An improper program or erase sequence attempt or termination has occurred (bit is<br>automatically on any set attempt of the WR bit)<br>0 = The program or erase operation completed normally<br>bit 6 ERASE: Erase/Program Enable bit <sup>(1)</sup><br>1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command<br>0 = Performs the program operation specified by NVMOP<3:0> on the next WR command<br>0 = Performs the program operation specified by NVMOP<3:0> on the next WR command<br>bit 5-4 Unimplemented: Read as 'o'<br>bit 3-0 NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup><br><u>If ERASE = 1:</u><br>1111 = No operation<br>1001 = Erase general segment<br>0010 = Reserved<br>0000 = Reserved<br><u>If ERASE = 0:</u><br>1111 = No operation<br>1001 = No operation                                                                                                                                                                                                                                                               | R = Readable      | e bit                       | W = Writable                   | e bit                                 | U = Unimple                 | mented bit, read   | l as '0'               |               |

| 1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the bicleared by hardware once operation is complete. This bit can only be set (not cleared) in software or erase operation is complete and inactive         0 = Program or erase operation is complete and inactive         bit 14       WREN: Write Enable bit <sup>(1)</sup> 1 = Enables Flash program/erase operations         0 = Inhibits Flash program/erase operations         0 = Inhibits Flash program/erase operations         bit 13       WRERR: Write Sequence Error Flag bit <sup>(1)</sup> 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation specified hy NVMOP<3:0> on the next WR command         0 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation Select bits <sup>(1,2)</sup> If ERASE = 1:         1111 = No operation         1101 = Erase general segment         011 = No operation         1101 = Reserved         0000 = Reserved         If ERASE = 0:         1111 = No operation         1101 = No operation         1101 = No operation         1111 = No operation         1101 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -n = Value at     | POR                         | '1' = Bit is se                | et                                    | '0' = Bit is cle            | eared              | x = Bit is unkr        | iown          |

| cleared by hardware once operation is complete. This bit can only be set (not cleared) in softwa<br>0 = Program or erase operation is complete and inactive<br>bit 14 WREN: Write Enable bit <sup>(1)</sup><br>1 = Enables Flash program/erase operations<br>0 = Inhibits Flash program/erase operations<br>bit 13 WRERR: Write Sequence Error Flag bit <sup>(1)</sup><br>1 = An improper program or erase sequence attempt or termination has occurred (bit is<br>automatically on any set attempt of the WR bit)<br>0 = The program or erase operation completed normally<br>bit 12-7 Unimplemented: Read as '0'<br>bit 6 ERASE: Erase/Program Enable bit <sup>(1)</sup><br>1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command<br>0 = Performs the program operation specified by NVMOP<3:0> on the next WR command<br>0 = Performs the program operation specified by NVMOP<3:0> on the next WR command<br>bit 5-4 Unimplemented: Read as '0'<br>bit 3-0 NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup><br>If ERASE = 1:<br>1111 = No operation<br>1010 = Erase general segment<br>0011 = No operation<br>0010 = Memory page erase operation<br>0010 = Reserved<br>0000 = Reserved<br>1111 = No operation<br>1011 | bit 15            |                             |                                |                                       | r orono oporati             | on The operation   | an is colf timed       | and the bit i |

| bit 14 WREN: Write Enable bit <sup>(1)</sup> 1 = Enables Flash program/erase operations 0 = Inhibits Flash program/erase operations bit 13 WRERR: Write Sequence Error Flag bit <sup>(1)</sup> 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit) 0 = The program or erase operation completed normally bit 12-7 Unimplemented: Read as '0' bit 6 ERASE: Erase/Program Enable bit <sup>(1)</sup> 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command 0 = Performs the program operation specified by NVMOP<3:0> on the next WR command 0 = Performs the program operation specified by NVMOP<3:0> on the next WR command 0 = Performs the program operation Select bits <sup>(1,2)</sup> bit 3-0 NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1: 1111 = No operation 1101 = Erase general segment 0011 = No operation 0010 = Memory page erase operation 0010 = Reserved 0000 = Reserved 0000 = Reserved 1111 = No operation 1011 = No operation 1011 = No operation 1011 = No operation 1011 = No operation 0010 = Memory word program operation 0011 = Memory word program operation 0010 = No operation 0011 = No operation 0010 = No operati                                                                                                                              |                   | cleared by                  | hardware onc                   | eoperation                            | is complete. Th             | is bit can only be |                        |               |

| 1 = Enables Flash program/erase operations         0 = Inhibits Flash program/erase operations         bit 13       WRERR: Write Sequence Error Flag bit <sup>(1)</sup> 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation completed normally         bit 12-7       Unimplemented: Read as '0'         bit 6       ERASE: Erase/Program Enable bit <sup>(1)</sup> 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         bit 5-4       Unimplemented: Read as '0'         bit 3-0       NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1:       1111 = No operation         1101 = Erase general segment       0011 = No operation         0010 = Memory page erase operation       0000 = Reserved         0000 = Reserved       If ERASE = 0:         1111 = No operation       1101 = No operation         1101 = No operation       0011 = No operation         1011 = No operation       10011 = No operation         1001 = No operation       0011 = No operation         1011 = No operation       1011 = No operation         1001 = No operation       0011 = Ne operation         0011 = Ne operatio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 14            | •                           |                                | · · · · · · · · · · · · · · · · · · · |                             |                    |                        |               |

| 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation completed normally         bit 12-7       Unimplemented: Read as '0'         bit 6       ERASE: Erase/Program Enable bit <sup>(1)</sup> 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         bit 5-4       Unimplemented: Read as '0'         bit 3-0       NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1:       1111 = No operation         101 = Erase general segment       0011 = No operation         0010 = Memory page erase operation       0010 = Reserved         If ERASE = 0:       1111 = No operation         1101 = No operation       1001 = Reserved         0000 = Reserved       If ERASE = 0:         1111 = No operation       1101 = No operation         0101 = No operation       0011 = Nemory word program operation         011 = No operation       0011 = Nemory word program operation         0011 = Nemory word program operation       0011 = Nemory word program operation         0010 = No operation       0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |                             |                                |                                       |                             |                    |                        |               |

| 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation completed normally         bit 12-7       Unimplemented: Read as '0'         bit 6       ERASE: Erase/Program Enable bit <sup>(1)</sup> 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         bit 5-4       Unimplemented: Read as '0'         bit 3-0       NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1:       1111 = No operation         101 = Erase general segment       0011 = Reserved         0010 = Memory page erase operation       0011 = Reserved         1111 = No operation       1101 = No operation         0010 = Reserved       If ERASE = 0:         11111 = No operation       1101 = No operation         0011 = Reserved       0000 = Reserved         1101 = No operation       1101 = No operation         1101 = No operation       1101 = No operation         1101 = No operation       1101 = No operation         0011 = Nemory word program operation       0011 = Memory word program operation         0011 = No operation       011 = No operation         0110 = No operation       011 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit 13            | WRERR: Write                | Sequence Er                    | ror Flag bit <sup>(</sup>             | 1)                          |                    |                        |               |

| bit 12-7 Unimplemented: Read as '0'<br>bit 6 ERASE: Erase/Program Enable bit <sup>(1)</sup><br>1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command<br>0 = Performs the program operation specified by NVMOP<3:0> on the next WR command<br>bit 5-4 Unimplemented: Read as '0'<br>bit 3-0 NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup><br>If ERASE = 1:<br>1111 = No operation<br>1101 = Erase general segment<br>0011 = No operation<br>0010 = Memory page erase operation<br>0010 = Reserved<br>0000 = Reserved<br>If ERASE = 0:<br>1111 = No operation<br>101 = No operation<br>101 = No operation<br>0011 = Memory word program operation<br>0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   | 1 = An improp<br>automatica | per program of ally on any set | or erase se<br>attempt of t           | equence attem<br>he WR bit) |                    | on has occurre         | ed (bit is se |

| bit 6       ERASE: Erase/Program Enable bit <sup>(1)</sup> 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         bit 5-4       Unimplemented: Read as '0'         bit 3-0       NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1:       1111 = No operation         1011 = Erase general segment       0011 = Kno operation         0010 = Memory page erase operation       0001 = Reserved         0000 = Reserved       If ERASE = 0:         1111 = No operation       1101 = No operation         0010 = Memory page erase operation       0011 = Reserved         0000 = Reserved       If ERASE = 0:         1111 = No operation       1001 = No operation         1001 = No operation       0010 = No operation         0011 = No operation       0011 = No operation         0010 = No operation       0011 = No operation         0011 = No operation       0011 = No operation         0011 = No operation       0011 = No operation         0111 = No operation       0011 = No operation         0011 = No operation       0011 = No operation         0011 = No operation       0011 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | hit 10 7          |                             |                                |                                       | ipieted normali             | у                  |                        |               |

| 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         bit 5-4       Unimplemented: Read as '0'         bit 3-0       NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1:       1111 = No operation         1011 = Erase general segment       0011 = No operation         0010 = Memory page erase operation       0001 = Reserved         0000 = Reserved       If ERASE = 0:         1111 = No operation       1101 = No operation         0101 = No operation       0001 = Reserved         0000 = Reserved       If ERASE = 0:         1111 = No operation       1001 = No operation         0011 = No operation       0011 = No operation         0010 = No operation       0011 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   | -                           |                                |                                       |                             |                    |                        |               |

| <ul> <li>0 = Performs the program operation specified by NVMOP&lt;3:0&gt; on the next WR command</li> <li>bit 5-4 Unimplemented: Read as '0'</li> <li>bit 3-0 NVMOP&lt;3:0&gt;: NVM Operation Select bits<sup>(1,2)</sup></li> <li>If ERASE = 1:<br/>1111 = No operation<br/>1101 = Erase general segment<br/>0011 = No operation<br/>0010 = Memory page erase operation<br/>0001 = Reserved<br/>0000 = Reserved</li> <li>If ERASE = 0:<br/>1111 = No operation<br/>1101 = No operation<br/>0011 = Memory word program operation<br/>0010 = No operation</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DILO              |                             | •                              |                                       |                             | <3:0> on the new   | vt WP comman           | d             |

| bit 5-4 Unimplemented: Read as '0'<br>bit 3-0 NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup><br>If ERASE = 1:<br>1111 = No operation<br>1101 = Erase general segment<br>0011 = No operation<br>0010 = Memory page erase operation<br>0001 = Reserved<br>0000 = Reserved<br>If ERASE = 0:<br>1111 = No operation<br>1101 = No operation<br>1101 = No operation<br>0011 = Memory word program operation<br>0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                   |                             |                                |                                       |                             |                    |                        |               |

| bit 3-0 NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1: 1111 = No operation 1101 = Erase general segment 0011 = No operation 0010 = Memory page erase operation 0001 = Reserved 0000 = Reserved If ERASE = 0: 1111 = No operation 1101 = No operation 1101 = No operation 0011 = Memory word program operation 0010 = No operation 0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 5-4           |                             |                                |                                       | ,                           |                    |                        |               |

| If ERASE = 1:         1111 = No operation         101 = Erase general segment         0011 = No operation         0010 = Memory page erase operation         0001 = Reserved         0000 = Reserved         If ERASE = 0:         1111 = No operation         1101 = No operation         0011 = Memory word program operation         0011 = Memory word program operation         0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bit 3-0           | -                           |                                |                                       | ts <sup>(1,2)</sup>         |                    |                        |               |

| <pre>1101 = Erase general segment<br/>0011 = No operation<br/>0010 = Memory page erase operation<br/>0001 = Reserved<br/>0000 = Reserved<br/><u>If ERASE = 0:</u><br/>1111 = No operation<br/>1101 = No operation<br/>0011 = Memory word program operation<br/>0010 = No operation</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |                             |                                |                                       |                             |                    |                        |               |

| 0011 = No operation         0010 = Memory page erase operation         0001 = Reserved         0000 = Reserved         If ERASE = 0:         1111 = No operation         1101 = No operation         0011 = Memory word program operation         0010 = No operation         0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   | •                           |                                |                                       |                             |                    |                        |               |

| 0010 = Memory page erase operation<br>0001 = Reserved<br>0000 = Reserved<br><u>If ERASE = 0:</u><br>1111 = No operation<br>1101 = No operation<br>0011 = Memory word program operation<br>0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |                             |                                | ent                                   |                             |                    |                        |               |

| 0001 = Reserved<br>0000 = Reserved<br><u>If ERASE = 0:</u><br>1111 = No operation<br>1101 = No operation<br>0011 = Memory word program operation<br>0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |                             |                                | oneration                             |                             |                    |                        |               |

| If ERASE = 0:<br>1111 = No operation<br>1101 = No operation<br>0011 = Memory word program operation<br>0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |                             |                                | peration                              |                             |                    |                        |               |

| <pre>1111 = No operation 1101 = No operation 0011 = Memory word program operation 0010 = No operation</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   | 0000 <b>= Reserv</b>        | red                            |                                       |                             |                    |                        |               |

| 1101 = No operation<br>0011 = Memory word program operation<br>0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   |                             | vration                        |                                       |                             |                    |                        |               |

| 0011 = Memory word program operation<br>0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |                             |                                |                                       |                             |                    |                        |               |