#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 6KB (2K x 24)                                                                    |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 256 x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 28-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs102a-e-ss |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

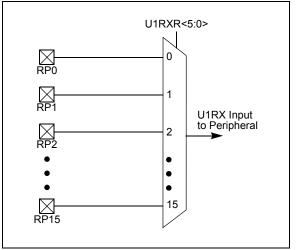

#### TABLE 4-24: PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33FJ06GS001

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11  | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|--------|--------|--------|--------|---------|--------|-------|-------|-------|-------|-------|-------|--------|--------|-------|-------|---------------|

| RPINR0   | 0680        | —      | —      |        |        | INT1R<5 | 5:0>   |       |       | —     | —     | —     | —     | —      | —      | _     | —     | 3F00          |

| RPINR1   | 0682        | _      | —      | _      | —      | _       |        | —     | _     | —     | _     |       |       | INT2R  | <5:0>  |       |       | 003F          |

| RPINR2   | 0684        | _      | —      |        |        | T1CKR<  | 5:0>   |       |       | —     | _     | _     | _     | —      | _      | _     | _     | 3F00          |

| RPINR3   | 0686        | _      | _      |        | —      | —       |        | —     | _     | _     |       |       |       | T2CKR  | <5:0>  |       |       | 003F          |

| RPINR29  | 06BA        | _      | _      |        |        | FLT1R<5 | 5:0>   | •     |       | _     |       | _     | _     | _      | _      | _     |       | 3F00          |

| RPINR30  | 06BC        | _      | _      |        |        | FLT3R<5 | 5:0>   |       |       | _     |       |       |       | FLT2R  | <5:0>  |       |       | 3F3F          |

| RPINR31  | 06BE        | _      | _      |        |        | FLT5R<5 | 5:0>   |       |       | _     |       |       |       | FLT4R  | <5:0>  |       |       | 3F3F          |

| RPINR32  | 06C0        | _      | _      |        |        | FLT7R<5 | 5:0>   |       |       | _     |       |       |       | FLT6R  | <5:0>  |       |       | 3F3F          |

| RPINR33  | 06C2        | _      | _      |        |        | SYNCI1R | <5:0>  |       |       | _     | _     |       |       | FLT8R  | <5:0>  |       |       | 3F3F          |

| RPINR34  | 06C4        | _      | _      | _      | —      | —       | _      | —     | _     | _     |       |       |       | SYNCI2 | R<5:0> |       |       | 003F          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-25: PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33FJ06GS101A AND dsPIC33FJ06GS102A

| SFR Name | SFR<br>Addr | Bit 15    | Bit 14   | Bit 13       | Bit 12      | Bit 11        | Bit 10      | Bit 9    | Bit 8      | Bit 7   | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|-----------|----------|--------------|-------------|---------------|-------------|----------|------------|---------|-------|-------|-------|--------|--------|-------|-------|---------------|

| RPINR0   | 0680        | —         | —        |              |             | INT1R<5       | 5:0>        |          |            | —       | —     | _     | —     | —      | —      | -     | —     | 3F00          |

| RPINR1   | 0682        | —         | —        | _            | _           | _             |             | —        | —          | _       | _     |       |       | INT2R  | <5:0>  |       |       | 003F          |

| RPINR2   | 0684        | _         | _        |              |             | T1CKR<        | 5:0>        |          |            | _       | _     |       | _     | _      | _      | _     | _     | 3F00          |

| RPINR3   | 0686        | _         | _        | _            | _           | _             |             | —        | _          | _       | _     |       |       | T2CKR  | <5:0>  |       | •     | 003F          |

| RPINR11  | 0696        | _         | _        | -            | _           | _             |             | _        | _          | _       | _     |       |       | OCFAF  | <5:0>  |       |       | 003F          |

| RPINR18  | 06A4        | _         | _        |              | •           | U1CTSR<       | <5:0>       | •        | •          |         | _     |       |       | U1RXF  | <5:0>  |       |       | 3F3F          |

| RPINR20  | 06A8        | _         | _        |              |             | SCK1R<        | 5:0>        |          |            |         | _     |       |       | SDI1R  | <5:0>  |       |       | 3F3F          |

| RPINR21  | 06AA        | _         | _        | _            | _           | _             |             | —        | _          | _       | _     |       |       | SS1R·  | <5:0>  |       |       | 003F          |

| RPINR29  | 06BA        | _         | _        |              | •           | FLT1R<        | 5:0>        | •        | •          | _       | _     | _     |       | _      | _      | _     |       | 3F00          |

| RPINR30  | 06BC        | —         | —        |              |             | FLT3R<        | 5:0>        |          |            | _       | _     |       |       | FLT2R  | <5:0>  |       |       | 3F3F          |

| RPINR31  | 06BE        | _         | _        |              |             | FLT5R<        | 5:0>        |          |            | _       | _     |       |       | FLT4R  | <5:0>  |       |       | 3F3F          |

| RPINR32  | 06C0        | _         | _        |              |             | FLT7R<        | 5:0>        |          |            | _       | _     |       |       | FLT6R  | <5:0>  |       |       | 3F3F          |

| RPINR33  | 06C2        | _         | _        |              |             | SYNCI1R       | <5:0>       |          |            |         | _     |       |       | FLT8R  | <5:0>  |       |       | 3F3F          |

| RPINR34  | 06C4        | _         | _        | _            | _           | _             |             | —        | —          | _       | _     |       |       | SYNCI2 | R<5:0> |       |       | 003F          |

| Legend:  | x = unkn    | own value | on Reset | , — = unimpl | emented, re | ad as '0'. Re | eset values | are show | n in hexad | ecimal. | •     |       |       |        |        |       |       | *             |

dsPIC33FJ06GS001/101A/102A/202A and dsPIC33FJ09GS302

#### **Flash Memory Control Registers** 5.5

| bit 15       Invariant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/SO-0            | R/W-0                       | R/W-0                          | U-0                                   | U-0                         | U-0                | U-0                    | U-0           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------|--------------------------------|---------------------------------------|-----------------------------|--------------------|------------------------|---------------|

| U-0       R/W-0       U-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         Image: Image                                                                                                                                                                                                                                                                                                        | WR <sup>(1)</sup> | WREN <sup>(1)</sup>         | WRERR <sup>(1)</sup>           | _                                     | —                           | _                  | —                      | _             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | bit 15            |                             | · · ·                          |                                       |                             |                    |                        | bit 8         |

| -         ERASE <sup>(1)</sup> -         NVMOP<3:0::         1.2           bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | U-0               | R/W-0                       | U-0                            | U-0                                   | R/W-0                       | R/W-0              | R/W-0                  | R/W-0         |

| bit 7       bit 7         Legend:       SO = Settable Only bit         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       WR: Write Control bit <sup>(1)</sup> 1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the b cleared by hardware once operation is complete. This bit can only be set (not cleared) in software once operation is complete and inactive         bit 14       WREN: Write Enable bit <sup>(1)</sup> 1 = Enables Flash program/erase operations         o = Inhibits Flash program/erase operations       o = Inhibits Flash program/erase operations         bit 13       WRERR: Write Sequence Error Flag bit <sup>(1)</sup> 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation sepecified by NVMOP<3:0> on the next WR command         bit 6       ERASE: Erase/Program Enable bit <sup>(1)</sup> 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         bit 5-4       Unimplemented: Read as '0'         bit 3-0       NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1:       1111 = No operation         1011 = No operation       0010 = Memory page erase operation         0011 = No oper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                 |                             | _                              | _                                     |                             | NVMOP              | <3:0> <sup>(1,2)</sup> | -             |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       WR: Write Control bit <sup>(1)</sup> 1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the bic cleared by hardware once operation is complete. This bit can only be set (not cleared) in software one operation is complete and inactive         bit 14       WREN: Write Enable bit <sup>(1)</sup> 1 = Enables Flash program/erase operations         0 = Inhibits Flash program/erase operations       0 = Inhibits Flash program/erase operations         bit 13       WRERR: Write Sequence Error Flag bit <sup>(1)</sup> 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation selectified by NVMOP<3:0> on the next WR command         0 = Performs the program operation Select bits <sup>(1,2)</sup> If ERASE = 1:         1111 = No operation         1010 = Erase general segment         0011 = Memory page erase operation         0011 = No operation         0011 = No operation         1011 = No operation         1011 = No operatio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | bit 7             |                             |                                |                                       |                             |                    |                        | bit           |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       WR: Write Control bit <sup>(1)</sup> 1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the bic cleared by hardware once operation is complete. This bit can only be set (not cleared) in software once operation is complete and inactive         bit 14       WREN: Write Enable bit <sup>(1)</sup> 1 = Enables Flash program/erase operations         0 = Inhibits Flash program/erase operations       0 = Inhibits Flash program/erase operations         bit 13       WRERR: Write Sequence Error Flag bit <sup>(1)</sup> 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         0 = Depration       1101 = Erase general segment         0101 = No operation       1101 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Legend:           |                             | SO = Settab                    | le Only bit                           |                             |                    |                        |               |

| bit 15 WR: Write Control bit <sup>(1)</sup><br>1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the b<br>cleared by hardware once operation is complete. This bit can only be set (not cleared) in softwa<br>0 = Program or erase operation is complete and inactive<br>bit 14 WREN: Write Enable bit <sup>(1)</sup><br>1 = Enables Flash program/erase operations<br>0 = Inhibits Flash program/erase operations<br>bit 13 WRERR: Write Sequence Error Flag bit <sup>(1)</sup><br>1 = An improper program or erase sequence attempt or termination has occurred (bit is<br>automatically on any set attempt of the WR bit)<br>0 = The program or erase operation completed normally<br>bit 6 ERASE: Erase/Program Enable bit <sup>(1)</sup><br>1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command<br>0 = Performs the program operation specified by NVMOP<3:0> on the next WR command<br>0 = Performs the program operation specified by NVMOP<3:0> on the next WR command<br>bit 5-4 Unimplemented: Read as 'o'<br>bit 3-0 NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup><br><u>If ERASE = 1:</u><br>1111 = No operation<br>1001 = Erase general segment<br>0010 = Reserved<br>0000 = Reserved<br><u>If ERASE = 0:</u><br>1111 = No operation<br>1001 = No operation                                                                                                                                                                                                                                                               | R = Readable      | e bit                       | W = Writable                   | e bit                                 | U = Unimple                 | mented bit, read   | l as '0'               |               |

| 1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the bicleared by hardware once operation is complete. This bit can only be set (not cleared) in software or erase operation is complete and inactive         0 = Program or erase operation is complete and inactive         bit 14       WREN: Write Enable bit <sup>(1)</sup> 1 = Enables Flash program/erase operations         0 = Inhibits Flash program/erase operations         0 = Inhibits Flash program/erase operations         bit 13       WRERR: Write Sequence Error Flag bit <sup>(1)</sup> 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation specified hy NVMOP<3:0> on the next WR command         0 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation Select bits <sup>(1,2)</sup> If ERASE = 1:         1111 = No operation         1101 = Erase general segment         011 = No operation         1101 = Reserved         0000 = Reserved         If ERASE = 0:         1111 = No operation         1101 = No operation         1101 = No operation         1111 = No operation         1101 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -n = Value at     | POR                         | '1' = Bit is se                | et                                    | '0' = Bit is cle            | eared              | x = Bit is unkr        | iown          |

| cleared by hardware once operation is complete. This bit can only be set (not cleared) in softwa<br>0 = Program or erase operation is complete and inactive<br>bit 14 WREN: Write Enable bit <sup>(1)</sup><br>1 = Enables Flash program/erase operations<br>0 = Inhibits Flash program/erase operations<br>bit 13 WRERR: Write Sequence Error Flag bit <sup>(1)</sup><br>1 = An improper program or erase sequence attempt or termination has occurred (bit is<br>automatically on any set attempt of the WR bit)<br>0 = The program or erase operation completed normally<br>bit 12-7 Unimplemented: Read as '0'<br>bit 6 ERASE: Erase/Program Enable bit <sup>(1)</sup><br>1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command<br>0 = Performs the program operation specified by NVMOP<3:0> on the next WR command<br>0 = Performs the program operation specified by NVMOP<3:0> on the next WR command<br>bit 5-4 Unimplemented: Read as '0'<br>bit 3-0 NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup><br>If ERASE = 1:<br>1111 = No operation<br>1010 = Erase general segment<br>0011 = No operation<br>0010 = Memory page erase operation<br>0010 = Reserved<br>0000 = Reserved<br>1111 = No operation<br>1011 | bit 15            |                             |                                |                                       | r orono oporati             | on The operation   | an is colf timed       | and the bit i |

| bit 14 WREN: Write Enable bit <sup>(1)</sup> 1 = Enables Flash program/erase operations 0 = Inhibits Flash program/erase operations bit 13 WRERR: Write Sequence Error Flag bit <sup>(1)</sup> 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit) 0 = The program or erase operation completed normally bit 12-7 Unimplemented: Read as '0' bit 6 ERASE: Erase/Program Enable bit <sup>(1)</sup> 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command 0 = Performs the program operation specified by NVMOP<3:0> on the next WR command 0 = Performs the program operation specified by NVMOP<3:0> on the next WR command 0 = Performs the program operation Select bits <sup>(1,2)</sup> bit 3-0 NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1: 1111 = No operation 1101 = Erase general segment 0011 = No operation 0010 = Memory page erase operation 0010 = Reserved 0000 = Reserved 0000 = Reserved 1111 = No operation 1011 = No operation 1011 = No operation 1011 = No operation 1011 = No operation 0010 = Memory word program operation 0011 = Memory word program operation 0010 = No operation 0011 = No operation 0010 = No operati                                                                                                                              |                   | cleared by                  | hardware onc                   | eoperation                            | is complete. Th             | is bit can only be |                        |               |

| 1 = Enables Flash program/erase operations         0 = Inhibits Flash program/erase operations         bit 13       WRERR: Write Sequence Error Flag bit <sup>(1)</sup> 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation completed normally         bit 12-7       Unimplemented: Read as '0'         bit 6       ERASE: Erase/Program Enable bit <sup>(1)</sup> 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         bit 5-4       Unimplemented: Read as '0'         bit 3-0       NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1:       1111 = No operation         1101 = Erase general segment       0011 = No operation         0010 = Memory page erase operation       0000 = Reserved         0000 = Reserved       If ERASE = 0:         1111 = No operation       1101 = No operation         1101 = No operation       0011 = No operation         1011 = No operation       10011 = No operation         1001 = No operation       0011 = No operation         1011 = No operation       1011 = No operation         1001 = No operation       0011 = Ne operation         0011 = Ne operatio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 14            | •                           |                                | · · · · · · · · · · · · · · · · · · · |                             |                    |                        |               |

| 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation completed normally         bit 12-7       Unimplemented: Read as '0'         bit 6       ERASE: Erase/Program Enable bit <sup>(1)</sup> 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         bit 5-4       Unimplemented: Read as '0'         bit 3-0       NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1:       1111 = No operation         101 = Erase general segment       0011 = No operation         0010 = Memory page erase operation       0010 = Reserved         If ERASE = 0:       1111 = No operation         1101 = No operation       1001 = Reserved         0000 = Reserved       If ERASE = 0:         1111 = No operation       1101 = No operation         0101 = No operation       0011 = Nemory word program operation         011 = No operation       0011 = Nemory word program operation         0011 = Nemory word program operation       0011 = Nemory word program operation         0010 = No operation       0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |                             |                                |                                       |                             |                    |                        |               |

| 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation completed normally         bit 12-7       Unimplemented: Read as '0'         bit 6       ERASE: Erase/Program Enable bit <sup>(1)</sup> 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         bit 5-4       Unimplemented: Read as '0'         bit 3-0       NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1:       1111 = No operation         101 = Erase general segment       0011 = Reserved         0010 = Memory page erase operation       0011 = Reserved         1111 = No operation       1101 = No operation         0010 = Reserved       If ERASE = 0:         11111 = No operation       1101 = No operation         0011 = Reserved       0000 = Reserved         1101 = No operation       1101 = No operation         1101 = No operation       1101 = No operation         1101 = No operation       1101 = No operation         0011 = Nemory word program operation       0011 = Memory word program operation         0011 = No operation       011 = No operation         0110 = No operation       011 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit 13            | WRERR: Write                | Sequence Er                    | ror Flag bit <sup>(</sup>             | 1)                          |                    |                        |               |

| bit 12-7 Unimplemented: Read as '0'<br>bit 6 ERASE: Erase/Program Enable bit <sup>(1)</sup><br>1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command<br>0 = Performs the program operation specified by NVMOP<3:0> on the next WR command<br>bit 5-4 Unimplemented: Read as '0'<br>bit 3-0 NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup><br>If ERASE = 1:<br>1111 = No operation<br>1101 = Erase general segment<br>0011 = No operation<br>0010 = Memory page erase operation<br>0010 = Reserved<br>0000 = Reserved<br>If ERASE = 0:<br>1111 = No operation<br>101 = No operation<br>101 = No operation<br>0011 = Memory word program operation<br>0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   | 1 = An improp<br>automatica | per program of ally on any set | or erase se<br>attempt of t           | equence attem<br>he WR bit) |                    | on has occurre         | ed (bit is se |

| bit 6       ERASE: Erase/Program Enable bit <sup>(1)</sup> 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         bit 5-4       Unimplemented: Read as '0'         bit 3-0       NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1:       1111 = No operation         1011 = Erase general segment       0011 = Kno operation         0010 = Memory page erase operation       0001 = Reserved         0000 = Reserved       If ERASE = 0:         1111 = No operation       1101 = No operation         0010 = Memory page erase operation       0011 = Reserved         0000 = Reserved       If ERASE = 0:         1111 = No operation       1001 = No operation         1001 = No operation       0010 = No operation         0011 = No operation       0011 = No operation         0010 = No operation       0011 = No operation         0011 = No operation       0011 = No operation         0011 = No operation       0011 = No operation         0111 = No operation       0011 = No operation         0011 = No operation       0011 = No operation         0011 = No operation       0011 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | hit 10 7          |                             |                                |                                       | ipieted normali             | у                  |                        |               |

| 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         bit 5-4       Unimplemented: Read as '0'         bit 3-0       NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1:       1111 = No operation         1011 = Erase general segment       0011 = No operation         0010 = Memory page erase operation       0001 = Reserved         0000 = Reserved       If ERASE = 0:         1111 = No operation       1101 = No operation         0101 = No operation       0001 = Reserved         0000 = Reserved       If ERASE = 0:         1111 = No operation       1001 = No operation         0011 = No operation       0011 = No operation         0010 = No operation       0011 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   | -                           |                                |                                       |                             |                    |                        |               |

| <ul> <li>0 = Performs the program operation specified by NVMOP&lt;3:0&gt; on the next WR command</li> <li>bit 5-4 Unimplemented: Read as '0'</li> <li>bit 3-0 NVMOP&lt;3:0&gt;: NVM Operation Select bits<sup>(1,2)</sup></li> <li>If ERASE = 1:<br/>1111 = No operation<br/>1101 = Erase general segment<br/>0011 = No operation<br/>0010 = Memory page erase operation<br/>0001 = Reserved<br/>0000 = Reserved</li> <li>If ERASE = 0:<br/>1111 = No operation<br/>1101 = No operation<br/>0011 = Memory word program operation<br/>0010 = No operation</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DILO              |                             | •                              |                                       |                             | <3:0> on the new   | vt WP comman           | d             |

| bit 5-4 Unimplemented: Read as '0'<br>bit 3-0 NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup><br>If ERASE = 1:<br>1111 = No operation<br>1101 = Erase general segment<br>0011 = No operation<br>0010 = Memory page erase operation<br>0001 = Reserved<br>0000 = Reserved<br>If ERASE = 0:<br>1111 = No operation<br>1101 = No operation<br>1101 = No operation<br>0011 = Memory word program operation<br>0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                   |                             |                                |                                       |                             |                    |                        |               |

| bit 3-0 NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1: 1111 = No operation 1101 = Erase general segment 0011 = No operation 0010 = Memory page erase operation 0001 = Reserved 0000 = Reserved If ERASE = 0: 1111 = No operation 1101 = No operation 1101 = No operation 0011 = Memory word program operation 0010 = No operation 0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 5-4           |                             |                                |                                       | ,                           |                    |                        |               |

| If ERASE = 1:         1111 = No operation         101 = Erase general segment         0011 = No operation         0010 = Memory page erase operation         0001 = Reserved         0000 = Reserved         If ERASE = 0:         1111 = No operation         1101 = No operation         0011 = Memory word program operation         0011 = Memory word program operation         0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bit 3-0           | -                           |                                |                                       | ts <sup>(1,2)</sup>         |                    |                        |               |

| <pre>1101 = Erase general segment<br/>0011 = No operation<br/>0010 = Memory page erase operation<br/>0001 = Reserved<br/>0000 = Reserved<br/><u>If ERASE = 0:</u><br/>1111 = No operation<br/>1101 = No operation<br/>0011 = Memory word program operation<br/>0010 = No operation</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |                             |                                |                                       |                             |                    |                        |               |

| 0011 = No operation         0010 = Memory page erase operation         0001 = Reserved         0000 = Reserved         If ERASE = 0:         1111 = No operation         1101 = No operation         0011 = Memory word program operation         0010 = No operation         0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   | •                           |                                |                                       |                             |                    |                        |               |

| 0010 = Memory page erase operation<br>0001 = Reserved<br>0000 = Reserved<br><u>If ERASE = 0:</u><br>1111 = No operation<br>1101 = No operation<br>0011 = Memory word program operation<br>0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |                             |                                | ent                                   |                             |                    |                        |               |

| 0001 = Reserved<br>0000 = Reserved<br><u>If ERASE = 0:</u><br>1111 = No operation<br>1101 = No operation<br>0011 = Memory word program operation<br>0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |                             |                                | oneration                             |                             |                    |                        |               |

| If ERASE = 0:<br>1111 = No operation<br>1101 = No operation<br>0011 = Memory word program operation<br>0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |                             |                                | peration                              |                             |                    |                        |               |

| <pre>1111 = No operation 1101 = No operation 0011 = Memory word program operation 0010 = No operation</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   | 0000 <b>= Reserv</b>        | red                            |                                       |                             |                    |                        |               |

| 1101 = No operation<br>0011 = Memory word program operation<br>0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   |                             | vration                        |                                       |                             |                    |                        |               |

| 0011 = Memory word program operation<br>0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |                             |                                |                                       |                             |                    |                        |               |