Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 6KB (2K x 24)                                                                    |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 256 x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

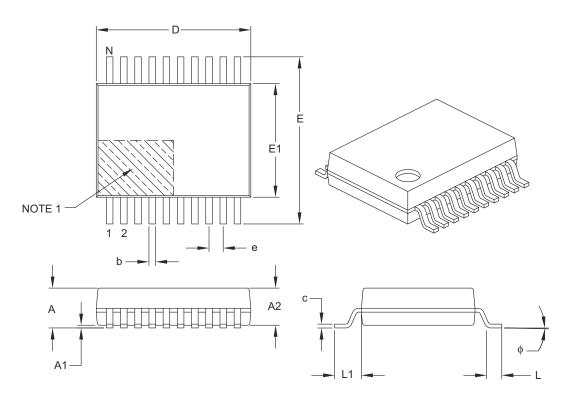

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 36-VFTLA Exposed Pad                                                             |

| Supplier Device Package    | 36-VTLA (5x5)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs102a-i-tl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

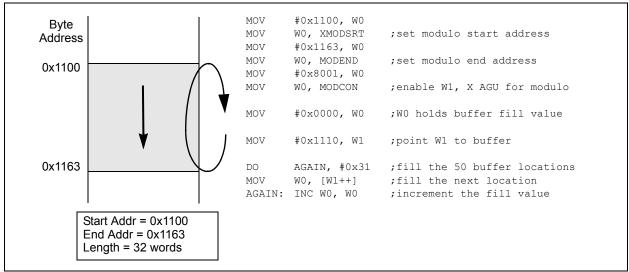

### 4.5 Modulo Addressing

Modulo Addressing mode is a method used to provide an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either data or program space (since the data pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into program space) and Y data spaces. Modulo Addressing can operate on any W register pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction as there are certain restrictions on the buffer start address (for incrementing buffers), or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

#### 4.5.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

| Note: | Υ   | space      | Modulo      | Addressing   | EA   |

|-------|-----|------------|-------------|--------------|------|

|       | cal | culations  | assume      | word-sized   | data |

|       | (LS | Sb of ever | y EA is alw | /ays clear). |      |

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

#### 4.5.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that will operate with Modulo Addressing:

- If XWM = 15, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 15, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X data space when XWM is set to any value other than '15' and the XMODEN bit is set at MODCON<15>.

The Y Address Space Pointer W register (YWM) to which Modulo Addressing is to be applied is stored in MODCON<7:4>. Modulo Addressing is enabled for Y data space when YWM is set to any value other than '15' and the YMODEN bit is set at MODCON<14>.

#### FIGURE 4-6: MODULO ADDRESSING OPERATION EXAMPLE

| REGISTER 7      | -3: INTCO                        | N1: INTERR                           |                  | ROL REGISTE                         | ER 1            |                 |       |

|-----------------|----------------------------------|--------------------------------------|------------------|-------------------------------------|-----------------|-----------------|-------|

| R/W-0           | R/W-0                            | R/W-0                                | R/W-0            | R/W-0                               | R/W-0           | R/W-0           | R/W-0 |

| NSTDIS          | OVAERR                           | OVBERR                               | COVAERR          | COVBERR                             | OVATE           | OVBTE           | COVTE |

| bit 15          |                                  |                                      |                  |                                     |                 |                 | bit   |

| R/W-0           | R/W-0                            | U-0                                  | R/W-0            | R/W-0                               | R/W-0           | R/W-0           | U-0   |

| SFTACERR        | DIV0ERR                          | _                                    | MATHERR          | ADDRERR                             | STKERR          | OSCFAIL         | _     |

| bit 7           |                                  |                                      | I                |                                     |                 |                 | bit   |

| Legend:         |                                  |                                      |                  |                                     |                 |                 |       |

| R = Readable    | bit                              | W = Writable                         | bit              | U = Unimplem                        | ented bit, read | 1 as '0'        |       |

| -n = Value at F | POR                              | '1' = Bit is set                     |                  | '0' = Bit is clea                   |                 | x = Bit is unkn | iown  |

|                 |                                  |                                      |                  |                                     |                 |                 |       |

| bit 15          | NSTDIS: Inte                     | rrupt Nesting E                      | isable bit       |                                     |                 |                 |       |

|                 |                                  | nesting is disat                     |                  |                                     |                 |                 |       |

| L:+ 4 4         |                                  | nesting is enab                      |                  | 1                                   |                 |                 |       |

| bit 14          |                                  | cumulator A O caused by ove          |                  | •                                   |                 |                 |       |

|                 |                                  | not caused by                        |                  |                                     |                 |                 |       |

| bit 13          | •                                | cumulator B O                        |                  |                                     |                 |                 |       |

|                 |                                  | caused by ove                        |                  | 0                                   |                 |                 |       |

|                 | 0 = Trap was                     | not caused by                        | overflow of A    | ccumulator B                        |                 |                 |       |

| bit 12          |                                  |                                      |                  | Overflow Trap F                     | •               |                 |       |

|                 |                                  |                                      |                  | flow of Accumu                      |                 |                 |       |

| bit 11          | COVBERR: A                       | Accumulator B                        | Catastrophic (   | Overflow Trap F                     | lag bit         |                 |       |

|                 |                                  |                                      |                  | flow of Accumu                      |                 |                 |       |

| bit 10          | -                                | umulator A Ove                       | -                |                                     |                 |                 |       |

|                 | 1 = Trap over<br>0 = Trap is dis | flow of Accum<br>sabled              | ulator A         |                                     |                 |                 |       |

| bit 9           | •                                | umulator B Ove                       | erflow Trap En   | able bit                            |                 |                 |       |

|                 |                                  | flow of Accum                        | -                |                                     |                 |                 |       |

| bit 8           | •                                | astrophic Overf                      | low Trap Enat    | ole bit                             |                 |                 |       |

|                 |                                  | atastrophic ove                      | •                | mulator A or B i                    | s enabled       |                 |       |

| bit 7           | •                                | Shift Accumula                       | ator Error Statu | us bit                              |                 |                 |       |

|                 |                                  |                                      |                  | alid accumulator<br>invalid accumul |                 |                 |       |

| bit 6           |                                  | vide-by-Zero E                       | -                |                                     |                 |                 |       |

|                 |                                  | or trap was cau                      | -                |                                     |                 |                 |       |

|                 |                                  | or trap was not                      | •                | ivide-by-zero                       |                 |                 |       |

| bit 5           | Unimplemen                       | ted: Read as '                       | 0'               |                                     |                 |                 |       |

| bit 4           |                                  | Math Error Trap                      |                  |                                     |                 |                 |       |

|                 |                                  | or trap has occu                     |                  |                                     |                 |                 |       |

| hit 2           |                                  | or trap has not (                    |                  |                                     |                 |                 |       |

| bit 3           |                                  | Address Error T                      | -                |                                     |                 |                 |       |

|                 |                                  | error trap has c<br>error trap has r |                  |                                     |                 |                 |       |

#### INTCOMA, INTERDURT CONTROL DECISTER A

| <b>REGISTER 7</b> | -4: INTCO                                       | N2: INTERR                                                                                         |                       | ROL REGIST       | ER 2             |                 |        |

|-------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------|------------------|------------------|-----------------|--------|

| R/W-0             | R-0                                             | U-0                                                                                                | U-0                   | U-0              | U-0              | U-0             | U-0    |

| ALTIVT            | DISI                                            | —                                                                                                  | _                     |                  | —                |                 | —      |

| bit 15            |                                                 |                                                                                                    |                       |                  |                  |                 | bit 8  |

| U-0               | U-0                                             | U-0                                                                                                | U-0                   | U-0              | R/W-0            | R/W-0           | R/W-0  |

|                   |                                                 |                                                                                                    | _                     |                  | INT2EP           | INT1EP          | INT0EP |

| bit 7             |                                                 |                                                                                                    |                       |                  |                  |                 | bit 0  |

|                   |                                                 |                                                                                                    |                       |                  |                  |                 |        |

| Legend:           |                                                 |                                                                                                    |                       |                  |                  |                 |        |

| R = Readable      | bit                                             | W = Writable                                                                                       | bit                   | U = Unimpler     | mented bit, read | as '0'          |        |

| -n = Value at F   | POR                                             | '1' = Bit is set                                                                                   |                       | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| bit 14            | 0 = Uses stan<br>DISI: DISI In<br>1 = DISI inst | rnate vector tab<br>idard (default) v<br>struction Status<br>ruction is active<br>ruction is not a | vector table<br>s bit |                  |                  |                 |        |

| bit 13-3          | Unimplemen                                      | ted: Read as '                                                                                     | )'                    |                  |                  |                 |        |

| bit 2             | 1 = Interrupt o                                 | rnal Interrupt 2<br>on negative edg<br>on positive edg                                             | je                    | Polarity Selec   | t bit            |                 |        |

| bit 1             | 1 = Interrupt o                                 | rnal Interrupt 1<br>on negative edg<br>on positive edg                                             | ge                    | Polarity Selec   | t bit            |                 |        |

| bit 0             | 1 = Interrupt o                                 | ernal Interrupt 0<br>on negative edg<br>on positive edge                                           | ge                    | Polarity Selec   | t bit            |                 |        |

| REGISTER     | 7-13: IEC1:     | INTERRUPT                           | ENABLE CO      | ONTROL RE               | GISTER 1             |                 |         |

|--------------|-----------------|-------------------------------------|----------------|-------------------------|----------------------|-----------------|---------|

| U-0          | U-0             | R/W-0                               | U-0            | U-0                     | U-0                  | U-0             | U-0     |

| _            |                 | INT2IE                              | —              | _                       | _                    | _               |         |

| bit 15       |                 |                                     |                |                         | •                    |                 | bit 8   |

|              |                 |                                     |                |                         |                      |                 |         |

| U-0          | U-0             | U-0                                 | R/W-0          | R/W-0                   | R/W-0                | R/W-0           | R/W-0   |

| —            | _               | —                                   | INT1IE         | CNIE                    | AC1IE <sup>(1)</sup> | MI2C1IE         | SI2C1IE |

| bit 7        |                 |                                     |                |                         |                      |                 | bit 0   |

|              |                 |                                     |                |                         |                      |                 |         |

| Legend:      |                 |                                     |                |                         |                      |                 |         |

| R = Readab   | le bit          | W = Writable                        | bit            | U = Unimpler            | mented bit, read     | d as '0'        |         |

| -n = Value a | t POR           | '1' = Bit is set                    |                | '0' = Bit is cle        | eared                | x = Bit is unkr | nown    |

|              |                 |                                     |                |                         |                      |                 |         |

| bit 15-14    | -               | ted: Read as '                      |                |                         |                      |                 |         |

| bit 13       |                 | rnal Interrupt 2                    |                |                         |                      |                 |         |

|              |                 | request is enab<br>request is not e |                |                         |                      |                 |         |

| bit 12-5     |                 | ited: Read as '                     |                |                         |                      |                 |         |

| bit 4        | -               | rnal Interrupt 1                    |                |                         |                      |                 |         |

| Dil 4        |                 | request is enab                     |                |                         |                      |                 |         |

|              |                 | request is not e                    |                |                         |                      |                 |         |

| bit 3        | CNIE: Input C   | Change Notifica                     | tion Interrupt | Enable bit              |                      |                 |         |

|              |                 | request is enab                     |                |                         |                      |                 |         |

|              | •               | request is not e                    |                |                         |                      |                 |         |

| bit 2        |                 | og Comparator                       |                | able bit <sup>(1)</sup> |                      |                 |         |

|              |                 | request is enab                     |                |                         |                      |                 |         |

| bit 1        | •               | request is not e<br>21 Master Even  |                | aabla bit               |                      |                 |         |

|              |                 | request is enab                     | -              |                         |                      |                 |         |

|              |                 | request is enab                     |                |                         |                      |                 |         |

| bit 0        | •               | 1 Slave Events                      |                | able bit                |                      |                 |         |

|              |                 | request is enab                     | •              |                         |                      |                 |         |

|              | 0 = Interrupt r | request is not e                    | nabled         |                         |                      |                 |         |

|              |                 |                                     |                |                         |                      |                 |         |

### **Note 1:** This bit is not implemented in dsPIC33FJ06GS101A/102A devices.

| <b>REGISTER 7</b>     | -16: IEC5:      | INTERRUPT                           | ENABLE CO                              | ONTROL RE            | GISTER 5 |                    |        |

|-----------------------|-----------------|-------------------------------------|----------------------------------------|----------------------|----------|--------------------|--------|

| R/W-0                 | R/W-0           | U-0                                 | U-0                                    | U-0                  | U-0      | U-0                | U-0    |

| PWM2IE <sup>(1)</sup> | PWM1IE          | —                                   | _                                      | —                    | —        | —                  | —      |

| bit 15                |                 |                                     |                                        |                      |          |                    | bit 8  |

|                       |                 |                                     |                                        |                      |          |                    |        |

| U-0                   | U-0             | U-0                                 | U-0                                    | U-0                  | U-0      | U-0                | R/W-0  |

|                       |                 |                                     | —                                      |                      |          | —                  | JTAGIE |

| bit 7                 |                 |                                     |                                        |                      |          |                    | bit 0  |

|                       |                 |                                     |                                        |                      |          |                    |        |

| Legend:               |                 |                                     |                                        |                      |          |                    |        |

| R = Readable          | bit             | W = Writable                        | bit U = Unimplemented bit, read as '0' |                      |          |                    |        |

| -n = Value at F       | POR             | '1' = Bit is set                    |                                        | '0' = Bit is cleared |          | x = Bit is unknown |        |

|                       |                 |                                     | (4)                                    |                      |          |                    |        |

| bit 15                |                 | /M2 Interrupt E                     |                                        |                      |          |                    |        |

|                       |                 | request is enab<br>request is not e |                                        |                      |          |                    |        |

| bit 14                | •               | /M1 Interrupt E                     |                                        |                      |          |                    |        |

| bit 14                |                 | request is enab                     |                                        |                      |          |                    |        |

|                       | •               | request is not e                    |                                        |                      |          |                    |        |

| bit 13-1              | Unimplemen      | ted: Read as '                      | כי                                     |                      |          |                    |        |

| bit 0                 | JTAGIE: JTA     | G Interrupt Ena                     | ble bit                                |                      |          |                    |        |

|                       | 1 = Interrupt i | request is enab                     | led                                    |                      |          |                    |        |

|                       | 0 = Interrupt i | request is not e                    | nabled                                 |                      |          |                    |        |

|                       |                 |                                     |                                        |                      |          |                    |        |

### REGISTER 7-16: IEC5: INTERRUPT ENABLE CONTROL REGISTER 5

**Note 1:** This bit is not implemented in dsPIC33FJ06GS001/101A devices.

| U-0          | R/W-1        | R/W-0                                   | R/W-0          | U-0               | R/W-1                    | R/W-0                     | R/W-0 |

|--------------|--------------|-----------------------------------------|----------------|-------------------|--------------------------|---------------------------|-------|

| _            |              | T1IP<2:0>                               |                | —                 |                          | OC1IP<2:0> <sup>(1)</sup> |       |

| pit 15       |              |                                         |                |                   |                          |                           | bit   |

|              |              |                                         |                |                   |                          |                           |       |

| U-0          | R/W-1        | R/W-0                                   | R/W-0          | U-0               | R/W-1                    | R/W-0                     | R/W-0 |

| —            |              | IC1IP<2:0> <sup>(2)</sup>               |                | —                 |                          | INT0IP<2:0>               |       |

| oit 7        |              |                                         |                |                   |                          |                           | bit   |

| Legend:      |              |                                         |                |                   |                          |                           |       |

| R = Readabl  | e bit        | W = Writable b                          | bit            | U = Unimple       | mented bit, re           | ad as '0'                 |       |

| n = Value at | POR          | '1' = Bit is set                        |                | '0' = Bit is cl   | eared                    | x = Bit is unkn           | own   |

|              |              |                                         |                |                   |                          |                           |       |

| bit 15       | -            | ented: Read as '0                       |                |                   |                          |                           |       |

| bit 14-12    |              | Timer1 Interrupt                        | -              |                   |                          |                           |       |

|              | 111 = Interr | upt is Priority 7 (h                    | lignest prior  | ity interrupt)    |                          |                           |       |

|              | •            |                                         |                |                   |                          |                           |       |

|              | •            |                                         |                |                   |                          |                           |       |

|              |              | upt is Priority 1<br>upt source is disa | abled          |                   |                          |                           |       |

| bit 11       | Unimpleme    | ented: Read as '0                       | ,              |                   |                          |                           |       |

| bit 10-8     | OC1IP<2:0    | >: Output Compa                         | re Channel     | 1 Interrupt Prio  | rity bits <sup>(1)</sup> |                           |       |

|              | 111 = Interr | upt is Priority 7 (ł                    | nighest prior  | ity interrupt)    |                          |                           |       |

|              | •            |                                         |                |                   |                          |                           |       |

|              | •            |                                         |                |                   |                          |                           |       |

|              | 001 = Interr | upt is Priority 1                       |                |                   |                          |                           |       |

|              |              | upt source is disa                      | abled          |                   |                          |                           |       |

| bit 7        | Unimpleme    | ented: Read as '0                       | ,              |                   |                          |                           |       |

| bit 6-4      | IC1IP<2:0>   | : Input Capture C                       | hannel 1 Int   | errupt Priority I | oits <sup>(2)</sup>      |                           |       |

|              |              | upt is Priority 7 (I                    |                |                   |                          |                           |       |

|              | •            |                                         |                |                   |                          |                           |       |

|              | •            |                                         |                |                   |                          |                           |       |

|              | 001 = Interr | upt is Priority 1                       |                |                   |                          |                           |       |

|              |              | upt source is disa                      | abled          |                   |                          |                           |       |

| bit 3        | Unimpleme    | nted: Read as '0                        | ,              |                   |                          |                           |       |

| bit 2-0      | INT0IP<2:0   | >: External Interr                      | upt 0 Priority | v bits            |                          |                           |       |

|              |              | upt is Priority 7 (I                    |                |                   |                          |                           |       |

|              | •            |                                         |                |                   |                          |                           |       |

|              | •            |                                         |                |                   |                          |                           |       |

|              | •            |                                         |                |                   |                          |                           |       |

|              | 001 = Interr | upt is Priority 1                       |                |                   |                          |                           |       |

#### **Note 1:** These bits are not implemented in the dsPIC33FJ06GS001 device.

2: These bits are not implemented in dsPIC33FJ06GS001/101A/102A devices.

| REGISTER 8      | -5: ACLK                                                                                                                             | CON: AUXILI                                                           | ARY CLOCI      |                             | ONTROL RE        |                 |       |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------|-----------------------------|------------------|-----------------|-------|

| R/W-0           | R-0                                                                                                                                  | R/W-1                                                                 | U-0            | U-0                         | R/W-1            | R/W-1           | R/W-1 |

| ENAPLL          | APLLCK                                                                                                                               | SELACLK                                                               |                | —                           | AF               | PSTSCLR<2:0>    | (2)   |

| bit 15          |                                                                                                                                      |                                                                       |                |                             |                  |                 | bit 8 |

|                 |                                                                                                                                      |                                                                       |                |                             |                  |                 |       |

| R/W-0           | R/W-0                                                                                                                                | U-0                                                                   | U-0            | U-0                         | U-0              | U-0             | U-0   |

| ASRCSEL         | FRCSEL                                                                                                                               |                                                                       | —              | —                           |                  |                 | —     |

| bit 7           |                                                                                                                                      |                                                                       |                |                             |                  |                 | bit 0 |

| Legend:         |                                                                                                                                      |                                                                       |                |                             |                  |                 |       |

| R = Readable    | bit                                                                                                                                  | W = Writable I                                                        | hit            | U = Unimpler                | mented bit, read | 1 as '0'        |       |

| -n = Value at F |                                                                                                                                      | '1' = Bit is set                                                      |                | '0' = Bit is cle            |                  | x = Bit is unkr | nown  |

|                 |                                                                                                                                      |                                                                       |                |                             |                  |                 |       |

| bit 15          | ENAPLL: Aux                                                                                                                          | xiliary PLL Enal                                                      | ble bit        |                             |                  |                 |       |

|                 | 1 = APLL is e                                                                                                                        | nabled                                                                |                |                             |                  |                 |       |

|                 | 0 = APLL is d                                                                                                                        | lisabled                                                              |                |                             |                  |                 |       |

| bit 14          | APLLCK: AP                                                                                                                           | LL Locked Stat                                                        | us bit (read-o | nly)                        |                  |                 |       |

|                 |                                                                                                                                      | that auxiliary P that auxiliary P                                     |                | ck                          |                  |                 |       |

| bit 13          | SELACLK: S                                                                                                                           | elect Auxiliary                                                       | Clock Source   | for Auxiliary C             | lock Divider bit |                 |       |

|                 |                                                                                                                                      | oscillators provi<br>PLL (Fvco) prov                                  |                |                             |                  |                 |       |

| bit 12-11       | -                                                                                                                                    | ted: Read as '                                                        |                |                             |                  |                 |       |

| bit 10-8        | -                                                                                                                                    | 2:0>: Auxiliary                                                       |                | Divider bits <sup>(2)</sup> |                  |                 |       |

|                 | 111 = Divideo<br>110 = Divideo<br>101 = Divideo<br>100 = Divideo<br>011 = Divideo<br>010 = Divideo<br>001 = Divideo<br>001 = Divideo | d by 1<br>d by 2<br>d by 4<br>d by 8<br>d by 16<br>d by 32<br>d by 64 |                |                             |                  |                 |       |

| bit 7           | ASRCSEL: S                                                                                                                           | elect Reference                                                       | e Clock Sourc  | e for Auxiliary             | Clock bit        |                 |       |

|                 | •                                                                                                                                    | scillator is the o                                                    |                |                             |                  |                 |       |

| bit 6           | FRCSEL: Sel                                                                                                                          | lect Reference                                                        | Clock Source   | for Auxiliary P             | LL bit           |                 |       |

|                 | 1 = Selects F                                                                                                                        | RC clock for au<br>k source is dete                                   | ixiliary PLL   | -                           |                  |                 |       |

|                 | Unimplemen                                                                                                                           |                                                                       |                |                             | B                |                 |       |

#### (1) \_

2: The auxiliary clock postscaler must be configured to divide-by-1 (APSTSCLR<2:0> = 111) for proper operation of the PWM module.

| <b>REGISTER 8-7:</b> | LFSR  | : LINEAR FEED    | BACK S | HIFT REGISTI                       | ER    |                 |       |

|----------------------|-------|------------------|--------|------------------------------------|-------|-----------------|-------|

| U-0                  | R/W-0 | R/W-0            | R/W-0  | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |

| —                    |       |                  |        | LFSR<14:8>                         |       |                 |       |

| bit 15               |       |                  |        |                                    |       |                 | bit 8 |

|                      |       |                  |        |                                    |       |                 |       |

| R/W-0                | R/W-0 | R/W-0            | R/W-0  | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |

|                      |       |                  | LFS    | R<7:0>                             |       |                 |       |

| bit 7                |       |                  |        |                                    |       |                 | bit 0 |

|                      |       |                  |        |                                    |       |                 |       |

| Legend:              |       |                  |        |                                    |       |                 |       |

| R = Readable bit     |       | W = Writable bit |        | U = Unimplemented bit, read as '0' |       |                 |       |

| -n = Value at PO     | २     | '1' = Bit is set |        | '0' = Bit is clea                  | ared  | x = Bit is unkr | nown  |

|                      |       |                  |        |                                    |       |                 |       |

bit 15 Unimplemented: Read as '0'

bit 14-0 LFSR<14:0>: Pseudo Random FRC Trim Value bits

| Input Name                                              | Function Name | Register | Configuration<br>Bits |

|---------------------------------------------------------|---------------|----------|-----------------------|

| External Interrupt 1                                    | INT1          | RPINR0   | INT1R<5:0>            |

| External Interrupt 2                                    | INT2          | RPINR1   | INT2R<5:0>            |

| Timer1 External Clock                                   | T1CK          | RPINR2   | T1CKR<5:0>            |

| Timer2 External Clock                                   | T2CK          | RPINR3   | T2CKR<5:0>            |

| Input Capture 1                                         | IC1           | RPINR7   | IC1R<5:0>             |

| Output Compare Fault A                                  | OCFA          | RPINR11  | OCFAR<5:0>            |

| UART1 Receive                                           | U1RX          | RPINR18  | U1RXR<5:0>            |

| UART1 Clear-to-Send                                     | U1CTS         | RPINR18  | U1CTSR<5:0>           |

| SPI Data Input 1                                        | SDI1          | RPINR20  | SDI1R<5:0>            |

| SPI Clock Input 1                                       | SCK1          | RPINR20  | SCK1R<5:0>            |

| SPI Slave Select Input 1                                | SS1           | RPINR21  | SS1R<5:0>             |

| PWM Fault Input                                         | FLT1          | RPINR29  | FLT1R<5:0>            |

| PWM Fault Input                                         | FLT2          | RPINR30  | FLT2R<5:0>            |

| PWM Fault Input                                         | FLT3          | RPINR30  | FLT3R<5:0>            |

| PWM Fault Input                                         | FLT4          | RPINR31  | FLT4R<5:0>            |

| PWM Fault Input                                         | FLT5          | RPINR31  | FLT5R<5:0>            |

| PWM Fault Input                                         | FLT6          | RPINR32  | FLT6R<5:0>            |

| PWM Fault Input                                         | FLT7          | RPINR32  | FLT7R<5:0>            |

| PWM Fault Input                                         | FLT8          | RPINR33  | FLT8R<5:0>            |

| External Synchronization Signal to PWM Master Time Base | SYNCI1        | RPINR33  | SYNCI1R<5:0>          |

| External Synchronization Signal to PWM Master Time Base | SYNCI2        | RPINR34  | SYNCI2R<5:0>          |

#### TABLE 10-1: SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTION)

| U-0          | U-0     | R/W-1            | R/W-1      | R/W-1                | R/W-1           | R/W-1              | R/W-1 |

|--------------|---------|------------------|------------|----------------------|-----------------|--------------------|-------|

| _            | —       |                  | FLT1R<5:0> |                      |                 |                    |       |

| bit 15       |         |                  |            |                      |                 |                    | bit 8 |

|              |         |                  |            |                      |                 |                    |       |

| U-0          | U-0     | U-0              | U-0        | U-0                  | U-0             | U-0                | U-0   |

| —            | _       | —                | _          | —                    |                 | —                  | —     |

| bit 7        |         |                  |            |                      |                 |                    | bit 0 |

| Legend:      |         |                  |            |                      |                 |                    |       |

| R = Readab   | ole bit | W = Writable     | bit        | U = Unimpler         | nented bit, rea | d as '0'           |       |

| -n = Value a | at POR  | '1' = Bit is set |            | '0' = Bit is cleared |                 | x = Bit is unknown |       |

#### REGISTER 10-10: RPINR29: PERIPHERAL PIN SELECT INPUT REGISTER 29

bit 15-14 Unimplemented: Read as '0'

bit 13-8

8 FLT1R<5:0>: Assign PWM Fault Input 1 (FLT1) to the Corresponding RPn Pin bits

111111 = Input tied to Vss 100011 = Input tied to RP35 100010 = Input tied to RP34 100001 = Input tied to RP33 100000 = Input tied to RP32 • • •

bit 7-0 Unimplemented: Read as '0'

| U-0                | U-0                                                                                                                       | R/W-1                                                                                                                                                                      | R/W-1                              | R/W-1                       | R/W-1            | R/W-1           | R/W-1 |

|--------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------------|------------------|-----------------|-------|

| _                  | —                                                                                                                         |                                                                                                                                                                            |                                    | FLT7                        | R<5:0>           |                 |       |

| bit 15             |                                                                                                                           |                                                                                                                                                                            |                                    |                             |                  |                 | bit 8 |

|                    |                                                                                                                           |                                                                                                                                                                            |                                    |                             |                  |                 |       |

| U-0                | U-0                                                                                                                       | R/W-1                                                                                                                                                                      | R/W-1                              | R/W-1                       | R/W-1            | R/W-1           | R/W-1 |

| _                  | —                                                                                                                         |                                                                                                                                                                            |                                    | FLT6                        | R<5:0>           |                 |       |

| bit 7              |                                                                                                                           |                                                                                                                                                                            |                                    |                             |                  |                 | bit ( |

| Legend:            |                                                                                                                           |                                                                                                                                                                            |                                    |                             |                  |                 |       |

| R = Readab         | le bit                                                                                                                    | W = Writable I                                                                                                                                                             | oit                                | U = Unimplen                | nented bit, read | d as '0'        |       |

| -n = Value a       | t POR                                                                                                                     | '1' = Bit is set                                                                                                                                                           |                                    | '0' = Bit is clea           |                  | x = Bit is unkr | nown  |

|                    |                                                                                                                           |                                                                                                                                                                            |                                    |                             |                  |                 |       |

| bit 15-14          | Unimpleme                                                                                                                 | nted: Read as '(                                                                                                                                                           | )'                                 |                             |                  |                 |       |

| bit 13-8           | •                                                                                                                         | : Assign PWM F                                                                                                                                                             |                                    | =I T7) to the Co            | orresponding R   | Pn Pin hits     |       |

|                    |                                                                                                                           | put tied to Vss                                                                                                                                                            |                                    |                             | incoponding is   |                 |       |

|                    |                                                                                                                           | put tied to RP35                                                                                                                                                           |                                    |                             |                  |                 |       |

|                    |                                                                                                                           |                                                                                                                                                                            |                                    |                             |                  |                 |       |

|                    | 100010 <b>= ln</b>                                                                                                        | put tied to RP34                                                                                                                                                           |                                    |                             |                  |                 |       |

|                    |                                                                                                                           | put tied to RP34<br>put tied to RP33                                                                                                                                       |                                    |                             |                  |                 |       |

|                    | 100001 <b>= In</b>                                                                                                        |                                                                                                                                                                            | 1                                  |                             |                  |                 |       |

|                    | 100001 <b>= In</b>                                                                                                        | put tied to RP33                                                                                                                                                           | 1                                  |                             |                  |                 |       |

|                    | 100001 <b>= In</b>                                                                                                        | put tied to RP33                                                                                                                                                           | 1                                  |                             |                  |                 |       |

|                    | 100001 <b>= In</b>                                                                                                        | put tied to RP33                                                                                                                                                           | 1                                  |                             |                  |                 |       |

|                    | 100001 = In<br>100000 = In<br>•                                                                                           | put tied to RP33<br>put tied to RP32                                                                                                                                       | 1                                  |                             |                  |                 |       |

| bit 7-6            | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>00000 = Inp                                                                  | put tied to RP33<br>put tied to RP32<br>ut tied to RP0                                                                                                                     |                                    |                             |                  |                 |       |

| bit 7-6            | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | put tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0                                                                                                 | ;<br>;<br>;                        | ELT6) to the Co             | prresponding P   | PDn Din hits    |       |

| bit 7-6<br>bit 5-0 | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | put tied to RP33<br>put tied to RP32<br>ut tied to RP0<br><b>nted:</b> Read as '0<br>:: Assign PWM F                                                                       | ;<br>;<br>;                        | FLT6) to the Co             | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | put tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss                                                            | <sub>)</sub> ,<br>Fault Input 6 (I | FLT6) to the Co             | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | put tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35                                        | ) <sup>)</sup><br>Fault Input 6 (I | FLT6) to the Co             | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34                     | ) <sup>)</sup><br>Fault Input 6 (I | <sup>-</sup> LT6) to the Co | orresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33 | o'<br>Fault Input 6 (I             | <sup>-</sup> LT6) to the Co | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34                     | o'<br>Fault Input 6 (I             | <sup>-</sup> LT6) to the Co | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33 | o'<br>Fault Input 6 (I             | <sup>-</sup> LT6) to the Co | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33 | o'<br>Fault Input 6 (I             | FLT6) to the Co             | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33 | o'<br>Fault Input 6 (I             | <sup>=</sup> LT6) to the Co | prresponding R   | Pn Pin bits     |       |

### REGISTER 10-13: RPINR32: PERIPHERAL PIN SELECT INPUT REGISTER 32

| U-0                | U-0                                                                                                                                      | R/W-1                                                                                                                                                                                                                  | R/W-1                                              | R/W-1                       | R/W-1            | R/W-1             | R/W-1   |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----------------------------|------------------|-------------------|---------|

| _                  | —                                                                                                                                        |                                                                                                                                                                                                                        |                                                    | SYNCI                       | 1R<5:0>          |                   |         |

| bit 15             |                                                                                                                                          |                                                                                                                                                                                                                        |                                                    |                             |                  |                   | bit     |

| U-0                | U-0                                                                                                                                      | R/W-1                                                                                                                                                                                                                  | R/W-1                                              | R/W-1                       | R/W-1            | R/W-1             | R/W-1   |

| 0-0                | 0-0                                                                                                                                      | 10/00-1                                                                                                                                                                                                                | 10/00-1                                            |                             | R<5:0>           | 10/00-1           | 10.00-1 |

| <br>bit 7          |                                                                                                                                          |                                                                                                                                                                                                                        |                                                    | FLIO                        | N=0.02           |                   | bit     |

|                    |                                                                                                                                          |                                                                                                                                                                                                                        |                                                    |                             |                  |                   | Dit     |

| Legend:            |                                                                                                                                          |                                                                                                                                                                                                                        |                                                    |                             |                  |                   |         |

| R = Readab         | le bit                                                                                                                                   | W = Writable                                                                                                                                                                                                           | bit                                                | U = Unimpler                | nented bit, read | d as '0'          |         |

| -n = Value a       | t POR                                                                                                                                    | '1' = Bit is set                                                                                                                                                                                                       |                                                    | '0' = Bit is cle            | ared             | x = Bit is unkr   | nown    |

|                    |                                                                                                                                          |                                                                                                                                                                                                                        |                                                    |                             |                  |                   |         |

| bit 15-14          | Unimpleme                                                                                                                                | nted: Read as '                                                                                                                                                                                                        | 0'                                                 |                             |                  |                   |         |

| bit 13-8           | SYNCI1R<5                                                                                                                                | :0>: Assign PW                                                                                                                                                                                                         | M Master Time                                      | e Base Externa              | al Synchronizat  | tion Signal to th | e       |

|                    |                                                                                                                                          |                                                                                                                                                                                                                        |                                                    |                             |                  |                   |         |

|                    | Correspondi                                                                                                                              | ng RPn Pin bits                                                                                                                                                                                                        |                                                    |                             |                  |                   |         |

|                    | 111111 <b>= In</b>                                                                                                                       | put tied to Vss                                                                                                                                                                                                        |                                                    |                             |                  |                   |         |

|                    | 111111 = ln<br>100011 = ln                                                                                                               | put tied to Vss                                                                                                                                                                                                        |                                                    |                             |                  |                   |         |

|                    | 111111 = In<br>100011 = In<br>100010 = In                                                                                                | put tied to Vss<br>put tied to RP35<br>put tied to RP34                                                                                                                                                                | 1                                                  |                             |                  |                   |         |

|                    | 111111 = In<br>100011 = In<br>100010 = In<br>100001 = In                                                                                 | put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33                                                                                                                                            | 4<br>3                                             |                             |                  |                   |         |

|                    | 111111 = In<br>100011 = In<br>100010 = In<br>100001 = In                                                                                 | put tied to Vss<br>put tied to RP35<br>put tied to RP34                                                                                                                                                                | 4<br>3                                             |                             |                  |                   |         |

|                    | 111111 = In<br>100011 = In<br>100010 = In<br>100001 = In                                                                                 | put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33                                                                                                                                            | 4<br>3                                             |                             |                  |                   |         |