Welcome to E-XFL.COM

Microchip Technology - DSPIC33FJ06GS102AT-E/TL Datasheet

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 6KB (2K x 24)                                                                     |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 256 x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 6x10b                                                                         |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 36-VFTLA Exposed Pad                                                              |

| Supplier Device Package    | 36-VTLA (5x5)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs102at-e-tl |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| REGISTER 7-     | -12: IEC0:      | INTERRUPT                           | ENABLE CO                    | ONTROL REC                   | GISTER 0              |                        |        |

|-----------------|-----------------|-------------------------------------|------------------------------|------------------------------|-----------------------|------------------------|--------|

| U-0             | U-0             | R/W-0                               | R/W-0                        | R/W-0                        | R/W-0                 | R/W-0                  | U-0    |

| —               | _               | ADIE                                | U1TXIE <sup>(1)</sup>        | U1RXIE <sup>(1)</sup>        | SPI1IE <sup>(1)</sup> | SPI1EIE <sup>(1)</sup> |        |

| bit 15          |                 |                                     |                              |                              |                       |                        | bit 8  |

| R/W-0           | U-0             | U-0                                 | U-0                          | R/W-0                        | R/W-0                 | R/W-0                  | R/W-0  |

| T2IE            | _               | _                                   |                              | T1IE                         | OC1IE <sup>(1)</sup>  | IC1IE <sup>(2)</sup>   | INTOIE |

| bit 7           |                 |                                     |                              |                              |                       |                        | bit (  |

| Legend:         |                 |                                     |                              |                              |                       |                        |        |

| R = Readable    | bit             | W = Writable                        | bit                          | U = Unimplen                 | nented bit, rea       | d as '0'               |        |

| -n = Value at P |                 | '1' = Bit is se                     |                              | '0' = Bit is clea            |                       | x = Bit is unkno       | own    |

|                 |                 |                                     | •                            | 0 2000 0.00                  |                       |                        |        |

| bit 15-14       | Unimplemen      | ted: Read as                        | ʻ0 <b>'</b>                  |                              |                       |                        |        |

| bit 13          | ADIE: ADC1      | Conversion Co                       | omplete Interru              | ipt Enable bit               |                       |                        |        |

|                 |                 | request is enal                     |                              |                              |                       |                        |        |

|                 |                 | request is not e                    |                              | (4)                          |                       |                        |        |

| bit 12          |                 |                                     | er Interrupt Ena             | ble bit <sup>(1)</sup>       |                       |                        |        |

|                 | •               | request is enal<br>request is not e |                              |                              |                       |                        |        |

| bit 11          | -               | -                                   | Interrupt Enabl              | e hit(1)                     |                       |                        |        |

|                 |                 | request is enal                     | -                            | C Dit                        |                       |                        |        |

|                 |                 | request is not e                    |                              |                              |                       |                        |        |

| bit 10          | SPI1IE: SPI1    | Event Interrup                      | ot Enable bit <sup>(1)</sup> |                              |                       |                        |        |

|                 |                 | request is enal<br>request is not ( |                              |                              |                       |                        |        |

| bit 9           | •               | •                                   | upt Enable bit <sup>(1</sup> | 1)                           |                       |                        |        |

|                 |                 | request is enal                     |                              |                              |                       |                        |        |

|                 | •               | request is not e                    |                              |                              |                       |                        |        |

| bit 8           | Unimplemen      | ted: Read as                        | ʻ0'                          |                              |                       |                        |        |

| bit 7           |                 | Interrupt Enab                      |                              |                              |                       |                        |        |

|                 |                 | request is enal                     |                              |                              |                       |                        |        |

| bit 6-4         | •               | request is not o                    |                              |                              |                       |                        |        |

| bit 3           | -               | ited: Read as                       |                              |                              |                       |                        |        |

| bit 5           |                 | Interrupt Enat<br>request is enal   |                              |                              |                       |                        |        |

|                 |                 | request is not e                    |                              |                              |                       |                        |        |

| bit 2           | OC1IE: Outp     | ut Compare Cl                       | nannel 1 Interro             | upt Enable bit <sup>(1</sup> | )                     |                        |        |

|                 |                 | request is enal<br>request is not e |                              |                              |                       |                        |        |

| bit 1           | •               | •                                   | nel 1 Interrupt E            | Enable bit(2)                |                       |                        |        |

|                 |                 | request is enal                     |                              |                              |                       |                        |        |

|                 | •               | request not en                      |                              |                              |                       |                        |        |

| bit 0           | INTOIE: Exter   | rnal Interrupt 0                    | Enable bit                   |                              |                       |                        |        |

|                 |                 | request is enal<br>request is not e |                              |                              |                       |                        |        |

| Note 1: This    | bit is not impl | emented in ds                       |                              | 001/1010/102/                | daviaca               |                        |        |

#### REGISTER 7-12: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0

**Note 1:** This bit is not implemented in dsPIC33FJ06GS001/101A/102A devices.

2: This bit is not implemented in the dsPIC33FJ06GS001 device.

| <b>REGISTER 7</b>     | -16: IEC5:      | INTERRUPT                           | ENABLE CO | ONTROL RE        | GISTER 5         |                |        |

|-----------------------|-----------------|-------------------------------------|-----------|------------------|------------------|----------------|--------|

| R/W-0                 | R/W-0           | U-0                                 | U-0       | U-0              | U-0              | U-0            | U-0    |

| PWM2IE <sup>(1)</sup> | PWM1IE          | —                                   | _         | —                | —                | —              | —      |

| bit 15                |                 |                                     |           |                  |                  |                | bit 8  |

|                       |                 |                                     |           |                  |                  |                |        |

| U-0                   | U-0             | U-0                                 | U-0       | U-0              | U-0              | U-0            | R/W-0  |

|                       |                 |                                     | —         |                  |                  | —              | JTAGIE |

| bit 7                 |                 |                                     |           |                  |                  |                | bit 0  |

|                       |                 |                                     |           |                  |                  |                |        |

| Legend:               |                 |                                     |           |                  |                  |                |        |

| R = Readable          | bit             | W = Writable                        | bit       | U = Unimpler     | mented bit, read | l as '0'       |        |

| -n = Value at F       | POR             | '1' = Bit is set                    |           | '0' = Bit is cle | eared            | x = Bit is unk | nown   |

|                       |                 |                                     | (4)       |                  |                  |                |        |

| bit 15                |                 | /M2 Interrupt E                     |           |                  |                  |                |        |

|                       |                 | request is enab<br>request is not e |           |                  |                  |                |        |

| bit 14                | •               | /M1 Interrupt E                     |           |                  |                  |                |        |

| bit 14                |                 | request is enab                     |           |                  |                  |                |        |

|                       | •               | request is not e                    |           |                  |                  |                |        |

| bit 13-1              | Unimplemen      | ted: Read as '                      | כי        |                  |                  |                |        |

| bit 0                 | JTAGIE: JTA     | G Interrupt Ena                     | ble bit   |                  |                  |                |        |

|                       | 1 = Interrupt i | request is enab                     | led       |                  |                  |                |        |

|                       | 0 = Interrupt i | request is not e                    | nabled    |                  |                  |                |        |

|                       |                 |                                     |           |                  |                  |                |        |

#### REGISTER 7-16: IEC5: INTERRUPT ENABLE CONTROL REGISTER 5

**Note 1:** This bit is not implemented in dsPIC33FJ06GS001/101A devices.

| U-0          | R/W-1       | R/W-0                                     | R/W-0          | U-0                          | R/W-1            | R/W-0           | R/W-0 |

|--------------|-------------|-------------------------------------------|----------------|------------------------------|------------------|-----------------|-------|

| —            |             | U1RXIP<2:0>(1)                            |                |                              |                  | SPI1IP<2:0>(1)  |       |

| oit 15       |             |                                           |                |                              |                  |                 | bit   |

|              |             |                                           |                |                              |                  |                 |       |

| U-0          | R/W-1       | R/W-0                                     | R/W-0          | U-0                          | U-0              | U-0             | U-0   |

|              |             | SPI1EIP<2:0>(1)                           | )              | —                            |                  | —               | _     |

| bit 7        |             |                                           |                |                              |                  |                 | bit   |

|              |             |                                           |                |                              |                  |                 |       |

| Legend:      |             |                                           |                |                              |                  |                 |       |

| R = Readab   | le bit      | W = Writable b                            | oit            | U = Unimpler                 | nented bit, read | d as '0'        |       |

| -n = Value a | t POR       | '1' = Bit is set                          |                | '0' = Bit is cle             | ared             | x = Bit is unkn | own   |

|              |             |                                           |                |                              |                  |                 |       |

| bit 15       | Unimplem    | ented: Read as 'o                         | )'             |                              |                  |                 |       |

| bit 14-12    | U1RXIP<2:   | 0>: UART1 Rece                            | iver Interrupt | Priority bits <sup>(1)</sup> |                  |                 |       |

|              | 111 = Inter | rupt is Priority 7 (ł                     | nighest priori | ty interrupt)                |                  |                 |       |

|              | •           |                                           |                |                              |                  |                 |       |

|              | •           |                                           |                |                              |                  |                 |       |

|              | 001 = Inter | rupt is Priority 1                        |                |                              |                  |                 |       |

|              |             | rupt source is disa                       | abled          |                              |                  |                 |       |

| bit 11       | Unimplem    | ented: Read as 'o                         | )'             |                              |                  |                 |       |

| bit 10-8     | SPI1IP<2:0  | >: SPI1 Event Int                         | errupt Priorit | y bits <sup>(1)</sup>        |                  |                 |       |

|              | 111 = Inter | rupt is Priority 7 (ł                     | nighest priori | ty interrupt)                |                  |                 |       |

|              | •           |                                           |                |                              |                  |                 |       |

|              | •           |                                           |                |                              |                  |                 |       |

|              | 001 = Inter | rupt is Priority 1                        |                |                              |                  |                 |       |

|              |             | rupt source is disa                       | abled          |                              |                  |                 |       |

| bit 7        | Unimplem    | ented: Read as 'o                         | )'             |                              |                  |                 |       |

| bit 6-4      | SPI1EIP<2   | :0>: SPI1 Error In                        | terrupt Priori | ty bits <sup>(1)</sup>       |                  |                 |       |

|              | 111 = Inter | rupt is Priority 7 (I                     | nighest priori | ty interrupt)                |                  |                 |       |

|              | •           |                                           |                |                              |                  |                 |       |

|              | •           |                                           |                |                              |                  |                 |       |

|              |             | rupt is Priority 1<br>rupt source is disa | abled          |                              |                  |                 |       |

|              |             | •                                         |                |                              |                  |                 |       |

#### Note 1: These bits are not implemented in the dsPIC33FJ06GS001 device.

| U-0           | R/W-1                                                               | R/W-0                 | R/W-0           | U-0                 | R/W-1            | R/W-0           | R/W-0 |  |  |  |

|---------------|---------------------------------------------------------------------|-----------------------|-----------------|---------------------|------------------|-----------------|-------|--|--|--|

| _             |                                                                     | PWM2IP <sup>(1)</sup> |                 |                     |                  | PWM1IP<2:0>     |       |  |  |  |

| bit 15        |                                                                     |                       |                 |                     |                  |                 | bit 8 |  |  |  |

|               |                                                                     |                       |                 |                     |                  |                 |       |  |  |  |

| U-0           | U-0                                                                 | U-0                   | U-0             | U-0                 | U-0              | U-0             | U-0   |  |  |  |

|               | _                                                                   | _                     | _               | —                   | —                | _               |       |  |  |  |

| bit 7         |                                                                     |                       |                 |                     |                  |                 | bit ( |  |  |  |

| Legend:       |                                                                     |                       |                 |                     |                  |                 |       |  |  |  |

| R = Readabl   | R = Readable bit W = Writable bit                                   |                       |                 | U = Unimplen        | nented bit, read | l as '0'        |       |  |  |  |

| -n = Value at | -n = Value at POR (1' = Bit is set                                  |                       |                 |                     | ared             | x = Bit is unkr | nown  |  |  |  |

|               |                                                                     |                       |                 |                     |                  |                 |       |  |  |  |

| bit 15        | Unimplemer                                                          | ted: Read as '        | 0'              |                     |                  |                 |       |  |  |  |

| bit 14-12     | PWM2IP<2:0                                                          | >: PWM2 Inter         | rupt Priority b | oits <sup>(1)</sup> |                  |                 |       |  |  |  |

|               | 111 = Interru                                                       | pt is Priority 7 (    | highest priori  | ty)                 |                  |                 |       |  |  |  |

|               | •                                                                   |                       |                 |                     |                  |                 |       |  |  |  |

|               | •                                                                   |                       |                 |                     |                  |                 |       |  |  |  |

|               | •                                                                   |                       |                 |                     |                  |                 |       |  |  |  |

|               | 001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled |                       |                 |                     |                  |                 |       |  |  |  |

| bit 11        | Unimplemer                                                          | ted: Read as '        | 0'              |                     |                  |                 |       |  |  |  |

| bit 10-8      | PWM1IP<2:0                                                          | >: PWM1 Inter         | rupt Priority b | oits                |                  |                 |       |  |  |  |

|               | 111 = Interru                                                       | pt is Priority 7 (    | highest priori  | ty)                 |                  |                 |       |  |  |  |

|               | •                                                                   |                       |                 |                     |                  |                 |       |  |  |  |

|               | •                                                                   |                       |                 |                     |                  |                 |       |  |  |  |

|               | •                                                                   |                       |                 |                     |                  |                 |       |  |  |  |

|               |                                                                     | pt is Priority 1      |                 |                     |                  |                 |       |  |  |  |

|               | 000 = Interru                                                       | pt source is dis      | abled           |                     |                  |                 |       |  |  |  |

| bit 7-0       |                                                                     | ted: Read as '        |                 |                     |                  |                 |       |  |  |  |

**Note 1:** These bits are not implemented in dsPIC33FJ06GS001/101A devices.

#### 8.6 Fail-Safe Clock Monitor (FSCM)

The Fail-Safe Clock Monitor (FSCM) allows the device to continue to operate, even in the event of an oscillator failure. The FSCM function is enabled by programming. If the FSCM function is enabled, the LPRC internal oscillator runs at all times (except during Sleep mode) and is not subject to control by the Watchdog Timer.

In the event of an oscillator failure, the FSCM generates a clock failure trap event and switches the system clock over to the FRC oscillator. Then, the application program can either attempt to restart the oscillator or execute a controlled shutdown. The trap can be treated as a warm Reset by simply loading the Reset address into the oscillator fail trap vector.

If the PLL multiplier is used to scale the system clock, the internal FRC is also multiplied by the same factor on clock failure. Essentially, the device switches to FRC with PLL on a clock failure.

#### 8.7 Pseudo-Random Generator

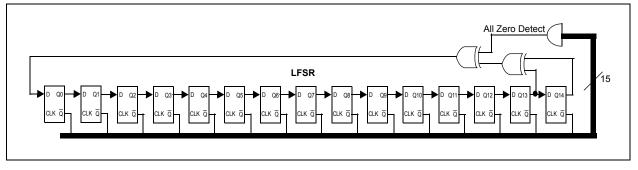

The pseudo-random generator is implemented with a 15-bit Linear Feedback Shift Register (LFSR), which is a shift register with a few exclusive OR gates. The shift register is clocked by the PWM clock and is a read-only register. The purpose of this feature is to provide the ability to randomly change the period or the active portion of the PWM.

A firmware routine can be used to read "n" random bits from the LFSR register and combine them, by either summing or performing another logical operation with the PWM period of the Duty Cycle registers. The result will be a PWM signal whose nominal period (or duty cycle) is the desired one, but whose effective value changes randomly. This capability will help in reducing the EMI/EMC emissions by spreading the power over a wider frequency range.

Figure 8-3 provides a block diagram of the LFSR.

| <b>REGISTER 9</b> | 9-2: PMD2    | 2: PERIPHER                        |                 | E DISABLE C       | ONTROL RE        | GISTER 2 |                      |

|-------------------|--------------|------------------------------------|-----------------|-------------------|------------------|----------|----------------------|

| U-0               | U-0          | U-0                                | U-0             | U-0               | U-0              | U-0      | R/W-0                |

|                   |              | —                                  | —               | —                 | —                | —        | IC1MD <sup>(1)</sup> |

| bit 15            |              |                                    |                 |                   |                  |          | bit 8                |

| U-0               | U-0          | U-0                                | U-0             | U-0               | U-0              | U-0      | R/W-0                |

|                   |              |                                    |                 | _                 | <u> </u>         |          | OC1MD <sup>(2)</sup> |

| bit 7             |              |                                    |                 | 4                 |                  |          | bit 0                |

|                   |              |                                    |                 |                   |                  |          |                      |

| Legend:           |              |                                    |                 |                   |                  |          |                      |

| R = Readable      | e bit        | W = Writable                       | bit             | U = Unimplem      | nented bit, read | l as '0' |                      |

| -n = Value at I   | POR          | '1' = Bit is set                   |                 | '0' = Bit is clea | nown             |          |                      |

|                   |              |                                    |                 |                   |                  |          |                      |

| bit 15-9          | -            | ted: Read as '                     |                 |                   |                  |          |                      |

| bit 8             | IC1MD: Input | Capture 1 Mod                      | dule Disable bi | t(1)              |                  |          |                      |

|                   |              | ture 1 module i<br>ture 1 module i |                 |                   |                  |          |                      |

| bit 7-1           | Unimplemen   | ted: Read as '                     | o'              |                   |                  |          |                      |

bit 0 OC1MD: Output Compare 1 Module Disable bit<sup>(2)</sup>

1 = Output Compare 1 module is disabled

0 = Output Compare 1 module is enabled

- **Note 1:** This bit is not implemented in dsPIC33FJ06GS001/101A/102A devices.

- 2: This bit is not implemented in the dsPIC33FJ06GS001 device.

| U-0          | U-0                 | U-0              | U-0            | U-0               | U-0              | U-0             | U-0   |  |  |  |

|--------------|---------------------|------------------|----------------|-------------------|------------------|-----------------|-------|--|--|--|

| _            | —                   | _                |                | —                 | _                | —               |       |  |  |  |

| bit 15       |                     |                  |                |                   |                  |                 | bit 8 |  |  |  |

|              |                     |                  |                |                   |                  |                 |       |  |  |  |

| U-0          | U-0                 | R/W-1            | R/W-1          | R/W-1             | R/W-1            | R/W-1           | R/W-1 |  |  |  |

| —            | —                   | T2CKR<5:0>       |                |                   |                  |                 |       |  |  |  |

| bit 7        |                     |                  |                |                   |                  |                 | bit 0 |  |  |  |

|              |                     |                  |                |                   |                  |                 |       |  |  |  |

| Legend:      |                     |                  |                |                   |                  |                 |       |  |  |  |

| R = Readab   | le bit              | W = Writable I   | oit            | U = Unimpler      | mented bit, read | as '0'          |       |  |  |  |

| -n = Value a | t POR               | '1' = Bit is set |                | '0' = Bit is cle  | ared             | x = Bit is unkn | iown  |  |  |  |

|              |                     |                  |                |                   |                  |                 |       |  |  |  |

| bit 15-6     | Unimplement         | ted: Read as '0  | )'             |                   |                  |                 |       |  |  |  |

| bit 5-0      | T2CKR<5:0>:         | Assign Timer2    | 2 External Clo | ock (T2CK) to the | he Correspondi   | ng RPn Pin bits | 5     |  |  |  |

|              | 111111 <b>= Inp</b> | ut tied to Vss   |                |                   |                  |                 |       |  |  |  |

|              |                     | ut tied to RP35  |                |                   |                  |                 |       |  |  |  |

|              |                     | ut tied to RP34  |                |                   |                  |                 |       |  |  |  |

|              |                     | ut tied to RP33  |                |                   |                  |                 |       |  |  |  |

|              | 100000 <b>= Inp</b> |                  |                |                   |                  |                 |       |  |  |  |

#### REGISTER 10-4: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

•

•

00000 = Input tied to RP0

| U-0          | U-0     | R/W-1            | R/W-1 | R/W-1                              | R/W-1  | R/W-1              | R/W-1 |

|--------------|---------|------------------|-------|------------------------------------|--------|--------------------|-------|

| _            | —       |                  |       | FLT1                               | R<5:0> |                    |       |

| bit 15       |         |                  |       |                                    |        |                    | bit 8 |

|              |         |                  |       |                                    |        |                    |       |

| U-0          | U-0     | U-0              | U-0   | U-0                                | U-0    | U-0                | U-0   |

| —            | _       | —                | _     | —                                  |        | —                  | —     |

| bit 7        |         |                  |       |                                    |        |                    | bit 0 |

| Legend:      |         |                  |       |                                    |        |                    |       |

| R = Readab   | ole bit | W = Writable     | bit   | U = Unimplemented bit, read as '0' |        |                    |       |

| -n = Value a | at POR  | '1' = Bit is set |       | '0' = Bit is cleared               |        | x = Bit is unknown |       |

#### REGISTER 10-10: RPINR29: PERIPHERAL PIN SELECT INPUT REGISTER 29

bit 15-14 Unimplemented: Read as '0'

bit 13-8

8 FLT1R<5:0>: Assign PWM Fault Input 1 (FLT1) to the Corresponding RPn Pin bits

111111 = Input tied to Vss 100011 = Input tied to RP35 100010 = Input tied to RP34 100001 = Input tied to RP33 100000 = Input tied to RP32 • • •

bit 7-0 Unimplemented: Read as '0'

| U-0                | U-0                                                                                                                                           | R/W-1                                                                                                                                                                                                                                 | R/W-1                              | R/W-1                       | R/W-1            | R/W-1             | R/W-1 |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------------|------------------|-------------------|-------|

|                    | —                                                                                                                                             |                                                                                                                                                                                                                                       |                                    | SYNCI                       | 1R<5:0>          |                   |       |

| bit 15             |                                                                                                                                               |                                                                                                                                                                                                                                       |                                    |                             |                  |                   | bit   |

|                    |                                                                                                                                               |                                                                                                                                                                                                                                       |                                    |                             |                  |                   |       |

| U-0                | U-0                                                                                                                                           | R/W-1                                                                                                                                                                                                                                 | R/W-1                              | R/W-1                       | R/W-1            | R/W-1             | R/W-1 |

| _                  |                                                                                                                                               |                                                                                                                                                                                                                                       |                                    | FLT8                        | R<5:0>           |                   |       |

| bit 7              |                                                                                                                                               |                                                                                                                                                                                                                                       |                                    |                             |                  |                   | bit   |

| Legend:            |                                                                                                                                               |                                                                                                                                                                                                                                       |                                    |                             |                  |                   |       |

| R = Readab         | le bit                                                                                                                                        | W = Writable I                                                                                                                                                                                                                        | oit                                | U = Unimplen                | nented bit, read | d as '0'          |       |

| -n = Value a       | t POR                                                                                                                                         | '1' = Bit is set                                                                                                                                                                                                                      |                                    | '0' = Bit is clea           |                  | x = Bit is unkr   | nown  |

|                    |                                                                                                                                               |                                                                                                                                                                                                                                       |                                    |                             |                  |                   |       |

| bit 15-14          | Unimplemen                                                                                                                                    | nted: Read as '0                                                                                                                                                                                                                      | )'                                 |                             |                  |                   |       |

| bit 13-8           | SYNCI1R<5:                                                                                                                                    | 0>: Assign PWI                                                                                                                                                                                                                        | M Master Tim                       | e Base Externa              | al Synchronizat  | ion Signal to th  | e     |

|                    |                                                                                                                                               |                                                                                                                                                                                                                                       |                                    | o Baoo Extorna              |                  | ion orginal to th |       |

|                    |                                                                                                                                               | ng RPn Pin bits                                                                                                                                                                                                                       |                                    |                             |                  |                   |       |

|                    | Correspondir                                                                                                                                  | ng RPn Pin bits<br>put tied to Vss                                                                                                                                                                                                    |                                    |                             |                  |                   |       |

|                    | Correspondir<br>111111 = Inp                                                                                                                  | •                                                                                                                                                                                                                                     | i                                  |                             |                  |                   |       |

|                    | Correspondir<br>111111 = Ing<br>100011 = Ing<br>100010 = Ing                                                                                  | put tied to Vss<br>put tied to RP35<br>put tied to RP34                                                                                                                                                                               |                                    |                             |                  |                   |       |

|                    | Correspondir<br>111111 = Ing<br>100011 = Ing<br>100010 = Ing<br>100001 = Ing                                                                  | put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33                                                                                                                                                           |                                    |                             |                  |                   |       |

|                    | Correspondir<br>111111 = Ing<br>100011 = Ing<br>100010 = Ing<br>100001 = Ing                                                                  | put tied to Vss<br>put tied to RP35<br>put tied to RP34                                                                                                                                                                               |                                    |                             |                  |                   |       |

|                    | Correspondir<br>111111 = Ing<br>100011 = Ing<br>100010 = Ing<br>100001 = Ing                                                                  | put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33                                                                                                                                                           |                                    |                             |                  |                   |       |

|                    | Correspondir<br>111111 = Ing<br>100011 = Ing<br>100010 = Ing<br>100001 = Ing                                                                  | put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33                                                                                                                                                           |                                    |                             |                  |                   |       |

|                    | Correspondir<br>111111 = Ing<br>100011 = Ing<br>100010 = Ing<br>100001 = Ing<br>00000 = Ing                                                   | put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33<br>put tied to RP33                                                                                                                                       |                                    |                             |                  |                   |       |

|                    | Correspondir<br>111111 = Ing<br>100011 = Ing<br>100010 = Ing<br>100001 = Ing<br>00000 = Ing                                                   | put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33                                                                                                                                                           |                                    |                             |                  |                   |       |

| bit 7-6            | Correspondir<br>111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>00000 = Inpu                                                  | put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33<br>put tied to RP33                                                                                                                                       |                                    |                             |                  |                   |       |

| bit 7-6<br>bit 5-0 | Correspondir<br>111111 = Ing<br>100011 = Ing<br>100010 = Ing<br>100000 = Ing<br>•<br>•<br>•<br>000000 = Ingu<br>Unimplement                   | put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33<br>put tied to RP32<br>ut tied to RP32                                                                                                                    | ,<br>,                             | FLT8) to the Co             | prresponding R   | Pn Pin bits       |       |

|                    | Correspondir<br>111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>000000 = Inpu<br>Unimplement<br>FLT8R<5:0>:    | put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33<br>put tied to RP32<br>ut tied to RP32                                                                                                                    | ,<br>,                             | <sup>-</sup> LT8) to the Co | prresponding R   | Pn Pin bits       |       |

|                    | Correspondir<br>111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100000 = Inp<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33<br>put tied to RP32<br>ut tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35                     | ),<br>Fault Input 8 (I             | <sup>-</sup> LT8) to the Co | prresponding R   | Pn Pin bits       |       |

|                    | Correspondir<br>111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100000 = Inp                                                                  | put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33<br>put tied to RP32<br>ut tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34 | ) <sup>)</sup><br>Fault Input 8 (I | FLT8) to the Co             | orresponding R   | Pn Pin bits       |       |

|                    | Correspondir<br>111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100000 = Inp                                                                  | put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33<br>put tied to RP32<br>ut tied to RP32<br>ut tied to RP35<br>put tied to RP35<br>put tied to RP34<br>put tied to RP34<br>put tied to RP33                 | o'<br>Fault Input 8 (I             | <sup>-</sup> LT8) to the Co | prresponding R   | Pn Pin bits       |       |

|                    | Correspondir<br>111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100000 = Inp                                                                  | put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33<br>put tied to RP32<br>ut tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34 | o'<br>Fault Input 8 (I             | <sup>-</sup> LT8) to the Co | prresponding R   | Pn Pin bits       |       |

|                    | Correspondir<br>111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100000 = Inp                                                                  | put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33<br>put tied to RP32<br>ut tied to RP32<br>ut tied to RP35<br>put tied to RP35<br>put tied to RP34<br>put tied to RP34<br>put tied to RP33                 | o'<br>Fault Input 8 (I             | FLT8) to the Co             | prresponding R   | Pn Pin bits       |       |

|                    | Correspondir<br>111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100000 = Inp                                                                  | put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33<br>put tied to RP32<br>ut tied to RP32<br>ut tied to RP35<br>put tied to RP35<br>put tied to RP34<br>put tied to RP34<br>put tied to RP33                 | o'<br>Fault Input 8 (I             | <sup>=</sup> LT8) to the Co | prresponding R   | Pn Pin bits       |       |

|                    | Correspondir<br>111111 = Inp<br>100011 = Inp<br>100010 = Inp<br>100000 = Inp                                                                  | put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33<br>put tied to RP32<br>ut tied to RP32<br>ut tied to RP35<br>put tied to RP35<br>put tied to RP34<br>put tied to RP34<br>put tied to RP33                 | o'<br>Fault Input 8 (I             | <sup>-</sup> LT8) to the Co | orresponding R   | Pn Pin bits       |       |

#### REGISTER 10-14: RPINR33: PERIPHERAL PIN SELECT INPUT REGISTER 33

#### 11.1 Timer1 Control Register

| R/W-0         | U-0                                              | R/W-0            | U-0           | U-0              | U-0              | U-0             | U-0 |  |  |  |

|---------------|--------------------------------------------------|------------------|---------------|------------------|------------------|-----------------|-----|--|--|--|

| TON           |                                                  | TSIDL            |               |                  |                  |                 | —   |  |  |  |

| bit 15        |                                                  |                  |               |                  |                  | 1               | bit |  |  |  |

|               |                                                  |                  |               |                  |                  |                 |     |  |  |  |

| U-0           | R/W-0                                            | R/W-0            | R/W-0         | U-0              | R/W-0            | R/W-0           | U-0 |  |  |  |

| —             | TGATE                                            | TCKP             | S<1:0>        |                  | TSYNC            | TCS             |     |  |  |  |

| bit 7         |                                                  |                  |               |                  |                  |                 | bit |  |  |  |

|               |                                                  |                  |               |                  |                  |                 |     |  |  |  |

| Legend:       | - 1-14                                           |                  | L 14          |                  |                  | l (0'           |     |  |  |  |

| R = Readabl   |                                                  | W = Writable     |               | -                | mented bit, read |                 |     |  |  |  |

| -n = Value at | POR                                              | '1' = Bit is set |               | '0' = Bit is cle | eared            | x = Bit is unkn | own |  |  |  |

|               |                                                  | 0.1.1            |               |                  |                  |                 |     |  |  |  |

| bit 15        | TON: Timer1                                      |                  |               |                  |                  |                 |     |  |  |  |

|               | 1 = Starts 16<br>0 = Stops 16                    |                  |               |                  |                  |                 |     |  |  |  |

| bit 14        | -                                                | nted: Read as '  | ∩'            |                  |                  |                 |     |  |  |  |

| bit 13        | -                                                | in Idle Mode bi  |               |                  |                  |                 |     |  |  |  |

|               |                                                  |                  |               | device enters    | Idle mode        |                 |     |  |  |  |

|               |                                                  | s module opera   |               |                  |                  |                 |     |  |  |  |

| bit 12-7      | Unimplemer                                       | nted: Read as '  | 0'            |                  |                  |                 |     |  |  |  |

| bit 6         | TGATE: Timer1 Gated Time Accumulation Enable bit |                  |               |                  |                  |                 |     |  |  |  |

|               | <u>When TCS =</u><br>This bit is ign             |                  |               |                  |                  |                 |     |  |  |  |

|               | When TCS =                                       |                  |               |                  |                  |                 |     |  |  |  |

|               |                                                  | ne accumulatio   |               |                  |                  |                 |     |  |  |  |

|               |                                                  | ne accumulatio   |               |                  |                  |                 |     |  |  |  |

| bit 5-4       |                                                  | Timer1 Input     | Clock Presca  | ale Select bits  |                  |                 |     |  |  |  |

|               | 11 = 1:256<br>10 = 1:64                          |                  |               |                  |                  |                 |     |  |  |  |

|               | 01 = 1:8                                         |                  |               |                  |                  |                 |     |  |  |  |

|               | 00 = 1:1                                         |                  |               |                  |                  |                 |     |  |  |  |

| bit 3         | Unimplemer                                       | nted: Read as '  | 0'            |                  |                  |                 |     |  |  |  |

| bit 2         | TSYNC: Time                                      | er1 External Cl  | ock Input Syr | hchronization S  | elect bit        |                 |     |  |  |  |

|               | When TCS =                                       |                  |               |                  |                  |                 |     |  |  |  |

|               |                                                  | nizes external o |               | innut            |                  |                 |     |  |  |  |

|               | When TCS =                                       | synchronize e    |               | input            |                  |                 |     |  |  |  |

|               | This bit is ign                                  |                  |               |                  |                  |                 |     |  |  |  |

| bit 1         | •                                                | Clock Source     | Select bit    |                  |                  |                 |     |  |  |  |

|               |                                                  | clock from T1C   |               | risina edae)     |                  |                 |     |  |  |  |

|               |                                                  |                  |               |                  |                  |                 |     |  |  |  |

|               | 0 = Internal c                                   |                  | P (* * *      | 5 - 5 - 7        |                  |                 |     |  |  |  |

#### REGISTER 11-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0            | R/W-0           | R/W-0                                | R/W-0                 | R/W-0            | R/W-0                 | R/W-0           | R/W-0  |

|------------------|-----------------|--------------------------------------|-----------------------|------------------|-----------------------|-----------------|--------|

| PENH             | PENL            | POLH                                 | POLL                  | PMOD             | <1:0> <sup>(1)</sup>  | OVRENH          | OVRENL |

| bit 15           |                 |                                      |                       |                  |                       |                 | bit    |

| R/W-0            | R/W-0           | R/W-0                                | R/W-0                 | R/W-0            | R/W-0                 | R/W-0           | R/W-0  |

|                  | )AT<1:0>        |                                      | -<1:0> <sup>(2)</sup> | -                | -<1:0> <sup>(2)</sup> | SWAP            | OSYNC  |

| bit 7            | /// · · · · ·   | 1 LI D/ (I                           | 1.0                   | 020/11           | 1.0                   | 0111            | bit    |

|                  |                 |                                      |                       |                  |                       |                 |        |

| Legend:          |                 |                                      |                       |                  |                       |                 |        |

| R = Readable bit |                 | W = Writable                         |                       | -                | nented bit, rea       | d as '0'        |        |

| -n = Value at    | POR             | '1' = Bit is set                     |                       | '0' = Bit is cle | ared                  | x = Bit is unkr | IOWN   |

| bit 15           | PENH: PWM       | IxH Output Pin                       | Ownership bit         | :                |                       |                 |        |

|                  |                 | dule controls F                      |                       |                  |                       |                 |        |

|                  | 0 = GPIO mo     | odule controls F                     | WMxH pin              |                  |                       |                 |        |

| bit 14           |                 | xL Output Pin (                      | -                     |                  |                       |                 |        |

|                  |                 | dule controls F                      |                       |                  |                       |                 |        |

| L:1 1 0          |                 | odule controls F                     | •                     |                  |                       |                 |        |

| bit 13           |                 | IxH Output Pin<br>pin is active-lov  | •                     |                  |                       |                 |        |

|                  |                 | pin is active-low                    |                       |                  |                       |                 |        |

| bit 12           |                 | xL Output Pin F                      |                       |                  |                       |                 |        |

|                  | 1 = PWMxL       | pin is active-low                    | V                     |                  |                       |                 |        |

| bit 11-10        | -               | : PWMx I/O Pir                       |                       |                  |                       |                 |        |

|                  | 11 = PWM I/     | O pin pair is in                     | the True Indep        | pendent Output   | mode                  |                 |        |

|                  |                 | O pin pair is in                     |                       |                  |                       |                 |        |

|                  |                 | O pin pair is in<br>O pin pair is in |                       |                  | aada                  |                 |        |

| bit 9            |                 | verride Enable                       | •                     |                  | loue                  |                 |        |

| DIL 9            |                 | <pre>verifice Enable </pre>          |                       |                  |                       |                 |        |

|                  |                 | nerator provide                      |                       |                  | 1                     |                 |        |

| bit 8            | OVRENL: O       | verride Enable                       | for PWMxL Pi          | n bit            |                       |                 |        |

|                  | 1 = OVRDAT      | <0> provides d                       | lata for output       | on PWMxL pin     | l                     |                 |        |

|                  | 0 = PWM ge      | nerator provide                      | s data for PW         | MxL pin          |                       |                 |        |

| bit 7-6          | OVRDAT<1:       | 0>: Data for PV                      | VMxH and PW           | /MxL Pins if Ov  | verride is Enab       | led bits        |        |

|                  |                 | = 1 then OVR                         | •                     |                  |                       |                 |        |

|                  |                 | = 1 then OVR                         | •                     |                  |                       |                 |        |

| bit 5-4          |                 | >: State for PW                      |                       |                  | I MOD IS Enab         | ied bits        |        |

|                  |                 | CLCONx<15>)<br>ive, then FLTD        |                       |                  | P\//MxH               |                 |        |

|                  |                 | ive, then FLTD                       |                       |                  |                       |                 |        |

|                  |                 | CLCONx<15>)                          | •                     |                  |                       |                 |        |

|                  | If current-lim  | it is active, then                   | FLTDAT<1>             | provides the sta | ate for PWMxI         | Η.              |        |

|                  | If Fault is act | ive then FLTD.                       | AT<0> nrovide         | es the state for | PWMxI                 |                 |        |

#### REGISTER 15-14: IOCONX: PWMx I/O CONTROL REGISTER

**Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

**2:** State represents the active/inactive state of the PWM module depending on the POLH and POLL bit settings.

| R/W-0        | R/W-0          | R/W-0                                                                           | R/W-0         | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |

|--------------|----------------|---------------------------------------------------------------------------------|---------------|------------------|------------------|-----------------|-------|--|--|

| PHR          | PHF            | PLR                                                                             | PLF           | FLTLEBEN         | CLLEBEN          | LEB<            | 6:5>  |  |  |

| bit 15       |                |                                                                                 |               |                  |                  |                 | bit   |  |  |

|              | <b>D</b> 444 0 | D 444 0                                                                         | DAMA          | DAMA             |                  |                 |       |  |  |

| R/W-0        | R/W-0          | R/W-0                                                                           | R/W-0         | R/W-0            | U-0              | U-0             | U-0   |  |  |

| L:1 7        |                | LEB<4:0>                                                                        |               |                  |                  | —               |       |  |  |

| bit 7        |                |                                                                                 |               |                  |                  |                 | bit   |  |  |

| Legend:      |                |                                                                                 |               |                  |                  |                 |       |  |  |

| R = Readat   | ole bit        | W = Writable                                                                    | bit           | U = Unimplen     | nented bit, read | as '0'          |       |  |  |

| -n = Value a | at POR         | '1' = Bit is set                                                                |               | '0' = Bit is cle | ared             | x = Bit is unkn | own   |  |  |

|              |                |                                                                                 |               |                  |                  |                 |       |  |  |

| bit 15       | PHR: PWM       | xH Rising Edge                                                                  | Trigger Enabl | le bit           |                  |                 |       |  |  |

|              |                | dge of PWMxH                                                                    |               | B counter        |                  |                 |       |  |  |

|              | 0 = LEB ign    | ores rising edge                                                                | of PWMxH      |                  |                  |                 |       |  |  |

| bit 14       | PHF: PWM       | xH Falling Edge                                                                 | Trigger Enab  | le bit           |                  |                 |       |  |  |

|              |                | edge of PWMxH                                                                   |               | EB counter       |                  |                 |       |  |  |

|              | •              | = LEB ignores falling edge of PWMxH<br>LR: PWMxL Rising Edge Trigger Enable bit |               |                  |                  |                 |       |  |  |

| bit 13       |                | 0 0                                                                             | 00            |                  |                  |                 |       |  |  |

|              | 0              | edge of PWMxL v<br>ores rising edge                                             | 00            | B counter        |                  |                 |       |  |  |

| bit 12       | •              | L Falling Edge T                                                                |               | e hit            |                  |                 |       |  |  |

|              |                | edge of PWMxL v                                                                 |               |                  |                  |                 |       |  |  |

|              |                | ores falling edge                                                               |               | D counter        |                  |                 |       |  |  |

| bit 11       | FLTLEBEN       | : Fault Input LEB                                                               | Enable bit    |                  |                  |                 |       |  |  |

|              |                | -edge blanking is                                                               |               |                  |                  |                 |       |  |  |

|              | 0 = Leading    | -edge blanking is                                                               | s not applied | to selected Fau  | llt input        |                 |       |  |  |

| bit 10       |                | Current-Limit LE                                                                |               |                  |                  |                 |       |  |  |

|              |                | -edge blanking is                                                               |               |                  |                  |                 |       |  |  |

|              | •              | -edge blanking is                                                               |               |                  | •                |                 |       |  |  |

| bit 9-3      |                | Leading-Edge Bl                                                                 | •             | urrent-Limit and | Fault Inputs bit | S               |       |  |  |

|              |                | 8.32 nsec incre                                                                 |               |                  |                  |                 |       |  |  |

| bit 2-0      |                | ented: Read as '                                                                |               |                  |                  |                 |       |  |  |

#### REGISTER 15-18: LEBCONX: PWMx LEADING-EDGE BLANKING CONTROL REGISTER

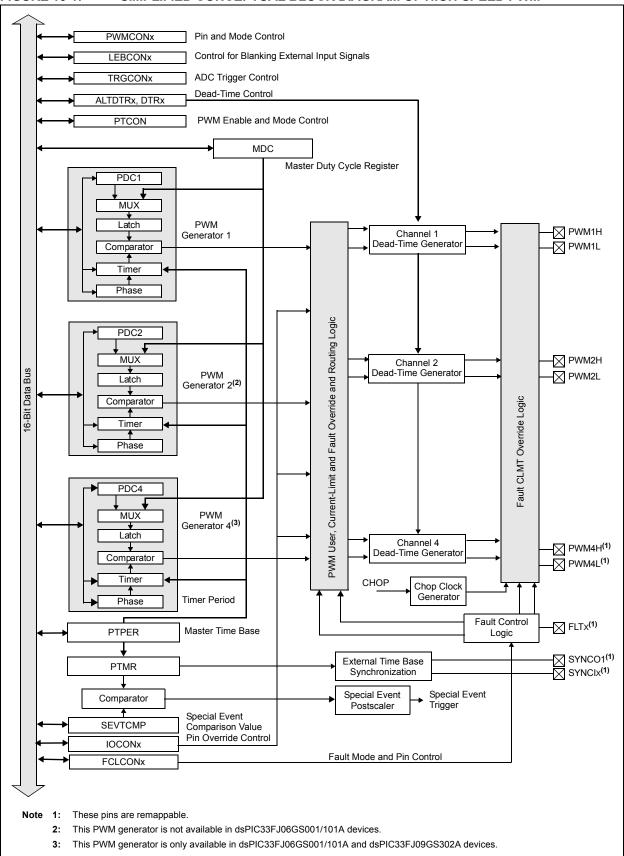

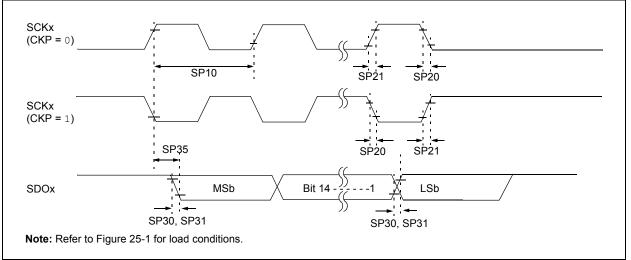

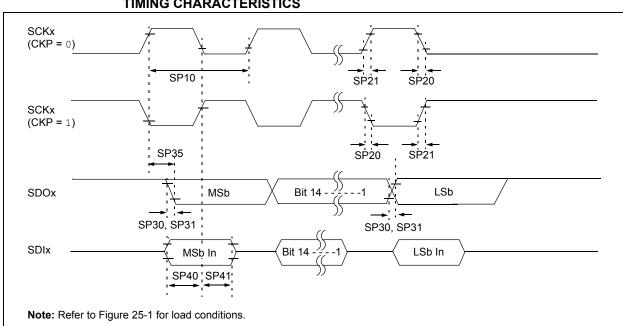

#### 16.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS001/101A/102A/ 202A and dsPIC33FJ09GS302 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 18. "Serial Peripheral Interface (SPI)" (DS70206) of the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

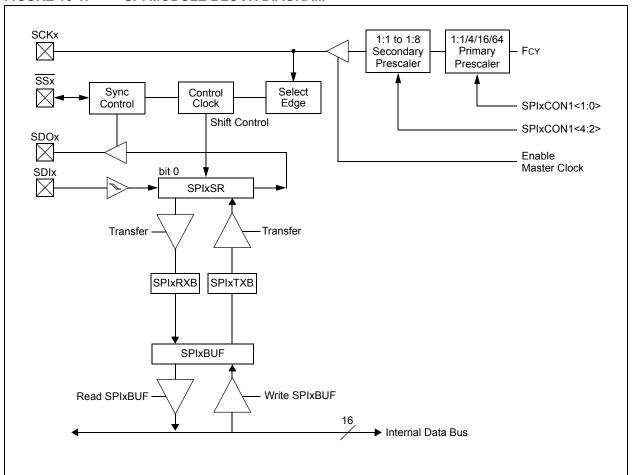

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, Analog-to-Digital Converters, etc. The SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP.

Each SPI module consists of a 16-bit shift register, SPIxSR (where x = 1 or 2), used for shifting data in and out, and a buffer register, SPIxBUF. A control register, SPIxCON, configures the module. Additionally, a status register, SPIxSTAT, indicates status conditions.

The serial interface consists of 4 pins:

- · SDIx (serial data input)

- · SDOx (serial data output)

- · SCKx (shift clock input or output)

- SSx (active-low slave select)

In Master mode operation, SCKx is a clock output; in Slave mode, it is a clock input.

#### FIGURE 16-1: SPI MODULE BLOCK DIAGRAM

# REGISTER 19-6: ADCPC1: ADC CONVERT PAIR CONTROL REGISTER 1 (CONTINUED) bit 7 IRQEN2: Interrupt Request Enable 2 bit<sup>(2)</sup> 1 = Enables IRQ generation when requested conversion of channels AN5 and AN4 is completed 0 = IRQ is not generated