Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 6КВ (2К х 24)                                                                     |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 256 x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 6x10b                                                                         |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-VQFN Exposed Pad                                                               |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs102at-i-mm |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

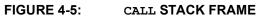

### 4.3.1 SOFTWARE STACK

In addition to its use as a working register, the W15 register in the devices is also used as a software Stack Pointer. The Stack Pointer always points to the first available free word and grows from lower to higher addresses. It predecrements for stack pops and post-increments for stack pushes, as shown in Figure 4-5. For a PC push during any CALL instruction, the MSb of the PC is zero-extended before the push, ensuring that the MSb is always clear.

| Note: | A PC push during exception processing    |  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|--|

|       | concatenates the SRL register to the MSb |  |  |  |  |  |  |  |

|       | of the PC prior to the push.             |  |  |  |  |  |  |  |

The Stack Pointer Limit register (SPLIM) associated with the Stack Pointer sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' because all stack operations must be word-aligned.

Whenever an EA is generated using W15 as a source or destination pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation. For example, to cause a stack error trap when the stack grows beyond address 0x1000 in RAM, initialize the SPLIM with the value 0x0FFE.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0x0800. This prevents the stack from interfering with the Special Function Register (SFR) space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

### 4.4 Instruction Addressing Modes

The addressing modes shown in Table 4-39 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

### 4.4.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire data space.

### 4.4.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where Operand 1 is always a working register (that is, the addressing mode can only be register direct), which is referred to as Wb. Operand 2 can be a W register, fetched from data memory, or a 5-bit literal. The result location can be either a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-Modified

- · Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

Note: Not all instructions support all of the addressing modes shown above. Individual instructions can support different subsets of these addressing modes.

#### **Flash Memory Control Registers** 5.5

| bit 15       Invariant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/SO-0            | R/W-0                       | R/W-0                          | U-0                         | U-0                         | U-0                | U-0                    | U-0           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------|--------------------------------|-----------------------------|-----------------------------|--------------------|------------------------|---------------|

| U-0       R/W-0       U-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         Image: Image                                                                                                                                                                                                                                                                                                        | WR <sup>(1)</sup> | WREN <sup>(1)</sup>         | WRERR <sup>(1)</sup>           | _                           | —                           | _                  | —                      | _             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | bit 15            |                             | · · ·                          |                             |                             |                    |                        | bit 8         |

| -         ERASE <sup>(1)</sup> -         NVMOP<3:0::         1.2           bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | U-0               | R/W-0                       | U-0                            | U-0                         | R/W-0                       | R/W-0              | R/W-0                  | R/W-0         |

| bit 7       bit 7         Legend:       SO = Settable Only bit         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       WR: Write Control bit <sup>(1)</sup> 1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the b cleared by hardware once operation is complete. This bit can only be set (not cleared) in software once operation is complete and inactive         bit 14       WREN: Write Enable bit <sup>(1)</sup> 1 = Enables Flash program/erase operations         o = Inhibits Flash program/erase operations       o = Inhibits Flash program/erase operations         bit 13       WRERR: Write Sequence Error Flag bit <sup>(1)</sup> 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation sepecified by NVMOP<3:0> on the next WR command         bit 6       ERASE: Erase/Program Enable bit <sup>(1)</sup> 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         bit 5-4       Unimplemented: Read as '0'         bit 3-0       NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1:       1111 = No operation         1011 = No operation       0010 = Memory page erase operation         0011 = No oper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                 |                             | _                              | _                           |                             | NVMOP              | <3:0> <sup>(1,2)</sup> | -             |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       WR: Write Control bit <sup>(1)</sup> 1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the bic cleared by hardware once operation is complete. This bit can only be set (not cleared) in software one operation is complete and inactive         bit 14       WREN: Write Enable bit <sup>(1)</sup> 1 = Enables Flash program/erase operations         0 = Inhibits Flash program/erase operations       0 = Inhibits Flash program/erase operations         bit 13       WRERR: Write Sequence Error Flag bit <sup>(1)</sup> 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation selectified by NVMOP<3:0> on the next WR command         0 = Performs the program operation Select bits <sup>(1,2)</sup> If ERASE = 1:         1111 = No operation         1010 = Erase general segment         0011 = Memory page erase operation         0011 = No operation         0011 = Reserved         If ERASE = 0:         11111 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 7             |                             |                                |                             |                             |                    |                        | bit           |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       WR: Write Control bit <sup>(1)</sup> 1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the bic cleared by hardware once operation is complete. This bit can only be set (not cleared) in software once operation is complete and inactive         bit 14       WREN: Write Enable bit <sup>(1)</sup> 1 = Enables Flash program/erase operations         0 = Inhibits Flash program/erase operations       0 = Inhibits Flash program/erase operations         bit 13       WRERR: Write Sequence Error Flag bit <sup>(1)</sup> 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         0 = Depration       1101 = Erase general segment         0101 = No operation       1101 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Legend:           |                             | SO = Settab                    | le Only bit                 |                             |                    |                        |               |

| bit 15 WR: Write Control bit <sup>(1)</sup><br>1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the b<br>cleared by hardware once operation is complete. This bit can only be set (not cleared) in softwa<br>0 = Program or erase operation is complete and inactive<br>bit 14 WREN: Write Enable bit <sup>(1)</sup><br>1 = Enables Flash program/erase operations<br>0 = Inhibits Flash program/erase operations<br>bit 13 WRERR: Write Sequence Error Flag bit <sup>(1)</sup><br>1 = An improper program or erase sequence attempt or termination has occurred (bit is<br>automatically on any set attempt of the WR bit)<br>0 = The program or erase operation completed normally<br>bit 6 ERASE: Erase/Program Enable bit <sup>(1)</sup><br>1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command<br>0 = Performs the program operation specified by NVMOP<3:0> on the next WR command<br>0 = Performs the program operation specified by NVMOP<3:0> on the next WR command<br>bit 5-4 Unimplemented: Read as 'o'<br>bit 3-0 NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup><br><u>If ERASE = 1:</u><br>1111 = No operation<br>1001 = Erase general segment<br>0010 = Reserved<br>0000 = Reserved<br><u>If ERASE = 0:</u><br>1111 = No operation<br>1001 = No operation                                                                                                                                                                                                                                                               | R = Readable      | e bit                       | W = Writable                   | e bit                       | U = Unimple                 | mented bit, read   | l as '0'               |               |

| 1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the bicleared by hardware once operation is complete. This bit can only be set (not cleared) in software or erase operation is complete and inactive         0 = Program or erase operation is complete and inactive         bit 14       WREN: Write Enable bit <sup>(1)</sup> 1 = Enables Flash program/erase operations         0 = Inhibits Flash program/erase operations         0 = Inhibits Flash program/erase operations         bit 13       WRERR: Write Sequence Error Flag bit <sup>(1)</sup> 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation specified hy NVMOP<3:0> on the next WR command         0 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation Select bits <sup>(1,2)</sup> If ERASE = 1:         1111 = No operation         1101 = Erase general segment         011 = No operation         1101 = Reserved         0000 = Reserved         If ERASE = 0:         1111 = No operation         1101 = No operation         1101 = No operation         1111 = No operation         1101 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -n = Value at     | POR                         | '1' = Bit is se                | et                          | '0' = Bit is cle            | eared              | x = Bit is unkr        | iown          |

| cleared by hardware once operation is complete. This bit can only be set (not cleared) in softwa<br>0 = Program or erase operation is complete and inactive<br>bit 14 WREN: Write Enable bit <sup>(1)</sup><br>1 = Enables Flash program/erase operations<br>0 = Inhibits Flash program/erase operations<br>bit 13 WRERR: Write Sequence Error Flag bit <sup>(1)</sup><br>1 = An improper program or erase sequence attempt or termination has occurred (bit is<br>automatically on any set attempt of the WR bit)<br>0 = The program or erase operation completed normally<br>bit 12-7 Unimplemented: Read as '0'<br>bit 6 ERASE: Erase/Program Enable bit <sup>(1)</sup><br>1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command<br>0 = Performs the program operation specified by NVMOP<3:0> on the next WR command<br>0 = Performs the program operation specified by NVMOP<3:0> on the next WR command<br>bit 5-4 Unimplemented: Read as '0'<br>bit 3-0 NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup><br>If ERASE = 1:<br>1111 = No operation<br>1010 = Erase general segment<br>0011 = No operation<br>0010 = Memory page erase operation<br>0010 = Reserved<br>0000 = Reserved<br>1111 = No operation<br>1011 | bit 15            |                             |                                |                             | r orono oporati             | on The operation   | an is colf timed       | and the bit i |

| bit 14 WREN: Write Enable bit <sup>(1)</sup> 1 = Enables Flash program/erase operations 0 = Inhibits Flash program/erase operations bit 13 WRERR: Write Sequence Error Flag bit <sup>(1)</sup> 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit) 0 = The program or erase operation completed normally bit 12-7 Unimplemented: Read as '0' bit 6 ERASE: Erase/Program Enable bit <sup>(1)</sup> 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command 0 = Performs the program operation specified by NVMOP<3:0> on the next WR command 0 = Performs the program operation specified by NVMOP<3:0> on the next WR command 0 = Performs the program operation Select bits <sup>(1,2)</sup> bit 3-0 NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1: 1111 = No operation 1101 = Erase general segment 0011 = No operation 0010 = Memory page erase operation 0010 = Reserved 0000 = Reserved 0000 = Reserved 1111 = No operation 1011 = No operation 1011 = No operation 1011 = No operation 1011 = No operation 0010 = Memory word program operation 0011 = Memory word program operation 0010 = No operation 0011 = No operation 0010 = No operation 0011 = No operation 0010 = No operati                                                                                                                              |                   | cleared by                  | hardware onc                   | eoperation                  | is complete. Th             | is bit can only be |                        |               |

| 1 = Enables Flash program/erase operations         0 = Inhibits Flash program/erase operations         bit 13       WRERR: Write Sequence Error Flag bit <sup>(1)</sup> 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation completed normally         bit 12-7       Unimplemented: Read as '0'         bit 6       ERASE: Erase/Program Enable bit <sup>(1)</sup> 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         bit 5-4       Unimplemented: Read as '0'         bit 3-0       NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1:       1111 = No operation         1101 = Erase general segment       0011 = No operation         0010 = Memory page erase operation       0000 = Reserved         0000 = Reserved       If ERASE = 0:         1111 = No operation       1101 = No operation         1101 = No operation       0011 = No operation         1011 = No operation       10011 = No operation         1001 = No operation       0011 = No operation         1011 = No operation       1011 = No operation         1001 = No operation       0011 = Ne operation         0011 = Ne operatio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 14            | •                           |                                | · · · P                     |                             |                    |                        |               |

| 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation completed normally         bit 12-7       Unimplemented: Read as '0'         bit 6       ERASE: Erase/Program Enable bit <sup>(1)</sup> 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         bit 5-4       Unimplemented: Read as '0'         bit 3-0       NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1:       1111 = No operation         101 = Erase general segment       0011 = No operation         0010 = Memory page erase operation       0010 = Reserved         If ERASE = 0:       1111 = No operation         1101 = No operation       1001 = Reserved         0000 = Reserved       If ERASE = 0:         1111 = No operation       1101 = No operation         0101 = No operation       0011 = Nemory word program operation         011 = No operation       0011 = Nemory word program operation         0011 = Nemory word program operation       0011 = Nemory word program operation         0010 = No operation       0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |                             |                                |                             |                             |                    |                        |               |

| 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation completed normally         bit 12-7       Unimplemented: Read as '0'         bit 6       ERASE: Erase/Program Enable bit <sup>(1)</sup> 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         bit 5-4       Unimplemented: Read as '0'         bit 3-0       NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1:       1111 = No operation         101 = Erase general segment       0011 = Reserved         0010 = Memory page erase operation       0011 = Reserved         1111 = No operation       1101 = No operation         0010 = Reserved       If ERASE = 0:         11111 = No operation       1101 = No operation         0011 = Reserved       0000 = Reserved         1101 = No operation       1101 = No operation         1101 = No operation       1101 = No operation         1101 = No operation       1101 = No operation         0011 = Nemory word program operation       0011 = Memory word program operation         0011 = No operation       011 = No operation         0110 = No operation       011 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit 13            | WRERR: Write                | Sequence Er                    | ror Flag bit <sup>(</sup>   | 1)                          |                    |                        |               |

| bit 12-7 Unimplemented: Read as '0'<br>bit 6 ERASE: Erase/Program Enable bit <sup>(1)</sup><br>1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command<br>0 = Performs the program operation specified by NVMOP<3:0> on the next WR command<br>bit 5-4 Unimplemented: Read as '0'<br>bit 3-0 NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup><br>If ERASE = 1:<br>1111 = No operation<br>1101 = Erase general segment<br>0011 = No operation<br>0010 = Memory page erase operation<br>0010 = Reserved<br>0000 = Reserved<br>If ERASE = 0:<br>1111 = No operation<br>101 = No operation<br>101 = No operation<br>0011 = Memory word program operation<br>0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   | 1 = An improp<br>automatica | per program of ally on any set | or erase se<br>attempt of t | equence attem<br>he WR bit) |                    | on has occurre         | ed (bit is se |

| bit 6       ERASE: Erase/Program Enable bit <sup>(1)</sup> 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         bit 5-4       Unimplemented: Read as '0'         bit 3-0       NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1:       1111 = No operation         1011 = Erase general segment       0011 = Kno operation         0010 = Memory page erase operation       0001 = Reserved         0000 = Reserved       If ERASE = 0:         1111 = No operation       1101 = No operation         0010 = Memory page erase operation       0011 = Reserved         0000 = Reserved       If ERASE = 0:         1111 = No operation       1001 = No operation         1001 = No operation       0010 = No operation         0011 = No operation       0011 = No operation         0010 = No operation       0011 = No operation         0011 = No operation       0011 = No operation         0011 = No operation       0011 = No operation         0111 = No operation       0011 = No operation         0011 = No operation       0011 = No operation         0011 = No operation       0011 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | hit 10 7          |                             |                                |                             | ipieted normali             | у                  |                        |               |

| 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         bit 5-4       Unimplemented: Read as '0'         bit 3-0       NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1:       1111 = No operation         1011 = Erase general segment       0011 = No operation         0010 = Memory page erase operation       0001 = Reserved         0000 = Reserved       If ERASE = 0:         1111 = No operation       1101 = No operation         0101 = No operation       0001 = Reserved         0000 = Reserved       If ERASE = 0:         1111 = No operation       1001 = No operation         0011 = No operation       0011 = No operation         0010 = No operation       0011 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   | -                           |                                |                             |                             |                    |                        |               |

| <ul> <li>0 = Performs the program operation specified by NVMOP&lt;3:0&gt; on the next WR command</li> <li>bit 5-4 Unimplemented: Read as '0'</li> <li>bit 3-0 NVMOP&lt;3:0&gt;: NVM Operation Select bits<sup>(1,2)</sup></li> <li>If ERASE = 1:<br/>1111 = No operation<br/>1101 = Erase general segment<br/>0011 = No operation<br/>0010 = Memory page erase operation<br/>0001 = Reserved<br/>0000 = Reserved</li> <li>If ERASE = 0:<br/>1111 = No operation<br/>1101 = No operation<br/>0011 = Memory word program operation<br/>0010 = No operation</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DILO              |                             | •                              |                             |                             | <3:0> on the new   | vt WP comman           | d             |

| bit 5-4 Unimplemented: Read as '0'<br>bit 3-0 NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup><br>If ERASE = 1:<br>1111 = No operation<br>1101 = Erase general segment<br>0011 = No operation<br>0010 = Memory page erase operation<br>0001 = Reserved<br>0000 = Reserved<br>If ERASE = 0:<br>1111 = No operation<br>1101 = No operation<br>1101 = No operation<br>0011 = Memory word program operation<br>0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                   |                             |                                |                             |                             |                    |                        |               |

| bit 3-0 NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1: 1111 = No operation 1101 = Erase general segment 0011 = No operation 0010 = Memory page erase operation 0001 = Reserved 0000 = Reserved If ERASE = 0: 1111 = No operation 1101 = No operation 1101 = No operation 0011 = Memory word program operation 0010 = No operation 0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 5-4           |                             |                                |                             | ,                           |                    |                        |               |

| If ERASE = 1:         1111 = No operation         101 = Erase general segment         0011 = No operation         0010 = Memory page erase operation         0001 = Reserved         0000 = Reserved         If ERASE = 0:         1111 = No operation         1101 = No operation         0011 = Memory word program operation         0011 = Memory word program operation         0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bit 3-0           | -                           |                                |                             | ts <sup>(1,2)</sup>         |                    |                        |               |

| <pre>1101 = Erase general segment<br/>0011 = No operation<br/>0010 = Memory page erase operation<br/>0001 = Reserved<br/>0000 = Reserved<br/><u>If ERASE = 0:</u><br/>1111 = No operation<br/>1101 = No operation<br/>0011 = Memory word program operation<br/>0010 = No operation</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |                             |                                |                             |                             |                    |                        |               |

| 0011 = No operation         0010 = Memory page erase operation         0001 = Reserved         0000 = Reserved         If ERASE = 0:         1111 = No operation         1101 = No operation         0011 = Memory word program operation         0010 = No operation         0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   | •                           |                                |                             |                             |                    |                        |               |

| 0010 = Memory page erase operation<br>0001 = Reserved<br>0000 = Reserved<br><u>If ERASE = 0:</u><br>1111 = No operation<br>1101 = No operation<br>0011 = Memory word program operation<br>0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |                             |                                | ent                         |                             |                    |                        |               |

| 0001 = Reserved<br>0000 = Reserved<br><u>If ERASE = 0:</u><br>1111 = No operation<br>1101 = No operation<br>0011 = Memory word program operation<br>0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |                             |                                | oneration                   |                             |                    |                        |               |

| If ERASE = 0:<br>1111 = No operation<br>1101 = No operation<br>0011 = Memory word program operation<br>0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |                             |                                | peration                    |                             |                    |                        |               |

| <pre>1111 = No operation 1101 = No operation 0011 = Memory word program operation 0010 = No operation</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   | 0000 <b>= Reserv</b>        | red                            |                             |                             |                    |                        |               |

| 1101 = No operation<br>0011 = Memory word program operation<br>0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   |                             | vration                        |                             |                             |                    |                        |               |

| 0011 = Memory word program operation<br>0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |                             |                                |                             |                             |                    |                        |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   |                             |                                | m operation                 | I                           |                    |                        |               |

| 0001 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   | 0010 <b>= No ope</b>        | ration                         |                             |                             |                    |                        |               |