#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 6КВ (2К х 24)                                                                     |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 256 x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 6x10b                                                                         |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                    |

| Supplier Device Package    | 28-SOIC                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs102at-i-so |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

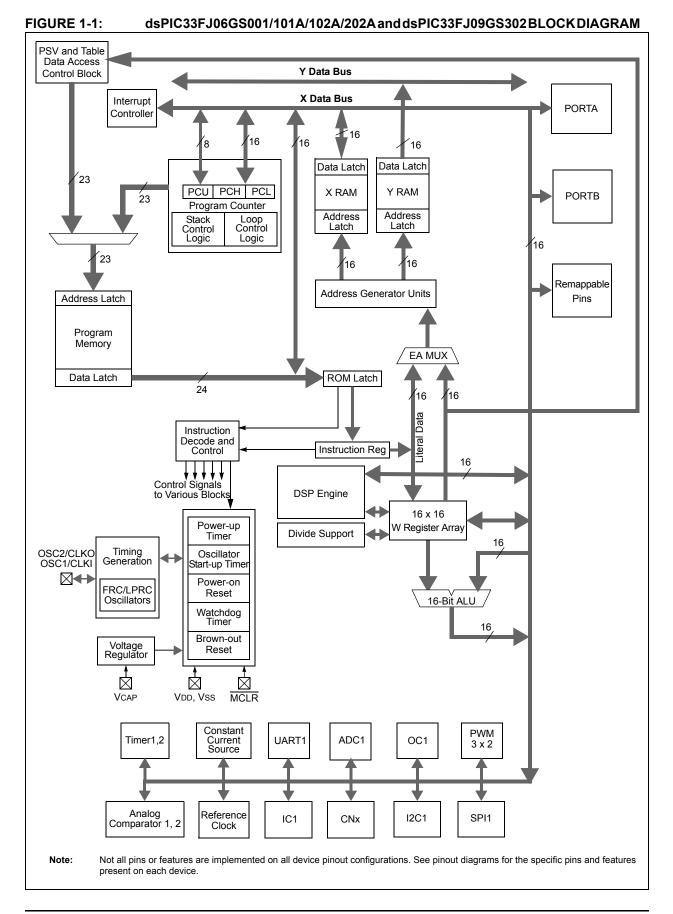

### 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS001/101A/102A/ 202A and dsPIC33FJ09GS302 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 2.** "CPU" (DS70204) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The CPU module has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for DSP. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space. The actual amount of program memory implemented varies from device to device. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

The dsPIC33FJ06GS001/101A/102A/202A and dsPIC33FJ09GS302 devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can serve as a Data, Address or Address Offset register. The sixteenth working register (W15) operates as a software Stack Pointer (SP) for interrupts and calls.

There are two classes of instruction: MCU and DSP. These two instruction classes are seamlessly integrated into a single CPU. The instruction set includes many addressing modes and is designed for optimum C compiler efficiency. For most instructions, the devices are capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing A + B = C operations to be executed in a single cycle.

A block diagram of the CPU is shown in Figure 3-1, and the programmer's model is shown in Figure 3-2.

### 3.1 Data Addressing Overview

The data space can be addressed as 32K words or 64 Kbytes and is split into two blocks, referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear data space. Certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y data space boundary is device-specific.

Overhead-free circular buffers (Modulo Addressing mode) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. Furthermore, the X AGU Circular Addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms.

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K program word boundary defined by the 8-bit Program Space Visibility Page (PSVPAG) register. The program-to-data space mapping feature lets any instruction access program space as if it were data space.

### 3.2 DSP Engine Overview

The DSP engine features a high-speed, 17-bit by 17-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bidirectional barrel shifter. The barrel shifter is capable of shifting a 40-bit value up to 16 bits, right or left, in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been designed for optimal realtime performance. The MAC instruction and other associated instructions can concurrently fetch two data operands from memory while multiplying two W registers and accumulating and optionally saturating the result in the same cycle. This instruction functionality requires that the RAM data space be split for these instructions and linear for all others. Data space partitioning is achieved in a transparent and flexible manner through dedicating certain working registers to each address space.

### TABLE 4-16: I2C1 REGISTER MAP

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7 | Bit 6 | Bit 5     | Bit 4       | Bit 3    | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|---------|--------|---------|--------|--------|--------|--------|-------|-------|-------|-----------|-------------|----------|-------|-------|-------|---------------|

| I2C1RCV     | 0200        | _       | _      |         | —      | —      | —      | —      | _     |       |       |           | Receive     | Register |       |       |       | 0000          |

| I2C1TRN     | 0202        | _       |        | _       | _      | -      | _      | _      | _     |       |       |           | Transmit    | Register |       |       |       | OOFF          |

| I2C1BRG     | 0204        | _       |        | _       | _      | -      | _      | _      |       |       |       | Baud Rate | e Generator | Register |       |       |       | 0000          |

| I2C1CON     | 0206        | I2CEN   |        | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN  | GCEN  | STREN | ACKDT     | ACKEN       | RCEN     | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT    | 0208        | ACKSTAT | TRSTAT | _       | _      | -      | BCL    | GCSTAT | ADD10 | IWCOL | I2COV | D_A       | Р           | S        | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD     | 020A        | _       |        | _       | _      | -      | _      |        |       |       |       | Address I | Register    |          |       |       |       | 0000          |

| I2C1MSK     | 020C        | _       | _      |         | —      | _      | _      |        |       |       |       | AMSK      | <9:0>       |          |       |       |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-17: UART1 REGISTER MAP FOR dsPiC33FJ06GS101A, dsPiC33FJ06GS102A, dsPiC33FJ06GS202A AND dsPiC33FJ09GS302

| SFR Name | SFR<br>Addr | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8       | Bit 7        | Bit 6   | Bit 5 | Bit 4       | Bit 3   | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|----------|-------------|----------|--------|----------|--------|--------|--------|-------|-------------|--------------|---------|-------|-------------|---------|-------|--------|-------|---------------|

| U1MODE   | 0220        | UARTEN   | —      | USIDL    | IREN   | RTSMD  | _      | UEN1  | UEN0        | WAKE         | LPBACK  | ABAUD | URXINV      | BRGH    | PDSEI | _<1:0> | STSEL | 0000          |

| U1STA    | 0222        | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT        | URXISE       | L<1:0>  | ADDEN | RIDLE       | PERR    | FERR  | OERR   | URXDA | 0110          |

| U1TXREG  | 0224        | _        | _      | -        | _      | _      | _      | -     |             |              |         | UART  | Transmit Re | egister |       |        |       | XXXX          |

| U1RXREG  | 0226        | _        | _      | -        | _      | _      | _      | -     |             |              |         | UART  | Receive Re  | egister |       |        |       | 0000          |

| U1BRG    | 0228        |          | -      |          |        | •      |        | B     | aud Rate Ge | enerator Pre | escaler |       |             |         |       |        |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

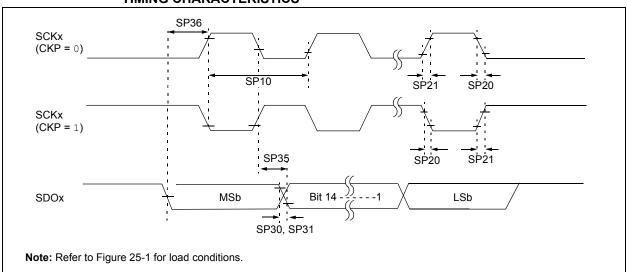

### TABLE 4-18:SPI1 REGISTER MAP FOR dsPIC33FJ06GS101A, dsPIC33FJ06GS102A, dsPIC33FJ06GS202A AND dsPIC33FJ09GS302

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8       | Bit 7       | Bit 6       | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------------|--------|--------|---------|--------|--------|--------|-----------|-------------|-------------|-------------|-------|-------|-----------|-------|--------|--------|---------------|

| SPI1STAT | 0240        | SPIEN  | _      | SPISIDL |        |        |        |           | _           |             | SPIROV      | _     | _     | _         | _     | SPITBF | SPIRBF | 0000          |

| SPI1CON1 | 0242        | _      | _      | _       | DISSCK | DISSDO | MODE16 | SMP       | CKE         | SSEN        | CKP         | MSTEN |       | SPRE<2:0> |       | PPRE   | <1:0>  | 0000          |

| SPI1CON2 | 0244        | FRMEN  | SPIFSD | FRMPOL  |        | _      | _      | _         | _           | _           | _           | _     | _     | _         | _     | FRMDLY | _      | 0000          |

| SPI1BUF  | 0248        |        |        |         |        |        |        | SPI1 Tran | smit and Re | ceive Buffe | er Register |       |       |           |       |        |        | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE 4- | 26:         | PERIPI | HERAL  | . PIN SE | LECT IN | PUT RE  | GISTER | R MAP | FOR d | sPIC33 | FJ06GS | 202A AN | ID dsP | IC33FJ0 | 9GS302 |       |       |   |

|----------|-------------|--------|--------|----------|---------|---------|--------|-------|-------|--------|--------|---------|--------|---------|--------|-------|-------|---|

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13   | Bit 12  | Bit 11  | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6  | Bit 5   | Bit 4  | Bit 3   | Bit 2  | Bit 1 | Bit 0 |   |

| RPINR0   | 0680        | —      | —      |          |         | INT1R<  | 5:0>   |       |       | —      | —      | -       | —      | —       | —      | —     | -     | Î |

| RPINR1   | 0682        | _      | _      | _        | _       | _       | —      | —     | —     | —      | _      |         |        | INT2R   | <5:0>  |       |       | Ĩ |

| RPINR2   | 0684        | _      | _      |          |         | T1CKR<  | 5:0>   |       |       | —      | _      | _       | —      | _       | _      | _     | _     | Ĩ |

| RPINR3   | 0686        | _      | _      | _        | _       | _       | —      | —     | —     | —      | _      |         |        | T2CKF   | <5:0>  |       |       | Ĩ |

| RPINR7   | 068E        | _      | _      | _        | _       | _       | _      | —     | —     | —      | _      |         |        | IC1R<   | <5:0>  |       |       | Ī |

| RPINR11  | 0696        | _      | _      | _        | _       | _       | —      | _     | —     | —      | _      |         |        | OCFAF   | <5:0>  |       |       | Ī |

| RPINR18  | 06A4        | _      | _      |          |         | U1CTSR- | <5:0>  |       |       | —      | _      |         |        | U1RXF   | <5:0>  |       |       | Ī |

| RPINR20  | 06A8        | _      | _      |          |         | SCK1R<  | 5:0>   |       |       | _      | _      |         |        | SDI1R   | <5:0>  |       |       | Ī |

| RPINR21  | 06AA        | _      | _      | _        | —       | _       | _      | —     | —     | _      |        |         |        | SS1R    | <5:0>  |       |       | Τ |

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

RPINR34 Legend:

RPINR29

RPINR30

RPINR31

RPINR32

RPINR33

06BA

06BC

06BE

06C0

06C2

06C4

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

FLT1R<5:0>

FLT3R<5:0>

FLT5R<5:0>

FLT7R<5:0>

SYNCI1R<5:0>

#### **TABLE 4-27:** PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33FJ06GS001 AND dsPIC33FJ06GS101A

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12                 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5     | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|------------------------|--------|--------|-------|-------|-------|-------|-----------|-------|-------|-------|-------|-------|---------------|

| RPOR0     | 06D0 | _      | _      |        | RP1R<5:0><br>RP3R<5:0> |        |        |       |       | _     | —     |           |       | RP0R< | <5:0> |       |       | 0000          |

| RPOR1     | 06D2 | _      | _      |        |                        |        |        |       |       | _     | _     | RP2R<5:0> |       |       |       |       |       | 0000          |

| RPOR2     | 06D4 | _      | _      |        | RP5R<5:0>              |        |        |       |       | _     | _     |           |       | RP4R  | <5:0> |       |       | 0000          |

| RPOR3     | 06D6 | _      | —      |        |                        | RP7    | R<5:0> |       |       | —     | _     | RP6R<5:0> |       |       |       |       |       | 0000          |

| RPOR16    | 06F0 | _      | _      |        | RP33R<5:0>             |        |        |       |       | —     | _     |           |       | RP32R | <5:0> |       |       | 0000          |

| RPOR17    | 06F2 | _      | _      |        | RP35R<5:0>             |        |        |       |       | _     | -     |           |       | RP34R | <5:0> |       |       | 0000          |

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

All Resets 3F00 003F 3F00 003F 003F 003F 3F3F 3F3F

003F

3F00

3F3F

3F3F

3F3F

3F3F

003F

\_

\_

FLT2R<5:0>

FLT4R<5:0>

FLT6R<5:0>

FLT8R<5:0>

SYNCI2R<5:0>

\_

| <b>REGISTER 7</b>     | -16: IEC5:      | INTERRUPT                           | ENABLE CO | ONTROL RE        | GISTER 5         |                |        |

|-----------------------|-----------------|-------------------------------------|-----------|------------------|------------------|----------------|--------|

| R/W-0                 | R/W-0           | U-0                                 | U-0       | U-0              | U-0              | U-0            | U-0    |

| PWM2IE <sup>(1)</sup> | PWM1IE          | —                                   | _         | —                | —                | —              | —      |

| bit 15                |                 |                                     |           |                  |                  |                | bit 8  |

|                       |                 |                                     |           |                  |                  |                |        |

| U-0                   | U-0             | U-0                                 | U-0       | U-0              | U-0              | U-0            | R/W-0  |

|                       |                 |                                     | —         |                  |                  | —              | JTAGIE |

| bit 7                 |                 |                                     |           |                  |                  |                | bit 0  |

|                       |                 |                                     |           |                  |                  |                |        |

| Legend:               |                 |                                     |           |                  |                  |                |        |

| R = Readable          | bit             | W = Writable                        | bit       | U = Unimpler     | mented bit, read | l as '0'       |        |

| -n = Value at F       | POR             | '1' = Bit is set                    |           | '0' = Bit is cle | eared            | x = Bit is unk | nown   |

|                       |                 |                                     | (4)       |                  |                  |                |        |

| bit 15                |                 | /M2 Interrupt E                     |           |                  |                  |                |        |

|                       |                 | request is enab<br>request is not e |           |                  |                  |                |        |

| bit 14                | •               | /M1 Interrupt E                     |           |                  |                  |                |        |

| bit 14                |                 | request is enab                     |           |                  |                  |                |        |

|                       | •               | request is not e                    |           |                  |                  |                |        |

| bit 13-1              | Unimplemen      | ted: Read as '                      | כי        |                  |                  |                |        |

| bit 0                 | JTAGIE: JTA     | G Interrupt Ena                     | ble bit   |                  |                  |                |        |

|                       | 1 = Interrupt i | request is enab                     | led       |                  |                  |                |        |

|                       | 0 = Interrupt i | request is not e                    | nabled    |                  |                  |                |        |

|                       |                 |                                     |           |                  |                  |                |        |

### REGISTER 7-16: IEC5: INTERRUPT ENABLE CONTROL REGISTER 5

**Note 1:** This bit is not implemented in dsPIC33FJ06GS001/101A devices.

| REGISTER     | R 7-26: IPC14: | INTERRUPT          |                 |                  | REGISTER 14      |                 |       |

|--------------|----------------|--------------------|-----------------|------------------|------------------|-----------------|-------|

| U-0          | U-0            | U-0                | U-0             | U-0              | U-0              | U-0             | U-0   |

|              | —              | —                  | —               | —                |                  |                 | —     |

| bit 15       |                |                    |                 |                  |                  |                 | bit 8 |

|              |                |                    |                 |                  |                  |                 |       |

| U-0          | R/W-1          | R/W-0              | R/W-0           | U-0              | U-0              | U-0             | U-0   |

| —            |                | PSEMIP<2:0>        |                 | —                | _                |                 | —     |

| bit 7        |                |                    |                 |                  |                  |                 | bit 0 |

|              |                |                    |                 |                  |                  |                 |       |

| Legend:      |                |                    |                 |                  |                  |                 |       |

| R = Readat   | ole bit        | W = Writable       | bit             | U = Unimpler     | mented bit, read | as '0'          |       |

| -n = Value a | at POR         | '1' = Bit is set   |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|              |                |                    |                 |                  |                  |                 |       |

| bit 15-7     | Unimplemen     | ted: Read as '     | 0'              |                  |                  |                 |       |

| bit 6-4      | PSEMIP<2:0     | PWM Special        | al Event Match  | n Interrupt Prio | rity bits        |                 |       |

|              | 111 = Interrup | ot is Priority 7 ( | highest priorit | y interrupt)     |                  |                 |       |

|              | •              |                    |                 |                  |                  |                 |       |

|              | •              |                    |                 |                  |                  |                 |       |

|              | •              |                    |                 |                  |                  |                 |       |

- 001 = Interrupt is Priority 1

- 000 = Interrupt source is disabled

bit 3-0 Unimplemented: Read as '0'

### REGISTER 7-27: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| U-0     | U-0   | U-0                       | U-0   | U-0 | U-0 | U-0 | U-0   |

|---------|-------|---------------------------|-------|-----|-----|-----|-------|

| —       | —     | —                         | _     | —   | —   | —   | —     |

| bit 15  |       |                           |       |     |     |     | bit 8 |

|         |       |                           |       |     |     |     |       |

| U-0     | R/W-1 | R/W-0                     | R/W-0 | U-0 | U-0 | U-0 | U-0   |

| —       |       | U1EIP<2:0> <sup>(1)</sup> |       | —   | —   | —   | —     |

| bit 7   |       |                           |       |     |     |     | bit 0 |

|         |       |                           |       |     |     |     |       |

| Legend: |       |                           |       |     |     |     |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                     |

|----------|----------------------------------------------------------------|

| bit 6-4  | U1EIP<2:0>: UART1 Error Interrupt Priority bits <sup>(1)</sup> |

|          | 111 = Interrupt is Priority 7 (highest priority interrupt)     |

|          | •                                                              |

|          | •                                                              |

|          | •                                                              |

|          | 001 = Interrupt is Priority 1                                  |

|          | 000 = Interrupt source is disabled                             |

| bit 3-0  | Unimplemented: Read as '0'                                     |

|          |                                                                |

**Note 1:** These bits are not implemented in the dsPIC33FJ06GS001 device.

| U-0           | R/W-1                 | R/W-0                                              | R/W-0      | U-0              | R/W-1            | R/W-0           | R/W-0 |

|---------------|-----------------------|----------------------------------------------------|------------|------------------|------------------|-----------------|-------|

| _             |                       | ADCP1IP<2:0>                                       | >          | —                |                  | ADCP0IP<2:0>    |       |

| bit 15        |                       |                                                    |            |                  | •                |                 | bit 8 |

| U-0           | U-0                   | U-0                                                | U-0        | U-0              | U-0              | U-0             | U-0   |

|               |                       |                                                    | _          | _                | _                |                 | _     |

| bit 7         |                       |                                                    |            |                  |                  |                 | bit 0 |

| Legend:       |                       |                                                    |            |                  |                  |                 |       |

| R = Readabl   | le bit                | W = Writable                                       | bit        | U = Unimpler     | mented bit, read | 1 as '0'        |       |

| -n = Value at | t POR                 | '1' = Bit is set                                   |            | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|               | •<br>•<br>001 = Inter | rupt is Priority 7 (<br>rupt is Priority 1         |            | ty interrupt)    |                  |                 |       |

| bit 11        |                       | rupt source is dis<br>ented: Read as '             |            |                  |                  |                 |       |

| bit 10-8      | ADCP0IP<              | <b>2:0&gt;:</b> ADC Pair 0<br>rupt is Priority 7 ( | Conversion |                  | Priority bits    |                 |       |

|               |                       | rupt is Priority 1<br>rupt source is dis           | abled      |                  |                  |                 |       |

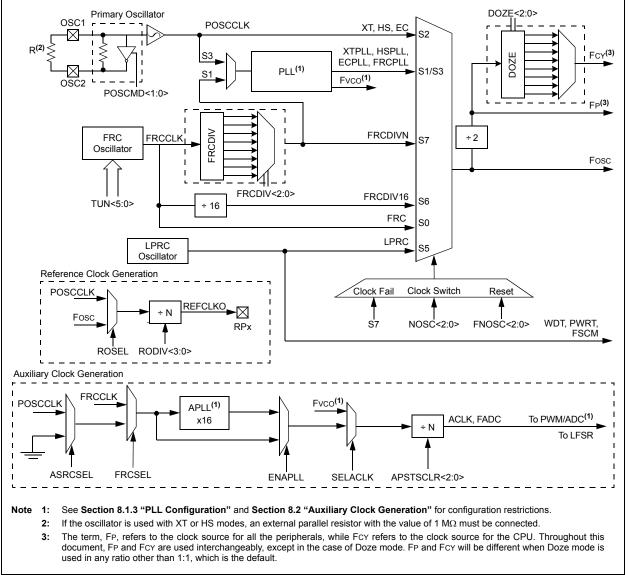

### 8.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS001/101A/102A/ 202A and dsPIC33FJ09GS302 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 42. "Oscillator (Part IV)" (DS70307) in the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The oscillator system provides:

- External and internal oscillator options as clock sources

- An on-chip Phase Lock Loop (PLL) to scale the internal operating frequency to the required system clock frequency

- An internal FRC oscillator that can also be used with the PLL, thereby allowing full-speed operation without any external clock generation hardware

- · Clock switching between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- An Oscillator Control register (OSCCON)

- Nonvolatile Configuration bits for main oscillator selection

- An auxiliary PLL for ADC and PWM

A simplified diagram of the oscillator system is shown in Figure 8-1.

### FIGURE 8-1: OSCILLATOR SYSTEM DIAGRAM

| U-0                                | U-0                                                                                                                                     | U-0                                                       | U-0   | U-0                                | U-0                    | U-0            | R/W-0   |  |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------|------------------------------------|------------------------|----------------|---------|--|

| _                                  | _                                                                                                                                       | _                                                         | _     | —                                  | —                      | —              | PLLDIV8 |  |

| bit 15                             |                                                                                                                                         |                                                           |       |                                    |                        |                | bit 8   |  |

|                                    |                                                                                                                                         |                                                           |       |                                    |                        |                |         |  |

| R/W-0                              | R/W-0                                                                                                                                   | R/W-1                                                     | R/W-1 | R/W-0                              | R/W-0                  | R/W-0          | R/W-0   |  |

|                                    |                                                                                                                                         |                                                           | PLLDI | V<7:0>                             |                        |                |         |  |

| bit 7                              |                                                                                                                                         |                                                           |       |                                    |                        |                | bit 0   |  |

|                                    |                                                                                                                                         |                                                           |       |                                    |                        |                |         |  |

| Legend:                            |                                                                                                                                         |                                                           |       |                                    |                        |                |         |  |

| R = Readab                         | ole bit                                                                                                                                 | W = Writable                                              | bit   | U = Unimplemented bit, read as '0' |                        |                |         |  |

| -n = Value at POR '1' = Bit is set |                                                                                                                                         |                                                           |       | '0' = Bit is cleared x = Bit i     |                        |                |         |  |

| -n = Value a                       | It POR                                                                                                                                  | '1' = Bit is set                                          |       | '0' = Bit is cle                   | ared                   | x = Bit is unk | nown    |  |

|                                    |                                                                                                                                         |                                                           |       | '0' = Bit is cle                   | ared                   | x = Bit is unk | nown    |  |

| -n = Value a<br>bit 15-9           |                                                                                                                                         | <ul><li>'1' = Bit is set</li><li>ted: Read as '</li></ul> |       | '0' = Bit is cle                   | ared                   | x = Bit is unk | nown    |  |

|                                    | Unimplemen                                                                                                                              | ted: Read as '                                            | 0'    |                                    | ared<br>as 'M', PLL mu |                | nown    |  |

| bit 15-9                           | Unimplemen                                                                                                                              | ted: Read as '<br>•: PLL Feedba                           | 0'    |                                    |                        |                | nown    |  |

| bit 15-9                           | Unimplemen<br>PLLDIV<8:0>                                                                                                               | ted: Read as '<br>•: PLL Feedba                           | 0'    |                                    |                        |                | nown    |  |

| bit 15-9                           | Unimplemen<br>PLLDIV<8:0>                                                                                                               | ted: Read as '<br>•: PLL Feedba                           | 0'    |                                    |                        |                | nown    |  |

| bit 15-9                           | Unimplemen<br>PLLDIV<8:0>                                                                                                               | ted: Read as '<br>•: PLL Feedba                           | 0'    |                                    |                        |                | nown    |  |

| bit 15-9                           | Unimplemen<br>PLLDIV<8:0>                                                                                                               | ted: Read as '<br>•: PLL Feedbac<br>= 513                 | 0'    |                                    |                        |                | nown    |  |

| bit 15-9                           | Unimplemen<br>PLLDIV<8:0><br>111111111 =<br>•<br>•                                                                                      | ted: Read as '<br>•: PLL Feedbac<br>= 513                 | 0'    |                                    |                        |                | nown    |  |

| bit 15-9                           | Unimplemen<br>PLLDIV<8:0><br>111111111 =<br>•<br>•                                                                                      | ted: Read as '<br>•: PLL Feedbac<br>= 513                 | 0'    |                                    |                        |                | nown    |  |

| bit 15-9                           | Unimplemen<br>PLLDIV<8:0><br>111111111 =<br>•<br>•                                                                                      | ted: Read as '<br>•: PLL Feedbac<br>= 513                 | 0'    |                                    |                        |                | nown    |  |

| bit 15-9                           | Unimplemen<br>PLLDIV<8:0><br>111111111 =<br>•<br>•                                                                                      | ted: Read as f<br>PLL Feedbac<br>513                      | 0'    |                                    |                        |                | nown    |  |

| bit 15-9                           | Unimplemen<br>PLLDIV<8:0><br>111111111 =<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ted: Read as f<br>PLL Feedbac<br>513<br>50 (default)      | 0'    |                                    |                        |                | nown    |  |

Note 1: This register is reset only on a Power-on Reset (POR).

| REGISTER      | REGISTER 9-5: PMD6: PERIPHERAL MODULE DISABLE CONTROL REGISTER 6                                          |                                  |                |                                         |     |                       |        |  |

|---------------|-----------------------------------------------------------------------------------------------------------|----------------------------------|----------------|-----------------------------------------|-----|-----------------------|--------|--|

| U-0           | U-0                                                                                                       | U-0                              | U-0            | R/W-0                                   | U-0 | R/W-0                 | R/W-0  |  |

| _             | _                                                                                                         | —                                |                | PWM4MD <sup>(1)</sup>                   | —   | PWM2MD <sup>(2)</sup> | PWM1MD |  |

| bit 15        |                                                                                                           |                                  |                |                                         |     |                       | bit 8  |  |

| U-0           | U-0                                                                                                       | U-0                              | U-0            | U-0                                     | U-0 | U-0                   | U-0    |  |

|               |                                                                                                           |                                  |                | <u> </u>                                |     |                       |        |  |

| bit 7         |                                                                                                           |                                  |                |                                         |     |                       | bit 0  |  |

| Legend:       |                                                                                                           |                                  |                |                                         |     |                       |        |  |

| R = Readable  | e bit                                                                                                     | W = Writable                     | bit            | U = Unimplemented bit, read as '0'      |     |                       |        |  |

| -n = Value at | POR                                                                                                       | '1' = Bit is set                 |                | '0' = Bit is cleared x = Bit is unknown |     |                       | own    |  |

| bit 15-12     | Unimplomon                                                                                                | ted: Read as '                   | ۰,             |                                         |     |                       |        |  |

| bit 11        | •                                                                                                         | NM Generator                     |                | able bit(1)                             |     |                       |        |  |

|               | 1 = PWM Ger                                                                                               | nerator 4 modu<br>nerator 4 modu | le is disabled |                                         |     |                       |        |  |

| bit 10        | Unimplement                                                                                               | ted: Read as '                   | )'             |                                         |     |                       |        |  |

| bit 9         | <b>PWM2MD:</b> PWM Generator 2 Module Disable bit <sup>(2)</sup>                                          |                                  |                |                                         |     |                       |        |  |

|               | <ul> <li>1 = PWM Generator 2 module is disabled</li> <li>0 = PWM Generator 2 module is enabled</li> </ul> |                                  |                |                                         |     |                       |        |  |

| bit 8         | PWM1MD: PWM Generator 1 Module Disable bit                                                                |                                  |                |                                         |     |                       |        |  |

|               | 1 = PWM Generator 1 module is disabled<br>0 = PWM Generator 1 module is enabled                           |                                  |                |                                         |     |                       |        |  |

| bit 7-0       | Unimplemented: Read as '0'                                                                                |                                  |                |                                         |     |                       |        |  |

**Note 1:** This bit is not implemented in dsPIC33FJ06GS102A/202A devices.

**2:** This bit is not implemented in dsPIC33FJ06GS001/101A devices.

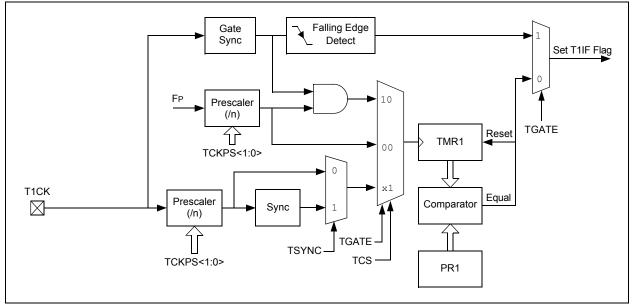

### 11.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS001/101A/102A/ 202A and dsPIC33FJ09GS302 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 11. "Timers"** (DS70205) in the *"dsPIC33F/PIC24H Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer, which can serve as a time counter for the Real-Time Clock (RTC) or operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be operated from the low-power 32 kHz crystal oscillator available on the device

- Can be operated in Asynchronous Counter mode from an external clock source

- The Timer1 External Clock Input (T1CK) can optionally be synchronized to the internal device clock and the clock synchronization is performed after the prescaler

The unique features of Timer1 allow it to be used for Real-Time Clock applications. A block diagram of Timer1 is shown in Figure 11-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- · Gated Timer mode

- · Synchronous Counter mode

- · Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FcY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer1 modes are determined by the following bits:

- Timer1 Clock Source Control bit: TCS (T1CON<1>)

- Timer1 Synchronization Control bit: TSYNC (T1CON<2>)

- Timer1 Gate Control bit: TGATE (T1CON<6>)

The Timer1 control bit settings for different operating modes are given in the Table 11-1.

| TABLE 11-1: | TIMER1 MODI | E SETTINGS |

|-------------|-------------|------------|

|-------------|-------------|------------|

| Mode                    | TCS | TGATE | TSYNC |

|-------------------------|-----|-------|-------|

| Timer1                  | 0   | 0     | х     |

| Gated Timer1            | 0   | 1     | х     |

| Synchronous<br>Counter  | 1   | х     | 1     |

| Asynchronous<br>Counter | 1   | х     | 0     |

### FIGURE 11-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

| U-0                                | U-0   | U-0   | U-0              | U-0         | U-0             | R/W-0    | R/W-0 |

|------------------------------------|-------|-------|------------------|-------------|-----------------|----------|-------|

| _                                  | —     | —     | _                | —           |                 | AMSK     | <9:8> |

| bit 15                             | ·     |       |                  | ·           |                 |          | bit 8 |

|                                    |       |       |                  |             |                 |          |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0            | R/W-0       | R/W-0           | R/W-0    | R/W-0 |

|                                    |       |       | AMS              | K<7:0>      |                 |          |       |

| bit 7                              |       |       |                  |             |                 |          | bit 0 |

|                                    |       |       |                  |             |                 |          |       |

| Legend:                            |       |       |                  |             |                 |          |       |

| R = Readable bit W = Writable bit  |       |       | bit              | U = Unimple | mented bit, rea | d as '0' |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cle | eared       | x = Bit is unkn | iown     |       |

bit 15-10 Unimplemented: Read as '0'

bit 9-0 AMSK<9:0>: Mask for Address bit x Select bits

1 = Enables masking for bit x of incoming message address; bit match not required in this position

0 = Disables masking for bit x; bit match required in this position

### 18.3 UART Registers

### REGISTER 18-1: U1MODE: UART1 MODE REGISTER

| R/W-0                   | U-0 | R/W-0                | R/W-0                 | R/W-0                | U-0 | R/W-0 | R/W-0               |

|-------------------------|-----|----------------------|-----------------------|----------------------|-----|-------|---------------------|

| UARTEN <sup>(1,3)</sup> | —   | USIDL <sup>(3)</sup> | IREN <sup>(2,3)</sup> | RTSMD <sup>(3)</sup> | —   | UEN<  | 1:0> <sup>(3)</sup> |

| bit 15                  |     |                      |                       |                      |     |       | bit 8               |

| R/W-0, HC           | R/W-0                 | R/W-0, HC            | R/W-0                 | R/W-0               | R/W-0  | R/W-0                | R/W-0                |

|---------------------|-----------------------|----------------------|-----------------------|---------------------|--------|----------------------|----------------------|

| WAKE <sup>(3)</sup> | LPBACK <sup>(3)</sup> | ABAUD <sup>(3)</sup> | URXINV <sup>(3)</sup> | BRGH <sup>(3)</sup> | PDSEL< | :1:0> <sup>(3)</sup> | STSEL <sup>(3)</sup> |

| bit 7               |                       |                      |                       |                     |        |                      | bit 0                |

| Legend:           | HC = Hardware Clearable bit                         |                      |                    |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |

| bit 15  | <b>UARTEN:</b> UART1 Enable bit <sup>(1,3)</sup>                                                                                                                                                                                                                                                                                                                                                          |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = UART1 is enabled; all UART1 pins are controlled by UART1, as defined by UEN&lt;1:0&gt;</li> <li>0 = UART1 is disabled; all UART1 pins are controlled by port latches; UART1 power consumption is minimal</li> </ul>                                                                                                                                                                          |

| bit 14  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                |

| bit 13  | USIDL: Stop in Idle Mode bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                               |

|         | <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul>                                                                                                                                                                                                                                                                   |

| bit 12  | IREN: IrDA <sup>®</sup> Encoder and Decoder Enable bit <sup>(2,3)</sup>                                                                                                                                                                                                                                                                                                                                   |

|         | 1 = $IrDA^{\ensuremath{\mathbb{R}}}$ encoder and decoder are enabled<br>0 = $IrDA^{\ensuremath{\mathbb{R}}}$ encoder and decoder are disabled                                                                                                                                                                                                                                                             |

| bit 11  | <b>RTSMD:</b> Mode Selection for U1RTS Pin bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                             |

|         | $1 = \overline{\text{U1RTS}} \text{ pin is in Simplex mode}$<br>0 = U1RTS pin is in Flow Control mode                                                                                                                                                                                                                                                                                                     |

| bit 10  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                |

| bit 9-8 | UEN<1:0>: UART1 Pin Enable bits <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>11 = U1TX, U1RX and BCLK pins are enabled and used; U1CTS pin is controlled by port latches</li> <li>10 = U1TX, U1RX, U1CTS and U1RTS pins are enabled and used</li> <li>01 = U1TX, U1RX and U1RTS pins are enabled and used; U1CTS pin is controlled by port latches</li> <li>00 = U1TX and U1RX pins are enabled and used; U1CTS and U1RTS/BCLK pins are controlled by port latches</li> </ul> |

| bit 7   | WAKE: Wake-up on Start bit Detect During Sleep Mode Enable bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                             |

|         | <ul> <li>1 = UART1 will continue to sample the U1RX pin; interrupt is generated on falling edge; bit is cleared<br/>in hardware on following rising edge</li> <li>0 = No wake-up is enabled</li> </ul>                                                                                                                                                                                                    |

| bit 6   | LPBACK: UART1 Loopback Mode Select bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                     |

|         | 1 = Enable Loopback mode                                                                                                                                                                                                                                                                                                                                                                                  |

|         | 0 = Loopback mode is disabled                                                                                                                                                                                                                                                                                                                                                                             |

| bit 5   | ABAUD: Auto-Baud Enable bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                |

|         | <ul> <li>1 = Enable baud rate measurement on the next character – requires reception of a Sync field (0x55)<br/>before other data; cleared in hardware upon completion</li> </ul>                                                                                                                                                                                                                         |

|         | 0 = Baud rate measurement is disabled or completed                                                                                                                                                                                                                                                                                                                                                        |

| Note 1: | Refer to <b>Section 17. "UART"</b> (DS70188) in the <i>"dsPIC33F/PIC24H Family Reference Manual"</i> for information on enabling the UART module for receive or transmit operation.                                                                                                                                                                                                                       |

| 2:      | This feature is only available for the 16x BRG mode (BRGH = $0$ ).                                                                                                                                                                                                                                                                                                                                        |

**3:** This bit is not available in the dsPIC33FJ06GS001 device.

### 19.0 HIGH-SPEED 10-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS001/101A/102A/ 202A and dsPIC33FJ09GS302 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 44. "High-Speed 10-Bit ADC" (DS70321) in the "dsPIC33F/ PIC24H Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJ06GS001/101A/102A/202A and dsPIC33FJ09GS302 family of devices provides high-speed successive approximation, Analog-to-Digital conversions to support applications such as AC-to-DC and DC-to-DC Power Converters.

### **19.1 Features Overview**

The ADC module comprises the following features:

- 10-bit resolution

- Unipolar inputs

- One Successive Approximation Register (SAR)

- · Up to eight external input channels

- · Up to two internal analog inputs

- Dedicated result register for each analog input

- ±1 LSB accuracy at 3.3V

- Single supply operation

- 2 Msps conversion rate at 3.3V

- Low-power CMOS technology

### **19.2 Module Description**

This ADC module is designed for applications that require low latency between the request for conversion and the resultant output data. Typical applications include:

- AC/DC Power Supplies

- DC/DC Converters

- Power Factor Correction (PFC)

This ADC works with the high-speed PWM module in power control applications that require high-frequency control loops. This small conversion delay reduces the "phase lag" between measurement and control system response. Up to three inputs may be sampled at a time (two inputs from the dedicated Sample-and-Hold circuits and one from the shared Sample-and-Hold circuit). If multiple inputs request conversion, the ADC will convert them in a sequential manner, starting with the lowest order input.

This ADC design provides each pair of analog inputs (AN1, AN0), (AN3, AN2),..., the ability to specify its own trigger source out of a maximum of sixteen different trigger sources. This capability allows this ADC to sample and convert analog inputs that are associated with PWM generators operating on independent time bases.

The user application typically requires synchronization between analog data sampling and PWM output to the application circuit. The very high-speed operation of this ADC module allows "data on demand".

In addition, several hardware features have been added to the peripheral interface to improve real-time performance in a typical DSP-based application:

- Result alignment options

- · Automated sampling

- External conversion start control

- Two internal inputs to monitor INTREF and EXTREF input signals (not available in dsPIC33FJ06GS101A/102A devices)

Block diagrams of the ADC module are shown in Figure 19-1 through Figure 19-5.

### 19.3 Module Functionality

The high-speed, 10-bit ADC module is designed to support power conversion applications when used with the high-speed PWM module. The ADC has one SAR and only one conversion can be processed at a time, yielding a conversion rate of 2 Msps or the equivalent of one 10-bit conversion, in half a microsecond ( $0.5 \ \mu s$ ).

The ADC module supports up to eight external analog inputs and two internal analog inputs. To monitor reference voltage, two internal inputs, AN12 and AN13, are connected to the EXTREF and INTREF voltages, respectively.

Note: The dsPIC33FJ06GS101A/102A devices do not have the internal connection to EXTREF.

The analog reference voltage is defined as the device supply voltage (AVDD/AVSS).

| R/W-0                | U-0                                                                                                                                   | R/W-0                                                                                                   | R/W-0                 | R/W-0                  | R/W-0                 | R/W-0                  | R/W-0                |  |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------|------------------------|-----------------------|------------------------|----------------------|--|--|--|

| CMPON <sup>(1)</sup> | _                                                                                                                                     | CMPSIDL <sup>(1)</sup>                                                                                  | HYSSE                 | L<1:0> <sup>(1)</sup>  | FLTREN <sup>(1)</sup> | FCLKSEL <sup>(1)</sup> | DACOE <sup>(1)</sup> |  |  |  |

| bit 15               |                                                                                                                                       |                                                                                                         |                       |                        |                       |                        | bit                  |  |  |  |

|                      |                                                                                                                                       |                                                                                                         |                       |                        |                       |                        |                      |  |  |  |

| R/W-0                | R/W-0                                                                                                                                 | R/W-0                                                                                                   | R/W-0                 | R/W-0                  | R/W-0                 | R/W-0                  | R/W-0                |  |  |  |

| INSEL                | <1:0> <sup>(1)</sup>                                                                                                                  | EXTREF <sup>(1)</sup>                                                                                   | HYSPOL <sup>(1)</sup> | CMPSTAT <sup>(1)</sup> | HGAIN <sup>(1)</sup>  | CMPPOL <sup>(1)</sup>  | RANGE <sup>(1)</sup> |  |  |  |

| bit 7                |                                                                                                                                       |                                                                                                         |                       |                        |                       |                        | bit                  |  |  |  |

| Legend:              |                                                                                                                                       |                                                                                                         |                       |                        |                       |                        |                      |  |  |  |

| R = Readable         | bit                                                                                                                                   | W = Writable                                                                                            | bit                   | U = Unimplen           | nented bit, read      | l as '0'               |                      |  |  |  |

| -n = Value at I      | POR                                                                                                                                   | '1' = Bit is set                                                                                        |                       | '0' = Bit is clea      | ared                  | x = Bit is unkn        | own                  |  |  |  |

| hit 1E               |                                                                                                                                       | mparator Opera                                                                                          | ting Mada bit         | (1)                    |                       |                        |                      |  |  |  |

| bit 15               |                                                                                                                                       | itor module is e                                                                                        | -                     |                        |                       |                        |                      |  |  |  |

|                      | •                                                                                                                                     | tor module is d                                                                                         |                       | es power cons          | umption)              |                        |                      |  |  |  |

| bit 14               | Unimplemer                                                                                                                            | nted: Read as '                                                                                         | 0'                    |                        |                       |                        |                      |  |  |  |

| bit 13               | CMPSIDL: S                                                                                                                            | top in Idle Mode                                                                                        | e bit <sup>(1)</sup>  |                        |                       |                        |                      |  |  |  |

|                      | 1 = Discontin                                                                                                                         | ues module op                                                                                           | eration when          | device enters lo       | dle mode.             |                        |                      |  |  |  |

|                      | <ul><li>1 = Discontinues module operation when device enters Idle mode.</li><li>0 = Continues module operation in Idle mode</li></ul> |                                                                                                         |                       |                        |                       |                        |                      |  |  |  |

|                      |                                                                                                                                       | If a device has multiple comparators, any CMPSIDL bit that is set to '1' disables all comparators while |                       |                        |                       |                        |                      |  |  |  |

|                      | in Idle mode.                                                                                                                         |                                                                                                         |                       | (4)                    |                       |                        |                      |  |  |  |

| bit 12-11            |                                                                                                                                       | 0>: Comparator                                                                                          | Hysteresis S          | elect bits(")          |                       |                        |                      |  |  |  |

|                      | 11 = 45 mV ł                                                                                                                          | •                                                                                                       |                       |                        |                       |                        |                      |  |  |  |

|                      | 10 = 30 mV h<br>01 = 15 mV h                                                                                                          |                                                                                                         |                       |                        |                       |                        |                      |  |  |  |

|                      |                                                                                                                                       | eresis is selecte                                                                                       | ed                    |                        |                       |                        |                      |  |  |  |

| bit 10               | -                                                                                                                                     | gital Filter Enabl                                                                                      |                       |                        |                       |                        |                      |  |  |  |

|                      |                                                                                                                                       | ter is enabled                                                                                          |                       |                        |                       |                        |                      |  |  |  |

|                      | •                                                                                                                                     | ter is disabled                                                                                         |                       |                        |                       |                        |                      |  |  |  |

| bit 9                | FCLKSEL: D                                                                                                                            | Digital Filter and                                                                                      | Pulse Stretch         | er Clock Selec         | t bit <sup>(1)</sup>  |                        |                      |  |  |  |

|                      | 1 = Digital filt                                                                                                                      | ter and pulse st                                                                                        | retcher operat        | e with the PWN         | /I clock              |                        |                      |  |  |  |

|                      | 0 = Digital filt                                                                                                                      | ter and pulse st                                                                                        | retcher operat        | e with the syste       | em clock              |                        |                      |  |  |  |

| bit 8                | DACOE: DA                                                                                                                             | C Output Enabl                                                                                          | e <sup>(1)</sup>      |                        |                       |                        |                      |  |  |  |

|                      |                                                                                                                                       | log voltage is o                                                                                        |                       |                        | _                     |                        |                      |  |  |  |

| hit 7 G              |                                                                                                                                       | llog voltage is n                                                                                       |                       |                        | 1                     |                        |                      |  |  |  |

| bit 7-6              |                                                                                                                                       | : Input Source S                                                                                        |                       | iparator bits ??       |                       |                        |                      |  |  |  |