### Welcome to E-XFL.COM

# What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 6KB (2K x 24)                                                                     |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 256 x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 6x10b                                                                         |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                    |

| Supplier Device Package    | 28-SSOP                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs102at-i-ss |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

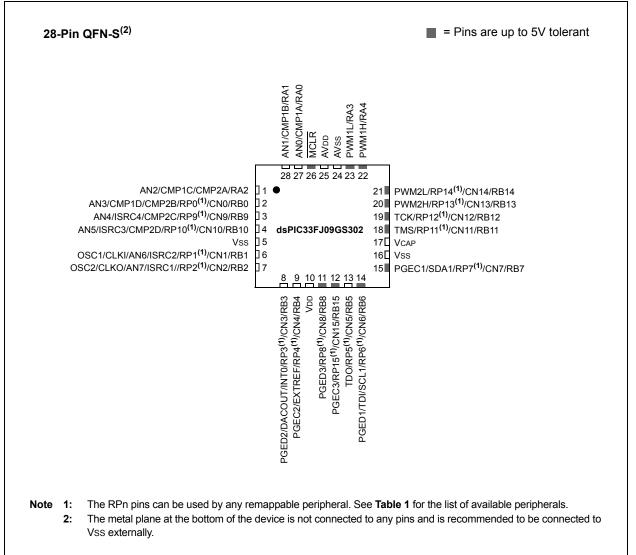

# **Pin Diagrams (Continued)**

# **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPlC33F/PlC24H Family Reference Manual"*. These documents should be considered the primary reference for the operation of a particular module or device feature.

| Note: | To ace               | cess th | listed b  | elow, |      |  |  |  |

|-------|----------------------|---------|-----------|-------|------|--|--|--|

|       | visit                | the     | Microchip | web   | site |  |  |  |

|       | (www.microchip.com). |         |           |       |      |  |  |  |

- Section 1. "Introduction" (DS70197)

- Section 2. "CPU" (DS70204)

- Section 3. "Data Memory" (DS70202)

- Section 4. "Program Memory" (DS70203)

- Section 5. "Flash Programming" (DS70191)

- Section 8. "Reset" (DS70192)

- Section 9. "Watchdog Timer (WDT) and Power-Saving Modes" (DS70196)

- Section 10. "I/O Ports" (DS70193)

- Section 11. "Timers" (DS70205)

- Section 12. "Input Capture" (DS70198)

- Section 13. "Output Compare" (DS70209)

- Section 17. "UART" (DS70188)

- Section 18. "Serial Peripheral Interface (SPI)" (DS70206)

- Section 19. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70195)

- Section 24. "Programming and Diagnostics" (DS70207)

- Section 25. "Device Configuration" (DS70194)

- Section 41. "Interrupts (Part IV)" (DS70300)

- Section 42. "Oscillator (Part IV)" (DS70307)

- Section 43. "High-Speed PWM" (DS70323)

- Section 44. "High-Speed 10-Bit ADC" (DS70321)

- Section 45. "High-Speed Analog Comparator" (DS70296)

NOTES:

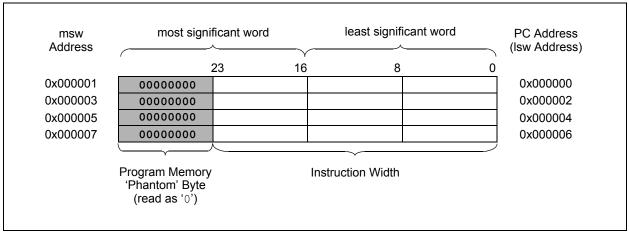

# 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (see Figure 4-2).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during the code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

# 4.1.2 INTERRUPT AND TRAP VECTORS

All devices reserve the addresses between 0x00000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at 0x000000, with the actual address for the start of code at 0x000002.

The devices also have two interrupt vector tables, located from 0x000004 to 0x0000FF and 0x000100 to 0x0001FF. These vector tables allow each of the device interrupt sources to be handled by separate Interrupt Service Routines (ISRs). A more detailed discussion of the interrupt vector tables is provided in **Section 7.1** "Interrupt Vector Table".

# FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

# 4.2.5 X AND Y DATA SPACES

The core has two data spaces, X and Y. These data spaces can be considered either separate (for some DSP instructions), or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms, such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X data space is used by all instructions and supports all addressing modes. X data space has separate read and write data buses. The X read data bus is the read data path for all instructions that view data space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y data space is used in concert with the X data space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y data spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X data space.

All data memory writes, included in DSP instructions, view data space as combined X and Y address space. The boundary between the X and Y data spaces is device-dependent and is not user-programmable.

All Effective Addresses are 16 bits wide and point to bytes within the data space. Therefore, the data space address range is 64 Kbytes, or 32K words, though the implemented memory locations vary by device.

# TABLE 4-28:PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33FJ06GS102A, dsPIC33FJ06GS202A AND<br/>dsPIC33FJ09GS302

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12     | Bit 11           | Bit 10  | Bit 9 | Bit 8 | Bit 7 | Bit 6     | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|------------|------------------|---------|-------|-------|-------|-----------|-------|-------|-------|-------|-------|-------|---------------|

| RPOR0     | 06D0 | _      | _      |        | RP1R<5:0>  |                  |         |       |       | -     | RP0R<5:0> |       |       |       |       |       | 0000  |               |

| RPOR1     | 06D2 | _      | _      |        | RP3R<5:0>  |                  |         |       |       | _     | _         |       |       | RP2R  | <5:0> |       |       | 0000          |

| RPOR2     | 06D4 | _      | _      |        | RP5R<5:0>  |                  |         |       | _     | _     | RP4R<5:0> |       |       |       |       | 0000  |       |               |

| RPOR3     | 06D6 | _      | _      |        | RP7R<5:0>  |                  |         |       | _     | _     | RP6R<5:0> |       |       |       |       | 0000  |       |               |

| RPOR4     | 06D8 | _      | _      |        |            | RP9              | R<5:0>  |       |       | _     | _         |       |       | RP8R  | <5:0> |       |       | 0000          |

| RPOR5     | 06DA | —      | _      |        |            | RP1 <sup>2</sup> | 1R<5:0> |       |       | —     | _         |       |       | RP10R | <5:0> |       |       | 0000          |

| RPOR6     | 06DC | _      | _      |        |            | RP1              | 3R<5:0> |       |       | _     | _         |       |       | RP12R | <5:0> |       |       | 0000          |

| RPOR7     | 06DE | _      | _      |        | RP15R<5:0> |                  |         |       | _     | _     |           |       | RP14R | <5:0> |       |       | 0000  |               |

| RPOR16    | 06F0 | _      | _      |        | RP33<5:0>  |                  |         | _     | _     |       |           | RP32  | <5:0> |       |       | 0000  |       |               |

| RPOR17    | 06F2 |        | _      |        |            | RP3              | 5<5:0>  |       |       |       | -         |       |       | RP34  | <5:0> |       |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

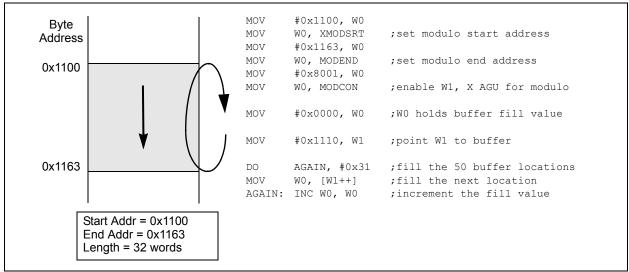

# 4.5 Modulo Addressing

Modulo Addressing mode is a method used to provide an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either data or program space (since the data pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into program space) and Y data spaces. Modulo Addressing can operate on any W register pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction as there are certain restrictions on the buffer start address (for incrementing buffers), or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

# 4.5.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

| Note: | Υ            | space      | Modulo      | Addressing   | EA   |

|-------|--------------|------------|-------------|--------------|------|

|       | calculations |            | assume      | word-sized   | data |

|       | (LS          | Sb of ever | y EA is alw | /ays clear). |      |

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

# 4.5.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that will operate with Modulo Addressing:

- If XWM = 15, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 15, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X data space when XWM is set to any value other than '15' and the XMODEN bit is set at MODCON<15>.

The Y Address Space Pointer W register (YWM) to which Modulo Addressing is to be applied is stored in MODCON<7:4>. Modulo Addressing is enabled for Y data space when YWM is set to any value other than '15' and the YMODEN bit is set at MODCON<14>.

# FIGURE 4-6: MODULO ADDRESSING OPERATION EXAMPLE

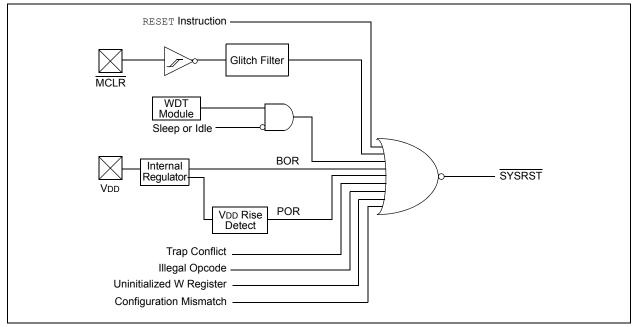

# 6.0 RESETS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS001/101A/102A/ 202A and dsPIC33FJ09GS302 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 8.** "**Reset**" (DS70192) in the "*dsPIC33F/PIC24H Family Reference Manual*", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- · POR: Power-on Reset

- · BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: Software RESET Instruction

- WDTO: Watchdog Timer Reset

- · CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- · IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

# FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state, and some are unaffected.

Note: Refer to the specific peripheral section or Section 3.0 "CPU" of this data sheet for register Reset states.

All types of device Reset sets a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits (except for the POR (RCON<0> bit) that are set. The user application can set or clear any bit, at any time, during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

| <b>REGISTER 7-7</b> | 7: IFS3: | INTERRUPT I      | FLAG STA                                        | TUS REGIST                              | ER 3 |        |       |

|---------------------|----------|------------------|-------------------------------------------------|-----------------------------------------|------|--------|-------|

| U-0                 | U-0      | U-0              | U-0                                             | U-0                                     | U-0  | R/W-0  | U-0   |

| —                   | _        | —                | _                                               | —                                       | _    | PSEMIF |       |

| bit 15              |          |                  |                                                 | ·                                       |      | •      | bit 8 |

|                     |          |                  |                                                 |                                         |      |        |       |

| U-0                 | U-0      | U-0              | U-0                                             | U-0                                     | U-0  | U-0    | U-0   |

| —                   |          | —                | _                                               | —                                       | _    | —      | —     |

| bit 7               |          | •                |                                                 |                                         |      | •      | bit 0 |

|                     |          |                  |                                                 |                                         |      |        |       |

| Legend:             |          |                  |                                                 |                                         |      |        |       |

| R = Readable b      | it       | W = Writable I   | /ritable bit U = Unimplemented bit, read as '0' |                                         |      |        |       |

| -n = Value at PC    | )R       | '1' = Bit is set |                                                 | '0' = Bit is cleared x = Bit is unknown |      |        | iown  |

| bit 15-10 | Unimplemented: Read as '0'                                |

|-----------|-----------------------------------------------------------|

| bit 9     | PSEMIF: PWM Special Event Match Interrupt Flag Status bit |

|           | 1 = Interrupt request has occurred                        |

|           | 0 = Interrupt request has not occurred                    |

| bit 8-0   | Unimplemented: Read as '0'                                |

# REGISTER 7-8: IFS4: INTERRUPT FLAG STATUS REGISTER 4

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | _   | _   | _   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0                | U-0   |

|-------|-----|-----|-----|-----|-----|----------------------|-------|

| —     | —   | —   | _   | _   | —   | U1EIF <sup>(1)</sup> | —     |

| bit 7 |     |     |     |     |     |                      | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-2 | Unimplemented: Read as '0'                                  |

|----------|-------------------------------------------------------------|

| bit 1    | U1EIF: UART1 Error Interrupt Flag Status bit <sup>(1)</sup> |

|          | <ol> <li>I = Interrupt request has occurred</li> </ol>      |

|          | 0 = Interrupt request has not occurred                      |

| bit 0    | Unimplemented: Read as '0'                                  |

**Note 1:** This bit is not implemented in the dsPIC33FJ06GS001 device.

| REGISTER     | REGISTER 7-26: IPC14: INTERRUPT PRIORITY CONTROL REGISTER 14 |                  |                |                  |                  |                 |       |  |  |  |  |

|--------------|--------------------------------------------------------------|------------------|----------------|------------------|------------------|-----------------|-------|--|--|--|--|

| U-0          | U-0                                                          | U-0              | U-0            | U-0              | U-0              | U-0             | U-0   |  |  |  |  |

|              | —                                                            | —                | —              | —                |                  |                 | —     |  |  |  |  |

| bit 15       |                                                              |                  |                |                  |                  |                 | bit 8 |  |  |  |  |

|              |                                                              |                  |                |                  |                  |                 |       |  |  |  |  |

| U-0          | R/W-1                                                        | R/W-0            | R/W-0          | U-0              | U-0              | U-0             | U-0   |  |  |  |  |

| —            |                                                              | PSEMIP<2:0>      |                | —                | _                |                 | —     |  |  |  |  |

| bit 7        |                                                              |                  |                |                  |                  |                 | bit 0 |  |  |  |  |

|              |                                                              |                  |                |                  |                  |                 |       |  |  |  |  |

| Legend:      |                                                              |                  |                |                  |                  |                 |       |  |  |  |  |

| R = Readat   | ole bit                                                      | W = Writable     | bit            | U = Unimpler     | mented bit, read | as '0'          |       |  |  |  |  |

| -n = Value a | at POR                                                       | '1' = Bit is set |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |  |  |  |

|              |                                                              |                  |                |                  |                  |                 |       |  |  |  |  |

| bit 15-7     | Unimplemen                                                   | ted: Read as '   | 0'             |                  |                  |                 |       |  |  |  |  |

| bit 6-4      | PSEMIP<2:0                                                   | PWM Special      | al Event Match | n Interrupt Prio | rity bits        |                 |       |  |  |  |  |

|              | 111 = Interrupt is Priority 7 (highest priority interrupt)   |                  |                |                  |                  |                 |       |  |  |  |  |

|              | •                                                            |                  |                |                  |                  |                 |       |  |  |  |  |

|              | •                                                            |                  |                |                  |                  |                 |       |  |  |  |  |

|              | •                                                            |                  |                |                  |                  |                 |       |  |  |  |  |

- 001 = Interrupt is Priority 1

- 000 = Interrupt source is disabled

bit 3-0 Unimplemented: Read as '0'

# REGISTER 7-27: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| U-0     | U-0   | U-0                       | U-0   | U-0 | U-0 | U-0 | U-0   |

|---------|-------|---------------------------|-------|-----|-----|-----|-------|

| —       | —     | —                         | _     | —   | —   | —   | —     |

| bit 15  |       |                           |       |     |     |     | bit 8 |

|         |       |                           |       |     |     |     |       |

| U-0     | R/W-1 | R/W-0                     | R/W-0 | U-0 | U-0 | U-0 | U-0   |

| —       |       | U1EIP<2:0> <sup>(1)</sup> |       | —   | —   | —   | —     |

| bit 7   |       |                           |       |     |     |     | bit 0 |

|         |       |                           |       |     |     |     |       |

| Legend: |       |                           |       |     |     |     |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                     |

|----------|----------------------------------------------------------------|

| bit 6-4  | U1EIP<2:0>: UART1 Error Interrupt Priority bits <sup>(1)</sup> |

|          | 111 = Interrupt is Priority 7 (highest priority interrupt)     |

|          | •                                                              |

|          | •                                                              |

|          | •                                                              |

|          | 001 = Interrupt is Priority 1                                  |

|          | 000 = Interrupt source is disabled                             |

| bit 3-0  | Unimplemented: Read as '0'                                     |

|          |                                                                |

**Note 1:** These bits are not implemented in the dsPIC33FJ06GS001 device.

| U-0           | R/W-1                                                               | R/W-0                                            | R/W-0 | U-0              | R/W-1            | R/W-0           | R/W-0 |  |  |  |

|---------------|---------------------------------------------------------------------|--------------------------------------------------|-------|------------------|------------------|-----------------|-------|--|--|--|

| _             |                                                                     | PWM2IP <sup>(1)</sup>                            |       |                  |                  | PWM1IP<2:0>     |       |  |  |  |

| bit 15        |                                                                     |                                                  |       |                  |                  |                 | bit 8 |  |  |  |

|               |                                                                     |                                                  |       |                  |                  |                 |       |  |  |  |

| U-0           | U-0                                                                 | U-0                                              | U-0   | U-0              | U-0              | U-0             | U-0   |  |  |  |

|               | _                                                                   | —                                                | —     | —                | —                | _               | — —   |  |  |  |

| bit 7         |                                                                     |                                                  |       |                  |                  |                 | bit ( |  |  |  |

| Legend:       |                                                                     |                                                  |       |                  |                  |                 |       |  |  |  |

| R = Readabl   | le bit                                                              | W = Writable                                     | bit   | U = Unimplen     | nented bit, read | l as '0'        |       |  |  |  |

| -n = Value at | t POR                                                               | '1' = Bit is set                                 |       | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |  |  |

|               |                                                                     |                                                  |       |                  |                  |                 |       |  |  |  |

| bit 15        | Unimplemer                                                          | nted: Read as '                                  | כי    |                  |                  |                 |       |  |  |  |

| bit 14-12     | PWM2IP<2:0>: PWM2 Interrupt Priority bits <sup>(1)</sup>            |                                                  |       |                  |                  |                 |       |  |  |  |

|               | 111 = Interrupt is Priority 7 (highest priority)                    |                                                  |       |                  |                  |                 |       |  |  |  |

|               | •                                                                   |                                                  |       |                  |                  |                 |       |  |  |  |

|               | •                                                                   |                                                  |       |                  |                  |                 |       |  |  |  |

|               | •                                                                   |                                                  |       |                  |                  |                 |       |  |  |  |

|               | 001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled |                                                  |       |                  |                  |                 |       |  |  |  |

| bit 11        | Unimplemer                                                          | nted: Read as '                                  | כ'    |                  |                  |                 |       |  |  |  |

| bit 10-8      | PWM1IP<2:0                                                          | . PWM1IP<2:0>: PWM1 Interrupt Priority bits      |       |                  |                  |                 |       |  |  |  |

|               | 111 = Interru                                                       | 111 = Interrupt is Priority 7 (highest priority) |       |                  |                  |                 |       |  |  |  |

|               | •                                                                   |                                                  |       |                  |                  |                 |       |  |  |  |

|               | •                                                                   |                                                  |       |                  |                  |                 |       |  |  |  |

|               | •                                                                   |                                                  |       |                  |                  |                 |       |  |  |  |

|               |                                                                     | pt is Priority 1                                 |       |                  |                  |                 |       |  |  |  |

|               | 000 = Interru                                                       | pt source is dis                                 | abled |                  |                  |                 |       |  |  |  |

| bit 7-0       |                                                                     | nted: Read as '                                  |       |                  |                  |                 |       |  |  |  |

**Note 1:** These bits are not implemented in dsPIC33FJ06GS001/101A devices.

| U-0          | U-0                         | U-0                        | U-0          | U-0                                     | U-0              | U-0          | U-0      |  |  |  |

|--------------|-----------------------------|----------------------------|--------------|-----------------------------------------|------------------|--------------|----------|--|--|--|

|              |                             |                            | _            | _                                       |                  | —            |          |  |  |  |

| bit 15       |                             |                            |              |                                         |                  |              | bit 8    |  |  |  |

| U-0          | U-0                         | R/W-1                      | R/W-1        | R/W-1                                   | R/W-1            | R/W-1        | R/W-1    |  |  |  |

|              |                             |                            |              |                                         |                  |              |          |  |  |  |

| bit 7        |                             |                            |              |                                         |                  |              | bit 0    |  |  |  |

| <b>.</b> .   |                             |                            |              |                                         |                  |              |          |  |  |  |

| Legend:      |                             |                            |              |                                         |                  |              |          |  |  |  |

| R = Readab   | ole bit                     | W = Writable               | bit          | -                                       | mented bit, read | d as '0'     |          |  |  |  |

| -n = Value a | at POR                      | '1' = Bit is set           |              | '0' = Bit is cleared x = Bit is unknown |                  |              | nown     |  |  |  |

|              | l lucius a lo un ou         | ntad. Daad as (            | <u>.</u>     |                                         |                  |              |          |  |  |  |

| bit 15-6     | •                           | nted: Read as '            |              |                                         |                  |              | <b>`</b> |  |  |  |

| bit 5-0      |                             | >: Assign Outpu            | it Compare A | (OCFA) to the                           | Corresponding    | RPn Pin bits | )        |  |  |  |

|              |                             | 111111 = Input tied to Vss |              |                                         |                  |              |          |  |  |  |

|              | 100011 = Input tied to RP35 |                            |              |                                         |                  |              |          |  |  |  |

|              | 100010 = Input tied to RP34 |                            |              |                                         |                  |              |          |  |  |  |

|              | 100001 = Input tied to RP33 |                            |              |                                         |                  |              |          |  |  |  |

|              | 100000 <b>= In</b>          | put tied to RP32           | 2            |                                         |                  |              |          |  |  |  |

|              | •                           | •                          |              |                                         |                  |              |          |  |  |  |

|              | •                           |                            |              |                                         |                  |              |          |  |  |  |

|              | •                           |                            |              |                                         |                  |              |          |  |  |  |

|              | 00000 <b>= Inp</b>          | ut tied to RP0             |              |                                         |                  |              |          |  |  |  |

|              |                             |                            |              |                                         |                  |              |          |  |  |  |

# REGISTER 10-6: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

**Note 1:** These bits are not implemented in the dsPIC33FJ06GS001 device.

| R/W-0         | R/W-0                                                                           | R/W-0            | U-0              | U-0                         | U-0              | U-0              | U-0            |  |  |

|---------------|---------------------------------------------------------------------------------|------------------|------------------|-----------------------------|------------------|------------------|----------------|--|--|

| FRMEN         | SPIFSD                                                                          | FRMPOL           | —                | —                           | —                | —                | —              |  |  |

| bit 15        |                                                                                 |                  |                  |                             |                  |                  | bit 8          |  |  |

|               |                                                                                 |                  |                  |                             |                  |                  |                |  |  |

| U-0           | U-0                                                                             | U-0              | U-0              | U-0                         | U-0              | R/W-0            | U-0            |  |  |

|               |                                                                                 |                  |                  |                             |                  | FRMDLY           | _              |  |  |

| bit 7         |                                                                                 |                  |                  |                             |                  |                  | bit C          |  |  |

|               |                                                                                 |                  |                  |                             |                  |                  |                |  |  |

| Legend:       |                                                                                 |                  |                  |                             |                  |                  |                |  |  |

| R = Readable  | e bit                                                                           | W = Writable     | bit              | U = Unimpler                | nented bit, read | l as '0'         |                |  |  |

| -n = Value at | POR                                                                             | '1' = Bit is set |                  | '0' = Bit is cleared x = Bi |                  | x = Bit is unkno | 3it is unknown |  |  |

|               |                                                                                 |                  |                  |                             |                  |                  |                |  |  |

| bit 15        | FRMEN: Fran                                                                     | ned SPIx Supp    | ort bit          |                             |                  |                  |                |  |  |

|               | 1 = Framed SPIx support enabled (SSx pin used as Frame Sync pulse input/output) |                  |                  |                             |                  |                  |                |  |  |

|               |                                                                                 | Plx support dis  |                  |                             |                  |                  |                |  |  |

| bit 14        |                                                                                 | me Sync Pulse    |                  | ntrol bit                   |                  |                  |                |  |  |

|               | 1 = Frame Sync pulse input (slave)<br>0 = Frame Sync pulse output (master)      |                  |                  |                             |                  |                  |                |  |  |

| bit 13        | ,                                                                               | ame Sync Puls    | ( )              |                             |                  |                  |                |  |  |

| DIL 13        |                                                                                 | inc pulse is act | •                |                             |                  |                  |                |  |  |

|               |                                                                                 | nc pulse is act  | 0                |                             |                  |                  |                |  |  |

| bit 12-2      |                                                                                 | ted: Read as '   |                  |                             |                  |                  |                |  |  |

| oit 1         | FRMDLY: Fra                                                                     | ame Sync Pulse   | e Edge Select    | t bit                       |                  |                  |                |  |  |

|               | 1 = Frame Sync pulse coincides with first bit clock                             |                  |                  |                             |                  |                  |                |  |  |

|               | 0 = Frame Sy                                                                    | nc pulse prece   | des first bit cl | lock                        |                  |                  |                |  |  |

| bit 0         | Unimplemen                                                                      | ted: This bit m  | ust not be set   | t to '1' by the us          | ser application  |                  |                |  |  |

|               |                                                                                 |                  |                  |                             |                  |                  |                |  |  |

# REGISTER 16-3: SPIxCON2: SPIx CONTROL REGISTER 2

# 18.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS001/101A/102A/ 202A and dsPIC33FJ09GS302 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 17. "UART" (DS70188) in the "dsPIC33F/PIC24H Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

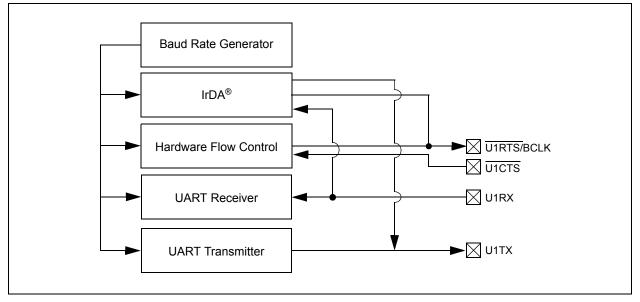

The Universal Asynchronous Receiver Transmitter (UART) module is a serial I/O module. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the U1CTS and U1RTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

| Note: | The dsPIC33FJ06GS001 device does not |

|-------|--------------------------------------|

|       | have a UART module.                  |

The primary features of the UART module are:

- Full-duplex, 8-bit or 9-bit data transmission through the U1TX and U1RX pins

- Even, Odd or No Parity options (for 8-bit data)

- One or two Stop bits

- Hardware flow control option with U1CTS and U1RTS pins

- Fully integrated Baud Rate Generator (BRG) with 16-bit prescaler

- Baud rates ranging from 10 Mbps to 38 bps at 40 MIPS

- 4-deep First-In First-Out (FIFO) transmit data buffer

- · 4-deep FIFO receive data buffer

- · Parity, framing and buffer overrun error detection

- Support for 9-bit mode with address detect (9th bit = 1)

- · Transmit and Receive interrupts

- Separate interrupt for all UART error conditions

- · Loopback mode for diagnostic support

- · Support for Sync and Break characters

- Support for automatic baud rate detection

- IrDA encoder and decoder logic

- 16x baud clock output for IrDA<sup>®</sup> support

A simplified block diagram of the UART module is shown in Figure 18-1. The UART module consists of these key hardware elements:

- BRG

- · Asynchronous transmitter

- · Asynchronous receiver

# FIGURE 18-1: UART SIMPLIFIED BLOCK DIAGRAM

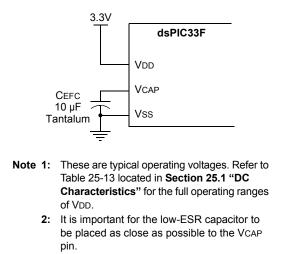

# 22.2 On-Chip Voltage Regulator

The devices power their core digital logic at a nominal 2.5V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. When the regulator is enabled, a low-ESR (less than 5 ohms) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (Figure 22-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 25-13, located in **Section 25.1 "DC Characteristics"**.

**Note:** It is important for the low-ESR capacitor to be placed as close as possible to the VCAP pin.

On a POR, it takes approximately 20 µs for the on-chip voltage regulator to generate an output voltage. During this time, designated as TSTARTUP, code execution is disabled. TSTARTUP is applied every time the device resumes operation after any power-down.

# FIGURE 22-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR<sup>(1,2,3)</sup>

**3:** Typical VCAP pin voltage = 2.5V when  $VDD \ge VDDMIN$ .

# 22.3 Brown-out Reset (BOR)

The Brown-out Reset (BOR) module is based on an internal voltage reference circuit. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse which resets the device. The BOR selects the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).

If an oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until the OST expires. If the PLL is used, the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the PWRT time-out (TPWRT) is applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of, TFSCM = 100, is applied. The total delay in this case is TFSCM.

The BOR status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle modes and resets the device should VDD fall below the BOR threshold voltage.

| TABL               | ABLE 23-2: INSTRUCTION SET OVERVIEW (CONTINUED) |        |                 |                                       |               |                |                          |  |

|--------------------|-------------------------------------------------|--------|-----------------|---------------------------------------|---------------|----------------|--------------------------|--|

| Base<br>Instr<br># | Assembly<br>Mnemonic                            |        | Assembly Syntax | Description                           | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |  |

| 66                 | RRNC                                            | RRNC   | f               | f = Rotate Right (No Carry) f         | 1             | 1              | N,Z                      |  |

|                    |                                                 | RRNC   | f,WREG          | WREG = Rotate Right (No Carry) f      | 1             | 1              | N,Z                      |  |

|                    |                                                 | RRNC   | Ws,Wd           | Wd = Rotate Right (No Carry) Ws       | 1             | 1              | N,Z                      |  |

| 67                 | SAC                                             | SAC    | Acc,#Slit4,Wdo  | Store Accumulator                     | 1             | 1              | None                     |  |

|                    |                                                 | SAC.R  | Acc,#Slit4,Wdo  | Store Rounded Accumulator             | 1             | 1              | None                     |  |

| 68                 | SE                                              | SE     | Ws,Wnd          | Wnd = Sign-Extended Ws                | 1             | 1              | C,N,Z                    |  |

| 69                 | SETM                                            | SETM   | f               | f = 0xFFFF                            | 1             | 1              | None                     |  |

|                    |                                                 | SETM   | WREG            | WREG = 0xFFFF                         | 1             | 1              | None                     |  |

|                    |                                                 | SETM   | Ws              | Ws = 0xFFFF                           | 1             | 1              | None                     |  |

| 70                 | SFTAC                                           | SFTAC  | Acc,Wn          | Arithmetic Shift Accumulator by (Wn)  | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |  |

|                    |                                                 | SFTAC  | Acc,#Slit6      | Arithmetic Shift Accumulator by Slit6 | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |  |

| 71                 | SL                                              | SL     | f               | f = Left Shift f                      | 1             | 1              | C,N,OV,Z                 |  |

|                    |                                                 | SL     | f,WREG          | WREG = Left Shift f                   | 1             | 1              | C,N,OV,Z                 |  |

|                    |                                                 | SL     | Ws,Wd           | Wd = Left Shift Ws                    | 1             | 1              | C,N,OV,Z                 |  |

|                    |                                                 | SL     | Wb,Wns,Wnd      | Wnd = Left Shift Wb by Wns            | 1             | 1              | N,Z                      |  |

|                    |                                                 | SL     | Wb,#lit5,Wnd    | Wnd = Left Shift Wb by lit5           | 1             | 1              | N,Z                      |  |

| 72                 | SUB                                             | SUB    | Acc             | Subtract Accumulators                 | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |  |

|                    |                                                 | SUB    | f               | f = f – WREG                          | 1             | 1              | C,DC,N,OV,Z              |  |

|                    |                                                 | SUB    | f,WREG          | WREG = f – WREG                       | 1             | 1              | C,DC,N,OV,Z              |  |

|                    |                                                 | SUB    | #lit10,Wn       | Wn = Wn - Iit10                       | 1             | 1              | C,DC,N,OV,Z              |  |

|                    |                                                 | SUB    | Wb,Ws,Wd        | Wd = Wb – Ws                          | 1             | 1              | C,DC,N,OV,Z              |  |

|                    |                                                 | SUB    | Wb,#lit5,Wd     | Wd = Wb – lit5                        | 1             | 1              | C,DC,N,OV,Z              |  |

| 73                 | SUBB                                            | SUBB   | f               | $f = f - WREG - (\overline{C})$       | 1             | 1              | C,DC,N,OV,Z              |  |

|                    |                                                 | SUBB   | f,WREG          | WREG = $f - WREG - (\overline{C})$    | 1             | 1              | C,DC,N,OV,Z              |  |

|                    |                                                 | SUBB   | #lit10,Wn       | $Wn = Wn - lit10 - (\overline{C})$    | 1             | 1              | C,DC,N,OV,Z              |  |

|                    |                                                 | SUBB   | Wb,Ws,Wd        | $Wd = Wb - Ws - (\overline{C})$       | 1             | 1              | C,DC,N,OV,Z              |  |

|                    |                                                 | SUBB   | Wb,#lit5,Wd     | $Wd = Wb - lit5 - (\overline{C})$     | 1             | 1              | C,DC,N,OV,Z              |  |

| 74                 | SUBR                                            | SUBR   | f               | f = WREG – f                          | 1             | 1              | C,DC,N,OV,Z              |  |

|                    |                                                 | SUBR   | f,WREG          | WREG = WREG – f                       | 1             | 1              | C,DC,N,OV,Z              |  |

|                    |                                                 | SUBR   | Wb,Ws,Wd        | Wd = Ws – Wb                          | 1             | 1              | C,DC,N,OV,Z              |  |

|                    |                                                 | SUBR   | Wb,#lit5,Wd     | Wd = lit5 – Wb                        | 1             | 1              | C,DC,N,OV,Z              |  |

| 75                 | SUBBR                                           | SUBBR  | f               | $f = WREG - f - (\overline{C})$       | 1             | 1              | C,DC,N,OV,Z              |  |

|                    |                                                 | SUBBR  | f,WREG          | WREG = WREG – f – $(\overline{C})$    | 1             | 1              | C,DC,N,OV,Z              |  |

|                    |                                                 | SUBBR  | Wb,Ws,Wd        | $Wd = Ws - Wb - (\overline{C})$       | 1             | 1              | C,DC,N,OV,Z              |  |

|                    |                                                 | SUBBR  | Wb,#lit5,Wd     | $Wd = lit5 - Wb - (\overline{C})$     | 1             | 1              | C,DC,N,OV,Z              |  |

| 76                 | SWAP                                            | SWAP.b | Wn              | Wn = Nibble Swap Wn                   | 1             | 1              | None                     |  |

| 10                 | OWIT                                            | SWAP   | Wn              | Wn = Byte Swap Wn                     | 1             | 1              | None                     |  |

| 77                 | TBLRDH                                          | TBLRDH | Ws,Wd           | Read Prog<23:16> to Wd<7:0>           | 1             | 2              | None                     |  |

| 78                 | TBLRDL                                          | TBLRDL | Ws,Wd           | Read Prog<15:0> to Wd                 | 1             | 2              | None                     |  |

| 79                 | TBLWTH                                          | TBLWTH | Ws,Wd           | Write Ws<7:0> to Prog<23:16>          | 1             | 2              | None                     |  |

| 80                 | TBLWTL                                          | TBLWTL | Ws,Wd           | Write Ws to Prog<15:0>                | 1             | 2              | None                     |  |

| 81                 | ULNK                                            | ULNK   |                 | Unlink Frame Pointer                  | 1             | 1              | None                     |  |

| 82                 | XOR                                             | XOR    | f               | f = f .XOR. WREG                      | 1             | 1              | N,Z                      |  |

|                    |                                                 | XOR    | f,WREG          | WREG = f .XOR. WREG                   | 1             | 1              | N,Z                      |  |

|                    |                                                 | XOR    | #lit10,Wn       | Wd = lit10 .XOR. Wd                   | 1             | 1              | N,Z                      |  |

|                    |                                                 | XOR    | Wb,Ws,Wd        | Wd = Wb .XOR. Ws                      | 1             | 1              | N,Z                      |  |

|                    |                                                 | XOR    | Wb,#lit5,Wd     | Wd = Wb .XOR. lit5                    | 1             | 1              | N,Z                      |  |

| 83                 | ZE                                              | ZE     | Ws,Wnd          | Wnd = Zero-Extend Ws                  | 1             | 1              | C,Z,N                    |  |

# TABLE 23-2: INSTRUCTION SET OVERVIEW (CONTINUED)

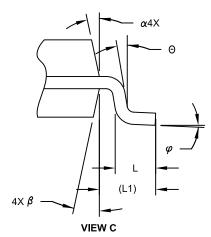

# 18-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS     |           |          |      |

|--------------------------|-----------------|-----------|----------|------|

| Dimension Lin            | nits            | MIN       | NOM      | MAX  |

| Number of Pins           | N               |           | 18       |      |

| Pitch                    | е               |           | 1.27 BSC |      |

| Overall Height           | A               | -         | -        | 2.65 |

| Molded Package Thickness | A2              | 2.05      | -        | -    |

| Standoff §               | A1              | 0.10      | -        | 0.30 |

| Overall Width            | E 10.30 BSC     |           |          |      |

| Molded Package Width     | Ith E1 7.50 BSC |           |          |      |

| Overall Length           | D               | 11.55 BSC |          |      |

| Chamfer (Optional)       | h               | 0.25      | -        | 0.75 |

| Foot Length              | L               | 0.40      | -        | 1.27 |

| Footprint                | L1              |           | 1.40 REF |      |

| Lead Angle               | Θ               | 0°        | -        | -    |

| Foot Angle               | $\varphi$       | 0°        | -        | 8°   |

| Lead Thickness           | С               | 0.20      | -        | 0.33 |

| Lead Width               | b               | 0.31      | -        | 0.51 |

| Mold Draft Angle Top     | α               | 5°        | -        | 15°  |

| Mold Draft Angle Bottom  | β               | 5°        | -        | 15°  |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-051C Sheet 2 of 2

# 28-Lead Plastic Quad Flat, No Lead Package (MM) - 6x6x0.9mm Body [QFN-S] With 0.40 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units     |          |          | S    |

|-------------------------|-----------|----------|----------|------|

| Dimensi                 | on Limits | MIN      | NOM      | MAX  |

| Number of Pins          | N         |          | 28       |      |

| Pitch                   | е         |          | 0.65 BSC |      |

| Overall Height          | A         | 0.80     | 0.90     | 1.00 |

| Standoff                | A1        | 0.00     | 0.02     | 0.05 |

| Terminal Thickness      | A3        | 0.20 REF |          |      |

| Overall Width           | E         | 6.00 BSC |          |      |

| Exposed Pad Width       | E2        | 3.65     | 3.70     | 4.70 |

| Overall Length          | D         | 6.00 BSC |          |      |

| Exposed Pad Length      | D2        | 3.65     | 3.70     | 4.70 |

| Terminal Width          | b         | 0.23     | 0.30     | 0.35 |

| Terminal Length         | L         | 0.30     | 0.40     | 0.50 |

| Terminal-to-Exposed Pad | K         | 0.20     | -        | -    |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-124C Sheet 2 of 2