Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 6КВ (2К х 24)                                                                     |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 256 x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 6x10b                                                                         |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 36-VFTLA Exposed Pad                                                              |

| Supplier Device Package    | 36-VTLA (5x5)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs102at-i-tl |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

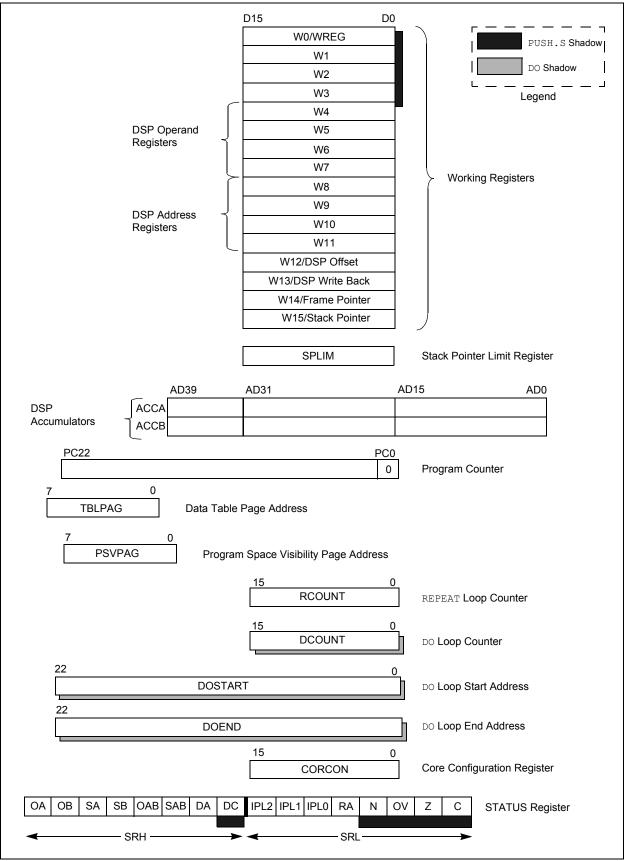

#### 3.3 Special MCU Features

A 17-bit by 17-bit single-cycle multiplier is shared by both the MCU ALU and DSP engine. The multiplier can perform signed, unsigned and mixed-sign multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication not only allows you to perform mixed-sign multiplication, it also achieves accurate results for special operations, such as (-1.0) x (-1.0). The 16/16 and 32/16 divide operations are supported, both fractional and integer. All divide instructions are iterative operations. They must be executed within a REPEAT loop, resulting in a total execution time of 19 instruction cycles. The divide operation can be interrupted during any of those 19 cycles without loss of data.

A 40-bit barrel shifter is used to perform up to a 16-bit left or right shift in a single cycle. The barrel shifter can be used by both MCU and DSP instructions.

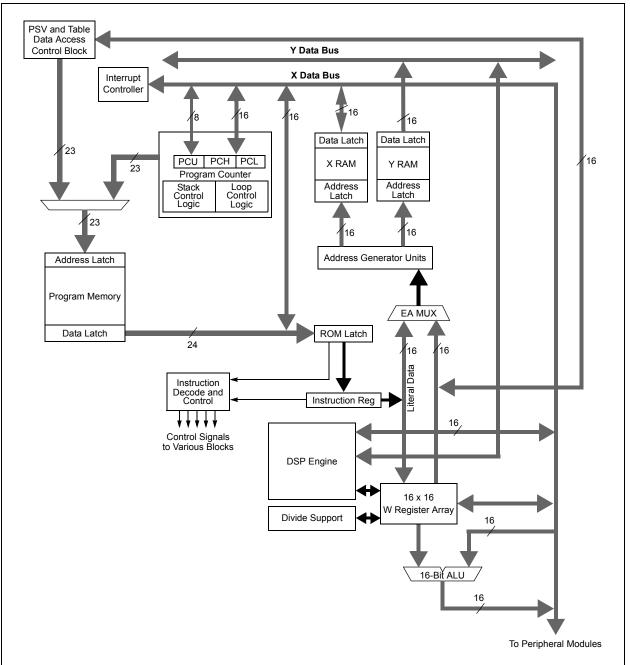

#### FIGURE 3-1: CPU CORE BLOCK DIAGRAM

#### TABLE 4-1: CPU CORE REGISTER MAP (CONTINUED)

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13                              | Bit 12   | Bit 11 | Bit 10 | Bit 9   | Bit 8 | Bit 7 | Bit 6 | Bit 5   | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|--------|--------|-------------------------------------|----------|--------|--------|---------|-------|-------|-------|---------|--------|-------|-------|-------|-------|---------------|

| CORCON   | 0044        | —      | _      | _                                   | US       | EDT    |        | DL<2:0> |       | SATA  | SATB  | SATDW   | ACCSAT | IPL3  | PSV   | RND   | IF    | 0020          |

| MODCON   | 0046        | XMODEN | YMODEN | _                                   | _        |        | BWM    | <3:0>   |       |       | ΥW    | /M<3:0> |        |       | XWM   | <3:0> |       | 0000          |

| XMODSRT  | 0048        |        |        |                                     | XS<15:1> |        |        |         |       |       |       |         |        | 0     | XXXX  |       |       |               |

| XMODEND  | 004A        |        |        |                                     | XE<15:1> |        |        |         |       |       |       |         | 1      | XXXX  |       |       |       |               |

| YMODSRT  | 004C        |        |        |                                     |          |        | Y      | S<15:1> |       |       |       |         |        |       |       |       | 0     | XXXX          |

| YMODEND  | 004E        |        |        |                                     | YE<15:1> |        |        |         |       |       |       | 1       | XXXX   |       |       |       |       |               |

| XBREV    | 0050        | BREN   |        | XB<14:0>                            |          |        |        |         |       |       |       | XXXX    |        |       |       |       |       |               |

| DISICNT  | 0052        | _      | _      | Disable Interrupts Counter Register |          |        |        |         |       |       |       | XXXX    |        |       |       |       |       |               |

Legend:

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| File Name | Addr<br>Offset | Bit 15  | Bit 14 | Bit 13  | Bit 12   | Bit 11   | Bit 10     | Bit 9         | Bit 8     | Bit 7 | Bit 6  | Bit 5   | Bit 4  | Bit 3   | Bit 2     | Bit 1   | Bit 0   | All<br>Resets |

|-----------|----------------|---------|--------|---------|----------|----------|------------|---------------|-----------|-------|--------|---------|--------|---------|-----------|---------|---------|---------------|

| PWMCON2   | 0440           | FLTSTAT | CLSTAT | TRGSTAT | FLTIEN   | CLIEN    | TRGIEN     | ITB           | MDCS      | DTC<  | 1:0>   | —       | —      | —       | CAM       | XPRES   | IUE     | 0000          |

| IOCON2    | 0442           | PENH    | PENL   | POLH    | POLL     | PMOD     | )<1:0>     | OVRENH        | OVRENL    | OVRDA | T<1:0> | FLTDA   | T<1:0> | CLDA    | AT<1:0>   | SWAP    | OSYNC   | 0000          |

| FCLCON2   | 0444           | IFLTMOD |        |         | CLSRC<4: | 0>       |            | CLPOL         | CLMOD     |       | FLT    | SRC<4:0 | >      |         | FLTPOL    | FLTMO   | D<1:0>  | 0000          |

| PDC2      | 0446           |         |        |         |          |          | PDC2<15:0> |               |           |       |        |         |        | 0000    |           |         |         |               |

| PHASE2    | 0448           |         |        |         |          |          |            | P             | HASE2<15  | :0>   |        |         |        |         |           |         |         | 0000          |

| DTR2      | 044A           | _       |        |         |          |          |            | DTR2<13:0>    |           |       |        |         |        |         | 0000      |         |         |               |

| ALTDTR2   | 044C           | _       | _      |         |          |          |            | ALTDTR2<13:0> |           |       |        |         |        |         | 0000      |         |         |               |

| SDC2      | 044E           |         |        |         |          |          |            |               | SDC2<15:0 | >     |        |         |        |         |           |         |         | 0000          |

| SPHASE2   | 0450           |         |        |         |          |          |            | SI            | PHASE2<18 | 5:0>  |        |         |        |         |           |         |         | 0000          |

| TRIG2     | 0452           |         |        |         |          |          | TRGCM      | P<15:3>       |           |       |        |         |        |         | _         | _       | _       | 0000          |

| TRGCON2   | 0454           |         | TRGD   | IV<3:0> |          | _        | _          | _             | _         | DTM   | _      |         |        | TRO     | GSTRT<5:0 | )>      |         | 0000          |

| STRIG2    | 0456           |         |        |         |          |          | STRGCN     | STRGCMP<15:3> |           |       |        |         |        | 0000    |           |         |         |               |

| PWMCAP2   | 0458           |         |        |         |          |          | PWMCA      | PWMCAP2<15:3> |           |       |        |         |        | 0000    |           |         |         |               |

| LEBCON2   | 045A           | PHR     | PHF    | PLR     | PLF      | FLTLEBEN | CLLEBEN    |               |           | LEI   | B<6:0> |         |        |         | _         | _       | _       | 0000          |

| AUXCON2   | 045E           | HRPDIS  | HRDDIS | _       | _        | _        | _          | _             | _         | _     |        |         | CHOPS  | EL<3:0> |           | CHOPHEN | CHOPLEN | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-34: PMD REGISTER MAP FOR dsPIC33FJ06GS001

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| PMD1        | 0770        | _      | _      | _      | T2MD   | T1MD   | _      | PWMMD  | _      | I2C1MD | _     | —     | —     |        | _     |       | ADCMD | 0000          |

| PMD3        | 0774        | _      | _      | _      | _      | _      | CMPMD  | _      | _      | _      | _     | _     | _     | _      | _     | _     | _     | 0000          |

| PMD4        | 0776        | _      | _      | _      |        | —      | _      |        |        | _      |       | —     | —     | REFOMD | _     | _     | _     | 0000          |

| PMD6        | 077A        | _      | _      | _      |        | PWM4MD | _      |        | PWM1MD | _      |       | —     | —     |        | _     | _     | _     | 0000          |

| PMD7        | 077C        | _      | _      | _      |        | —      | _      | CMPMD2 | CMPMD1 | _      | _     | _     | —     |        | _     | _     | _     | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-35: PMD REGISTER MAP FOR dsPIC33FJ06GS101A

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|--------|--------|--------|--------|--------|--------|-------|--------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| PMD1        | 0770        |        | —      |        | T2MD   | T1MD   | _      | PWMMD | -      | I2C1MD |       | U1MD  | _     | SPI1MD | _     | _     | ADCMD | 0000          |

| PMD2        | 0772        | _      | _      | _      |        | _      | _      |       | _      |        |       | —     | _     |        | _     |       | OC1MD | 0000          |

| PMD4        | 0776        | _      | _      | _      | _      | _      | _      | _     | _      | _      | _     |       | _     | REFOMD |       | _     | _     | 0000          |

| PMD6        | 077A        | —      | _      | -      |        | PWM4MD | _      | -     | PWM1MD |        |       | _     | —     |        | _     |       |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-36: PMD REGISTER MAP FOR dsPIC33FJ06GS102A

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| PMD1        | 0770        |        |        | _      | T2MD   | T1MD   | _      | PWMMD  | _      | I2C1MD | _     | U1MD  | _     | SPI1MD | _     | _     | ADCMD | 0000          |

| PMD2        | 0772        | _      | _      | _      | _      | _      | _      | _      | _      | _      |       | _     | _     | _      | _     | _     | OC1MD | 0000          |

| PMD4        | 0776        | _      | _      | _      | _      | _      | _      | _      | _      | _      |       | _     | _     | REFOMD | _     | _     | _     | 0000          |

| PMD6        | 077A        | _      | _      | _      | _      | _      | _      | PWM2MD | PWM1MD | _      | _     | —     | _     | -      | _     | —     | _     | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| <b>REGISTER 7</b> | -4: INTCO                                                                                                                        | N2: INTERR                                                                                         |                       | ROL REGIST       | ER 2             |                 |        |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------|------------------|------------------|-----------------|--------|--|

| R/W-0             | R-0                                                                                                                              | U-0                                                                                                | U-0                   | U-0              | U-0              | U-0             | U-0    |  |

| ALTIVT            | DISI                                                                                                                             | —                                                                                                  | _                     |                  | —                |                 | —      |  |

| bit 15            |                                                                                                                                  |                                                                                                    |                       |                  |                  |                 | bit 8  |  |

| U-0               | U-0                                                                                                                              | U-0                                                                                                | U-0                   | U-0              | R/W-0            | R/W-0           | R/W-0  |  |

|                   |                                                                                                                                  |                                                                                                    | _                     |                  | INT2EP           | INT1EP          | INT0EP |  |

| bit 7             |                                                                                                                                  |                                                                                                    |                       |                  |                  |                 | bit 0  |  |

|                   |                                                                                                                                  |                                                                                                    |                       |                  |                  |                 |        |  |

| Legend:           |                                                                                                                                  |                                                                                                    |                       |                  |                  |                 |        |  |

| R = Readable      | bit                                                                                                                              | W = Writable                                                                                       | bit                   | U = Unimpler     | mented bit, read | as '0'          |        |  |

| -n = Value at F   | POR                                                                                                                              | '1' = Bit is set                                                                                   |                       | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |  |

| bit 14            | 0 = Uses stan<br>DISI: DISI In<br>1 = DISI inst                                                                                  | rnate vector tab<br>idard (default) v<br>struction Status<br>ruction is active<br>ruction is not a | vector table<br>s bit |                  |                  |                 |        |  |

| bit 13-3          | Unimplemen                                                                                                                       | ted: Read as '                                                                                     | )'                    |                  |                  |                 |        |  |

| bit 2             | 1 = Interrupt o                                                                                                                  | rnal Interrupt 2<br>on negative edg<br>on positive edg                                             | je                    | Polarity Selec   | t bit            |                 |        |  |

| bit 1             | 1 = Interrupt o                                                                                                                  | rnal Interrupt 1<br>on negative edg<br>on positive edg                                             | ge                    | Polarity Selec   | t bit            |                 |        |  |

| bit 0             | INTOEP: External Interrupt 0 Edge Detect Polarity Select bit<br>1 = Interrupt on negative edge<br>0 = Interrupt on positive edge |                                                                                                    |                       |                  |                  |                 |        |  |

| U-0          | R/W-1        | R/W-0                                   | R/W-0          | U-0               | R/W-1                    | R/W-0                     | R/W-0 |

|--------------|--------------|-----------------------------------------|----------------|-------------------|--------------------------|---------------------------|-------|

| _            |              | T1IP<2:0>                               |                | —                 |                          | OC1IP<2:0> <sup>(1)</sup> |       |

| pit 15       |              |                                         |                |                   |                          |                           | bit   |

|              |              |                                         |                |                   |                          |                           |       |

| U-0          | R/W-1        | R/W-0                                   | R/W-0          | U-0               | R/W-1                    | R/W-0                     | R/W-0 |

| —            |              | IC1IP<2:0> <sup>(2)</sup>               |                | —                 |                          | INT0IP<2:0>               |       |

| oit 7        |              |                                         |                |                   |                          |                           | bit   |

| Legend:      |              |                                         |                |                   |                          |                           |       |

| R = Readabl  | e bit        | W = Writable b                          | bit            | U = Unimple       | mented bit, re           | ad as '0'                 |       |

| n = Value at | POR          | '1' = Bit is set                        |                | '0' = Bit is cl   | eared                    | x = Bit is unkn           | own   |

|              |              |                                         |                |                   |                          |                           |       |

| bit 15       | -            | ented: Read as '0                       |                |                   |                          |                           |       |

| bit 14-12    |              | Timer1 Interrupt                        | -              |                   |                          |                           |       |

|              | 111 = Interr | upt is Priority 7 (h                    | lignest prior  | ity interrupt)    |                          |                           |       |

|              | •            |                                         |                |                   |                          |                           |       |

|              | •            |                                         |                |                   |                          |                           |       |

|              |              | upt is Priority 1<br>upt source is disa | abled          |                   |                          |                           |       |

| bit 11       | Unimpleme    | ented: Read as '0                       | ,              |                   |                          |                           |       |

| bit 10-8     | OC1IP<2:0    | >: Output Compa                         | re Channel     | 1 Interrupt Prio  | rity bits <sup>(1)</sup> |                           |       |

|              | 111 = Interr | upt is Priority 7 (ł                    | nighest prior  | ity interrupt)    |                          |                           |       |

|              | •            |                                         |                |                   |                          |                           |       |

|              | •            |                                         |                |                   |                          |                           |       |

|              | 001 = Interr | upt is Priority 1                       |                |                   |                          |                           |       |

|              |              | upt source is disa                      | abled          |                   |                          |                           |       |

| bit 7        | Unimpleme    | ented: Read as '0                       | ,              |                   |                          |                           |       |

| bit 6-4      | IC1IP<2:0>   | : Input Capture C                       | hannel 1 Int   | errupt Priority I | oits <sup>(2)</sup>      |                           |       |

|              |              | upt is Priority 7 (I                    |                |                   |                          |                           |       |

|              | •            |                                         |                |                   |                          |                           |       |

|              | •            |                                         |                |                   |                          |                           |       |

|              | 001 = Interr | upt is Priority 1                       |                |                   |                          |                           |       |

|              |              | upt source is disa                      | abled          |                   |                          |                           |       |

| bit 3        | Unimpleme    | nted: Read as '0                        | ,              |                   |                          |                           |       |

| bit 2-0      | INT0IP<2:0   | >: External Interr                      | upt 0 Priority | v bits            |                          |                           |       |

|              |              | upt is Priority 7 (I                    |                |                   |                          |                           |       |

|              | •            |                                         |                |                   |                          |                           |       |

|              | •            |                                         |                |                   |                          |                           |       |

|              | •            |                                         |                |                   |                          |                           |       |

|              | 001 = Interr | upt is Priority 1                       |                |                   |                          |                           |       |

#### **Note 1:** These bits are not implemented in the dsPIC33FJ06GS001 device.

2: These bits are not implemented in dsPIC33FJ06GS001/101A/102A devices.

### 8.1 CPU Clocking System

The devices provide six system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with PLL

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- · Low-Power RC (LPRC) Oscillator

- FRC Oscillator with Postscaler

#### 8.1.1 SYSTEM CLOCK SOURCES

The Fast RC (FRC) internal oscillator runs at a nominal frequency of 7.37 MHz. User software can tune the FRC frequency. User software can optionally specify a factor (ranging from 1:2 to 1:256) by which the FRC clock frequency is divided. This factor is selected using the FRCDIV<2:0> (CLKDIV<10:8>) bits.

The primary oscillator can use one of the following as its clock source:

- XT (Crystal): Crystals and ceramic resonators in the range of 3 MHz to 10 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- HS (High-Speed Crystal): Crystals in the range of 10 MHz to 32 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- EC (External Clock): The external clock signal is directly applied to the OSC1 pin.

The LPRC internal oscIllator runs at a nominal frequency of 32.768 kHz. It is also used as a reference clock by the Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The clock signals generated by the FRC and primary oscillators can be optionally applied to an on-chip Phase Lock Loop (PLL) to provide a wide range of

output frequencies for device operation. PLL configuration is described in **Section 8.1.3 "PLL Configuration"**.

The FRC frequency depends on the FRC accuracy (see Table 25-20) and the value of the FRC Oscillator Tuning register (see Register 8-4).

#### 8.1.2 SYSTEM CLOCK SELECTION

The oscillator source used at a device Power-on Reset event is selected using Configuration bit settings. The Oscillator Configuration bit settings are located in the Configuration registers in the program memory. (Refer to Section 22.1 "Configuration Bits" for further details.) The initial Oscillator Selection Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), and the Primary Oscillator Mode Select Configuration bits. POSCMD<1:0> (FOSC<1:0>), select the oscillator source that is used at a Power-on Reset. The FRC primary oscillator is the default (unprogrammed) selection.

The Configuration bits allow users to choose among 12 different clock modes, shown in Table 8-1.

The output of the oscillator (or the output of the PLL if a PLL mode has been selected), FOSC, is divided by 2 to generate the device instruction clock (FCY) and the peripheral clock time base (FP). FCY defines the operating speed of the device and speeds up to 40 MHz are supported by the device architecture.

Instruction execution speed or device operating frequency, FCY, is given by Equation 8-1.

#### EQUATION 8-1: DEVICE OPERATING FREQUENCY

FCY = FOSC/2

| Oscillator Mode                                 | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See Note |

|-------------------------------------------------|-------------------|-------------|------------|----------|

| Fast RC Oscillator with Divide-by-N (FRCDIVN)   | Internal          | XX          | 111        | 1, 2     |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16) | Internal          | XX          | 110        | 1        |

| Low-Power RC Oscillator (LPRC)                  | Internal          | XX          | 101        | 1        |

| Reserved                                        | Reserved          | XX          | 100        | —        |

| Primary Oscillator (HS) with PLL (HSPLL)        | Primary           | 10          | 011        | _        |

| Primary Oscillator (XT) with PLL (XTPLL)        | Primary           | 01          | 011        | —        |

| Primary Oscillator (EC) with PLL (ECPLL)        | Primary           | 00          | 011        | 1        |

| Primary Oscillator (HS)                         | Primary           | 10          | 010        | _        |

| Primary Oscillator (XT)                         | Primary           | 01          | 010        | —        |

| Primary Oscillator (EC)                         | Primary           | 00          | 010        | 1        |

| Fast RC Oscillator with PLL (FRCPLL)            | Internal          | XX          | 001        | 1        |

| Fast RC Oscillator (FRC)                        | Internal          | XX          | 000        | 1        |

### TABLE 8-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

NOTES:

| U-0           | U-0                 | U-0                                  | U-0           | U-0              | U-0                  | U-0                          | U-0   |

|---------------|---------------------|--------------------------------------|---------------|------------------|----------------------|------------------------------|-------|

| —             | —                   | —                                    | _             | —                | _                    |                              |       |

| bit 15        |                     |                                      |               |                  |                      |                              | bit 8 |

|               |                     |                                      |               |                  |                      |                              |       |

| U-0           | U-0                 | R/W-1                                | R/W-1         | R/W-1            | R/W-1                | R/W-1                        | R/W-1 |

|               |                     |                                      |               | SS1R             | <5:0> <sup>(1)</sup> |                              |       |

| bit 7         |                     |                                      |               |                  |                      |                              | bit 0 |

|               |                     |                                      |               |                  |                      |                              |       |

| Legend:       |                     |                                      |               |                  |                      |                              |       |

| R = Readabl   | le bit              | W = Writable                         | bit           | U = Unimpler     | mented bit, read     | as '0'                       |       |

| -n = Value at | t POR               | '1' = Bit is set                     |               | '0' = Bit is cle | ared                 | x = Bit is unkn              | iown  |

|               |                     |                                      |               |                  |                      |                              |       |

| bit 15-6      | Unimplemen          | ted: Read as '                       | כי            |                  |                      |                              |       |

| bit 5-0       | SS1R<5:0>: /        | Assign SPI1 Sla                      | ave Select In | put (SS1) to the | e Corresponding      | g RPn Pin bits <sup>(1</sup> | 1)    |

|               | 111111 <b>= Inp</b> |                                      |               |                  |                      |                              |       |

|               |                     | out tied to RP35                     |               |                  |                      |                              |       |

|               |                     | out tied to RP34                     |               |                  |                      |                              |       |

|               |                     | out tied to RP33<br>out tied to RP32 |               |                  |                      |                              |       |

|               | •                   |                                      | -             |                  |                      |                              |       |

|               | •                   |                                      |               |                  |                      |                              |       |

|               | •                   |                                      |               |                  |                      |                              |       |

|               | 00000 <b>= Inpu</b> | t tied to RP0                        |               |                  |                      |                              |       |

|               |                     |                                      |               |                  |                      |                              |       |

#### REGISTER 10-9: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

**Note 1:** These bits are not implemented in the dsPIC33FJ06GS001 device.

| U-0          | U-0                               | R/W-1        | R/W-1 | R/W-1            | R/W-1           | R/W-1    | R/W-1 |

|--------------|-----------------------------------|--------------|-------|------------------|-----------------|----------|-------|

|              | —                                 |              |       | FLT1             | R<5:0>          |          |       |

| bit 15       |                                   |              |       |                  |                 |          | bit 8 |

|              |                                   |              |       |                  |                 |          |       |

| U-0          | U-0                               | U-0          | U-0   | U-0              | U-0             | U-0      | U-0   |

| —            | _                                 | —            | _     | —                |                 | —        | —     |

| bit 7        |                                   |              |       |                  |                 |          | bit 0 |

| Legend:      |                                   |              |       |                  |                 |          |       |

| R = Readab   | ole bit                           | W = Writable | bit   | U = Unimpler     | nented bit, rea | d as '0' |       |

| -n = Value a | n = Value at POR (1' = Bit is set |              |       | '0' = Bit is cle | nown            |          |       |

#### REGISTER 10-10: RPINR29: PERIPHERAL PIN SELECT INPUT REGISTER 29

bit 15-14 Unimplemented: Read as '0'

bit 13-8

8 FLT1R<5:0>: Assign PWM Fault Input 1 (FLT1) to the Corresponding RPn Pin bits

111111 = Input tied to Vss 100011 = Input tied to RP35 100010 = Input tied to RP34 100001 = Input tied to RP33 100000 = Input tied to RP32 • • •

bit 7-0 Unimplemented: Read as '0'

|                 |     |                  |       |                  |                  | -               |       |

|-----------------|-----|------------------|-------|------------------|------------------|-----------------|-------|

| U-0             | U-0 | U-0              | U-0   | U-0              | U-0              | U-0             | U-0   |

| _               |     | _                |       | —                | —                | —               | —     |

| bit 15          |     |                  |       |                  |                  |                 | bit 8 |

|                 |     |                  |       |                  |                  |                 |       |

| U-0             | U-0 | R/W-1            | R/W-1 | R/W-1            | R/W-1            | R/W-1           | R/W-1 |

| _               |     |                  |       | SYNC             | l2R<5:0>         |                 |       |

| bit 7           |     |                  |       |                  |                  |                 | bit 0 |

|                 |     |                  |       |                  |                  |                 |       |

| Legend:         |     |                  |       |                  |                  |                 |       |

| R = Readable I  | oit | W = Writable     | bit   | U = Unimpler     | mented bit, read | d as '0'        |       |

| -n = Value at P | OR  | '1' = Bit is set |       | '0' = Bit is cle | ared             | x = Bit is unkı | nown  |

#### REGISTER 10-15: RPINR34: PERIPHERAL PIN SELECT INPUT REGISTER 34

bit 15-6 Unimplemented: Read as '0'

bit 5-0

**SYNCI2R<5:0>:** Assign PWM Master Time Base External Synchronization Signal to the Corresponding RPn Pin bits

111111 = Input tied to Vss 100011 = Input tied to RP35 100010 = Input tied to RP34 100001 = Input tied to RP33 100000 = Input tied to RP32 •

00000 = Input tied to RP0

© 2011-2012 Microchip Technology Inc.

#### REGISTER 10-18: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2

| U-0    | U-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|--------|-----|-------|-----------|-------|-------|-------|-------|--|

| —      | —   |       | RP5R<5:0> |       |       |       |       |  |

| bit 15 |     |       |           |       |       |       | bit 8 |  |

| U-0   | U-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------|-----|-------|-----------|-------|-------|-------|-------|--|

| —     | —   |       | RP4R<5:0> |       |       |       |       |  |

| bit 7 |     |       |           |       |       |       | bit 0 |  |

| Legend:           |                  |                       |                                    |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |

| bit 15-14 | Unimplemented: Read as '0'                                               |

|-----------|--------------------------------------------------------------------------|

| bit 13-8  | RP5R<5:0>: Peripheral Output Function is Assigned to RP5 Output Pin bits |

|           | (see Table 10-2 for peripheral function numbers)                         |

| bit 7-6   | Unimplemented: Read as '0'                                               |

| bit 5-0   | RP4R<5:0>: Peripheral Output Function is Assigned to RP4 Output Pin bits |

|           | (see Table 10-2 for peripheral function numbers)                         |

#### REGISTER 10-19: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| U-0    | U-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|--------|-----|-----------|-------|-------|-------|-------|-------|--|

| —      | —   | RP7R<5:0> |       |       |       |       |       |  |

| bit 15 |     |           |       |       |       |       | bit 8 |  |

| U-0   | U-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----------|-------|-------|-------|-------|-------|

| —     | —   | RP6R<5:0> |       |       |       |       |       |

| bit 7 |     |           |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

| bit 13-8 | <b>RP7R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP7 Output Pin bits |

|----------|---------------------------------------------------------------------------------------|

|          | (see Table 10-2 for peripheral function numbers)                                      |

| bit 7-6  | Unimplemented: Read as '0'                                                            |

bit 5-0 **RP6R<5:0>:** Peripheral Output Function is Assigned to RP6 Output Pin bits (see Table 10-2 for peripheral function numbers)

#### REGISTER 15-15: FCLCONX: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER (CONTINUED)

bit 7-3

**FLTSRC<4:0>:** Fault Control Signal Source Select for PWM Generator # bits<sup>(2,3)</sup>

- .

- .

- •

- 01000 = Reserved

- 00111 = Fault 8 00110 = Fault 7 00101 = Fault 6 00100 = Fault 5 00011 = Fault 4 00010 = Fault 3

- 00001 = Fault 2 00000 = Fault 1

- bit 2 **FLTPOL:** Fault Polarity for PWMx Generator # bit<sup>(1)</sup>

- 1 = The selected Fault source is active-low

- 0 = The selected Fault source is active-high

bit 1-0 **FLTMOD<1:0>:** Fault Mode for PWMx Generator # bits

- 11 = Fault input is disabled

- 10 = Reserved

- 01 = The selected Fault source forces PWMxH, PWMxL pins to FLTDAT values (cycle)

- 00 = The selected Fault source forces PWMxH, PWMxL pins to FLTDAT values (latched condition)

- **Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

- 2: When Independent Fault mode is enabled (IFLTMOD<1:0> = 1), and Fault 1 is used for Current-Limit mode (CLSRC<4:0> = b0000), the Fault Control Source Select bits (FLTSRC<4:0>) should be set to an unused Fault source to prevent Fault 1 from disabling both the PWMxL and PWMxH outputs.

- 3: When Independent Fault mode is enabled (IFLTMOD<1:0> = 1) and Fault 1 is used for Fault mode (FLTSRC<4:0> = b0000), the Current-Limit Control Source Select bits (CLSRC<4:0>) should be set to an unused current-limit source to prevent the current-limit source from disabling both the PWMxH and PWMxL outputs.

| REGISTER 19-3: | ADBASE: ADC BASE REGISTER <sup>(1)</sup> |

|----------------|------------------------------------------|

|----------------|------------------------------------------|

| R/W-0                      | R/W-0 | R/W-0 | R/W-0  | R/W-0                 | R/W-0 | R/W-0 | R/W-0 |

|----------------------------|-------|-------|--------|-----------------------|-------|-------|-------|

|                            |       |       | ADBASE | <15:8> <sup>(2)</sup> |       |       |       |

| bit 15                     |       |       |        |                       |       |       | bit 8 |

| R/W-0                      | R/W-0 | R/W-0 | R/W-0  | R/W-0                 | R/W-0 | R/W-0 | U-0   |

| ADBASE<7:1> <sup>(2)</sup> |       |       |        |                       |       |       |       |

| bit 7                      |       |       |        |                       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 15-1 ADBASE<15:1>: ADC Base Register bits<sup>(2)</sup>

This register contains the base address of the user's ADC Interrupt Service Routine (ISR) jump table. This register, when read, contains the sum of the ADBASE register contents and the encoded value of the PxRDY status bits.

The encoder logic provides the bit number of the highest priority PxRDY bits, where P0RDY is the highest priority and P6RDY is the lowest priority.

- bit 0 Unimplemented: Read as '0'

- **Note 1:** As an alternative to using the ADBASE register, the ADCP0-6 ADC Pair Conversion Complete Interrupts can be used to invoke A to D conversion completion routines for individual ADC input pairs.

- 2: The encoding results are shifted left two bits, so bits 1-0 of the result are always zero.

| U-0                                | U-0                                                                         | U-0                                   | U-0                                     | U-0                                | U-0   | U-0   | U-0   |  |

|------------------------------------|-----------------------------------------------------------------------------|---------------------------------------|-----------------------------------------|------------------------------------|-------|-------|-------|--|

| —                                  | —                                                                           | —                                     | _                                       | —                                  | —     | —     | _     |  |

| bit 15                             | ·                                                                           |                                       |                                         |                                    |       |       | bit 8 |  |

|                                    |                                                                             |                                       |                                         |                                    |       |       |       |  |

| R/W-0                              | R/W-0                                                                       | U-0                                   | U-0                                     | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |

| PCFG7 <sup>(1)</sup>               | PCFG6 <sup>(1)</sup>                                                        | —                                     | _                                       | PCFG3                              | PCFG2 | PCFG1 | PCFG0 |  |

| bit 7                              |                                                                             | · · · · · · · · · · · · · · · · · · · |                                         |                                    |       |       | bit C |  |

|                                    |                                                                             |                                       |                                         |                                    |       |       |       |  |

| Legend:                            |                                                                             |                                       |                                         |                                    |       |       |       |  |

| R = Readable                       | bit                                                                         | W = Writable I                        | bit                                     | U = Unimplemented bit, read as '0' |       |       |       |  |

| -n = Value at POR '1' = Bit is set |                                                                             |                                       | '0' = Bit is cleared x = Bit is unknown |                                    | nown  |       |       |  |

|                                    |                                                                             |                                       |                                         |                                    |       |       |       |  |

| bit 15-8                           | Unimplemented: Read as '0'                                                  |                                       |                                         |                                    |       |       |       |  |

| bit 7-6                            | PCFG<7:6>: Analog-to-Digital Port Configuration Control bits <sup>(1)</sup> |                                       |                                         |                                    |       |       |       |  |

#### REGISTER 19-4: ADPCFG: ADC PORT CONFIGURATION REGISTER

bit 7-6 **PCFG<7:6>:** Analog-to-Digital Port Configuration Control bits

- 1 = Port pin is in Digital mode; port read input is enabled; Analog-to-Digital input multiplexer is connected to AVss

- 0 = Port pin is in Analog mode; port read input is disabled; Analog-to-Digital samples pin voltage

#### bit 5-4 Unimplemented: Read as '0'

- bit 3-0 **PCFG<3:0>:** Analog-to-Digital Port Configuration Control bits

- 1 = Port pin is in Digital mode; port read input is enabled; Analog-to-Digital input multiplexer is connected to AVss

- 0 = Port pin is in Analog mode; port read input is disabled; Analog-to-Digital samples pin voltage

- **Note 1:** This bit is not implemented in dsPIC33FJ06GS102A/202A devices.

- 2: This bit is not implemented in dsPIC33FJ06GS001/101A devices.

| IADL                                    | E 23-2: | INSTRUCTION SET OVERVIEW (CONTINUED)                     |                         |                                        |               |                |                          |  |  |  |

|-----------------------------------------|---------|----------------------------------------------------------|-------------------------|----------------------------------------|---------------|----------------|--------------------------|--|--|--|

| Base<br>Instr<br># Assembly<br>Mnemonic |         | Assembly Syntax                                          |                         | Description                            | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |  |  |  |

| 29                                      | DIV     | DIV.S                                                    | Wm,Wn                   | Signed 16/16-bit Integer Divide        | 1             | 18             | N,Z,C,OV                 |  |  |  |

|                                         |         | DIV.SD                                                   | Wm,Wn                   | Signed 32/16-bit Integer Divide        | 1             | 18             | N,Z,C,OV                 |  |  |  |

|                                         |         | DIV.U                                                    | Wm,Wn                   | Unsigned 16/16-bit Integer Divide      | 1             | 18             | N,Z,C,OV                 |  |  |  |

|                                         |         | DIV.UD                                                   | Wm,Wn                   | Unsigned 32/16-bit Integer Divide      | 1             | 18             | N,Z,C,OV                 |  |  |  |

| 30                                      | DIVF    | DIVF                                                     | Wm,Wn                   | Signed 16/16-bit Fractional Divide     | 1             | 18             | N,Z,C,OV                 |  |  |  |

| 31                                      | DO      | DO #lit14,Expr                                           |                         | Do code to PC + Expr, lit14 + 1 times  | 2             | 2              | None                     |  |  |  |

|                                         |         | DO                                                       | Wn,Expr                 | Do code to PC + Expr, (Wn) + 1 times   | 2             | 2              | None                     |  |  |  |

| 32                                      | ED      | ED                                                       | Wm*Wm,Acc,Wx,Wy,Wxd     | Euclidean Distance (no accumulate)     | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |  |  |  |

| 33                                      | EDAC    | EDAC                                                     | Wm*Wm,Acc,Wx,Wy,Wxd     | Euclidean Distance                     | 1             | 1              | OA,OB,OAB<br>SA,SB,SAB   |  |  |  |

| 34                                      | EXCH    | EXCH                                                     | Wns,Wnd                 | Swap Wns with Wnd                      | 1             | 1              | None                     |  |  |  |

| 35                                      | FBCL    | FBCL                                                     | Ws,Wnd                  | Find Bit Change from Left (MSb) Side   | 1             | 1              | С                        |  |  |  |

| 36                                      | FF1L    | FF1L                                                     | Ws,Wnd                  | Find First One from Left (MSb) Side    | 1             | 1              | С                        |  |  |  |

| 37                                      | FF1R    | FF1R                                                     | Ws,Wnd                  | Find First One from Right (LSb) Side   | 1             | 1              | С                        |  |  |  |

| 38                                      | GOTO    | GOTO                                                     | Expr                    | Go to Address                          | 2             | 2              | None                     |  |  |  |

|                                         |         | GOTO                                                     | Wn                      | Go to Indirect                         | 1             | 2              | None                     |  |  |  |

| 39                                      | INC     | INC                                                      | f                       | f = f + 1                              | 1             | 1              | C,DC,N,OV,Z              |  |  |  |

|                                         |         | INC                                                      | f,WREG                  | WREG = f + 1                           | 1             | 1              | C,DC,N,OV,Z              |  |  |  |

|                                         |         | INC                                                      | Ws,Wd                   | Wd = Ws + 1                            | 1             | 1              | C,DC,N,OV,Z              |  |  |  |

| 40                                      | INC2    | INC2                                                     | f                       | f = f + 2                              | 1             | 1              | C,DC,N,OV,Z              |  |  |  |

|                                         |         | INC2                                                     | f,WREG                  | WREG = f + 2                           | 1             | 1              | C,DC,N,OV,Z              |  |  |  |

|                                         |         | INC2                                                     | Ws,Wd                   | Wd = Ws + 2                            | 1             | 1              | C,DC,N,OV,Z              |  |  |  |

| 41                                      | IOR     | IOR                                                      | f                       | f = f .IOR. WREG                       | 1             | 1              | N,Z                      |  |  |  |

|                                         |         | IOR                                                      | f,WREG                  | WREG = f .IOR. WREG                    | 1             | 1              | N,Z                      |  |  |  |

|                                         |         | IOR                                                      | #lit10,Wn               | Wd = lit10 .IOR. Wd                    | 1             | 1              | N,Z                      |  |  |  |

|                                         |         | IOR                                                      | Wb,Ws,Wd                | Wd = Wb .IOR. Ws                       | 1             | 1              | N,Z                      |  |  |  |

|                                         |         | IOR                                                      | Wb,#lit5,Wd             | Wd = Wb .IOR. lit5                     | 1             | 1              | N,Z                      |  |  |  |

| 42                                      | LAC     | LAC                                                      | Wso,#Slit4,Acc          | Load Accumulator 1                     |               | 1              | OA,OB,OAB<br>SA,SB,SAB   |  |  |  |

| 43                                      | LNK     | LNK                                                      | #lit14                  | Link Frame Pointer                     | 1             | 1              | None                     |  |  |  |

| 44                                      | LSR     | LSR                                                      | f                       | f = Logical Right Shift f              | 1             | 1              | C,N,OV,Z                 |  |  |  |

|                                         |         | LSR                                                      | f,WREG                  | WREG = Logical Right Shift f           | 1             | 1              | C,N,OV,Z                 |  |  |  |

|                                         |         | LSR                                                      | Ws,Wd                   | Wd = Logical Right Shift Ws            | 1             | 1              | C,N,OV,Z                 |  |  |  |

|                                         |         | LSR                                                      | Wb,Wns,Wnd              | Wnd = Logical Right Shift Wb by Wns    | 1             | 1              | N,Z                      |  |  |  |

|                                         |         | LSR                                                      | Wb,#lit5,Wnd            | Wnd = Logical Right Shift Wb by lit5   | 1             | 1              | N,Z                      |  |  |  |

| 45                                      | MAC     | MAC Wm*Wn, Acc, Wx, Wxd, Wy, Wyd Multiply and Accumulate |                         | , o o ,                                | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |  |  |  |

|                                         |         | MAC                                                      | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd | Square and Accumulate                  | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |  |  |  |

| 46                                      | MOV     | MOV                                                      | f,Wn                    | Move f to Wn                           | 1             | 1              | None                     |  |  |  |

|                                         |         | MOV                                                      | f                       | Move f to f                            | 1             | 1              | N,Z                      |  |  |  |

|                                         |         | MOV                                                      | f,WREG                  | Move f to WREG                         | 1             | 1              | None                     |  |  |  |

|                                         |         | MOV                                                      | #lit16,Wn               | Move 16-bit Literal to Wn              | 1             | 1              | None                     |  |  |  |

|                                         |         | MOV.b                                                    | #lit8,Wn                | Move 8-bit Literal to Wn               | 1             | 1              | None                     |  |  |  |

|                                         |         | MOV                                                      | Wn,f                    | Move Wn to f                           | 1             | 1              | None                     |  |  |  |

|                                         |         | MOV                                                      | Wso,Wdo                 | Move Ws to Wd                          | 1             | 1              | None                     |  |  |  |

|                                         |         | MOV                                                      | WREG, f                 | Move WREG to f                         | 1             | 1              | None                     |  |  |  |

|                                         |         | MOV.D                                                    | Wns,Wd                  | Move Double from W(ns):W(ns + 1) to Wd | 1             | 2              | None                     |  |  |  |

|                                         |         | MOV.D                                                    | Ws,Wnd                  | Move Double from Ws to W(nd + 1):W(nd) | 1             | 2              | None                     |  |  |  |

| 47                                      | MOVSAC  | MOVSAC                                                   | Acc,Wx,Wxd,Wy,Wyd,AWB   | Prefetch and Store Accumulator         | 1             | 1              | None                     |  |  |  |

#### TABLE 23-2: INSTRUCTION SET OVERVIEW (CONTINUED)

#### 24.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

#### 24.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

### 24.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

#### 24.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

#### 24.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB IDE compatibility

DS75018C-page 316

© 2011-2012 Microchip Technology Inc

dsPIC33FJ06GS001/101A/102A/202A and dsPIC33FJ09GS302

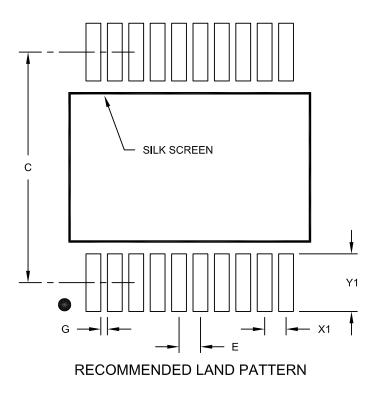

20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |      |          |      |  |

|--------------------------|-------------|------|----------|------|--|

| Dimension Limit          |             | MIN  | NOM      | MAX  |  |

| Contact Pitch            | E           |      | 0.65 BSC |      |  |

| Contact Pad Spacing      | С           |      | 7.20     |      |  |

| Contact Pad Width (X20)  | X1          |      |          | 0.45 |  |

| Contact Pad Length (X20) | Y1          |      |          | 1.75 |  |

| Distance Between Pads    | G           | 0.20 |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2072A