#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 6КВ (2К х 24)                                                                    |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b; D/A 2x10b                                                             |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

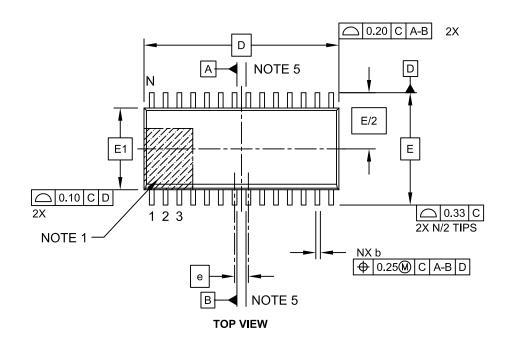

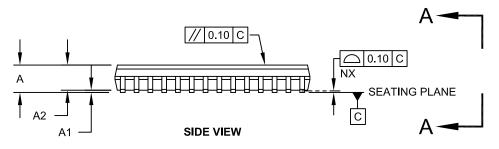

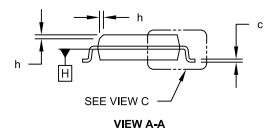

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 28-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs202a-e-ss |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

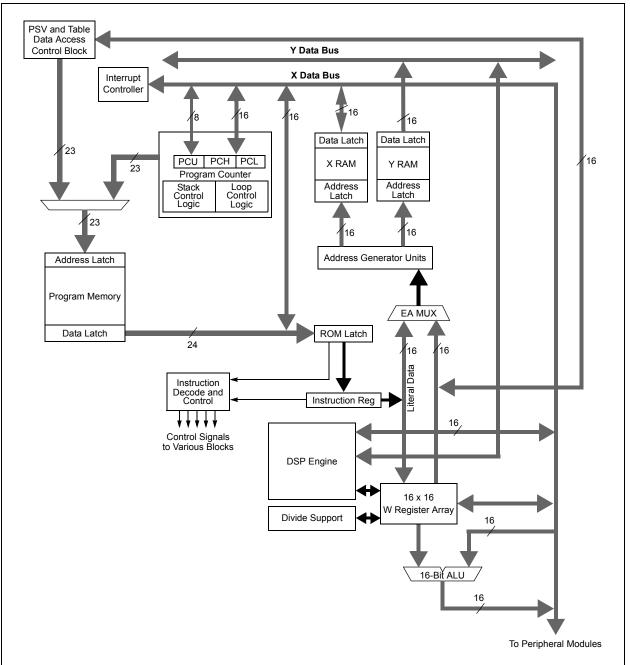

#### 3.3 Special MCU Features

A 17-bit by 17-bit single-cycle multiplier is shared by both the MCU ALU and DSP engine. The multiplier can perform signed, unsigned and mixed-sign multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication not only allows you to perform mixed-sign multiplication, it also achieves accurate results for special operations, such as (-1.0) x (-1.0). The 16/16 and 32/16 divide operations are supported, both fractional and integer. All divide instructions are iterative operations. They must be executed within a REPEAT loop, resulting in a total execution time of 19 instruction cycles. The divide operation can be interrupted during any of those 19 cycles without loss of data.

A 40-bit barrel shifter is used to perform up to a 16-bit left or right shift in a single cycle. The barrel shifter can be used by both MCU and DSP instructions.

#### FIGURE 3-1: CPU CORE BLOCK DIAGRAM

| IADLE        | 4-1.         |         | LINIOF  |            | NOLLEN  |         |        |            | IN USFI | COOLING  | 002027  |              |         |            |        |             |         |               |

|--------------|--------------|---------|---------|------------|---------|---------|--------|------------|---------|----------|---------|--------------|---------|------------|--------|-------------|---------|---------------|

| File<br>Name | SFR<br>Addr. | Bit 15  | Bit 14  | Bit 13     | Bit 12  | Bit 11  | Bit 10 | Bit 9      | Bit 8   | Bit 7    | Bit 6   | Bit 5        | Bit 4   | Bit 3      | Bit 2  | Bit 1       | Bit 0   | All<br>Resets |

| INTCON1      | 0080         | NSTDIS  | OVAERR  | OVBERR     | COVAERR | COVBERR | OVATE  | OVBTE      | COVTE   | SFTACERR | DIV0ERR | _            | MATHERR | ADDRERR    | STKERR | OSCFAIL     | _       | 0000          |

| INTCON2      | 0082         | ALTIVT  | DISI    | —          | —       | —       | _      | —          | _       | -        | —       | _            | _       | _          | INT2EP | INT1EP      | INT0EP  | 0000          |

| IFS0         | 0084         |         | —       | ADIF       | U1TXIF  | U1RXIF  | SPI1IF | SPI1EIF    | _       | T2IF     | —       | _            | _       | T1IF       | OC1IF  | IC1IF       | INTOIF  | 0000          |

| IFS1         | 0086         | _       | _       | INT2IF     | _       | _       | _      | _          | -       | _        | _       |              | INT1IF  | CNIF       | AC1IF  | MI2C1IF     | SI2C1IF | 0000          |

| IFS3         | 008A         | _       | _       | _          | _       | —       | _      | PSEMIF     | -       |          | _       |              | _       | _          |        | _           |         | 0000          |

| IFS4         | 008C         | _       | _       | _          | _       | _       | _      | _          | _       | _        | _       | _            | _       | —          | _      | U1EIF       |         | 0000          |

| IFS5         | 008E         | PWM2IF  | PWM1IF  | _          | _       | _       |        | _          | _       | _        | _       | _            | _       | _          |        | _           | JTAGIF  | 0000          |

| IFS6         | 0090         | ADCP1IF | ADCP0IF | _          | _       | _       | _      | _          | _       | AC2IF    | _       | _            | _       | —          | _      | _           |         | 0000          |

| IFS7         | 0092         | _       | _       | _          | _       | _       | _      | _          | _       | _        | _       | _            | ADCP6IF | —          | _      | _           | ADCP2IF | 0000          |

| IEC0         | 0094         | _       | _       | ADIE       | U1TXIE  | U1RXIE  | SPI1IE | SPI1EIE    | _       | T2IE     | _       | _            | _       | T1IE       | OC1IE  | IC1IE       | INTOIE  | 0000          |

| IEC1         | 0096         | _       | _       | INT2IE     | _       | _       | _      | _          | _       | _        | _       | _            | INT1IE  | CNIE       | AC1IE  | MI2C1IE     | SI2C1IE | 0000          |

| IEC3         | 009A         | _       | _       | _          | _       | _       | _      | PSEMIE     | _       | _        | _       | _            | _       | _          | _      | _           | _       | 0000          |

| IEC4         | 009C         |         | —       | —          | —       | —       |        | —          |         |          | —       |              | _       | —          | -      | U1EIE       | _       | 0000          |

| IEC5         | 009E         | PWM2IE  | PWM1IE  | _          | _       | _       | _      | _          | _       | _        | _       | _            | _       | _          | _      | _           | JTAGIE  | 0000          |

| IEC6         | 00A0         | ADCP1IE | ADCP0IE | —          | —       | —       |        | —          |         | AC2IE    | —       |              | _       | —          | _      | —           | _       | 0000          |

| IEC7         | 00A2         |         | —       | —          | —       | —       |        | —          |         |          | —       |              | ADCP6IE | —          |        | —           | ADCP2IE | 0000          |

| IPC0         | 00A4         |         |         | T1IP<2:0>  |         | —       | U      | OC1IP<2:0  | )>      |          |         | IC1IP<2:0>   | •       | —          |        | INT0IP<2:0> |         | 4444          |

| IPC1         | 00A6         |         |         | T2IP<2:0>  |         | —       |        | —          |         |          | —       |              | —       | —          |        | —           |         | 4000          |

| IPC2         | 00A8         |         |         | U1RXIP<2:0 | )>      | —       |        | SPI1IP<2:0 | )>      |          | 5       | SPI1EIP<2:0  | )>      | —          |        | —           |         | 4440          |

| IPC3         | 00AA         |         | —       | —          | —       | —       |        | —          |         |          |         | ADIP<2:0>    |         | —          | ι      | J1TXIP<2:0> | •       | 0044          |

| IPC4         | 00AC         |         |         | CNIP<2:0>  | •       | —       |        | AC1IP<2:0  | >       |          | Ν       | /II2C1IP<2:0 | )>      | —          | 9      | SI2C1IP<2:0 | >       | 4444          |

| IPC5         | 00AE         |         | —       | —          | —       | —       |        | —          |         |          | —       |              | —       | —          |        | INT1IP<2:0> |         | 0004          |

| IPC7         | 00B2         |         | —       | —          | —       | —       |        | —          |         |          |         | INT2IP<2:0   | >       | —          |        | —           |         | 0040          |

| IPC14        | 00C0         |         | —       | —          | —       | —       |        | —          |         |          | F       | PSEMIP<2:0   | )>      | —          |        | —           |         | 0040          |

| IPC16        | 00C4         |         | —       | —          | —       | —       |        | —          |         |          |         | U1EIP<2:0    | >       | —          |        | —           |         | 0040          |

| IPC20        | 00CC         |         | —       | —          | —       | —       |        | —          |         |          | —       |              | —       | —          | ,      | JTAGIP<2:0> | •       | 0004          |

| IPC23        | 00D2         |         | F       | PWM2IP<2:( | )>      | —       | Р      | WM1IP<2:   | 0>      |          | —       |              | —       | —          |        | —           |         | 4400          |

| IPC25        | 00D6         | -       |         | AC2IP<2:0  | >       | _       |        | _          | _       | _        | _       | _            | _       | —          | -      | _           | _       | 4000          |

| IPC27        | 00DA         |         | A       | ADCP1IP<2: | 0>      | —       | A      | DCP0IP<2   | :0>     |          | -       | -            | _       | —          | -      | —           | _       | 4400          |

| IPC28        | 00DC         | -       | _       | _          | _       | _       |        | _          | _       | _        | _       | _            | _       | —          | A      | DCP2IP<2:0  | >       | 0004          |

| IPC29        | 00DE         | -       | _       | _          | _       | _       | _      | _          | -       | _        | _       | _            | _       | _          | A      | DCP6IP<2:0  | >       | 0004          |

| INTTREG      | 00E0         | _       | _       | _          | _       |         | ILR<   | 3:0>       |         | _        |         |              | ١       | /ECNUM<6:0 | )>     |             |         | 0000          |

#### TABLE 4-7: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33FJ06GS202A DEVICES ONLY

|           |                | USFICJ  | 313036 | 53302   |                               |        |        |           |          |         |         |         |        |         |          |         |         |               |

|-----------|----------------|---------|--------|---------|-------------------------------|--------|--------|-----------|----------|---------|---------|---------|--------|---------|----------|---------|---------|---------------|

| File Name | Addr<br>Offset | Bit 15  | Bit 14 | Bit 13  | Bit 12                        | Bit 11 | Bit 10 | Bit 9     | Bit 8    | Bit 7   | Bit 6   | Bit 5   | Bit 4  | Bit 3   | Bit 2    | Bit 1   | Bit 0   | All<br>Resets |

| PWMCON4   | 0480           | FLTSTAT | CLSTAT | TRGSTAT | FLTIEN                        | CLIEN  | TRGIEN | ITB       | MDCS     | DTC     | <1:0>   | —       | —      | —       | CAM      | XPRES   | IUE     | 0000          |

| IOCON4    | 0482           | PENH    | PENL   | POLH    | POLL                          | PMOD   | )<1:0> | OVRENH    | OVRENL   | OVRDA   | AT<1:0> | FLTDA   | T<1:0> | CLDA    | T<1:0>   | SWAP    | OSYNC   | 0000          |

| FCLCON4   | 0484           | IFLTMOD |        |         | CLSRC<4                       | :0>    |        | CLPOL     | CLMOD    |         | F       | LTSRC<4 | :0>    |         | FLTPOL   | FLTMO   | D<1:0>  | 0000          |

| PDC4      | 0486           |         |        |         |                               |        |        |           | PDC4<15  | :0>     |         |         |        |         |          |         |         | 0000          |

| PHASE4    | 0488           |         |        |         |                               |        |        |           | PHASE4<1 | 5:0>    |         |         |        |         |          |         |         | 0000          |

| DTR4      | 048A           | _       | -      |         | DTR4<13:0>                    |        |        |           |          |         |         | 0000    |        |         |          |         |         |               |

| ALTDTR4   | 048C           | _       | —      |         |                               |        |        |           | /        | ALTDTR4 | <13:0>  |         |        |         |          |         |         | 0000          |

| SDC4      | 048E           |         |        |         |                               |        |        |           | SDC4<15  | :0>     |         |         |        |         |          |         |         | 0000          |

| SPHASE4   | 0490           |         |        |         |                               |        |        | 5         | SPHASE4< | 15:0>   |         |         |        |         |          |         |         | 0000          |

| TRIG4     | 0492           |         |        |         |                               |        | TRGC   | MP<15:3>  |          |         |         |         |        |         | —        | _       | —       | 0000          |

| TRGCON4   | 0494           |         | TRGD   | IV<3:0> |                               | _      | _      | _         | —        | DTM     | —       |         |        | TRG     | STRT<5:0 | >       |         | 0000          |

| STRIG4    | 0496           |         |        |         |                               |        | STRGC  | MP<15:3>  |          |         |         |         |        |         | —        | _       | —       | 0000          |

| PWMCAP4   | 0498           |         |        |         |                               |        | PWMC   | AP4<15:3> |          |         |         |         |        |         | —        | _       | —       | 0000          |

| LEBCON4   | 049A           | PHR     | PHF    | PLR     | PLF FLTLEBEN CLLEBEN LEB<6:0> |        |        |           |          |         |         | 0000    |        |         |          |         |         |               |

| AUXCON4   | 049E           | HRPDIS  | HRDDIS | _       | _                             | _      | _      | _         | _        | _       | _       |         | CHOPS  | EL<3:0> |          | CHOPHEN | CHOPLEN | 0000          |

| 1         |                |         |        |         |                               |        |        |           |          |         |         |         |        |         |          |         |         |               |

# TABLE 4-15: HIGH-SPEED PWM GENERATOR 4 REGISTER MAP FOR dsPIC33FJ06GS001, dsPIC33FJ06GS101A AND dsPIC33FJ09GS302

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| <b>REGISTER 7</b>     | -9: IFS5:     | INTERRUPT        | FLAG STAT                    | US REGISTI       | ER 5             |                 |        |

|-----------------------|---------------|------------------|------------------------------|------------------|------------------|-----------------|--------|

| R/W-0                 | R/W-0         | U-0              | U-0                          | U-0              | U-0              | U-0             | U-0    |

| PWM2IF <sup>(1)</sup> | PWM1IF        |                  |                              | _                |                  |                 |        |

| bit 15                |               |                  |                              |                  |                  |                 | bit 8  |

| U-0                   | U-0           | U-0              | U-0                          | U-0              | U-0              | U-0             | R/W-0  |

| _                     |               |                  | _                            | _                | _                | _               | JTAGIF |

| bit 7                 |               |                  |                              |                  |                  |                 | bit 0  |

| Legend:               |               |                  |                              |                  |                  |                 |        |

| R = Readable          | bit           | W = Writable     | hit                          | l I = l Inimplei | mented bit, read | l as '0'        |        |

| -n = Value at F       |               | '1' = Bit is set |                              | '0' = Bit is cle |                  | x = Bit is unkr | nown   |

|                       |               |                  |                              |                  |                  |                 |        |

| bit 15                | PWM2IF: PV    | VM2 Interrupt F  | lag Status bit <sup>(*</sup> | 1)               |                  |                 |        |

|                       |               | request has oc   |                              |                  |                  |                 |        |

|                       | 0 = Interrupt | request has not  | occurred                     |                  |                  |                 |        |

| bit 14                | PWM1IF: PV    | VM1 Interrupt F  | ag Status bit                |                  |                  |                 |        |

|                       | 1 = Interrupt | request has oc   | curred                       |                  |                  |                 |        |

|                       | 0 = Interrupt | request has not  | t occurred                   |                  |                  |                 |        |

| bit 13-1              | Unimplemer    | nted: Read as '  | 0'                           |                  |                  |                 |        |

| bit 0                 | JTAGIF: JTA   | G Interrupt Flag | g Status bit                 |                  |                  |                 |        |

|                       |               | request has oc   | -                            |                  |                  |                 |        |

|                       | •             | request has not  |                              |                  |                  |                 |        |

|                       |               |                  |                              |                  |                  |                 |        |

Note 1: This bit is not implemented in dsPIC33FJ06GS001/101A devices.

#### **REGISTER 7-35: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER**

| U-0           | U-0                | U-0                                        | U-0            | R-0                 | R-0          | R-0             | R-0   |  |  |

|---------------|--------------------|--------------------------------------------|----------------|---------------------|--------------|-----------------|-------|--|--|

| —             | —                  | —                                          | —              | ILR<3:0>            |              |                 |       |  |  |

| bit 15        |                    |                                            |                |                     |              |                 | bit 8 |  |  |

|               |                    |                                            |                |                     |              |                 |       |  |  |

| U-0           | R-0                | R-0                                        | R-0            | R-0                 | R-0          | R-0             | R-0   |  |  |

| —             |                    |                                            |                | VECNUM<6:0>         |              |                 |       |  |  |

| bit 7         |                    |                                            |                |                     |              |                 | bit 0 |  |  |

|               |                    |                                            |                |                     |              |                 |       |  |  |

| Legend:       |                    |                                            |                |                     |              |                 |       |  |  |

| R = Readable  | e bit              | W = Writable b                             | it             | U = Unimpleme       | nted bit, re | ad as '0'       |       |  |  |

| -n = Value at | POR                | '1' = Bit is set                           |                | '0' = Bit is cleare | ed           | x = Bit is unkn | own   |  |  |

|               |                    |                                            |                |                     |              |                 |       |  |  |

| bit 15-12     | Unimpleme          | nted: Read as '0'                          |                |                     |              |                 |       |  |  |

| bit 11-8      | ILR<3:0>: ℕ        | lew CPU Interrupt                          | t Priority Lev | /el bits            |              |                 |       |  |  |

|               | 1111 = CPL         | J Interrupt Priority                       | Level is 15    |                     |              |                 |       |  |  |

|               | •                  |                                            |                |                     |              |                 |       |  |  |

|               | •                  |                                            |                |                     |              |                 |       |  |  |

|               | •<br>0001 = CPI    | J Interrupt Priority                       | l evel is 1    |                     |              |                 |       |  |  |

|               |                    | J Interrupt Priority                       |                |                     |              |                 |       |  |  |

| bit 7         | Unimpleme          | nted: Read as '0'                          |                |                     |              |                 |       |  |  |

| bit 6-0       | -                  | :0>: Vector Numb                           |                | ng Interrupt bits   |              |                 |       |  |  |

|               |                    | Interrupt vector pe                        |                | •                   |              |                 |       |  |  |

|               | •                  | ··· · · · · · · · · · ·                    | <b>J</b>       |                     |              |                 |       |  |  |

|               | •                  |                                            |                |                     |              |                 |       |  |  |

|               | •                  | Interruption                               | anding in Ne   | mbor 0              |              |                 |       |  |  |

|               |                    | Interrupt vector pe<br>Interrupt vector pe | •              |                     |              |                 |       |  |  |

|               | - 0000000 <b>-</b> |                                            |                |                     |              |                 |       |  |  |

### 8.4 Oscillator Control Registers

| REGISTER   | <b>、8-1: OSCC</b>                                                                            | ON: OSCILL                                                                                                                                     | ATOR CON                                                                    | TROL REGIS                          | STER                              |                                          |                    |

|------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------|-----------------------------------|------------------------------------------|--------------------|

| U-0        | R-0                                                                                          | R-0                                                                                                                                            | R-0                                                                         | U-0                                 | R/W-y                             | R/W-y                                    | R/W-y              |

|            |                                                                                              | COSC<2:0>                                                                                                                                      |                                                                             |                                     |                                   | NOSC<2:0>(2)                             |                    |

| bit 15     | ·                                                                                            |                                                                                                                                                |                                                                             |                                     |                                   |                                          | bit                |

| R/W-0      | R/W-0                                                                                        | R-0                                                                                                                                            | U-0                                                                         | R/C-0                               | U-0                               | U-0                                      | R/W-0              |

| CLKLOC     |                                                                                              | LOCK                                                                                                                                           |                                                                             | CF                                  |                                   |                                          | OSWEN              |

| bit 7      |                                                                                              | LOOK                                                                                                                                           |                                                                             | 01                                  |                                   |                                          | bit                |

|            |                                                                                              |                                                                                                                                                |                                                                             |                                     |                                   |                                          |                    |

| Legend:    |                                                                                              | •                                                                                                                                              | •                                                                           | ration bits on P                    |                                   |                                          |                    |

| R = Reada  |                                                                                              | W = Writable                                                                                                                                   |                                                                             | •                                   | mented bit, rea                   |                                          |                    |

| -n = Value | at POR                                                                                       | '1' = Bit is set                                                                                                                               |                                                                             | '0' = Bit is cl€                    | eared                             | x = Bit is unkr                          | nown               |

| bit 15     | Unimplemen                                                                                   | ted: Read as '                                                                                                                                 | 0'                                                                          |                                     |                                   |                                          |                    |

| bit 14-12  | COSC<2:0>:                                                                                   | Current Oscilla                                                                                                                                | ator Selection                                                              | bits (read-only                     | ()                                |                                          |                    |

|            | 101 = Low-Po<br>100 = Reserv<br>011 = Primar<br>010 = Primar<br>001 = Fast R                 | C Oscillator (Fl<br>ower RC Oscill<br>yed<br>y Oscillator (XT<br>y Oscillator (XT<br>C Oscillator (Fl<br>C Oscillator (Fl                      | ator (LPRC)<br>, HS, EC) wit<br>, HS, EC)<br>RC) with PLL                   | -                                   |                                   |                                          |                    |

| oit 11     | Unimplemen                                                                                   | ted: Read as '                                                                                                                                 | 0'                                                                          |                                     |                                   |                                          |                    |

| bit 10-8   | NOSC<2:0>:                                                                                   | New Oscillator                                                                                                                                 | Selection bit                                                               | S <sup>(2)</sup>                    |                                   |                                          |                    |

|            | 110 = Fast R<br>101 = Low-Po<br>100 = Reserv<br>011 = Primar<br>010 = Primar<br>001 = Fast R | C Oscillator (FI<br>C Oscillator (FI<br>ower RC Oscilla<br>red<br>y Oscillator (XT<br>y Oscillator (XT<br>C Oscillator (FI<br>C Oscillator (FI | RC) with divid<br>ator (LPRC)<br>, HS, EC) wit<br>, HS, EC)<br>RC) with PLL | le-by-16                            |                                   |                                          |                    |

| oit 7      |                                                                                              | Clock Lock Ena                                                                                                                                 |                                                                             |                                     |                                   |                                          |                    |

|            | 1 = Clock sw                                                                                 | itching is disab                                                                                                                               | led, system c                                                               | lock source is                      | locked                            | SC<7:6>) bits =                          |                    |

| oit 6      | 1 = Peripheri                                                                                |                                                                                                                                                | locked, write                                                               |                                     |                                   | sters is not allow<br>registers is allow |                    |

| oit 5      | LOCK: PLL L                                                                                  | ock Status bit (                                                                                                                               | read-only)                                                                  |                                     |                                   |                                          |                    |

|            |                                                                                              | that PLL is in I<br>that PLL is ou                                                                                                             |                                                                             |                                     |                                   | L is disabled                            |                    |

|            | Writes to this regis<br>in the <i>"dsPIC33F/</i> F                                           |                                                                                                                                                |                                                                             |                                     |                                   | cillator (Part IV                        | <b>)"</b> (DS70307 |

| 2:         | Direct clock switch<br>ted. This applies to<br>FRC mode as a tra                             | es between an<br>clock switche                                                                                                                 | y Primary Os<br>s in either dire                                            | cillator mode w<br>ection. In these | vith PLL and Fl<br>instances, the |                                          |                    |

|            | This register is res                                                                         |                                                                                                                                                |                                                                             |                                     |                                   |                                          |                    |

### **REGISTER 8-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup>

3: This register is reset only on a Power-on Reset (POR).

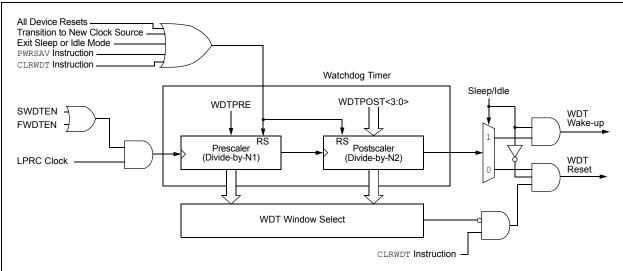

#### 8.6 Fail-Safe Clock Monitor (FSCM)

The Fail-Safe Clock Monitor (FSCM) allows the device to continue to operate, even in the event of an oscillator failure. The FSCM function is enabled by programming. If the FSCM function is enabled, the LPRC internal oscillator runs at all times (except during Sleep mode) and is not subject to control by the Watchdog Timer.

In the event of an oscillator failure, the FSCM generates a clock failure trap event and switches the system clock over to the FRC oscillator. Then, the application program can either attempt to restart the oscillator or execute a controlled shutdown. The trap can be treated as a warm Reset by simply loading the Reset address into the oscillator fail trap vector.

If the PLL multiplier is used to scale the system clock, the internal FRC is also multiplied by the same factor on clock failure. Essentially, the device switches to FRC with PLL on a clock failure.

#### 8.7 Pseudo-Random Generator

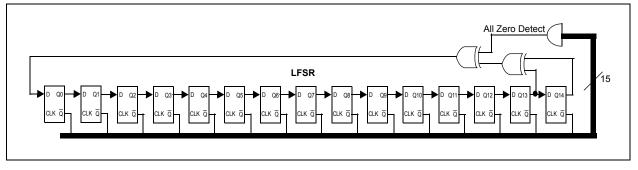

The pseudo-random generator is implemented with a 15-bit Linear Feedback Shift Register (LFSR), which is a shift register with a few exclusive OR gates. The shift register is clocked by the PWM clock and is a read-only register. The purpose of this feature is to provide the ability to randomly change the period or the active portion of the PWM.

A firmware routine can be used to read "n" random bits from the LFSR register and combine them, by either summing or performing another logical operation with the PWM period of the Duty Cycle registers. The result will be a PWM signal whose nominal period (or duty cycle) is the desired one, but whose effective value changes randomly. This capability will help in reducing the EMI/EMC emissions by spreading the power over a wider frequency range.

Figure 8-3 provides a block diagram of the LFSR.

|               |                     |                  | -              | -                |                 |                   |       |

|---------------|---------------------|------------------|----------------|------------------|-----------------|-------------------|-------|

| U-0           | U-0                 | R/W-1            | R/W-1          | R/W-1            | R/W-1           | R/W-1             | R/W-1 |

| _             |                     |                  |                | T1Cł             | <r<5:0></r<5:0> |                   |       |

| bit 15        |                     | •                |                |                  |                 |                   | bit 8 |

|               |                     |                  |                |                  |                 |                   |       |

| U-0           | U-0                 | U-0              | U-0            | U-0              | U-0             | U-0               | U-0   |

| —             | —                   | —                |                | _                | —               | —                 | —     |

| bit 7         |                     |                  |                |                  |                 |                   | bit C |

|               |                     |                  |                |                  |                 |                   |       |

| Legend:       |                     |                  |                |                  |                 |                   |       |

| R = Readabl   | le bit              | W = Writable     | bit            | U = Unimple      | mented bit, rea | d as '0'          |       |

| -n = Value at | t POR               | '1' = Bit is set |                | '0' = Bit is cle | ared            | x = Bit is unkr   | nown  |

|               |                     |                  |                |                  |                 |                   |       |

| bit 15-14     | Unimplemen          | ted: Read as '   | )'             |                  |                 |                   |       |

| bit 13-8      | T1CKR<5:0>          | : Assign Timer   | 1 External Clo | ock (T1CK) to t  | he Correspond   | ling RPn Pin bits | 6     |

|               | 111111 <b>= Inp</b> | out tied to Vss  |                |                  |                 |                   |       |

|               | 100011 <b>= Inp</b> | out tied to RP35 | 5              |                  |                 |                   |       |

|               |                     | out tied to RP34 |                |                  |                 |                   |       |

|               |                     | out tied to RP33 |                |                  |                 |                   |       |

|               | 100000 <b>= Inp</b> | out tied to RP32 | 2              |                  |                 |                   |       |

|               | •                   |                  |                |                  |                 |                   |       |

|               | •                   |                  |                |                  |                 |                   |       |

|               | •                   |                  |                |                  |                 |                   |       |

|               | 00000 <b>= Inpu</b> | it tied to RP0   |                |                  |                 |                   |       |

| bit 7-0       | Unimplemen          | ted: Read as '   | )'             |                  |                 |                   |       |

|               | -                   |                  |                |                  |                 |                   |       |

| U-0           | U-0                 | R/W-1             | R/W-1          | R/W-1            | R/W-1                 | R/W-1                      | R/W-1 |

|---------------|---------------------|-------------------|----------------|------------------|-----------------------|----------------------------|-------|

| —             | —                   |                   |                | SCK1F            | R<5:0> <sup>(1)</sup> |                            |       |

| bit 15        |                     |                   |                |                  |                       |                            | bit 8 |

|               |                     |                   |                |                  |                       |                            |       |

| U-0           | U-0                 | R/W-1             | R/W-1          | R/W-1            | R/W-1                 | R/W-1                      | R/W-1 |

|               |                     |                   |                | SDI1R            | <5:0> <sup>(1)</sup>  |                            |       |

| bit 7         |                     |                   |                |                  |                       |                            | bit ( |

|               |                     |                   |                |                  |                       |                            |       |

| Legend:       |                     |                   |                |                  |                       |                            |       |

| R = Readabl   |                     | W = Writable      |                | •                | mented bit, read      | d as '0'                   |       |

| -n = Value at | t POR               | '1' = Bit is set  |                | '0' = Bit is cle | ared                  | x = Bit is unkr            | nown  |

| L:1 4 5 4 4   |                     | ta da Da a da a ( | ~ '            |                  |                       |                            |       |

| bit 15-14     | -                   | ted: Read as '    |                |                  |                       | (4)                        |       |

| bit 13-8      | SCK1R<5:0>          | : Assign SPI1     | Clock Input (S | CK1) to the Co   | prresponding R        | Pn Pin bits <sup>(1)</sup> |       |

|               | 111111 <b>= Inp</b> |                   |                |                  |                       |                            |       |

|               |                     | out tied to RP3   |                |                  |                       |                            |       |

|               |                     | out tied to RP34  |                |                  |                       |                            |       |

|               |                     | out tied to RP3   |                |                  |                       |                            |       |

|               |                     | out tied to RP32  | 2              |                  |                       |                            |       |

|               | •                   |                   |                |                  |                       |                            |       |

|               | •                   |                   |                |                  |                       |                            |       |

|               | 00000 <b>= Inpu</b> | t tied to RP0     |                |                  |                       |                            |       |

| bit 7-6       |                     | ted: Read as '    | 0'             |                  |                       |                            |       |

| bit 5-0       | -                   |                   |                | 11) to the Corre | esponding RPn         | Pin bits <sup>(1)</sup>    |       |

|               | 111111 = Inp        |                   |                |                  | sepending rain        |                            |       |

|               |                     | out tied to RP3   | 5              |                  |                       |                            |       |

|               |                     | out tied to RP34  |                |                  |                       |                            |       |

|               |                     | out tied to RP33  |                |                  |                       |                            |       |

|               |                     | out tied to RP32  |                |                  |                       |                            |       |

|               | •                   |                   |                |                  |                       |                            |       |

|               | •                   |                   |                |                  |                       |                            |       |

|               | •                   |                   |                |                  |                       |                            |       |

|               | 00000 <b>= Inpu</b> | t tied to RPO     |                |                  |                       |                            |       |

|               | 00000 <b>– mpu</b>  |                   |                |                  |                       |                            |       |

#### REGISTER 10-8: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

**Note 1:** These bits are not implemented in the dsPIC33FJ06GS001 device.

| U-0                | U-0                                                                                                                       | R/W-1                                                                                                                                                                      | R/W-1                              | R/W-1                       | R/W-1            | R/W-1           | R/W-1 |

|--------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------------|------------------|-----------------|-------|

| _                  | —                                                                                                                         |                                                                                                                                                                            |                                    | FLT7                        | R<5:0>           |                 |       |

| bit 15             |                                                                                                                           |                                                                                                                                                                            |                                    |                             |                  |                 | bit 8 |

|                    |                                                                                                                           |                                                                                                                                                                            |                                    |                             |                  |                 |       |

| U-0                | U-0                                                                                                                       | R/W-1                                                                                                                                                                      | R/W-1                              | R/W-1                       | R/W-1            | R/W-1           | R/W-1 |

| _                  | —                                                                                                                         |                                                                                                                                                                            |                                    | FLT6                        | R<5:0>           |                 |       |

| bit 7              |                                                                                                                           |                                                                                                                                                                            |                                    |                             |                  |                 | bit ( |

| Legend:            |                                                                                                                           |                                                                                                                                                                            |                                    |                             |                  |                 |       |

| R = Readab         | le bit                                                                                                                    | W = Writable I                                                                                                                                                             | oit                                | U = Unimplen                | nented bit, read | d as '0'        |       |

| -n = Value a       | t POR                                                                                                                     | '1' = Bit is set                                                                                                                                                           |                                    | '0' = Bit is clea           |                  | x = Bit is unkr | nown  |

|                    |                                                                                                                           |                                                                                                                                                                            |                                    |                             |                  |                 |       |

| bit 15-14          | Unimpleme                                                                                                                 | nted: Read as '(                                                                                                                                                           | )'                                 |                             |                  |                 |       |

| bit 13-8           | •                                                                                                                         | : Assign PWM F                                                                                                                                                             |                                    | =I T7) to the Co            | orresponding R   | Pn Pin hits     |       |

|                    |                                                                                                                           | put tied to Vss                                                                                                                                                            |                                    |                             | incoponding is   |                 |       |

|                    |                                                                                                                           | put tied to RP35                                                                                                                                                           |                                    |                             |                  |                 |       |

|                    |                                                                                                                           |                                                                                                                                                                            |                                    |                             |                  |                 |       |

|                    | 100010 <b>= ln</b>                                                                                                        | put tied to RP34                                                                                                                                                           |                                    |                             |                  |                 |       |

|                    |                                                                                                                           | put tied to RP34<br>put tied to RP33                                                                                                                                       |                                    |                             |                  |                 |       |

|                    | 100001 <b>= In</b>                                                                                                        |                                                                                                                                                                            | 1                                  |                             |                  |                 |       |

|                    | 100001 <b>= In</b>                                                                                                        | put tied to RP33                                                                                                                                                           | 1                                  |                             |                  |                 |       |

|                    | 100001 <b>= In</b>                                                                                                        | put tied to RP33                                                                                                                                                           | 1                                  |                             |                  |                 |       |

|                    | 100001 <b>= In</b>                                                                                                        | put tied to RP33                                                                                                                                                           | 1                                  |                             |                  |                 |       |

|                    | 100001 = In<br>100000 = In<br>•                                                                                           | put tied to RP33<br>put tied to RP32                                                                                                                                       | 1                                  |                             |                  |                 |       |

| bit 7-6            | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>00000 = Inp                                                                  | put tied to RP33<br>put tied to RP32<br>ut tied to RP0                                                                                                                     |                                    |                             |                  |                 |       |

| bit 7-6            | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | put tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0                                                                                                 | ;<br>;<br>;                        | ELT6) to the Co             | prresponding P   | PDn Din hits    |       |

| bit 7-6<br>bit 5-0 | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | put tied to RP33<br>put tied to RP32<br>ut tied to RP0<br><b>nted:</b> Read as '0<br>:: Assign PWM F                                                                       | ;<br>;<br>;                        | FLT6) to the Co             | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | put tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss                                                            | <sub>)</sub> ,<br>Fault Input 6 (I | FLT6) to the Co             | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | put tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35                                        | ) <sup>)</sup><br>Fault Input 6 (I | FLT6) to the Co             | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34                     | ) <sup>)</sup><br>Fault Input 6 (I | <sup>-</sup> LT6) to the Co | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33 | o'<br>Fault Input 6 (I             | <sup>-</sup> LT6) to the Co | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34                     | o'<br>Fault Input 6 (I             | <sup>-</sup> LT6) to the Co | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33 | o'<br>Fault Input 6 (I             | <sup>-</sup> LT6) to the Co | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33 | o'<br>Fault Input 6 (I             | FLT6) to the Co             | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33 | o'<br>Fault Input 6 (I             | <sup>=</sup> LT6) to the Co | prresponding R   | Pn Pin bits     |       |

#### REGISTER 10-13: RPINR32: PERIPHERAL PIN SELECT INPUT REGISTER 32

| U-0                                                                  | U-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0                | R/W-0           | R/W-0 |

|----------------------------------------------------------------------|-----|------------------|-------|------------------|----------------------|-----------------|-------|

| —                                                                    | _   |                  |       | RP9R             | <5:0> <sup>(1)</sup> |                 |       |

| bit 15                                                               |     |                  |       |                  |                      |                 | bit 8 |

|                                                                      |     |                  |       |                  |                      |                 |       |

| U-0                                                                  | U-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0                | R/W-0           | R/W-0 |

|                                                                      | _   |                  |       | RP8R             | <5:0> <sup>(1)</sup> |                 |       |

| bit 7                                                                |     |                  |       |                  |                      |                 | bit 0 |

|                                                                      |     |                  |       |                  |                      |                 |       |

| Legend:                                                              |     |                  |       |                  |                      |                 |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |     |                  |       |                  |                      |                 |       |

| -n = Value at F                                                      | POR | '1' = Bit is set |       | '0' = Bit is cle | ared                 | x = Bit is unkr | nown  |

#### **REGISTER 10-20: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4**

| bit 15-14 | Unimplemented: Read as '0'                                                                           |

|-----------|------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP9R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP9 Output Pin bits <sup>(1)</sup> |

|           | (see Table 10-2 for peripheral function numbers)                                                     |

| bit 7-6   | Unimplemented: Read as '0'                                                                           |

| bit 5-0   | <b>RP8R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP8 Output Pin bits <sup>(1)</sup> |

|           | (see Table 10-2 for peripheral function numbers)                                                     |

Note 1: These bits are not implemented in dsPIC33FJ06GS001/101A devices.

#### **REGISTER 10-21: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5**

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0                | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|----------------------|-------|-------|

| —      |     |       |       | RP11F | <5:0> <sup>(1)</sup> |       |       |

| bit 15 |     |       |       |       |                      |       | bit 8 |

|        |     |       |       |       |                      |       |       |

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0                | R/W-0 | R/W-0 |

|        |     |       |       | RP10F | <5:0> <sup>(1)</sup> |       |       |

| bit 7  |     |       |       |       |                      |       | bit 0 |

|        |     |       |       |       |                      |       |       |

| Legend:                           |                  |                        |                    |

|-----------------------------------|------------------|------------------------|--------------------|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

- RP11R<5:0>: Peripheral Output Function is Assigned to RP11 Output Pin bits<sup>(1)</sup> bit 13-8 (see Table 10-2 for peripheral function numbers) bit 7-6 Unimplemented: Read as '0'

- RP10R<5:0>: Peripheral Output Function is Assigned to RP10 Output Pin bits<sup>(1)</sup> bit 5-0 (see Table 10-2 for peripheral function numbers)

Note 1: These bits are not implemented in dsPIC33FJ06GS001/101A devices.

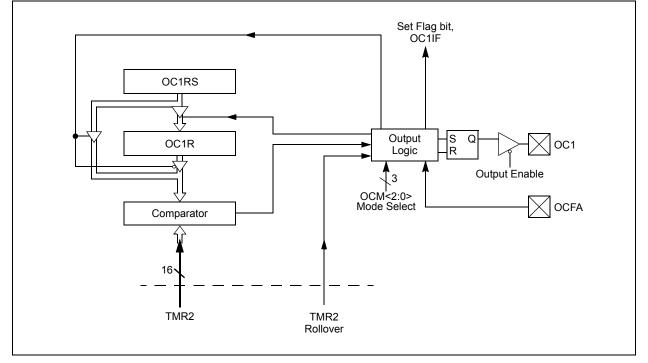

### 14.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS001/101A/102A/ 202A and dsPIC33FJ09GS302 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 13. "Output Compare" (DS70209) in the "dsPIC33F/ PIC24H Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The output compare module can select either Timer1 or Timer2 for its time base. The module compares the value of the timer with the value of one or two Compare registers, depending on the operating mode selected. The state of the output pin changes when the timer value matches the Output Compare register value. The output compare module generates either a single output pulse, or a sequence of output pulses, by changing the state of the output pin on the compare match events. The output compare module can also generate interrupts on compare match events.

The output compare module has multiple operating modes:

- Active-Low One-Shot mode

- Active-High One-Shot mode

- Toggle mode

- · Delayed One-Shot mode

- Continuous Pulse mode

- PWM mode without Fault Protection

- PWM mode with Fault Protection

| Note: | The out  | put co  | mpare   | module   | is  | not  |

|-------|----------|---------|---------|----------|-----|------|

|       | implemer | nted in | the dsF | PIC33FJ0 | 6GS | 6001 |

|       | device.  |         |         |          |     |      |

If a Fault condition is detected on the OCFA pin, the output pin(s) of the output compare module are placed in tri-state. The user may elect to use a pull-down or pull-up resistor on the PWM pin to provide for a desired state if a Fault condition occurs.

#### FIGURE 14-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

#### **15.2 Feature Description**

The PWM module is designed for applications that require:

- High-resolution at high PWM frequencies

- The ability to drive Standard, Edge-Aligned, Center-Aligned Complementary mode, and Push-Pull mode outputs

- · The ability to create multiphase PWM outputs

For Center-Aligned mode, the duty cycle, period, phase and dead-time resolutions will be 8.32 ns.

Two common, medium power converter topologies are push-pull and half-bridge. These designs require the PWM output signal to be switched between alternate pins, as provided by the Push-Pull PWM mode.

A phase-shifted PWM describes the situation where each PWM generator provides outputs, but the phase relationship between the generator outputs is specifiable and changeable. A multiphase PWM is often used to improve DC/DC Converter load transient response, and reduce the size of output filter capacitors and inductors. Multiple DC/DC Converters are often operated in parallel, but phase-shifted in time. A single PWM output, operating at 250 kHz, has a period of 4  $\mu$ s, but an array of four PWM channels staggered by 1  $\mu$ s each, yields an effective switching frequency of 1 MHz. Multiphase PWM applications typically use a fixed-phase relationship.

A variable phase PWM is useful in Zero Voltage Transition (ZVT) power converters. Here, the PWM duty cycle is always 50%, and the power flow is controlled by varying the relative phase-shift between the two PWM generators.

#### REGISTER 15-15: FCLCONX: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER (CONTINUED)

bit 7-3

**FLTSRC<4:0>:** Fault Control Signal Source Select for PWM Generator # bits<sup>(2,3)</sup>

- .

- .

- •

- 01000 = Reserved

- 00111 = Fault 8 00110 = Fault 7 00101 = Fault 6 00100 = Fault 5 00011 = Fault 4 00010 = Fault 3

- 00001 = Fault 2 00000 = Fault 1

- bit 2 **FLTPOL:** Fault Polarity for PWMx Generator # bit<sup>(1)</sup>

- 1 = The selected Fault source is active-low

- 0 = The selected Fault source is active-high

bit 1-0 **FLTMOD<1:0>:** Fault Mode for PWMx Generator # bits

- 11 = Fault input is disabled

- 10 = Reserved

- 01 = The selected Fault source forces PWMxH, PWMxL pins to FLTDAT values (cycle)

- 00 = The selected Fault source forces PWMxH, PWMxL pins to FLTDAT values (latched condition)

- **Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

- 2: When Independent Fault mode is enabled (IFLTMOD<1:0> = 1), and Fault 1 is used for Current-Limit mode (CLSRC<4:0> = b0000), the Fault Control Source Select bits (FLTSRC<4:0>) should be set to an unused Fault source to prevent Fault 1 from disabling both the PWMxL and PWMxH outputs.

- 3: When Independent Fault mode is enabled (IFLTMOD<1:0> = 1) and Fault 1 is used for Fault mode (FLTSRC<4:0> = b0000), the Current-Limit Control Source Select bits (CLSRC<4:0>) should be set to an unused current-limit source to prevent the current-limit source from disabling both the PWMxH and PWMxL outputs.

| REGISTE      | R 17-2: I20                     | C1STAT: I2C1                                         | STATUS RE                  | GISTER                         |                               |                  |           |

|--------------|---------------------------------|------------------------------------------------------|----------------------------|--------------------------------|-------------------------------|------------------|-----------|

| R-0, HSC     | R-0, HSC                        | U-0                                                  | U-0                        | U-0                            | R/C-0, HSC                    | R-0, HSC         | R-0, HSC  |

| ACKSTAT      | TRSTAT                          |                                                      |                            | _                              | BCL                           | GCSTAT           | ADD10     |

| bit 15       |                                 |                                                      |                            |                                | •                             |                  | bit 8     |

|              |                                 |                                                      |                            |                                |                               |                  |           |

| R/C-0, HS    | R/C-0, HS                       | R-0, HSC                                             | R/C-0, HSC                 | R/C-0, HSC                     | R-0, HSC                      | R-0, HSC         | R-0, HSC  |

| IWCOL        | I2COV                           | D_A                                                  | Р                          | S                              | R_W                           | RBF              | TBF       |

| bit 7        |                                 |                                                      |                            |                                |                               |                  | bit 0     |

| Legend:      |                                 | HS - Hardwa                                          | re Settable biť            | HSC - Hardward                 | e Settable/Clearab            | le hit           |           |

| R = Reada    | blo bit                         | W = Writable I                                       |                            |                                | ited bit, read as '0'         |                  | hit       |

|              |                                 |                                                      | JIL                        | •                              |                               |                  |           |

| -n = Value a | at POR                          | '1' = Bit is set                                     |                            | '0' = Bit is cleare            | a                             | x = Bit is unkr  | IOWN      |

| bit 15       | (when operat<br>1 = NACK is     | received from s                                      | ter, applicable t<br>slave | o master transmi               | t operation)                  |                  |           |

|              |                                 | ceived from sla                                      |                            |                                |                               |                  |           |

| bit 14       |                                 |                                                      | end of slave Ack           |                                | applicable to ma              | etor transmit o  | poration) |