Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 6КВ (2К х 24)                                                                    |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b; D/A 2x10b                                                             |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 36-VFTLA Exposed Pad                                                             |

| Supplier Device Package    | 36-VTLA (5x5)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs202a-e-tl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the dsPIC33FJ06GS001/101A/102A/202A and dsPIC33FJ09GS302 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual". Please see the Microchip web site (www.microchip.com) for the latest "dsPIC33F/PIC24H Family Reference Manual" sections.

This document contains device-specific information for the following dsPIC33F Digital Signal Controller (DSC) devices:

- dsPIC33FJ06GS001

- dsPIC33FJ06GS101A

- dsPIC33FJ06GS102A

- dsPIC33FJ06GS202A

- dsPIC33FJ09GS302

The dsPIC33FJ06GS001/101A/102A/202A and dsPIC33FJ09GS302 devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit microcontroller (MCU) architecture.

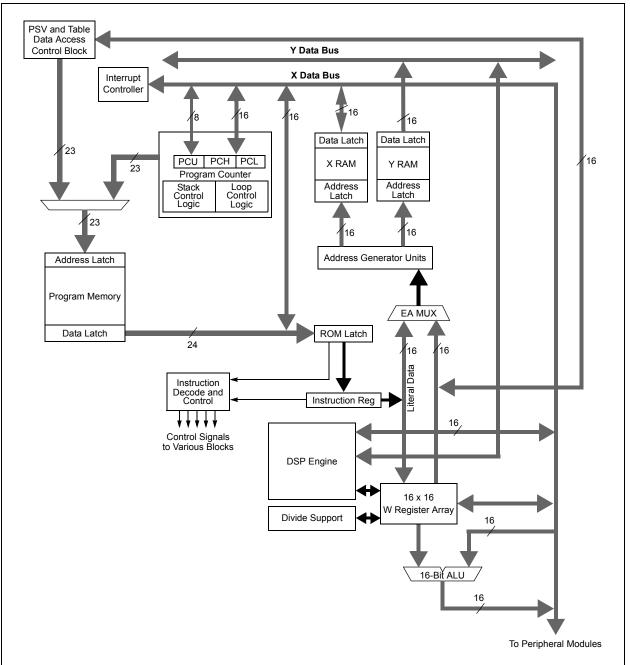

Figure 1-1 shows a general block diagram of the core and peripheral modules in the devices. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

## 3.3 Special MCU Features

A 17-bit by 17-bit single-cycle multiplier is shared by both the MCU ALU and DSP engine. The multiplier can perform signed, unsigned and mixed-sign multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication not only allows you to perform mixed-sign multiplication, it also achieves accurate results for special operations, such as (-1.0) x (-1.0). The 16/16 and 32/16 divide operations are supported, both fractional and integer. All divide instructions are iterative operations. They must be executed within a REPEAT loop, resulting in a total execution time of 19 instruction cycles. The divide operation can be interrupted during any of those 19 cycles without loss of data.

A 40-bit barrel shifter is used to perform up to a 16-bit left or right shift in a single cycle. The barrel shifter can be used by both MCU and DSP instructions.

# FIGURE 3-1: CPU CORE BLOCK DIAGRAM

# 4.3 Special Function Register Maps

### TABLE 4-1: CPU CORE REGISTER MAP

| IABLE 4-1 | 1:          |          | LE KEGI  |          |          |          |           |                 |              |       |         |          |               |           |           |           |       |               |

|-----------|-------------|----------|----------|----------|----------|----------|-----------|-----------------|--------------|-------|---------|----------|---------------|-----------|-----------|-----------|-------|---------------|

| SFR Name  | SFR<br>Addr | Bit 15   | Bit 14   | Bit 13   | Bit 12   | Bit 11   | Bit 10    | Bit 9           | Bit 8        | Bit 7 | Bit 6   | Bit 5    | Bit 4         | Bit 3     | Bit 2     | Bit 1     | Bit 0 | All<br>Resets |

| WREG0     | 0000        |          |          |          |          |          | V         | Vorking Regist  | er 0         |       |         |          |               |           |           |           |       | 0000          |

| WREG1     | 0002        |          |          |          |          |          | V         | Vorking Regist  | er 1         |       |         |          |               |           |           |           |       | 0000          |

| WREG2     | 0004        |          |          |          |          |          | V         | Vorking Regist  | er 2         |       |         |          |               |           |           |           |       | 0000          |

| WREG3     | 0006        |          |          |          |          |          | V         | Vorking Regist  | er 3         |       |         |          |               |           |           |           |       | 0000          |

| WREG4     | 0008        |          |          |          |          |          | V         | Vorking Regist  | er 4         |       |         |          |               |           |           |           |       | 0000          |

| WREG5     | 000A        |          |          |          |          |          | V         | Vorking Regist  | er 5         |       |         |          |               |           |           |           |       | 0000          |

| WREG6     | 000C        |          |          |          |          |          | V         | Vorking Regist  | er 6         |       |         |          |               |           |           |           |       | 0000          |

| WREG7     | 000E        |          |          |          |          |          | V         | Vorking Regist  | er 7         |       |         |          |               |           |           |           |       | 0000          |

| WREG8     | 0010        |          |          |          |          |          | V         | Vorking Regist  | er 8         |       |         |          |               |           |           |           | ,     | 0000          |

| WREG9     | 0012        |          |          |          |          |          | V         | Vorking Regist  | er 9         |       |         |          |               |           |           |           |       | 0000          |

| WREG10    | 0014        |          |          |          |          |          | W         | orking Registe  | er 10        |       |         |          |               |           |           |           | ,     | 0000          |

| WREG11    | 0016        |          |          |          |          |          | W         | /orking Registe | er 11        |       |         |          |               |           |           |           | ,     | 0000          |

| WREG12    | 0018        |          |          |          |          |          | W         | orking Registe  | er 12        |       |         |          |               |           |           |           |       | 0000          |

| WREG13    | 001A        |          |          |          |          |          | W         | orking Registe  | er 13        |       |         |          |               |           |           |           | ,     | 0000          |

| WREG14    | 001C        |          |          |          |          |          | W         | orking Registe  | er 14        |       |         |          |               |           |           |           |       | 0000          |

| WREG15    | 001E        |          |          |          |          |          | W         | orking Registe  | er 15        |       |         |          |               |           |           |           | ,     | 0800          |

| SPLIM     | 0020        |          |          |          |          |          | Stack     | Pointer Limit   | Register     |       |         |          |               |           |           |           | ,     | XXXX          |

| ACCAL     | 0022        |          |          |          |          |          |           | ACCAL           |              |       |         |          |               |           |           |           |       | XXXX          |

| ACCAH     | 0024        |          |          |          |          |          |           | ACCAH           |              |       |         |          |               |           |           |           | ,     | XXXX          |

| ACCAU     | 0026        | ACCA<39> | ACCA<39> | ACCA<39> | ACCA<39> | ACCA<39> | ACCA<39>  | ACCA<39>        | ACCA<39>     |       |         |          | ACCA          | Ú         |           |           |       | XXXX          |

| ACCBL     | 0028        |          |          |          |          |          |           | ACCBL           |              | •     |         |          |               |           |           |           | ,     | XXXX          |

| ACCBH     | 002A        |          |          |          |          |          |           | ACCBH           |              |       |         |          |               |           |           |           |       | XXXX          |

| ACCBU     | 002C        | ACCB<39> | ACCB<39> | ACCB<39> | ACCB<39> | ACCB<39> | ACCB<39>  | ACCB<39>        | ACCB<39>     |       |         |          | ACCB          | U         |           |           |       | XXXX          |

| PCL       | 002E        |          |          |          |          | •        | Program C | Counter Low W   | ord Register | r     |         |          |               |           |           |           |       | 0000          |

| PCH       | 0030        | _        | _        | _        | _        | _        | _         | _               | _            |       |         | Program  | Counter Hig   | gh Byte I | Register  |           |       | 0000          |

| TBLPAG    | 0032        | _        | _        | _        | _        | _        | _         | _               | _            |       |         | Table Pa | ge Address    | Pointer I | Register  |           |       | 0000          |

| PSVPAG    | 0034        | _        | _        | _        | _        | _        | _         | _               | _            |       | Program | Memory V | isibility Pag | e Addres  | ss Pointe | er Regist | er    | 0000          |

| RCOUNT    | 0036        |          |          |          |          |          | Repea     | t Loop Counte   | r Register   |       |         |          |               |           |           |           |       | XXXX          |

| DCOUNT    | 0038        |          |          |          |          |          |           | DCOUNT<15:      | 0>           |       |         |          |               |           |           |           |       | XXXX          |

| DOSTARTL  | 003A        |          |          |          |          |          | DOST      | TARTL<15:1>     |              |       |         |          |               |           |           |           | 0     | XXXX          |

| DOSTARTH  | 003C        | —        | —        | _        | _        | _        | _         | _               | —            | —     | —       |          | DC            | START     | H<5:0>    |           |       | 00xx          |

| DOENDL    | 003E        |          |          |          |          |          | DOE       | NDL<15:1>       |              |       |         |          |               |           |           |           | 0     | XXXX          |

| DOENDH    | 0040        | —        | —        | _        | _        | _        | _         | _               | —            | —     | —       |          |               | DOEN      | DH        |           |       | 00xx          |

|           | 0042        | OA       | OB       | SA       | SB       | 1        |           | -               |              |       | IPL<2:0 |          | 1             |           | -         | -         |       | +             |

dsPIC33FJ06GS001/101A/102A/202A and dsPIC33FJ09GS302

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-22: HIGH-SPEED 10-BIT ADC REGISTER MAP FOR dsPIC33FJ09GS302

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14               | Bit 13 | Bit 12  | Bit 11 | Bit 10    | Bit 9 | Bit 8  | Bit 7        | Bit 6 | Bit 5   | Bit 4     | Bit 3 | Bit 2    | Bit 1   | Bit 0 | All<br>Resets |

|----------|-------------|--------|----------------------|--------|---------|--------|-----------|-------|--------|--------------|-------|---------|-----------|-------|----------|---------|-------|---------------|

| ADCON    | 0300        | ADON   | —                    | ADSIDL | SLOWCLK | —      | GSWTRG    | _     | FORM   | EIE          | ORDER | SEQSAMP | ASYNCSAMP | —     | A        | DCS<2:0 | >     | 0003          |

| ADPCFG   | 0302        | _      | —                    | _      | —       | -      | —         | _     | _      | PCFG7        | PCFG6 | PCFG5   | PCFG4     | PCFG3 | PCFG2    | PCFG1   | PCFG0 | 0000          |

| ADSTAT   | 0306        |        | —                    | —      | —       |        | _         | _     | —      | _            | P6RDY | —       | —         | P3RDY | P2RDY    | P1RDY   | PORDY | 0000          |

| ADBASE   | 0308        |        |                      |        |         |        |           | Α     | DBASE< | 15:1>        |       |         |           |       |          |         | _     | 0000          |

| ADCPC0   | 030A        | IRQEN1 | PEND1                | SWTRG1 |         | TRO    | SRC1<4:0> |       |        | IRQEN0       | PEND0 | SWTRG0  |           | TRGS  | RC0<4:0> |         |       | 0000          |

| ADCPC1   | 030C        | IRQEN3 | PEND3                | SWTRG3 |         | TRO    | SRC3<4:0> |       |        | IRQEN2       | PEND2 | SWTRG2  |           | TRGS  | RC2<4:0> |         |       | 0000          |

| ADCPC3   | 0310        |        | —                    | —      | _       |        | _         | _     | —      | IRQEN6       | PEND6 | SWTRG6  |           | TRGS  | RC6<4:0> |         |       | 0000          |

| ADCBUF0  | 0320        |        |                      |        |         |        |           |       | ADC Da | ata Buffer 0 |       |         |           |       |          |         |       | XXXX          |

| ADCBUF1  | 0322        |        |                      |        |         |        |           |       | ADC Da | ata Buffer 1 |       |         |           |       |          |         |       | XXXX          |

| ADCBUF2  | 0324        |        |                      |        |         |        |           |       | ADC Da | ata Buffer 2 |       |         |           |       |          |         |       | XXXX          |

| ADCBUF3  | 0326        |        |                      |        |         |        |           |       | ADC Da | ata Buffer 3 |       |         |           |       |          |         |       | XXXX          |

| ADCBUF4  | 0328        |        |                      |        |         |        |           |       | ADC Da | ata Buffer 4 |       |         |           |       |          |         |       | XXXX          |

| ADCBUF5  | 032A        |        |                      |        |         |        |           |       | ADC Da | ata Buffer 5 |       |         |           |       |          |         |       | XXXX          |

| ADCBUF6  | 032C        |        | ADC Data Buffer 6    |        |         |        |           |       |        |              | XXXX  |         |           |       |          |         |       |               |

| ADCBUF7  | 032E        |        | ADC Data Buffer 7    |        |         |        |           |       |        |              | xxxx  |         |           |       |          |         |       |               |

| ADCBUF12 | 0338        |        | ADC Data Buffer 12   |        |         |        |           |       |        |              | xxxx  |         |           |       |          |         |       |               |

| ADCBUF13 | 033A        |        | ADC Data Buffer 13 x |        |         |        |           |       |        | xxxx         |       |         |           |       |          |         |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-23: ANALOG COMPARATOR CONTROL REGISTER MAP FOR dsPIC33FJ06GS001, dsPIC33FJ06GS202A AND dsPIC33FJ09GS302

| File Name | ADR  | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11  | Bit 10 | Bit 9      | Bit 8                | Bit 7 | Bit 6  | Bit 5  | Bit 4   | Bit 3   | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|---------|--------|---------|--------|------------|----------------------|-------|--------|--------|---------|---------|-------|--------|-------|---------------|

| CMPCON1   | 0540 | CMPON  | _      | CMPSIDL | HYSSI  | EL<1:0> | FLTREN | FCLKSEL    | DACOE <sup>(1)</sup> | INSEL | .<1:0> | EXTREF | HYSPOL  | CMPSTAT | HGAIN | CMPPOL | RANGE | 0000          |

| CMPDAC1   | 0542 | _      | _      | _       | _      | _       | _      |            |                      |       |        | CMR    | EF<9:0> |         |       |        |       | 0000          |

| CMPCON2   | 0544 | CMPON  | _      | CMPSIDL | HYSSI  | EL<1:0> | FLTREN | FCLKSEL    | DACOE <sup>(1)</sup> | INSEL | .<1:0> | EXTREF | HYSPOL  | CMPSTAT | HGAIN | CMPPOL | RANGE | 0000          |

| CMPDAC2   | 0546 | —      | _      | _       | _      | _       | _      | CMREF<9:0> |                      |       |        |        |         | 0000    |       |        |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note 1:** This bit is not available in the dsPIC33FJ06GS001 device.

# **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 1 BOR: Brown-out Reset Flag bit

- 1 = A Brown-out Reset has occurred

- 0 = A Brown-out Reset has not occurred

### bit 0 POR: Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

# 7.4 Interrupt Setup Procedures

### 7.4.1 INITIALIZATION

Complete the following steps to configure an interrupt source at initialization:

- 1. Set the NSTDIS bit (INTCON1<15>) if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level will depend on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits for all enabled interrupt sources can be programmed to the same non-zero value.

**Note:** At a device Reset, the IPCx registers are initialized such that all user interrupt sources are assigned to Priority Level 4.

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

# 7.4.2 INTERRUPT SERVICE ROUTINE

The method used to declare an ISR and initialize the IVT with the correct vector address depends on the programming language (C or assembler) and the language development toolsuite used to develop the application.

In general, the user application must clear the interrupt flag in the appropriate IFSx register for the source of the interrupt that the ISR handles; otherwise, the program will re-enter the ISR immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and the old CPU priority level.

# 7.4.3 TRAP SERVICE ROUTINE

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

### 7.4.4 INTERRUPT DISABLE

The following steps outline the procedure to disable all user interrupts:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to Priority Level 7 by inclusive ORing the value, 0xE0 with SRL.

To enable user interrupts, the POP instruction can be used to restore the previous SR value.

| Note: | Only user interrupts with a priority level of |

|-------|-----------------------------------------------|

|       | 7 or lower can be disabled. Trap sources      |

|       | (Level 8-Level 15) cannot be disabled.        |

The DISI instruction provides a convenient way to disable interrupts of Priority Levels 1-6 for a fixed period of time. Level 7 interrupt sources are not disabled by the DISI instruction.

# 8.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS001/101A/102A/ 202A and dsPIC33FJ09GS302 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 42. "Oscillator (Part IV)" (DS70307) in the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

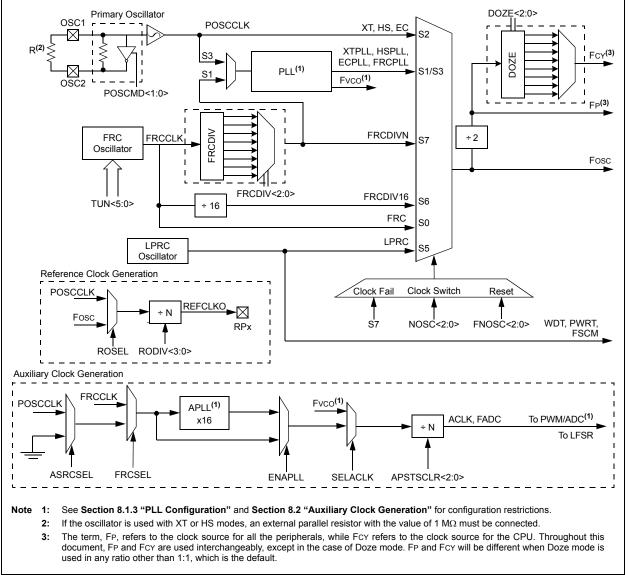

The oscillator system provides:

- External and internal oscillator options as clock sources

- An on-chip Phase Lock Loop (PLL) to scale the internal operating frequency to the required system clock frequency

- An internal FRC oscillator that can also be used with the PLL, thereby allowing full-speed operation without any external clock generation hardware

- · Clock switching between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- An Oscillator Control register (OSCCON)

- Nonvolatile Configuration bits for main oscillator selection

- An auxiliary PLL for ADC and PWM

A simplified diagram of the oscillator system is shown in Figure 8-1.

# FIGURE 8-1: OSCILLATOR SYSTEM DIAGRAM

| R/W-0            | R/W-0                                                                                                                      | R/W-1                                                                           | R/W-1          | R/W-0                                   | R/W-0         | R/W-0                 | R/W-0      |

|------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------|-----------------------------------------|---------------|-----------------------|------------|

| ROI              |                                                                                                                            | DOZE<2:0>                                                                       |                | DOZEN <sup>(1)</sup>                    |               | FRCDIV<2:0>           |            |

| bit 15           |                                                                                                                            |                                                                                 |                | · · · · · · · · · · · · · · · · · · ·   |               |                       | bit        |

| R/W-0            | R/W-1                                                                                                                      | U-0                                                                             | R/W-0          | R/W-0                                   | R/W-0         | R/W-0                 | R/W-0      |

| PLLP             | OST<1:0>                                                                                                                   | _                                                                               |                | F                                       | PLLPRE<4:     | 0>                    |            |

| bit 7            |                                                                                                                            |                                                                                 |                |                                         |               |                       | bit        |

| Legend:          |                                                                                                                            |                                                                                 |                |                                         |               |                       |            |

| R = Readab       | le bit                                                                                                                     | W = Writable                                                                    | bit            | U = Unimpleme                           | ented bit, re | ad as '0'             |            |

| -n = Value a     | t POR                                                                                                                      | '1' = Bit is set                                                                |                | '0' = Bit is clear                      | red           | x = Bit is unkno      | own        |

| bit 15           | 1 = Interrupts                                                                                                             | on Interrupt bi<br>will clear the I<br>have no effec                            | DOZEN bit a    |                                         | clock/periph  | eral clock ratio is : | set to 1:1 |

|                  | 111 = FCY/12<br>110 = FCY/64<br>101 = FCY/32<br>100 = FCY/16<br>011 = FCY/8 (<br>010 = FCY/4<br>001 = FCY/2<br>000 = FCY/1 | -                                                                               |                |                                         |               |                       |            |

| bit 11           | <b>DOZEN:</b> Doze<br>1 = DOZE<2                                                                                           |                                                                                 | es the ratio b | between the perip<br>o is forced to 1:1 | heral clocks  | and the processo      | or clocks  |

| bit 10-8         | 111 = FRC di<br>110 = FRC di<br>101 = FRC di<br>100 = FRC di<br>011 = FRC di<br>010 = FRC di<br>001 = FRC di               | vide-by-256<br>vide-by-64<br>vide-by-32<br>vide-by-16<br>vide-by-8<br>vide-by-4 |                | or Postscaler bits                      |               |                       |            |

| bit 7-6          |                                                                                                                            | <b>0&gt;:</b> PLL VCO (<br>d<br>(default)                                       | -              | er Select bits (also                    | o denoted a   | s 'N2', PLL postsc    | aler)      |

| bit 5<br>bit 4-0 | Unimplemen<br>PLLPRE<4:0<br>11111 = Inpu<br>•<br>•                                                                         | ted: Read as 'i<br>>: PLL Phase I<br>t/33                                       |                | ıt Divider bits (als                    | o denoted a   | is 'N1', PLL presca   | aler)      |

|                  | 00001 = Inpu<br>00000 = Inpu                                                                                               |                                                                                 |                |                                         |               |                       |            |

### Note 1: This bit is cleared when the ROI bit is set and an interrupt occurs.

**2:** This register is reset only on a Power-on Reset (POR).

| REGISTER 9      | -3: PMD3                                                                   | 3: PERIPHER    | AL MODULE | DISABLE C    | ONTROL RE            | GISTER 3 |       |

|-----------------|----------------------------------------------------------------------------|----------------|-----------|--------------|----------------------|----------|-------|

| U-0             | U-0                                                                        | U-0            | U-0       | U-0          | R/W-0                | U-0      | U-0   |

| —               | —                                                                          | —              | —         | —            | CMPMD <sup>(1)</sup> | —        | —     |

| bit 15          |                                                                            |                |           |              |                      |          | bit 8 |

|                 |                                                                            |                |           |              |                      |          |       |

| U-0             | U-0                                                                        | U-0            | U-0       | U-0          | U-0                  | U-0      | U-0   |

| _               |                                                                            | —              |           |              |                      | _        | —     |

| bit 7           |                                                                            |                |           |              |                      |          | bit 0 |

|                 |                                                                            |                |           |              |                      |          |       |

| Legend:         |                                                                            |                |           |              |                      |          |       |

| R = Readable    | bit                                                                        | W = Writable I | bit       | U = Unimplen | nented bit, read     | l as '0' |       |

| -n = Value at F | -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                |           |              |                      |          | nown  |

#### DECISTED 0 2. AL MODULE DISABLE CONTROL DECISTED 2 DMD2. DE

| bit 15-11 | <b>Unimplemented:</b> | Read as '0' | , |

|-----------|-----------------------|-------------|---|

|           |                       |             |   |

| bit 10  | CMPMD: Analog Comparator Module Disable bit <sup>(1)</sup> |

|---------|------------------------------------------------------------|

|         | 1 = Analog comparator module is disabled                   |

|         | 0 = Analog comparator module is enabled                    |

| bit 9-0 | Unimplemented: Read as '0'                                 |

Note 1: This bit is not implemented in dsPIC33FJ06GS101A/102A devices.

#### **REGISTER 9-4:** PMD4: PERIPHERAL MODULE DISABLE CONTROL REGISTER 4

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/W-0  | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|--------|-----|-----|-------|

| —     | —   | —   | —   | REFOMD | —   | —   | —     |

| bit 7 |     |     |     |        |     |     | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | id as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-4 | Unimplemented: Read as '0'                           |

|----------|------------------------------------------------------|

| bit 3    | REFOMD: Reference Clock Generator Module Disable bit |

|          | 1 = Reference clock generator module is disabled     |

|          | 0 = Reference clock generator module is enabled      |

| bit 2-0  | Unimplemented: Read as '0'                           |

| REGISTER 9      | EGISTER 9-6: PMD7: PERIPHERAL MODULE DISABLE CONTROL REGISTER 7 |                  |     |                                    |     |                       |                       |  |

|-----------------|-----------------------------------------------------------------|------------------|-----|------------------------------------|-----|-----------------------|-----------------------|--|

| U-0             | U-0                                                             | U-0              | U-0 | U-0                                | U-0 | R/W-0                 | R/W-0                 |  |

|                 | _                                                               | —                | _   |                                    |     | CMP2MD <sup>(1)</sup> | CMP1MD <sup>(1)</sup> |  |

| bit 15          |                                                                 |                  |     |                                    |     |                       | bit 8                 |  |

|                 |                                                                 |                  |     |                                    |     |                       |                       |  |

| U-0             | U-0                                                             | U-0              | U-0 | U-0                                | U-0 | U-0                   | U-0                   |  |

| _               | _                                                               | —                | —   | —                                  | _   | —                     |                       |  |

| bit 7           |                                                                 |                  |     |                                    |     |                       | bit 0                 |  |

|                 |                                                                 |                  |     |                                    |     |                       |                       |  |

| Legend:         |                                                                 |                  |     |                                    |     |                       |                       |  |

| R = Readable    | bit                                                             | W = Writable     | bit | U = Unimplemented bit, read as '0' |     |                       |                       |  |

| -n = Value at F | POR                                                             | '1' = Bit is set |     | '0' = Bit is cleared               |     | x = Bit is unkr       | nown                  |  |

| bit 15-10 | Unimplemented: Read as '0'                                                                                     |

|-----------|----------------------------------------------------------------------------------------------------------------|

| bit 9     | CMP2MD: Analog Comparator 2 Module Disable bit <sup>(1)</sup>                                                  |

|           | <ul><li>1 = Analog Comparator 2 module is disabled</li><li>0 = Analog Comparator 2 module is enabled</li></ul> |

| bit 8     | CMP1MD: Analog Comparator 1 Module Disable bit <sup>(1)</sup>                                                  |

|           | <ul><li>1 = Analog Comparator 1 module is disabled</li><li>0 = Analog Comparator 1 module is enabled</li></ul> |

| bit 7-0   | Unimplemented: Read as '0'                                                                                     |

**Note 1:** This bit is not implemented in dsPIC33FJ06GS101A/102A devices.

# 10.2 Open-Drain Configuration

In addition to the PORT, LAT and TRIS registers for data control, some digital only port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (for example, 5V), on any desired 5V tolerant pins, by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

Refer to the **"Pin Diagrams"** section for the available pins and their functionality.

# 10.3 Configuring Analog Port Pins

The ADPCFG and TRIS registers control the operation of the Analog-to-Digital port pins. The port pins that are to function as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The ADPCFG register has a default value of 0x0000; therefore, all pins that share ANx functions are analog (not digital) by default.

When the PORT register is read, all pins configured as analog input channels will read as cleared (a low level).

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin, defined as a digital input (including the ANx pins), can cause the input buffer to consume current that exceeds the device specifications.

# 10.4 I/O Port Write/Read Timing

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP. An example is shown in Example 10-1.

# 10.5 Input Change Notification

The Input Change Notification function of the I/O ports allows devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States (COS), even in Sleep mode when the clocks are disabled. Depending on the device pin count, up to 16 external signals (CNx pin) can be selected (enabled) for generating an interrupt request on a Change-of-State.

Four control registers are associated with the CN module. The CNEN1 register contains the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pin.

Each CN pin also has a weak pull-up connected to it. The pull-ups act as a current source connected to the pin and eliminate the need for external resistors when the push button or keypad devices are connected. The pull-ups are enabled separately, using the CNPU1 register, which contains the control bits for each of the CN pins. Setting any of the control bits enables the weak pull-ups for the corresponding pins.

**Note:** Pull-ups on change notification pins should always be disabled when the port pin is configured as a digital output.

| MOV  | 0xFF00, W0 | ; Configure PORTB<15:8> as inputs |

|------|------------|-----------------------------------|

| MOV  | W0, TRISBB | ; and PORTB<7:0> as outputs       |

| NOP  |            | ; Delay 1 cycle                   |

| BTSS | PORTB, #13 | ; Next Instruction                |

EXAMPLE 10-1: PORT WRITE/READ EXAMPLE

| U-0          | U-0                | U-0                | U-0          | U-0                                     | U-0                                | U-0          | U-0     |  |  |  |

|--------------|--------------------|--------------------|--------------|-----------------------------------------|------------------------------------|--------------|---------|--|--|--|

| _            |                    | —                  | _            | _                                       |                                    | —            |         |  |  |  |

| bit 15       |                    |                    |              |                                         |                                    |              | bit 8   |  |  |  |

| U-0          | U-0                | R/W-1              | R/W-1        | R/W-1                                   | R/W-1                              | R/W-1        | R/W-1   |  |  |  |

|              |                    |                    | 10/00-1      |                                         | R<5:0> <sup>(1)</sup>              | 10/00-1      | 10/00-1 |  |  |  |

| bit 7        |                    |                    |              |                                         |                                    |              | bit 0   |  |  |  |

| <b>.</b> .   |                    |                    |              |                                         |                                    |              |         |  |  |  |

| Legend:      |                    |                    |              |                                         |                                    |              |         |  |  |  |

| R = Readab   | ole bit            | W = Writable       | bit          | -                                       | U = Unimplemented bit, read as '0' |              |         |  |  |  |

| -n = Value a | at POR             | '1' = Bit is set   |              | '0' = Bit is cleared x = Bit is unknown |                                    |              |         |  |  |  |

| h# 45 0      |                    | ata da Danadara (j | ~ <b>.</b>   |                                         |                                    |              |         |  |  |  |

| bit 15-6     | -                  | nted: Read as '    |              |                                         |                                    | (1           | N N     |  |  |  |

| bit 5-0      |                    | >: Assign Outpu    | it Compare A | (OCFA) to the                           | Corresponding                      | RPn Pin bits | )       |  |  |  |

|              |                    | put tied to Vss    |              |                                         |                                    |              |         |  |  |  |

|              |                    | put tied to RP35   |              |                                         |                                    |              |         |  |  |  |

|              |                    | put tied to RP34   |              |                                         |                                    |              |         |  |  |  |

|              |                    | put tied to RP33   |              |                                         |                                    |              |         |  |  |  |

|              | 100000 <b>= In</b> | put tied to RP32   | 2            |                                         |                                    |              |         |  |  |  |

|              | •                  |                    |              |                                         |                                    |              |         |  |  |  |

|              | •                  |                    |              |                                         |                                    |              |         |  |  |  |

|              | •                  |                    |              |                                         |                                    |              |         |  |  |  |

|              | 00000 <b>= Inp</b> | ut tied to RP0     |              |                                         |                                    |              |         |  |  |  |

|              | ·                  |                    |              |                                         |                                    |              |         |  |  |  |

# REGISTER 10-6: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

**Note 1:** These bits are not implemented in the dsPIC33FJ06GS001 device.

# 15.0 HIGH-SPEED PWM

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS001/101A/102A/ 202A and dsPIC33FJ09GS302 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 43. "High-Speed PWM" (DS70323) in the "dsPIC33F/ PIC24H Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The high-speed PWM module supports a wide variety of PWM modes and output formats. This PWM module is ideal for power conversion applications, such as:

- AC/DC Converters

- DC/DC Converters

- Power Factor Correction (PFC)

- Uninterruptible Power Supply (UPS)

- Inverters

- · Battery Chargers

- · Digital Lighting

# 15.1 Features Overview

The high-speed PWM module incorporates the following features:

- Two to three PWM generators with four to six outputs

- Individual time base and duty cycle for each of the six PWM outputs

- · Dead time for rising and falling edges:

- Duty cycle resolution of 1.04 ns<sup>(1,2)</sup>

- Dead-time resolution of 1.04 ns<sup>(1,2)</sup>

- Phase-shift resolution of 1.04 ns<sup>(1,2)</sup>

- Frequency resolution of 1.04 ns<sup>(1,2)</sup>

Note 1: Resolution is 8.32 ns in Center-Aligned PWM mode.

2: Resolution is 8.32 ns for dsPIC33FJ06GS001 devices.

- Supported PWM modes:

- Standard Edge-Aligned

- True Independent Output

- Complementary

- Center-Aligned

- Push-Pull

- Multiphase

- Variable Phase

- Fixed Off Time

- Current Reset

- Current Limit

- Independent Fault/Current-Limit inputs for each of the six PWM outputs

- Output override control

- Special Event Trigger

- · PWM capture feature

- Prescaler for input clock

- Dual trigger from PWM to ADC

- PWMxH, PWMxL output pin swapping

- Remappable PWM4H, PWM4L pins

- On-the-fly PWM frequency, duty cycle and phase-shift changes

- Disabling of individual PWM generators to reduce power consumption

- Leading-Edge Blanking (LEB) functionality

- PWM output chopping (see Note 1)

- **Note 1:** The chopping function performs a logical AND of the PWM outputs with a very high-frequency clock signal. The chopping frequency is typically hundreds or thousands of time higher in frequency, as compared to the PWM frequency. Chopping a PWM signal constrains the use of a pulse transformer to cross the isolation barrier.

Figure 15-1 conceptualizes the PWM module in a simplified block diagram. Figure 15-2 illustrates how the module hardware is partitioned for each PWM output pair for the Complementary PWM mode. Each functional unit of the PWM module is discussed in subsequent sections.

The PWM module contains three PWM generators. The module has up to six PWM output pins: PWM1H, PWM1L, PWM2H, PWM2L, PWM4H and PWM4L. For complementary outputs, these six I/O pins are grouped into H/L pairs.

# 16.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS001/101A/102A/ 202A and dsPIC33FJ09GS302 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 18. "Serial Peripheral Interface (SPI)" (DS70206) of the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

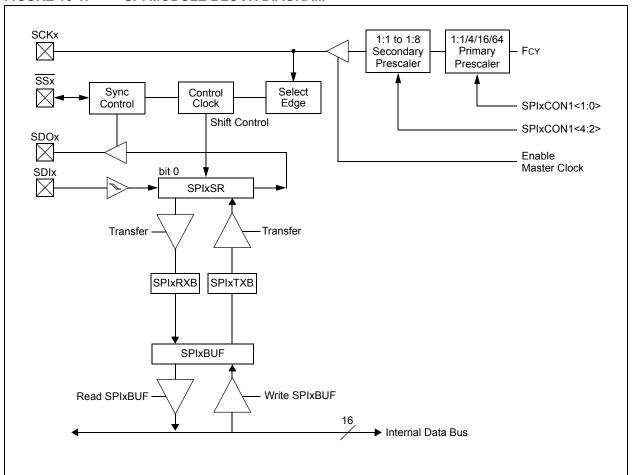

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, Analog-to-Digital Converters, etc. The SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP.

Each SPI module consists of a 16-bit shift register, SPIxSR (where x = 1 or 2), used for shifting data in and out, and a buffer register, SPIxBUF. A control register, SPIxCON, configures the module. Additionally, a status register, SPIxSTAT, indicates status conditions.

The serial interface consists of 4 pins:

- · SDIx (serial data input)

- · SDOx (serial data output)

- · SCKx (shift clock input or output)

- SSx (active-low slave select)

In Master mode operation, SCKx is a clock output; in Slave mode, it is a clock input.

### FIGURE 16-1: SPI MODULE BLOCK DIAGRAM

# **REGISTER 19-7:** ADCPC3: ADC CONVERT PAIR CONTROL REGISTER 3<sup>(1)</sup> (CONTINUED)

```

bit 4-0

TRGSRC6<4:0>: Trigger 6 Source Selection bits

Selects trigger source for conversion of analog channels AN13 and AN12.

11111 = Timer2 period match

11011 = Reserved

11010 = PWM Generator 4 current-limit ADC trigger

11001 = Reserved

11000 = PWM Generator 2 current-limit ADC trigger

10111 = PWM Generator 1 current-limit ADC trigger

10110 = Reserved

10010 = Reserved

10001 = PWM Generator 4 secondary trigger is selected

10000 = Reserved

01111 = PWM Generator 2 secondary trigger is selected

01110 = PWM Generator 1 secondary trigger is selected

01101 = Reserved

```

01101 = Timer1 period match 01100 = Timer1 period match 01000 = Reserved 00111 = PWM Generator 4 primary trigger is selected 00101 = PWM Generator 2 primary trigger is selected 00100 = PWM Generator 1 primary trigger is selected 00011 = PWM Special Event Trigger is selected 00011 = Global software trigger is selected 00001 = Individual software trigger is selected

00000 = No conversion is enabled

- **Note 1:** If other conversions are in progress, conversion will be performed when the conversion resources are available.

- 2: AN13 is internally connected to Vref in all devices. AN12 is internally connected to the EXTREF pin in the dsPIC33FJ06001/202A and dsPIC33FJ09GS302 devices. The dsPIC33FJ06GS101A/102A devices not have an EXTREF pin; therefore, any data read on the corresponding AN12 input will be invalid.

# 25.2 AC Characteristics and Timing Parameters

This section defines dsPIC33FJ06GS001/101A/102A/202A and dsPIC33FJ09GS302 AC characteristics and timing parameters.

### TABLE 25-14: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)                                                            |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| AC CHARACTERISTICS | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |

|                    | Operating voltage VDD range as described in Table 25-1.                                                                             |

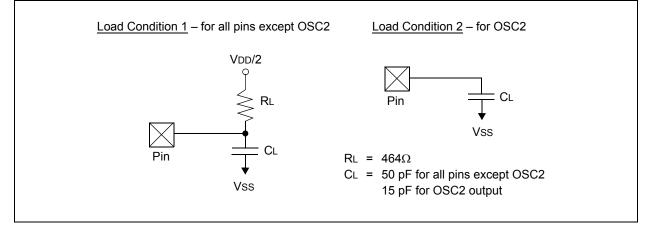

### FIGURE 25-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

### TABLE 25-15: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param. | Symbol | Characteristic        | Min. | Тур. | Max. | Units | Conditions                                                      |

|--------|--------|-----------------------|------|------|------|-------|-----------------------------------------------------------------|

| DO50   | Cosco  | OSC2 Pin              | _    | _    | 15   |       | In XT and HS modes when external<br>clock is used to drive OSC1 |

| DO56   | Сю     | All I/O Pins and OSC2 | —    | —    | 50   | pF    | EC mode                                                         |

| DO58   | Св     | SCL1, SDA1            |      | _    | 400  | pF    | In I <sup>2</sup> C™ mode                                       |

| AC CHARACTERISTICS |        |                                                                     | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |      |       |                             |  |  |

|--------------------|--------|---------------------------------------------------------------------|-------------------------------------------------------|---------------------|------|-------|-----------------------------|--|--|

| Param.             | Symbol | Characteristic                                                      | Min.                                                  | Typ. <sup>(1)</sup> | Max. | Units | Conditions                  |  |  |

| OS50               | Fplli  | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range | 0.8                                                   |                     | 8    | MHz   | ECPLL, XTPLL modes          |  |  |

| OS51               | Fsys   | On-Chip VCO System<br>Frequency                                     | 100                                                   | —                   | 200  | MHz   |                             |  |  |

| OS52               | TLOCK  | PLL Start-up Time (Lock Time)                                       | 0.9                                                   | 1.5                 | 3.1  | mS    |                             |  |  |

| OS53               | DCLK   | CLKO Stability (Jitter) <sup>(2)</sup>                              | -3                                                    | 0.5                 | 3    | %     | Measured over 100 ms period |  |  |

# TABLE 25-17:PLL CLOCK TIMING SPECIFICATIONS (VDD = 3.0V TO 3.6V)

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested in manufacturing.

2: These parameters are characterized by similarity, but are not tested in manufacturing. This specification is based on clock cycle by clock cycle measurements. To calculate the effective jitter for individual time bases or communication clocks use this formula:

$$Peripheral Clock Jitter = \frac{DCLK}{\sqrt{\frac{FOSC}{Peripheral Bit Rate Clock}}}$$

For example: FOSC = 32 MHz, DCLK = 3%, SPI bit rate clock (i.e., SCK) is 2 MHz.

$$SPI SCK Jitter = \left[\frac{D_{CLK}}{\sqrt{\left(\frac{32 \ MHz}{2 \ MHz}\right)}}\right] = \left[\frac{3\%}{\sqrt{16}}\right] = \left[\frac{3\%}{4}\right] = 0.75\%$$

### TABLE 25-18: AUXILIARY PLL CLOCK TIMING SPECIFICATIONS (VDD = 3.0V TO 3.6V)

|        |        |                                                   | (unless                                        | rd Operat<br>otherwis<br>ng temper | <b>e stated)</b><br>ature -4 | 0°C ≤ TA | 3.0V to 3.6V<br>≤ +85°C for Industrial<br>≤ +125°C for Extended |

|--------|--------|---------------------------------------------------|------------------------------------------------|------------------------------------|------------------------------|----------|-----------------------------------------------------------------|

| Param. | Symbol | Characteristic                                    | Min. Typ. <sup>(1)</sup> Max. Units Conditions |                                    |                              |          |                                                                 |

| OS56   | Fhpout | On-Chip 16x PLL CCO<br>Frequency                  | 112                                            | 118                                | 120                          | MHz      |                                                                 |

| OS57   | Fhpin  | On-Chip 16x PLL Phase<br>Detector Input Frequency | 7.0                                            | 7.37                               | 7.5                          | MHz      |                                                                 |

| OS58   | Tsu    | Frequency Generator Lock<br>Time                  | —                                              | —                                  | 10                           | μs       |                                                                 |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested in manufacturing.

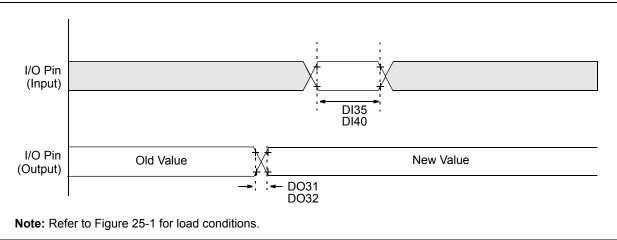

### TABLE 25-21: I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                                                      | (unless | rd Operat<br>otherwis | <b>e statec</b><br>ature - | <b>i)</b><br>-40°C ≤ T | <b>3.0V to 3.6V</b><br>$A \le +85^{\circ}C$ for Industrial<br>$A \le +125^{\circ}C$ for Extended |

|--------------------|--------|----------------------------------------------------------------------|---------|-----------------------|----------------------------|------------------------|--------------------------------------------------------------------------------------------------|

| Param.             | Symbol | Characteristic                                                       | Min.    | Typ. <sup>(1)</sup>   | Max.                       | Units                  | Conditions                                                                                       |

| DO31               | TioR   | I/O Pins: 4x Sink Driver Pins<br>RA0-RA2, RB0-RB2, RB5-RB10,<br>RB15 | _       | 10                    | 25                         | ns                     | Refer to Figure 25-1 for test conditions                                                         |

|                    |        | I/O Pins: 16x Sink Driver Pins<br>RA3, RA4, RB3, RB4, RB11-RB14      | —       | 6                     | 15                         | ns                     |                                                                                                  |

| DO32               | TioF   | I/O Pins: 4x Sink Driver Pins<br>RA0-RA2, RB0-RB2, RB5-RB10,<br>RB15 | _       | 10                    | 25                         | ns                     | Refer to Figure 25-1 for test conditions                                                         |

|                    |        | I/O Pins: 16x Sink Driver Pins<br>RA3, RA4, RB3, RB4, RB11-RB14      | —       | 6                     | 15                         | ns                     |                                                                                                  |

| DI35               | TINP   | INTx Pin High or Low Time (input)                                    | 20      | _                     |                            | ns                     |                                                                                                  |

| DI40               | Trbp   | CNx High or Low Time (input)                                         | 2       |                       | _                          | TCY                    |                                                                                                  |

Note 1: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

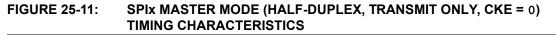

| AC CHARAG            | CTERISTICS                               |                                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industria} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |     |     |     |  |  |

|----------------------|------------------------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|--|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)                                                                                                                                                                                                                                           | СКЕ | СКР | SMP |  |  |

| 15 MHz               | Table 25-30                              | _                                           | _                                                                                                                                                                                                                                                                                    | 0,1 | 0,1 | 0,1 |  |  |

| 9 MHz                | _                                        | Table 25-31                                 | —                                                                                                                                                                                                                                                                                    | 1   | 0,1 | 1   |  |  |

| 9 MHz                | —                                        | Table 25-32                                 | —                                                                                                                                                                                                                                                                                    | 0   | 0,1 | 1   |  |  |

| 15 MHz               | _                                        | —                                           | Table 25-33                                                                                                                                                                                                                                                                          | 1   | 0   | 0   |  |  |

| 11 MHz               | —                                        | —                                           | Table 25-34                                                                                                                                                                                                                                                                          | 1   | 1   | 0   |  |  |

| 15 MHz               | _                                        | —                                           | Table 25-35                                                                                                                                                                                                                                                                          | 0   | 1   | 0   |  |  |

| 11 MHz               | _                                        | —                                           | Table 25-36                                                                                                                                                                                                                                                                          | 0   | 0   | 0   |  |  |

### TABLE 25-29: SPIx MAXIMUM DATA/CLOCK RATE SUMMARY

# TABLE 25-36:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                    |     |       |                                         |  |

|--------------------|-----------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|-----------------------------------------|--|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                                | Min                                                                                                                                                                                                                                                                                     | Тур <sup>(2)</sup> | Max | Units | Conditions                              |  |

| SP70               | TscP                  | Maximum SCKx Input Frequency                                 | _                                                                                                                                                                                                                                                                                       |                    | 11  | MHz   | See Note 3                              |  |

| SP72               | TscF                  | SCKx Input Fall Time                                         | —                                                                                                                                                                                                                                                                                       | _                  | _   | ns    | See Parameter<br>DO32 and <b>Note 4</b> |  |

| SP73               | TscR                  | SCKx Input Rise Time                                         | —                                                                                                                                                                                                                                                                                       |                    |     | ns    | See Parameter DO31 and Note 4           |  |

| SP30               | TdoF                  | SDOx Data Output Fall Time                                   | —                                                                                                                                                                                                                                                                                       |                    |     | ns    | See Parameter<br>DO32 and <b>Note 4</b> |  |

| SP31               | TdoR                  | SDOx Data Output Rise Time                                   | —                                                                                                                                                                                                                                                                                       | _                  |     | ns    | See Parameter DO31 and Note 4           |  |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                    | —                                                                                                                                                                                                                                                                                       | 6                  | 20  | ns    |                                         |  |

| SP36               | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                 | 30                                                                                                                                                                                                                                                                                      | _                  | _   | ns    |                                         |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                   | 30                                                                                                                                                                                                                                                                                      |                    |     | ns    |                                         |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                    | 30                                                                                                                                                                                                                                                                                      | -                  |     | ns    |                                         |  |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx Input | 120                                                                                                                                                                                                                                                                                     | —                  | —   | ns    |                                         |  |

| SP51               | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance                       | 10                                                                                                                                                                                                                                                                                      | _                  | 50  | ns    | See Note 4                              |  |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                          | 1.5 Tcy + 40                                                                                                                                                                                                                                                                            |                    |     | ns    | See Note 4                              |  |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 91 ns. Therefore, the SCKx clock generated by the master must not violate this specification.

**4:** Assumes 50 pF load on all SPIx pins.