#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 6KB (2K x 24)                                                                    |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b; D/A 2x10b                                                             |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Through Hole                                                                     |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                          |

| Supplier Device Package    | 28-SPDIP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs202a-i-sp |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.5 ICSP<sup>™</sup> Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins, are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and Input Voltage High (VIH) and Input Voltage Low (VIL) pin requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins), programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>TM</sup>.

For more information on MPLAB ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site (www.microchip.com):

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS51765)

- "Multi-Tool Design Advisory" (DS51764)

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator User's Guide" (DS51616)

- *"Using MPLAB<sup>®</sup> REAL ICE™"* (poster) (DS51749)

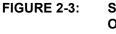

### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

# 3.4 CPU Control Registers

| R-0                  | R-0                                               | R/C-0                                  | R/C-0             | R-0                    | R/C-0                | R -0             | R/W-0         |

|----------------------|---------------------------------------------------|----------------------------------------|-------------------|------------------------|----------------------|------------------|---------------|

| OA                   | OB                                                | SA <sup>(1)</sup>                      | SB <sup>(1)</sup> | OAB                    | SAB <sup>(1,4)</sup> | DA               | DC            |

| bit 15               |                                                   |                                        |                   |                        | •                    |                  | bit 8         |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup>                              | R/W-0 <sup>(3)</sup>                   | R-0               | R/W-0                  | R/W-0                | R/W-0            | R/W-0         |

|                      | IPL<2:0> <sup>(2)</sup>                           |                                        | RA                | N                      | OV                   | Z                | С             |

| bit 7                |                                                   |                                        |                   |                        |                      |                  | bit (         |

| Legend:              |                                                   |                                        |                   |                        |                      |                  |               |

| C = Clearab          | le bit                                            | R = Readable                           | e bit             | U = Unimple            | mented bit, read     | as '0'           |               |

| S = Settable         | bit                                               | W = Writable                           | bit               | -n = Value at          | POR                  |                  |               |

| '1' = Bit is se      | et                                                | '0' = Bit is clea                      | ared              | x = Bit is unk         | nown                 |                  |               |

| bit 15               | OA: Accumul                                       | lator A Overflow                       | v Status bit      |                        |                      |                  |               |

|                      |                                                   | ator A overflowe                       |                   |                        |                      |                  |               |

| 1.1.4.4              |                                                   | ator A has not c                       |                   |                        |                      |                  |               |

| bit 14               |                                                   | lator B Overflow<br>ator B overflowe   |                   |                        |                      |                  |               |

|                      |                                                   | ator B has not c                       |                   |                        |                      |                  |               |

| bit 13               | SA: Accumul                                       | ator A Saturatio                       | on 'Sticky' Sta   | tus bit <sup>(1)</sup> |                      |                  |               |

|                      | 1 = Accumula                                      | ator A is saturat<br>ator A is not sat | ed or has bee     |                        | some time            |                  |               |

| bit 12               | SB: Accumul                                       | ator B Saturatio                       | on 'Sticky' Sta   | tus bit <sup>(1)</sup> |                      |                  |               |

|                      |                                                   | ator B is saturat<br>ator B is not sat |                   | en saturated at        | some time            |                  |               |

| bit 11               | <b>0AB:</b> 0A    0                               | DB Combined A                          | ccumulator O      | verflow Status         | bit                  |                  |               |

|                      | 1 = Accumula                                      | ators A or B hav                       | ve overflowed     |                        |                      |                  |               |

| bit 10               | <b>SAB:</b> SA    S                               | B Combined A                           | ccumulator 'St    | icky' Status bit       | (1,4)                |                  |               |

|                      | 1 = Accumula                                      |                                        | saturated or      | have been sat          | urated at some       | time in the past | t             |

| bit 9                | DA: DO Loop                                       | Active bit                             |                   |                        |                      |                  |               |

|                      | 1 = DO <b>loop ir</b>                             |                                        |                   |                        |                      |                  |               |

|                      | -                                                 | ot in progress                         |                   |                        |                      |                  |               |

| bit 8                |                                                   | U Half Carry/B                         |                   |                        |                      |                  |               |

|                      | of the res                                        | sult occurred                          |                   | -                      | data) or 8th low-o   |                  |               |

|                      | •                                                 | -out from the 4 the result occur       |                   | bit (for byte-siz      | ed data) or 8th      | low-order bit (1 | for word-size |

| Note 1: ⊤            | his bit can be rea                                | ad or cleared (n                       | ot set).          |                        |                      |                  |               |

| L                    | he IPL<2:0> bits<br>evel (IPL). The v<br>PL3 = 1. |                                        |                   |                        |                      |                  |               |

|                      |                                                   |                                        |                   |                        |                      |                  |               |

#### REGISTER 3-1: SR: CPU STATUS REGISTER

**3:** The IPL<2:0> Status bits are read-only when NSTDIS = 1 (INTCON1<15>).

**4:** Clearing this bit will clear SA and SB.

| IABLE 4  | -21.        | nion   | SFEEL              |        |         | GISTEI |           | OK US | FICJJI | 30003        | IUZA A | UD USFIC | 33L10009  | ZUZA  |          |         |       |              |

|----------|-------------|--------|--------------------|--------|---------|--------|-----------|-------|--------|--------------|--------|----------|-----------|-------|----------|---------|-------|--------------|

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14             | Bit 13 | Bit 12  | Bit 11 | Bit 10    | Bit 9 | Bit 8  | Bit 7        | Bit 6  | Bit 5    | Bit 4     | Bit 3 | Bit 2    | Bit 1   | Bit 0 | All<br>Reset |

| ADCON    | 0300        | ADON   | _                  | ADSIDL | SLOWCLK | _      | GSWTRG    | —     | FORM   | EIE          | ORDER  | SEQSAMP  | ASYNCSAMP | _     | A        | DCS<2:0 | >     | 0003         |

| ADPCFG   | 0302        | _      | —                  | _      | —       | _      | _         | _     | _      | —            |        | PCFG5    | PCFG4     | PCFG3 | PCFG2    | PCFG1   | PCFG0 | 0000         |

| ADSTAT   | 0306        | _      | —                  | _      | —       | _      | —         |       | _      | —            | P6RDY  | _        | —         | _     | P2RDY    | P1RDY   | P0RDY | 0000         |

| ADBASE   | 0308        |        |                    |        |         |        |           | Α     | DBASE< | 15:1>        |        |          |           |       |          |         | _     | 0000         |

| ADCPC0   | 030A        | IRQEN1 | PEND1              | SWTRG1 |         | TRG    | SRC1<4:0> |       |        | IRQEN0       | PEND0  | SWTRG0   |           | TRGS  | RC0<4:0> |         |       | 0000         |

| ADCPC1   | 030C        | _      | —                  | _      | _       | _      | —         |       | _      | IRQEN2       | PEND2  | SWTRG2   |           | TRGS  | RC2<4:0> |         |       | 0000         |

| ADCPC3   | 0310        | _      | _                  | _      | _       | _      | _         | _     | _      | IRQEN6       | PEND6  | SWTRG6   |           | TRGS  | RC6<4:0> |         |       | 0000         |

| ADCBUF0  | 0320        |        |                    |        |         |        |           |       | ADC D  | ata Buffer 0 | )      |          |           |       |          |         |       | XXXX         |

| ADCBUF1  | 0322        |        |                    |        |         |        |           |       | ADC D  | ata Buffer 1 |        |          |           |       |          |         |       | XXXX         |

| ADCBUF2  | 0324        |        |                    |        |         |        |           |       | ADC D  | ata Buffer 2 | 2      |          |           |       |          |         |       | XXXX         |

| ADCBUF3  | 0326        |        |                    |        |         |        |           |       | ADC D  | ata Buffer 3 | 3      |          |           |       |          |         |       | XXXX         |

| ADCBUF4  | 0328        |        |                    |        |         |        |           |       | ADC D  | ata Buffer 4 | ļ      |          |           |       |          |         |       | XXXX         |

| ADCBUF5  | 032A        |        | ADC Data Buffer 5  |        |         |        |           |       |        | XXXX         |        |          |           |       |          |         |       |              |

| ADCBUF12 | 0338        |        | ADC Data Buffer 12 |        |         |        |           |       |        | XXXX         |        |          |           |       |          |         |       |              |

| ADCBUF13 | 033A        |        | ADC Data Buffer 13 |        |         |        |           |       |        |              | XXXX   |          |           |       |          |         |       |              |

# TABLE 4-21: HIGH-SPEED 10-BIT ADC REGISTER MAP FOR dsPIC33FJ06GS102A AND dsPIC33FJ06GS202A

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

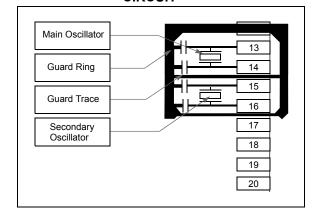

## 4.5 Modulo Addressing

Modulo Addressing mode is a method used to provide an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either data or program space (since the data pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into program space) and Y data spaces. Modulo Addressing can operate on any W register pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction as there are certain restrictions on the buffer start address (for incrementing buffers), or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

#### 4.5.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

| Note: | Υ   | space      | Modulo      | Addressing   | EA   |

|-------|-----|------------|-------------|--------------|------|

|       | cal | culations  | assume      | word-sized   | data |

|       | (LS | Sb of ever | y EA is alw | /ays clear). |      |

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

#### 4.5.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that will operate with Modulo Addressing:

- If XWM = 15, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 15, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X data space when XWM is set to any value other than '15' and the XMODEN bit is set at MODCON<15>.

The Y Address Space Pointer W register (YWM) to which Modulo Addressing is to be applied is stored in MODCON<7:4>. Modulo Addressing is enabled for Y data space when YWM is set to any value other than '15' and the YMODEN bit is set at MODCON<14>.

#### FIGURE 4-6: MODULO ADDRESSING OPERATION EXAMPLE

# 5.2 RTSP Operation

The dsPIC33FJ06GS001/101A/102A/202A and dsPIC33FJ09GS302 Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to erase a page of memory, which consists of eight rows (512 instructions) at a time, and to program one row or one word at a time. Table 25-12 shows typical erase and programming times. The 8-row erase pages and single row write rows are edge-aligned from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively.

The program memory implements holding buffers that can contain 64 instructions of programming data. Prior to the actual programming operation, the write data must be loaded into the buffers sequentially. The instruction words loaded must always be from a group of 64 boundary.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register. A total of 64 TBLWTL and TBLWTH instructions are required to load the instructions.

All of the table write operations are single-word writes (two instruction cycles) because only the buffers are written. A programming cycle is required for programming each row.

# 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

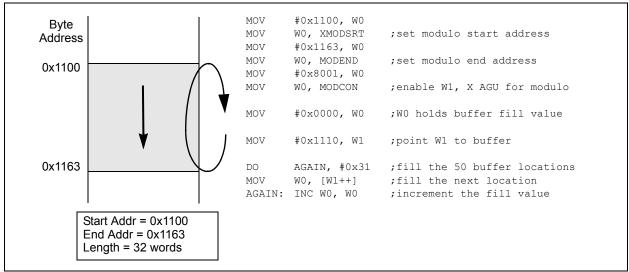

The programming time depends on the FRC accuracy (see Table 25-19) and the value of the FRC Oscillator Tuning register (see Register 8-4). Use the following formula to calculate the minimum and maximum values for the Row Write Time, Page Erase Time and Word Write Cycle Time parameters (see Table 25-12).

#### EQUATION 5-1: PROGRAMMING TIME

For example, if the device is operating at +125°C, the FRC accuracy will be  $\pm 5\%$ . If the TUN<5:0> bits (see Register 8-4) are set to `b111111, the minimum row write time is equal to Equation 5-2.

#### EQUATION 5-2: MINIMUM PAGE ERASE TIME

$$T_{RW} = \frac{168517 \ Cycles}{7.37 \ MHz \times (1 + 0.05) \times (1 - 0.00375)} = 21.85 ms$$

The maximum row write time is equal to Equation 5-3.

#### EQUATION 5-3: MAXIMUM PAGE ERASE TIME

$$T_{RW} = \frac{168517 \text{ Cycles}}{7.37 \text{ MHz} \times (1 - 0.05) \times (1 - 0.00375)} = 24.16 \text{ ms}$$

Setting the WR bit (NVMCON<15>) starts the operation, and the WR bit is automatically cleared when the operation is finished.

# 5.4 Control Registers

Two SFRs are used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to **Section 5.3 "Programming Operations"** for further details.

#### **Flash Memory Control Registers** 5.5

| bit 15       Invariant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/SO-0            | R/W-0                       | R/W-0                          | U-0                         | U-0                         | U-0                | U-0                    | U-0           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------|--------------------------------|-----------------------------|-----------------------------|--------------------|------------------------|---------------|

| U-0       R/W-0       U-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         Image: Image                                                                                                                                                                                                                                                                                                        | WR <sup>(1)</sup> | WREN <sup>(1)</sup>         | WRERR <sup>(1)</sup>           | _                           | —                           | _                  | _                      | _             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | bit 15            |                             | · · ·                          |                             |                             |                    | ·                      | bit 8         |

| -         ERASE <sup>(1)</sup> -         NVMOP<3:0::         1.2           bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | U-0               | R/W-0                       | U-0                            | U-0                         | R/W-0                       | R/W-0              | R/W-0                  | R/W-0         |

| bit 7       bit 7         Legend:       SO = Settable Only bit         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       WR: Write Control bit <sup>(1)</sup> 1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the b cleared by hardware once operation is complete. This bit can only be set (not cleared) in software once operation is complete and inactive         bit 14       WREN: Write Enable bit <sup>(1)</sup> 1 = Enables Flash program/erase operations         o = Inhibits Flash program/erase operations       o = Inhibits Flash program/erase operations         bit 13       WRERR: Write Sequence Error Flag bit <sup>(1)</sup> 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation sepecified by NVMOP<3:0> on the next WR command         bit 6       ERASE: Erase/Program Enable bit <sup>(1)</sup> 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         bit 5-4       Unimplemented: Read as '0'         bit 3-0       NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1:       1111 = No operation         1011 = No operation       0010 = Memory page erase operation         0011 = No oper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                 |                             | _                              | _                           |                             | NVMOP              | <3:0> <sup>(1,2)</sup> | -             |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       WR: Write Control bit <sup>(1)</sup> 1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the bic cleared by hardware once operation is complete. This bit can only be set (not cleared) in software one operation is complete and inactive         bit 14       WREN: Write Enable bit <sup>(1)</sup> 1 = Enables Flash program/erase operations         0 = Inhibits Flash program/erase operations       0 = Inhibits Flash program/erase operations         bit 13       WRERR: Write Sequence Error Flag bit <sup>(1)</sup> 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation selectified by NVMOP<3:0> on the next WR command         0 = Performs the program operation Select bits <sup>(1,2)</sup> If ERASE = 1:         1111 = No operation         1010 = Erase general segment         0011 = Memory page erase operation         0011 = No operation         0011 = Reserved         If ERASE = 0:         11111 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 7             |                             |                                |                             |                             |                    |                        | bit           |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       WR: Write Control bit <sup>(1)</sup> 1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the bic cleared by hardware once operation is complete. This bit can only be set (not cleared) in software once operation is complete and inactive         bit 14       WREN: Write Enable bit <sup>(1)</sup> 1 = Enables Flash program/erase operations         0 = Inhibits Flash program/erase operations       0 = Inhibits Flash program/erase operations         bit 13       WRERR: Write Sequence Error Flag bit <sup>(1)</sup> 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         0 = Depration       1101 = Erase general segment         0101 = No operation       1101 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Legend:           |                             | SO = Settab                    | le Only bit                 |                             |                    |                        |               |

| bit 15 WR: Write Control bit <sup>(1)</sup><br>1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the b<br>cleared by hardware once operation is complete. This bit can only be set (not cleared) in softwa<br>0 = Program or erase operation is complete and inactive<br>bit 14 WREN: Write Enable bit <sup>(1)</sup><br>1 = Enables Flash program/erase operations<br>0 = Inhibits Flash program/erase operations<br>bit 13 WRERR: Write Sequence Error Flag bit <sup>(1)</sup><br>1 = An improper program or erase sequence attempt or termination has occurred (bit is<br>automatically on any set attempt of the WR bit)<br>0 = The program or erase operation completed normally<br>bit 6 ERASE: Erase/Program Enable bit <sup>(1)</sup><br>1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command<br>0 = Performs the program operation specified by NVMOP<3:0> on the next WR command<br>0 = Performs the program operation specified by NVMOP<3:0> on the next WR command<br>bit 5-4 Unimplemented: Read as 'o'<br>bit 3-0 NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup><br><u>If ERASE = 1:</u><br>1111 = No operation<br>1001 = Erase general segment<br>0010 = Reserved<br>0000 = Reserved<br><u>If ERASE = 0:</u><br>1111 = No operation<br>1001 = No operation                                                                                                                                                                                                                                        | R = Readable      | e bit                       | W = Writable                   | e bit                       | U = Unimple                 | mented bit, read   | l as '0'               |               |

| 1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the bicleared by hardware once operation is complete. This bit can only be set (not cleared) in software or erase operation is complete and inactive         0 = Program or erase operation is complete and inactive         bit 14       WREN: Write Enable bit <sup>(1)</sup> 1 = Enables Flash program/erase operations         0 = Inhibits Flash program/erase operations         0 = Inhibits Flash program/erase operations         bit 13       WRERR: Write Sequence Error Flag bit <sup>(1)</sup> 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation specified hy NVMOP<3:0> on the next WR command         0 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation Select bits <sup>(1,2)</sup> If ERASE = 1:         1111 = No operation         1101 = Erase general segment         011 = No operation         1101 = Reserved         0000 = Reserved         If ERASE = 0:         1111 = No operation         1101 = No operation         1101 = No operation         1111 = No operation         1101 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -n = Value at     | POR                         | '1' = Bit is se                | et                          | '0' = Bit is cle            | eared              | x = Bit is unkr        | iown          |

| cleared by hardware once operation is complete. This bit can only be set (not cleared) in softwa<br>0 = Program or erase operation is complete and inactive<br>bit 14 WREN: Write Enable bit <sup>(1)</sup><br>1 = Enables Flash program/erase operations<br>0 = Inhibits Flash program/erase operations<br>bit 13 WRERR: Write Sequence Error Flag bit <sup>(1)</sup><br>1 = An improper program or erase sequence attempt or termination has occurred (bit is<br>automatically on any set attempt of the WR bit)<br>0 = The program or erase operation completed normally<br>bit 12-7 Unimplemented: Read as '0'<br>bit 6 ERASE: Erase/Program Enable bit <sup>(1)</sup><br>1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command<br>0 = Performs the program operation specified by NVMOP<3:0> on the next WR command<br>0 = Performs the program operation specified by NVMOP<3:0> on the next WR command<br>bit 5-4 Unimplemented: Read as '0'<br>bit 3-0 NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup><br>If ERASE = 1:<br>1111 = No operation<br>1010 = Erase general segment<br>0011 = No operation<br>0010 = Memory page erase operation<br>0010 = Reserved<br>0000 = Reserved<br>1111 = No operation<br>1011 | bit 15            |                             |                                |                             | r orono oporati             | on The operation   | an is colf timed       | and the bit i |

| bit 14 WREN: Write Enable bit <sup>(1)</sup> 1 = Enables Flash program/erase operations 0 = Inhibits Flash program/erase operations bit 13 WRERR: Write Sequence Error Flag bit <sup>(1)</sup> 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit) 0 = The program or erase operation completed normally bit 12-7 Unimplemented: Read as '0' bit 6 ERASE: Erase/Program Enable bit <sup>(1)</sup> 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command 0 = Performs the program operation specified by NVMOP<3:0> on the next WR command 0 = Performs the program operation specified by NVMOP<3:0> on the next WR command 0 = Performs the program operation Select bits <sup>(1,2)</sup> bit 3-0 NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1: 1111 = No operation 1101 = Erase general segment 0011 = No operation 0010 = Memory page erase operation 0010 = Reserved 0000 = Reserved 0000 = Reserved 1111 = No operation 1011 = No operation 1011 = No operation 1011 = No operation 1011 = No operation 0010 = Memory word program operation 0011 = Memory word program operation 0010 = No operation 0011 = No operation 0010 = No operati                                                                                                                              |                   | cleared by                  | hardware onc                   | eoperation                  | is complete. Th             | is bit can only be |                        |               |

| 1 = Enables Flash program/erase operations         0 = Inhibits Flash program/erase operations         bit 13       WRERR: Write Sequence Error Flag bit <sup>(1)</sup> 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation completed normally         bit 12-7       Unimplemented: Read as '0'         bit 6       ERASE: Erase/Program Enable bit <sup>(1)</sup> 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         bit 5-4       Unimplemented: Read as '0'         bit 3-0       NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1:       1111 = No operation         1101 = Erase general segment       0011 = No operation         0010 = Memory page erase operation       0000 = Reserved         0000 = Reserved       If ERASE = 0:         1111 = No operation       1101 = No operation         1101 = No operation       0011 = No operation         1011 = No operation       10011 = No operation         1001 = No operation       0011 = No operation         1011 = No operation       1011 = No operation         1001 = No operation       0011 = Ne operation         0011 = Ne operatio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 14            | •                           |                                | · · · P                     |                             |                    |                        |               |

| 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation completed normally         bit 12-7       Unimplemented: Read as '0'         bit 6       ERASE: Erase/Program Enable bit <sup>(1)</sup> 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         bit 5-4       Unimplemented: Read as '0'         bit 3-0       NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1:       1111 = No operation         101 = Erase general segment       0011 = No operation         0010 = Memory page erase operation       0010 = Reserved         If ERASE = 0:       1111 = No operation         1101 = No operation       1001 = Reserved         0000 = Reserved       If ERASE = 0:         1111 = No operation       1101 = No operation         0101 = No operation       0011 = Nemory word program operation         011 = No operation       0011 = Nemory word program operation         0011 = Nemory word program operation       0011 = Nemory word program operation         0010 = No operation       0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |                             |                                |                             |                             |                    |                        |               |

| 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation completed normally         bit 12-7       Unimplemented: Read as '0'         bit 6       ERASE: Erase/Program Enable bit <sup>(1)</sup> 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         bit 5-4       Unimplemented: Read as '0'         bit 3-0       NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1:       1111 = No operation         101 = Erase general segment       0011 = Reserved         0010 = Memory page erase operation       0011 = Reserved         1111 = No operation       1101 = No operation         0010 = Reserved       If ERASE = 0:         11111 = No operation       1101 = No operation         0011 = Reserved       0000 = Reserved         1101 = No operation       1101 = No operation         1101 = No operation       1101 = No operation         1101 = No operation       1101 = No operation         0011 = Nemory word program operation       0011 = Memory word program operation         0011 = No operation       011 = No operation         0110 = No operation       011 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit 13            | WRERR: Write                | Sequence Er                    | ror Flag bit <sup>(</sup>   | 1)                          |                    |                        |               |

| bit 12-7 Unimplemented: Read as '0'<br>bit 6 ERASE: Erase/Program Enable bit <sup>(1)</sup><br>1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command<br>0 = Performs the program operation specified by NVMOP<3:0> on the next WR command<br>bit 5-4 Unimplemented: Read as '0'<br>bit 3-0 NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup><br>If ERASE = 1:<br>1111 = No operation<br>1101 = Erase general segment<br>0011 = No operation<br>0010 = Memory page erase operation<br>0010 = Reserved<br>0000 = Reserved<br>If ERASE = 0:<br>1111 = No operation<br>101 = No operation<br>101 = No operation<br>0011 = Memory word program operation<br>0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   | 1 = An improp<br>automatica | per program of ally on any set | or erase se<br>attempt of t | equence attem<br>he WR bit) |                    | on has occurre         | ed (bit is se |

| bit 6       ERASE: Erase/Program Enable bit <sup>(1)</sup> 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         bit 5-4       Unimplemented: Read as '0'         bit 3-0       NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1:       1111 = No operation         1011 = Erase general segment       0011 = Kno operation         0010 = Memory page erase operation       0001 = Reserved         0000 = Reserved       If ERASE = 0:         1111 = No operation       1101 = No operation         0010 = Memory page erase operation       0011 = Reserved         0000 = Reserved       If ERASE = 0:         1111 = No operation       1001 = No operation         1001 = No operation       0010 = No operation         0011 = No operation       0011 = No operation         0010 = No operation       0011 = No operation         0011 = No operation       0011 = No operation         0011 = No operation       0011 = No operation         0111 = No operation       0011 = No operation         0011 = No operation       0011 = No operation         0011 = No operation       0011 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | hit 10 7          |                             |                                |                             | ipieted normali             | у                  |                        |               |

| 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         bit 5-4       Unimplemented: Read as '0'         bit 3-0       NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1:       1111 = No operation         1011 = Erase general segment       0011 = No operation         0010 = Memory page erase operation       0001 = Reserved         0000 = Reserved       If ERASE = 0:         1111 = No operation       1101 = No operation         0101 = No operation       0001 = Reserved         0000 = Reserved       If ERASE = 0:         1111 = No operation       1001 = No operation         0011 = No operation       0011 = No operation         0010 = No operation       0011 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   | -                           |                                |                             |                             |                    |                        |               |

| <ul> <li>0 = Performs the program operation specified by NVMOP&lt;3:0&gt; on the next WR command</li> <li>bit 5-4 Unimplemented: Read as '0'</li> <li>bit 3-0 NVMOP&lt;3:0&gt;: NVM Operation Select bits<sup>(1,2)</sup></li> <li>If ERASE = 1:<br/>1111 = No operation<br/>1101 = Erase general segment<br/>0011 = No operation<br/>0010 = Memory page erase operation<br/>0001 = Reserved<br/>0000 = Reserved</li> <li>If ERASE = 0:<br/>1111 = No operation<br/>1101 = No operation<br/>0011 = Memory word program operation<br/>0010 = No operation</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DILO              |                             | •                              |                             |                             | <3:0> on the new   | vt WP comman           | d             |

| bit 5-4 Unimplemented: Read as '0'<br>bit 3-0 NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup><br>If ERASE = 1:<br>1111 = No operation<br>1101 = Erase general segment<br>0011 = No operation<br>0010 = Memory page erase operation<br>0001 = Reserved<br>0000 = Reserved<br>If ERASE = 0:<br>1111 = No operation<br>1101 = No operation<br>1101 = No operation<br>0011 = Memory word program operation<br>0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                   |                             |                                |                             |                             |                    |                        |               |

| bit 3-0 NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1: 1111 = No operation 1101 = Erase general segment 0011 = No operation 0010 = Memory page erase operation 0001 = Reserved 0000 = Reserved If ERASE = 0: 1111 = No operation 1101 = No operation 1101 = No operation 0011 = Memory word program operation 0010 = No operation 0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 5-4           |                             |                                |                             | ,                           |                    |                        |               |

| If ERASE = 1:         1111 = No operation         101 = Erase general segment         0011 = No operation         0010 = Memory page erase operation         0001 = Reserved         0000 = Reserved         If ERASE = 0:         1111 = No operation         1101 = No operation         0011 = Memory word program operation         0011 = Memory word program operation         0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bit 3-0           | -                           |                                |                             | ts <sup>(1,2)</sup>         |                    |                        |               |

| <pre>1101 = Erase general segment<br/>0011 = No operation<br/>0010 = Memory page erase operation<br/>0001 = Reserved<br/>0000 = Reserved<br/><u>If ERASE = 0:</u><br/>1111 = No operation<br/>1101 = No operation<br/>0011 = Memory word program operation<br/>0010 = No operation</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |                             |                                |                             |                             |                    |                        |               |

| 0011 = No operation         0010 = Memory page erase operation         0001 = Reserved         0000 = Reserved         If ERASE = 0:         1111 = No operation         1101 = No operation         0011 = Memory word program operation         0010 = No operation         0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   | •                           |                                |                             |                             |                    |                        |               |

| 0010 = Memory page erase operation<br>0001 = Reserved<br>0000 = Reserved<br><u>If ERASE = 0:</u><br>1111 = No operation<br>1101 = No operation<br>0011 = Memory word program operation<br>0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |                             |                                | ent                         |                             |                    |                        |               |