#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 6КВ (2К х 24)                                                                    |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b; D/A 2x10b                                                             |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 28-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs202a-i-ss |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                |                      | #0 DE00             | RIPTION                  |                                                                                                                                                                                                      |

|--------------------------------|----------------------|---------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                       | Pin<br>Type          | Buffer<br>Type      | PPS<br>Capable           | Description                                                                                                                                                                                          |

| AN0-AN7                        | I                    | Analog              | No                       | Analog input channels.                                                                                                                                                                               |

| CLKI                           | I                    | ST/CMOS             | No                       | External clock source input. Always associated with OSC1 pin                                                                                                                                         |

| CLKO                           | 0                    | _                   | No                       | function.<br>Oscillator crystal output. Connects to crystal or resonator in Crysta<br>Oscillator mode. Optionally functions as CLKO in RC and EC<br>modes. Always associated with OSC2 pin function. |

| OSC1                           | I                    | ST/CMOS             | No                       | Oscillator crystal input. ST buffer when configured in RC mode;                                                                                                                                      |

| OSC2                           | I/O                  | _                   | No                       | CMOS otherwise.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC<br>modes.                                    |

| CN0-CN15                       | I                    | ST                  | No                       | Change notification inputs. Can be software programmed for internal weak pull-ups on all inputs.                                                                                                     |

| IC1                            | I                    | ST                  | Yes                      | Capture Input 1.                                                                                                                                                                                     |

| OCFA<br>OC1                    | I<br>O               | ST<br>—             | Yes<br>Yes               | Compare Fault A input (for Compare Channel 1).<br>Compare Output 1.                                                                                                                                  |

| INT0<br>INT1<br>INT2           |                      | ST<br>ST<br>ST      | No<br>Yes<br>Yes         | External Interrupt 0.<br>External Interrupt 1.<br>External Interrupt 2.                                                                                                                              |

| RA0-RA4                        | I/O                  | ST                  | No                       | PORTA is a bidirectional I/O port.                                                                                                                                                                   |

| RB0-RB15 <sup>(1)</sup>        | I/O                  | ST                  | No                       | PORTB is a bidirectional I/O port.                                                                                                                                                                   |

| RP0-RP15 <sup>(1)</sup>        | I/O                  | ST                  | No                       | Remappable I/O pins.                                                                                                                                                                                 |

| T1CK<br>T2CK                   |                      | ST<br>ST            | Yes<br>Yes               | Timer1 external clock input.<br>Timer2 external clock input.                                                                                                                                         |

| U1CTS<br>U1RTS<br>U1RX<br>U1TX | <br>0<br> <br>0      | ST<br>—<br>ST<br>—  | Yes<br>Yes<br>Yes<br>Yes | UART1 Clear-to-Send.<br>UART1 Ready-to-Send.<br>UART1 receive.<br>UART1 transmit.                                                                                                                    |

| SCK1<br>SDI1<br>SDO1<br>SS1    | I/O<br>I<br>O<br>I/O | ST<br>ST<br>—<br>ST | Yes<br>Yes<br>Yes<br>Yes | Synchronous serial clock input/output for SPI1.<br>SPI1 data in.<br>SPI1 data out.<br>SPI1 slave synchronization or frame pulse I/O.                                                                 |

| SCL1<br>SDA1                   | I/O<br>I/O           | ST<br>ST            | No<br>No                 | Synchronous serial clock input/output for I2C1.<br>Synchronous serial data input/output for I2C1.                                                                                                    |

| TMS<br>TCK<br>TDI<br>TDO       | <br> <br> <br> <br>0 | TTL<br>TTL<br>TTL   | No<br>No<br>No<br>No     | JTAG Test mode select pin.<br>JTAG test clock input pin.<br>JTAG test data input pin.<br>JTAG test data output pin.                                                                                  |

## TABLE 1-1:PINOUT I/O DESCRIPTIONS

ST = Schmitt Trigger input with CMOS levels<br/>TTL = Transistor-Transistor LogicP = PowerO = OutputPPS = Peripheral Pin Select— = Does not applyNote 1:Not all pins are available on all devices. Refer to the specific device in the "Pin Diagrams" section for

availability.2: This pin is available on dsPIC33FJ09GS302 devices only.

## 3.4 CPU Control Registers

| R-0                  | R-0                                               | R/C-0                                  | R/C-0             | R-0                    | R/C-0                | R -0             | R/W-0         |

|----------------------|---------------------------------------------------|----------------------------------------|-------------------|------------------------|----------------------|------------------|---------------|

| OA                   | OB                                                | SA <sup>(1)</sup>                      | SB <sup>(1)</sup> | OAB                    | SAB <sup>(1,4)</sup> | DA               | DC            |

| bit 15               |                                                   |                                        |                   |                        | •                    |                  | bit 8         |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup>                              | R/W-0 <sup>(3)</sup>                   | R-0               | R/W-0                  | R/W-0                | R/W-0            | R/W-0         |

|                      | IPL<2:0> <sup>(2)</sup>                           |                                        | RA                | N                      | OV                   | Z                | С             |

| bit 7                |                                                   |                                        |                   |                        |                      |                  | bit (         |

| Legend:              |                                                   |                                        |                   |                        |                      |                  |               |

| C = Clearab          | le bit                                            | R = Readable                           | e bit             | U = Unimple            | mented bit, read     | as '0'           |               |

| S = Settable         | bit                                               | W = Writable                           | bit               | -n = Value at          | POR                  |                  |               |

| '1' = Bit is se      | et                                                | '0' = Bit is clea                      | ared              | x = Bit is unk         | nown                 |                  |               |

| bit 15               | OA: Accumul                                       | lator A Overflow                       | v Status bit      |                        |                      |                  |               |

|                      |                                                   | ator A overflowe                       |                   |                        |                      |                  |               |

| 1.1.4.4              |                                                   | ator A has not c                       |                   |                        |                      |                  |               |

| bit 14               |                                                   | lator B Overflow<br>ator B overflowe   |                   |                        |                      |                  |               |

|                      |                                                   | ator B has not c                       |                   |                        |                      |                  |               |

| bit 13               | SA: Accumul                                       | ator A Saturatio                       | on 'Sticky' Sta   | tus bit <sup>(1)</sup> |                      |                  |               |

|                      | 1 = Accumula                                      | ator A is saturat<br>ator A is not sat | ed or has bee     |                        | some time            |                  |               |

| bit 12               | SB: Accumul                                       | ator B Saturatio                       | on 'Sticky' Sta   | tus bit <sup>(1)</sup> |                      |                  |               |

|                      |                                                   | ator B is saturat<br>ator B is not sat |                   | en saturated at        | some time            |                  |               |

| bit 11               | <b>0AB:</b> 0A    0                               | DB Combined A                          | ccumulator O      | verflow Status         | bit                  |                  |               |

|                      | 1 = Accumula                                      | ators A or B hav                       | ve overflowed     |                        |                      |                  |               |

| bit 10               | <b>SAB:</b> SA    S                               | B Combined A                           | ccumulator 'St    | icky' Status bit       | (1,4)                |                  |               |

|                      | 1 = Accumula                                      |                                        | saturated or      | have been sat          | urated at some       | time in the past | t             |

| bit 9                | DA: DO Loop                                       | Active bit                             |                   |                        |                      |                  |               |

|                      | 1 = DO <b>loop ir</b>                             |                                        |                   |                        |                      |                  |               |

|                      | -                                                 | ot in progress                         |                   |                        |                      |                  |               |

| bit 8                |                                                   | U Half Carry/B                         |                   |                        |                      |                  |               |

|                      | of the res                                        | sult occurred                          |                   | -                      | data) or 8th low-o   |                  |               |

|                      | •                                                 | -out from the 4 the result occur       |                   | bit (for byte-siz      | ed data) or 8th      | low-order bit (1 | for word-size |

| Note 1: ⊤            | his bit can be rea                                | ad or cleared (n                       | ot set).          |                        |                      |                  |               |

| L                    | he IPL<2:0> bits<br>evel (IPL). The v<br>PL3 = 1. |                                        |                   |                        |                      |                  |               |

|                      |                                                   |                                        |                   |                        |                      |                  |               |

#### REGISTER 3-1: SR: CPU STATUS REGISTER

**3:** The IPL<2:0> Status bits are read-only when NSTDIS = 1 (INTCON1<15>).

**4:** Clearing this bit will clear SA and SB.

### REGISTER 3-1: SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup>                                                                        |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------|

|         | 111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled                                                                     |

|         | 110 = CPU Interrupt Priority Level is 6 (14)                                                                                               |

|         | 101 = CPU Interrupt Priority Level is 5 (13)<br>100 = CPU Interrupt Priority Level is 4 (12)                                               |

|         | 011 = CPU Interrupt Priority Level is 3 (11)                                                                                               |

|         | 010 = CPU Interrupt Priority Level is 2 (10)                                                                                               |

|         | 001 = CPU Interrupt Priority Level is 1 (9)                                                                                                |

|         | 000 = CPU Interrupt Priority Level is 0 (8)                                                                                                |

| bit 4   | RA: REPEAT Loop Active bit                                                                                                                 |

|         | 1 = REPEAT loop in progress                                                                                                                |

|         | 0 = REPEAT loop not in progress                                                                                                            |

| bit 3   | N: MCU ALU Negative bit                                                                                                                    |

|         | 1 = Result was negative                                                                                                                    |

|         | 0 = Result was non-negative (zero or positive)                                                                                             |

| bit 2   | OV: MCU ALU Overflow bit                                                                                                                   |

|         | This bit is used for signed arithmetic (2's complement). It indicates an overflow of a magnitude that causes the sign bit to change state. |

|         | <ul> <li>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)</li> <li>0 = No overflow occurred</li> </ul>           |

| bit 1   | <b>Z</b> : MCU ALU Zero bit                                                                                                                |

|         | 1 = An operation that affects the Z bit has set it at some time in the past                                                                |

|         | 0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)                                              |

| bit 0   | C: MCU ALU Carry/Borrow bit                                                                                                                |

|         | 1 = A carry-out from the Most Significant bit of the result occurred                                                                       |

|         | 0 = No carry-out from the Most Significant bit of the result occurred                                                                      |

|         |                                                                                                                                            |

Note 1: This bit can be read or cleared (not set).

- 2: The IPL<2:0> bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU Interrupt Priority Level (IPL). The value in parentheses indicates the IPL if IPL3 = 1. User interrupts are disabled when IPL3 = 1.

- 3: The IPL<2:0> Status bits are read-only when NSTDIS = 1 (INTCON1<15>).

- 4: Clearing this bit will clear SA and SB.

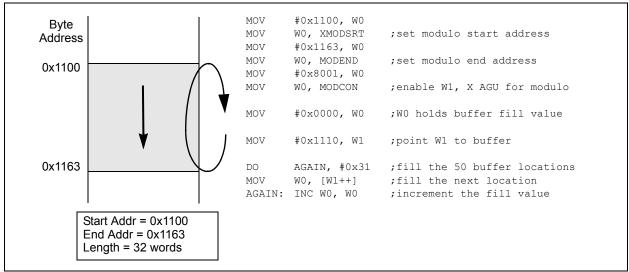

## 4.5 Modulo Addressing

Modulo Addressing mode is a method used to provide an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either data or program space (since the data pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into program space) and Y data spaces. Modulo Addressing can operate on any W register pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction as there are certain restrictions on the buffer start address (for incrementing buffers), or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

### 4.5.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

| Note: | Υ            | space      | Modulo      | Addressing   | EA   |

|-------|--------------|------------|-------------|--------------|------|

|       | calculations |            | assume      | word-sized   | data |

|       | (LS          | Sb of ever | y EA is alw | /ays clear). |      |

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

### 4.5.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that will operate with Modulo Addressing:

- If XWM = 15, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 15, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X data space when XWM is set to any value other than '15' and the XMODEN bit is set at MODCON<15>.

The Y Address Space Pointer W register (YWM) to which Modulo Addressing is to be applied is stored in MODCON<7:4>. Modulo Addressing is enabled for Y data space when YWM is set to any value other than '15' and the YMODEN bit is set at MODCON<14>.

### FIGURE 4-6: MODULO ADDRESSING OPERATION EXAMPLE

### 7.3 Interrupt Control and Status Registers

The following registers are implemented for the interrupt controller:

- INTCON1

- INTCON2

- IFSx

- IECx

- IPCx

- INTTREG

### 7.3.1 INTCON1 AND INTCON2

Global interrupt control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the Alternate Interrupt Vector Table.

### 7.3.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

### 7.3.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

### 7.3.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

## 7.3.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number (VECNUM<6:0>) and Interrupt Level (ILR<3:0>) bit fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence that they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit is found in IEC0<0> and the INT0IP bits are found in the first position of IPC0 (IPC0<2:0>).

## 7.3.6 STATUS/CONTROL REGISTERS

Although they are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality.

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user can change the current CPU priority level by writing to the IPL bits.

- The CORCON register contains the IPL3 bit, which together with IPL<2:0>, indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-1 through Register 7-35.

| U-0          | U-0           | U-0             | U-0            | U-0                                     | U-0                       | U-0                    | U-0                    |

|--------------|---------------|-----------------|----------------|-----------------------------------------|---------------------------|------------------------|------------------------|

| _            | _             | _               | _              | _                                       | —                         | _                      | —                      |

| bit 15       | ·             |                 |                |                                         |                           | ·                      | bit 8                  |

|              |               |                 |                |                                         |                           |                        |                        |

| U-0          | U-0           | U-0             | R/W-0          | U-0                                     | U-0                       | R/W-0                  | R/W-0                  |

| _            | —             |                 | ADCP6IF        | —                                       | —                         | ADCP3IF <sup>(1)</sup> | ADCP2IF <sup>(2)</sup> |

| bit 7        |               |                 |                |                                         |                           |                        | bit 0                  |

|              |               |                 |                |                                         |                           |                        |                        |

| Legend:      |               |                 |                |                                         |                           |                        |                        |

| R = Readat   | ole bit       | W = Writable    | bit            | U = Unimplei                            | mented bit, rea           | ad as '0'              |                        |

| -n = Value a | at POR        | '1' = Bit is se | t              | '0' = Bit is cleared x = Bit is unknown |                           |                        | nown                   |

|              |               |                 |                |                                         |                           |                        |                        |

| bit 15-5     | Unimplemen    | ted: Read as    | 'O'            |                                         |                           |                        |                        |

| bit 4        | ADCP6IF: A    | DC Pair 6 Con   | version Done I | nterrupt Flag S                         | Status bit                |                        |                        |

|              | 1 = Interrupt | request has o   | curred         |                                         |                           |                        |                        |

|              | 0 = Interrupt | request has no  | ot occurred    |                                         |                           |                        |                        |

| bit 3-2      | Unimplemen    | ted: Read as    | '0'            |                                         |                           |                        |                        |

| bit 1        | ADCP3IF: A    | DC Pair 3 Con   | version Done I | nterrupt Flag S                         | Status bit <sup>(1)</sup> |                        |                        |

|              | 1 = Interrupt | request has o   | curred         |                                         |                           |                        |                        |

|              | 0 = Interrupt | request has no  | ot occurred    |                                         |                           |                        |                        |

| bit 0        | ADCP2IF: AI   | DC Pair 2 Con   | version Done I | nterrupt Flag S                         | Status bit <sup>(2)</sup> |                        |                        |

|              | 1 = Interrupt | request has o   | curred         |                                         |                           |                        |                        |

|              |               | request has no  |                |                                         |                           |                        |                        |

- Note 1: This bit is not implemented in dsPIC33FJ06GS102A/202A devices.

- 2: This bit is not implemented in dsPIC33FJ06GS001/101A devices.

| REGISTER     | 7-13: IEC1:                                                                                        | INTERRUPT                           | ENABLE CO      | ONTROL RE               | GISTER 1             |                 |         |

|--------------|----------------------------------------------------------------------------------------------------|-------------------------------------|----------------|-------------------------|----------------------|-----------------|---------|

| U-0          | U-0                                                                                                | R/W-0                               | U-0            | U-0                     | U-0                  | U-0             | U-0     |

| _            |                                                                                                    | INT2IE                              | —              | _                       | _                    | _               |         |

| bit 15       |                                                                                                    |                                     |                |                         | •                    |                 | bit 8   |

|              |                                                                                                    |                                     |                |                         |                      |                 |         |

| U-0          | U-0                                                                                                | U-0                                 | R/W-0          | R/W-0                   | R/W-0                | R/W-0           | R/W-0   |

| —            | _                                                                                                  | —                                   | INT1IE         | CNIE                    | AC1IE <sup>(1)</sup> | MI2C1IE         | SI2C1IE |

| bit 7        |                                                                                                    |                                     |                |                         |                      |                 | bit 0   |

|              |                                                                                                    |                                     |                |                         |                      |                 |         |

| Legend:      |                                                                                                    |                                     |                |                         |                      |                 |         |

| R = Readab   | le bit                                                                                             | W = Writable                        | bit            | U = Unimpler            | mented bit, read     | d as '0'        |         |

| -n = Value a | t POR                                                                                              | '1' = Bit is set                    |                | '0' = Bit is cle        | eared                | x = Bit is unkr | nown    |

|              |                                                                                                    |                                     |                |                         |                      |                 |         |

| bit 15-14    | -                                                                                                  | ted: Read as '                      |                |                         |                      |                 |         |

| bit 13       |                                                                                                    | rnal Interrupt 2                    |                |                         |                      |                 |         |

|              |                                                                                                    | request is enab<br>request is not e |                |                         |                      |                 |         |

| bit 12-5     |                                                                                                    | ited: Read as '                     |                |                         |                      |                 |         |

| bit 4        | -                                                                                                  | rnal Interrupt 1                    |                |                         |                      |                 |         |

| Dil 4        |                                                                                                    | request is enab                     |                |                         |                      |                 |         |

|              |                                                                                                    | request is not e                    |                |                         |                      |                 |         |

| bit 3        | CNIE: Input C                                                                                      | Change Notifica                     | tion Interrupt | Enable bit              |                      |                 |         |

|              |                                                                                                    | request is enab                     |                |                         |                      |                 |         |

|              | •                                                                                                  | request is not e                    |                |                         |                      |                 |         |

| bit 2        |                                                                                                    | og Comparator                       |                | able bit <sup>(1)</sup> |                      |                 |         |

|              | <ul> <li>1 = Interrupt request is enabled</li> <li>0 = Interrupt request is not enabled</li> </ul> |                                     |                |                         |                      |                 |         |

| bit 1        | •                                                                                                  | 1 Master Even                       |                | aabla bit               |                      |                 |         |

|              |                                                                                                    | request is enab                     | -              |                         |                      |                 |         |

|              |                                                                                                    | request is enab                     |                |                         |                      |                 |         |

| bit 0        | •                                                                                                  | 1 Slave Events                      |                | able bit                |                      |                 |         |

|              |                                                                                                    | request is enab                     | •              |                         |                      |                 |         |

|              | 0 = Interrupt r                                                                                    | request is not e                    | nabled         |                         |                      |                 |         |

|              |                                                                                                    |                                     |                |                         |                      |                 |         |

## **Note 1:** This bit is not implemented in dsPIC33FJ06GS101A/102A devices.

| REGISTER       | R 7-18: IEC7:                                                           | INTERRUPT                           | ENABLE CO                             |                      | GISTER 7             |                        |                        |

|----------------|-------------------------------------------------------------------------|-------------------------------------|---------------------------------------|----------------------|----------------------|------------------------|------------------------|

| U-0            | U-0                                                                     | U-0                                 | U-0                                   | U-0                  | U-0                  | U-0                    | U-0                    |

| —              | —                                                                       | —                                   | —                                     | —                    | —                    | —                      | _                      |

| bit 15         |                                                                         |                                     |                                       |                      |                      |                        | bit 8                  |

|                |                                                                         |                                     |                                       |                      |                      |                        |                        |

| U-0            | U-0                                                                     | U-0                                 | R/W-0                                 | U-0                  | U-0                  | R/W-0                  | R/W-0                  |

|                | _                                                                       | _                                   | ADCP6IE                               |                      |                      | ADCP3IE <sup>(1)</sup> | ADCP2IE <sup>(2)</sup> |

| bit 7          |                                                                         |                                     |                                       |                      |                      |                        | bit 0                  |

| Legend:        |                                                                         |                                     |                                       |                      |                      |                        |                        |

| R = Readab     | ole bit                                                                 | W = Writable                        | bit                                   | U = Unimpler         | nented bit, read     | as '0'                 |                        |

| -n = Value a   |                                                                         | '1' = Bit is set                    |                                       | '0' = Bit is cleared |                      | x = Bit is unknown     |                        |

|                |                                                                         |                                     |                                       | o Dicio die          |                      | X Dit io uniti         |                        |

| bit 15-5       | Unimplemen                                                              | ted: Read as '                      | 0'                                    |                      |                      |                        |                        |

| bit 4          | ADCP6IE: AI                                                             | DC Pair 6 Conv                      | ersion Done I                         | nterrupt Enable      | e bit                |                        |                        |

|                |                                                                         | request is enab                     |                                       |                      |                      |                        |                        |

|                | 0 = Interrupt                                                           | request is not e                    | nabled                                |                      |                      |                        |                        |

| bit 3-2        | Unimplemented: Read as '0'                                              |                                     |                                       |                      |                      |                        |                        |

|                | ADCP3IE: ADC Pair 3 Conversion Done Interrupt Enable bit <sup>(1)</sup> |                                     |                                       |                      |                      |                        |                        |

| bit 1          | ADCP3IE: AI                                                             | DC Pair 3 Conv                      | ersion Done I                         | nterrupt Enable      | e bit <sup>(1)</sup> |                        |                        |

| bit 1          |                                                                         | DC Pair 3 Conv<br>request is enab   |                                       | nterrupt Enable      | e bit <sup>(1)</sup> |                        |                        |

| bit 1          | 1 = Interrupt                                                           |                                     | led                                   | nterrupt Enable      | e bit <sup>(1)</sup> |                        |                        |

| bit 1<br>bit 0 | 1 = Interrupt<br>0 = Interrupt                                          | request is enab                     | led<br>nabled                         |                      |                      |                        |                        |

|                | 1 = Interrupt<br>0 = Interrupt<br>ADCP2IE: Al<br>1 = Interrupt          | request is enab<br>request is not e | led<br>nabled<br>ersion Done I<br>led |                      |                      |                        |                        |

### **Note 1:** This bit is not implemented in dsPIC33FJ06GS102A/202A devices.

2: This bit is not implemented in dsPIC33FJ06GS001/101A devices.

| U-0          | R/W-1                                                                          | R/W-0                                           | R/W-0        | U-0               | R/W-1               | R/W-0                     | R/W-0 |  |  |  |  |  |

|--------------|--------------------------------------------------------------------------------|-------------------------------------------------|--------------|-------------------|---------------------|---------------------------|-------|--|--|--|--|--|

| _            |                                                                                | T1IP<2:0>                                       |              | —                 |                     | OC1IP<2:0> <sup>(1)</sup> |       |  |  |  |  |  |

| pit 15       |                                                                                |                                                 |              |                   |                     |                           | bit   |  |  |  |  |  |

|              |                                                                                |                                                 |              |                   |                     |                           |       |  |  |  |  |  |

| U-0          | R/W-1                                                                          | R/W-0                                           | R/W-0        | U-0               | R/W-1               | R/W-0                     | R/W-0 |  |  |  |  |  |

| —            |                                                                                | IC1IP<2:0> <sup>(2)</sup>                       |              | —                 |                     | INT0IP<2:0>               |       |  |  |  |  |  |

| oit 7        |                                                                                |                                                 |              |                   |                     |                           | bit   |  |  |  |  |  |

| Legend:      |                                                                                |                                                 |              |                   |                     |                           |       |  |  |  |  |  |

| R = Readabl  | e bit                                                                          | W = Writable b                                  | bit          | U = Unimple       | mented bit, re      | ad as '0'                 |       |  |  |  |  |  |

| n = Value at | POR                                                                            | '1' = Bit is set                                |              | '0' = Bit is cl   | eared               | x = Bit is unkn           | own   |  |  |  |  |  |

|              |                                                                                |                                                 |              |                   |                     |                           |       |  |  |  |  |  |

| bit 15       | -                                                                              | ented: Read as '0                               |              |                   |                     |                           |       |  |  |  |  |  |

| bit 14-12    | T1IP<2:0>: Timer1 Interrupt Priority bits                                      |                                                 |              |                   |                     |                           |       |  |  |  |  |  |

|              | <ul> <li>111 = Interrupt is Priority 7 (highest priority interrupt)</li> </ul> |                                                 |              |                   |                     |                           |       |  |  |  |  |  |

|              | •                                                                              |                                                 |              |                   |                     |                           |       |  |  |  |  |  |

|              | •                                                                              |                                                 |              |                   |                     |                           |       |  |  |  |  |  |

|              |                                                                                | upt is Priority 1<br>upt source is disa         | abled        |                   |                     |                           |       |  |  |  |  |  |

| bit 11       | Unimpleme                                                                      | ented: Read as '0                               | ,            |                   |                     |                           |       |  |  |  |  |  |

| bit 10-8     | OC1IP<2:0>: Output Compare Channel 1 Interrupt Priority bits <sup>(1)</sup>    |                                                 |              |                   |                     |                           |       |  |  |  |  |  |

|              | 111 = Interrupt is Priority 7 (highest priority interrupt)                     |                                                 |              |                   |                     |                           |       |  |  |  |  |  |

|              | •                                                                              |                                                 |              |                   |                     |                           |       |  |  |  |  |  |

|              |                                                                                |                                                 |              |                   |                     |                           |       |  |  |  |  |  |

|              | •<br>001 = Interrupt is Priority 1                                             |                                                 |              |                   |                     |                           |       |  |  |  |  |  |

|              |                                                                                | upt source is disa                              | abled        |                   |                     |                           |       |  |  |  |  |  |

| bit 7        | Unimpleme                                                                      | ented: Read as '0                               | ,            |                   |                     |                           |       |  |  |  |  |  |

| bit 6-4      | IC1IP<2:0>                                                                     | : Input Capture C                               | hannel 1 Int | errupt Priority I | oits <sup>(2)</sup> |                           |       |  |  |  |  |  |

|              |                                                                                | upt is Priority 7 (I                            |              |                   |                     |                           |       |  |  |  |  |  |

|              | •                                                                              |                                                 |              |                   |                     |                           |       |  |  |  |  |  |

|              | •                                                                              |                                                 |              |                   |                     |                           |       |  |  |  |  |  |

|              | •<br>001 = Interrupt is Priority 1                                             |                                                 |              |                   |                     |                           |       |  |  |  |  |  |

|              |                                                                                | upt source is disa                              | abled        |                   |                     |                           |       |  |  |  |  |  |

| bit 3        | Unimpleme                                                                      | nted: Read as '0                                | ,            |                   |                     |                           |       |  |  |  |  |  |

| bit 2-0      | INT0IP<2:0                                                                     | INT0IP<2:0>: External Interrupt 0 Priority bits |              |                   |                     |                           |       |  |  |  |  |  |

|              |                                                                                | upt is Priority 7 (I                            |              |                   |                     |                           |       |  |  |  |  |  |

|              | •                                                                              |                                                 |              |                   |                     |                           |       |  |  |  |  |  |

|              | •                                                                              |                                                 |              |                   |                     |                           |       |  |  |  |  |  |

|              | •                                                                              |                                                 |              |                   |                     |                           |       |  |  |  |  |  |

|              | 001 = Interr                                                                   | upt is Priority 1                               |              |                   |                     |                           |       |  |  |  |  |  |

## **Note 1:** These bits are not implemented in the dsPIC33FJ06GS001 device.

2: These bits are not implemented in dsPIC33FJ06GS001/101A/102A devices.

| U-0          | U-0                         | U-0              | U-0            | U-0               | U-0              | U-0             | U-0   |

|--------------|-----------------------------|------------------|----------------|-------------------|------------------|-----------------|-------|

| _            | —                           | _                |                | —                 | _                | —               |       |

| bit 15       |                             |                  |                |                   |                  |                 | bit 8 |

|              |                             |                  |                |                   |                  |                 |       |

| U-0          | U-0                         | R/W-1            | R/W-1          | R/W-1             | R/W-1            | R/W-1           | R/W-1 |

| —            | —                           |                  |                | T2CK              | (R<5:0>          |                 |       |

| bit 7        |                             |                  |                |                   |                  |                 | bit 0 |

|              |                             |                  |                |                   |                  |                 |       |

| Legend:      |                             |                  |                |                   |                  |                 |       |

| R = Readab   | le bit                      | W = Writable I   | oit            | U = Unimpler      | mented bit, read | as '0'          |       |

| -n = Value a | t POR                       | '1' = Bit is set |                | '0' = Bit is cle  | ared             | x = Bit is unkn | iown  |

|              |                             |                  |                |                   |                  |                 |       |

| bit 15-6     | Unimplement                 | ted: Read as '0  | )'             |                   |                  |                 |       |

| bit 5-0      | T2CKR<5:0>:                 | Assign Timer2    | 2 External Clo | ock (T2CK) to the | he Correspondi   | ng RPn Pin bits | 5     |

|              | 111111 <b>= Inp</b>         | ut tied to Vss   |                |                   |                  |                 |       |

|              |                             | ut tied to RP35  |                |                   |                  |                 |       |

|              |                             | ut tied to RP34  |                |                   |                  |                 |       |

|              |                             | ut tied to RP33  |                |                   |                  |                 |       |

|              | 100000 = Input tied to RP32 |                  |                |                   |                  |                 |       |

### REGISTER 10-4: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

•

•

00000 = Input tied to RP0

| U-0           | U-0                                                                                                                                   | R/W-1                     | R/W-1          | R/W-1            | R/W-1                | R/W-1                      | R/W-1 |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------|------------------|----------------------|----------------------------|-------|--|--|--|--|

| —             | —                                                                                                                                     | SCK1R<5:0> <sup>(1)</sup> |                |                  |                      |                            |       |  |  |  |  |

| bit 15        |                                                                                                                                       |                           |                |                  |                      |                            | bit 8 |  |  |  |  |

|               |                                                                                                                                       |                           |                |                  |                      |                            |       |  |  |  |  |

| U-0           | U-0                                                                                                                                   | R/W-1                     | R/W-1          | R/W-1            | R/W-1                | R/W-1                      | R/W-1 |  |  |  |  |

|               |                                                                                                                                       |                           |                | SDI1R            | <5:0> <sup>(1)</sup> |                            |       |  |  |  |  |

| bit 7         |                                                                                                                                       |                           |                |                  |                      |                            | bit ( |  |  |  |  |

|               |                                                                                                                                       |                           |                |                  |                      |                            |       |  |  |  |  |

| Legend:       |                                                                                                                                       |                           |                |                  |                      |                            |       |  |  |  |  |

| R = Readabl   |                                                                                                                                       | W = Writable              |                | •                | mented bit, read     | d as '0'                   |       |  |  |  |  |

| -n = Value at | t POR                                                                                                                                 | '1' = Bit is set          |                | '0' = Bit is cle | ared                 | x = Bit is unkr            | nown  |  |  |  |  |

| L:1 4 5 4 4   |                                                                                                                                       | ta da Da a da a (         | ~ '            |                  |                      |                            |       |  |  |  |  |

| bit 15-14     | -                                                                                                                                     | ted: Read as '            |                |                  |                      | (4)                        |       |  |  |  |  |

| bit 13-8      | SCK1R<5:0>                                                                                                                            | : Assign SPI1             | Clock Input (S | CK1) to the Co   | orresponding R       | Pn Pin bits <sup>(1)</sup> |       |  |  |  |  |

|               | 111111 = Input tied to Vss                                                                                                            |                           |                |                  |                      |                            |       |  |  |  |  |

|               | 100011 = Input tied to RP35<br>100010 = Input tied to RP34                                                                            |                           |                |                  |                      |                            |       |  |  |  |  |

|               |                                                                                                                                       |                           |                |                  |                      |                            |       |  |  |  |  |

|               |                                                                                                                                       | out tied to RP3           |                |                  |                      |                            |       |  |  |  |  |

|               |                                                                                                                                       | out tied to RP32          | 2              |                  |                      |                            |       |  |  |  |  |

|               | •                                                                                                                                     |                           |                |                  |                      |                            |       |  |  |  |  |

|               | •                                                                                                                                     |                           |                |                  |                      |                            |       |  |  |  |  |

|               | 00000 = Input tied to RP0                                                                                                             |                           |                |                  |                      |                            |       |  |  |  |  |

| bit 7-6       |                                                                                                                                       | ted: Read as '            | 0'             |                  |                      |                            |       |  |  |  |  |

| bit 5-0       | -                                                                                                                                     |                           |                | 11) to the Corre | esponding RPn        | Pin bits <sup>(1)</sup>    |       |  |  |  |  |

|               | <b>SDI1R&lt;5:0&gt;:</b> Assign SPI1 Data Input (SDI1) to the Corresponding RPn Pin bits <sup>(1)</sup><br>111111 = Input tied to Vss |                           |                |                  |                      |                            |       |  |  |  |  |

|               | 111111 = Input tied to Vss<br>100011 = Input tied to RP35                                                                             |                           |                |                  |                      |                            |       |  |  |  |  |

|               | 100011 = Input tied to RP35<br>100010 = Input tied to RP34                                                                            |                           |                |                  |                      |                            |       |  |  |  |  |

|               | 100001 = Input tied to RP33                                                                                                           |                           |                |                  |                      |                            |       |  |  |  |  |

|               |                                                                                                                                       | out tied to RP32          |                |                  |                      |                            |       |  |  |  |  |

|               | •                                                                                                                                     |                           |                |                  |                      |                            |       |  |  |  |  |

|               | •                                                                                                                                     |                           |                |                  |                      |                            |       |  |  |  |  |

|               | •                                                                                                                                     |                           |                |                  |                      |                            |       |  |  |  |  |

|               | 00000 <b>= Inpu</b>                                                                                                                   | t tied to RPO             |                |                  |                      |                            |       |  |  |  |  |

|               | 00000 <b>– mpu</b>                                                                                                                    |                           |                |                  |                      |                            |       |  |  |  |  |

## REGISTER 10-8: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

**Note 1:** These bits are not implemented in the dsPIC33FJ06GS001 device.

## REGISTER 17-1: I2C1CON: I2C1 CONTROL REGISTER (CONTINUED)

| bit 8 | SMEN: SMBus Input Levels bit                                                                                                                                                                                                 |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Enables I/O pin thresholds compliant with SMBus specification</li> <li>0 = Disables SMBus input thresholds</li> </ul>                                                                                           |

| bit 7 | GCEN: General Call Enable bit (when operating as I <sup>2</sup> C slave)                                                                                                                                                     |

|       | <ul> <li>1 = Enables interrupt when a general call address is received in the I2C1RSR<br/>(module is enabled for reception)</li> <li>0 = General call address is disabled</li> </ul>                                         |

| bit 6 | STREN: SCL1 Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)                                                                                                                                              |

|       | Used in conjunction with SCLREL bit.<br>1 = Enables software or receives clock stretching<br>0 = Disables software or receives clock stretching                                                                              |

| bit 5 | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                    |

|       | Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends NACK during Acknowledge<br>0 = Sends ACK during Acknowledge                                                                      |

| bit 4 | <b>ACKEN:</b> Acknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                  |

|       | <ul> <li>1 = Initiates Acknowledge sequence on SDA1 and SCL1 pins and transmits ACKDT data bit.<br/>Hardware is clear at end of master Acknowledge sequence.</li> <li>0 = Acknowledge sequence is not in progress</li> </ul> |

| bit 3 | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                  |

|       | <ul> <li>1 = Enables Receive mode for I<sup>2</sup>C. Hardware is clear at end of eighth bit of master receive data byte.</li> <li>0 = Receive sequence is not in progress</li> </ul>                                        |

| bit 2 | <b>PEN:</b> Stop Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                            |

|       | <ul> <li>1 = Initiates Stop condition on SDA1 and SCL1 pins. Hardware is clear at end of master Stop sequence.</li> <li>0 = Stop condition is not in progress</li> </ul>                                                     |

| bit 1 | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                 |

|       | <ul> <li>1 = Initiates Repeated Start condition on SDA1 and SCL1 pins. Hardware is clear at end of master<br/>Repeated Start sequence.</li> </ul>                                                                            |

|       | 0 = Repeated Start condition is not in progress                                                                                                                                                                              |

| bit 0 | <b>SEN:</b> Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                           |

|       | 1 = Initiates Start condition on SDA1 and SCL1 pins. Hardware is clear at end of master Start sequence.                                                                                                                      |

|       | 0 = Start condition is not in progress                                                                                                                                                                                       |

| U-0                               | U-0   | U-0                | U-0                                | U-0                  | U-0    | R/W-0              | R/W-0     |  |

|-----------------------------------|-------|--------------------|------------------------------------|----------------------|--------|--------------------|-----------|--|

| —                                 | —     | —                  |                                    | —                    | —      | AMSK               | AMSK<9:8> |  |

| bit 15                            | ·     | ·                  |                                    |                      | -<br>- | -                  | bit 8     |  |

|                                   |       |                    |                                    |                      |        |                    |           |  |

| R/W-0                             | R/W-0 | R/W-0              | R/W-0                              | R/W-0                | R/W-0  | R/W-0              | R/W-0     |  |

|                                   |       |                    | AMS                                | K<7:0>               |        |                    |           |  |

| bit 7                             |       |                    |                                    |                      |        |                    | bit 0     |  |

|                                   |       |                    |                                    |                      |        |                    |           |  |

| Legend:                           |       |                    |                                    |                      |        |                    |           |  |

| R = Readable bit W = Writable bit |       | bit                | U = Unimplemented bit, read as '0' |                      |        |                    |           |  |

| -n = Value at POR                 |       | R '1' = Bit is set |                                    | '0' = Bit is cleared |        | x = Bit is unknown |           |  |

bit 15-10 Unimplemented: Read as '0'

bit 9-0 AMSK<9:0>: Mask for Address bit x Select bits

1 = Enables masking for bit x of incoming message address; bit match not required in this position

0 = Disables masking for bit x; bit match required in this position

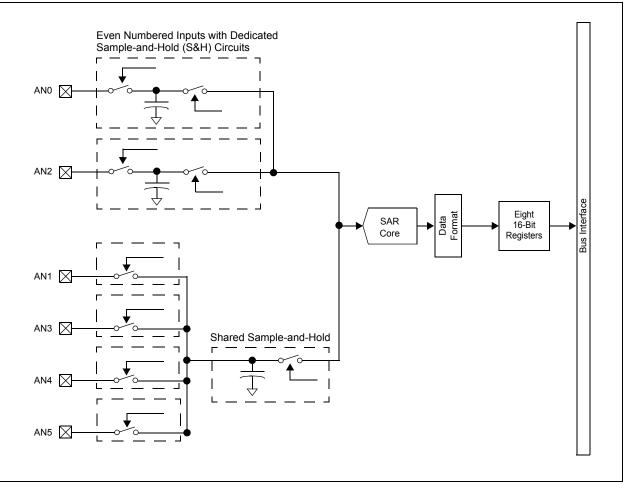

### FIGURE 19-3: ADC BLOCK DIAGRAM FOR dsPIC33FJ06GS102A DEVICE

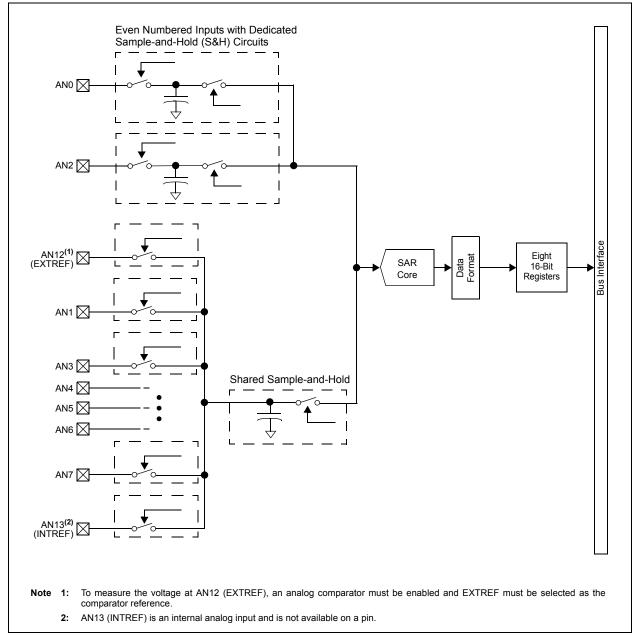

### FIGURE 19-5: ADC BLOCK DIAGRAM FOR dsPIC33FJ09GS302 DEVICE

| U-0                               | U-0                  | U-0              | U-0                  | U-0                                | U-0                    | U-0                | U-0   |