Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XFI

| Product Status             | Obsolete                                                                          |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 6KB (2K x 24)                                                                     |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 1K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 6x10b; D/A 2x10b                                                              |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-VQFN Exposed Pad                                                               |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs202at-e-mm |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

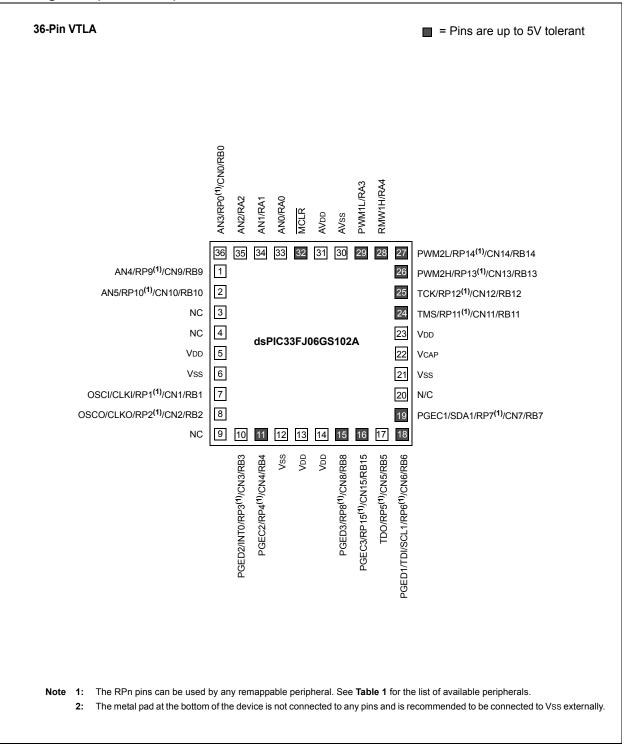

#### Pin Diagrams (Continued)

#### 2.5 ICSP<sup>™</sup> Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins, are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and Input Voltage High (VIH) and Input Voltage Low (VIL) pin requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins), programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>TM</sup>.

For more information on MPLAB ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site (www.microchip.com):

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS51765)

- "Multi-Tool Design Advisory" (DS51764)

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator User's Guide" (DS51616)

- *"Using MPLAB<sup>®</sup> REAL ICE™"* (poster) (DS51749)

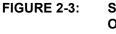

#### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

| File Name | Addr<br>Offset | Bit 15  | Bit 14 | Bit 13  | Bit 12   | Bit 11   | Bit 10  | Bit 9     | Bit 8     | Bit 7     | Bit 6  | Bit 5   | Bit 4  | Bit 3   | Bit 2     | Bit 1   | Bit 0   | All<br>Resets |

|-----------|----------------|---------|--------|---------|----------|----------|---------|-----------|-----------|-----------|--------|---------|--------|---------|-----------|---------|---------|---------------|

| PWMCON2   | 0440           | FLTSTAT | CLSTAT | TRGSTAT | FLTIEN   | CLIEN    | TRGIEN  | ITB       | MDCS      | DTC<      | 1:0>   | —       | —      | —       | CAM       | XPRES   | IUE     | 0000          |

| IOCON2    | 0442           | PENH    | PENL   | POLH    | POLL     | PMOD     | )<1:0>  | OVRENH    | OVRENL    | OVRDA     | T<1:0> | FLTDA   | T<1:0> | CLDA    | AT<1:0>   | SWAP    | OSYNC   | 0000          |

| FCLCON2   | 0444           | IFLTMOD |        |         | CLSRC<4: | 0>       |         | CLPOL     | CLMOD     |           | FLT    | SRC<4:0 | >      |         | FLTPOL    | FLTMO   | D<1:0>  | 0000          |

| PDC2      | 0446           |         |        |         |          |          |         |           | PDC2<15:0 | >         |        |         |        |         |           |         |         | 0000          |

| PHASE2    | 0448           |         |        |         |          |          |         | P         | HASE2<15  | :0>       |        |         |        |         |           |         |         | 0000          |

| DTR2      | 044A           | _       |        |         |          |          |         |           |           | DTR2<13:0 | )>     |         |        |         |           |         |         | 0000          |

| ALTDTR2   | 044C           | _       | _      |         |          |          |         |           | AI        | TDTR2<1   | 3:0>   |         |        |         |           |         |         | 0000          |

| SDC2      | 044E           |         |        |         |          |          |         |           | SDC2<15:0 | >         |        |         |        |         |           |         |         | 0000          |

| SPHASE2   | 0450           |         |        |         |          |          |         | SI        | PHASE2<18 | 5:0>      |        |         |        |         |           |         |         | 0000          |

| TRIG2     | 0452           |         |        |         |          |          | TRGCM   | P<15:3>   |           |           |        |         |        |         | _         | _       | _       | 0000          |

| TRGCON2   | 0454           |         | TRGD   | IV<3:0> |          | _        | _       | _         | _         | DTM       | _      |         |        | TR      | GSTRT<5:0 | )>      |         | 0000          |

| STRIG2    | 0456           |         |        |         |          |          | STRGCN  | /IP<15:3> |           |           |        |         |        |         | _         | _       | _       | 0000          |

| PWMCAP2   | 0458           |         |        |         |          |          | PWMCA   | P2<15:3>  |           |           |        |         |        |         | _         | _       | _       | 0000          |

| LEBCON2   | 045A           | PHR     | PHF    | PLR     | PLF      | FLTLEBEN | CLLEBEN |           |           | LEI       | B<6:0> |         |        |         | _         | _       | _       | 0000          |

| AUXCON2   | 045E           | HRPDIS  | HRDDIS | _       | _        | _        | _       | _         | _         | _         |        |         | CHOPS  | EL<3:0> |           | CHOPHEN | CHOPLEN | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| IABLE 4  | -21.        | nion   | SFEEL                   |        |         | GISTEI |           | OK US | FICJJI | 30003        | IUZA A | UD USFIC | 33L10009                              | ZUZA  |          |         |       |              |

|----------|-------------|--------|-------------------------|--------|---------|--------|-----------|-------|--------|--------------|--------|----------|---------------------------------------|-------|----------|---------|-------|--------------|

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                  | Bit 13 | Bit 12  | Bit 11 | Bit 10    | Bit 9 | Bit 8  | Bit 7        | Bit 6  | Bit 5    | Bit 4                                 | Bit 3 | Bit 2    | Bit 1   | Bit 0 | All<br>Reset |

| ADCON    | 0300        | ADON   | _                       | ADSIDL | SLOWCLK | _      | GSWTRG    | —     | FORM   | EIE          | ORDER  | SEQSAMP  | ASYNCSAMP                             | _     | A        | DCS<2:0 | >     | 0003         |

| ADPCFG   | 0302        | _      | —                       | _      | —       | _      | —         |       | _      | —            |        | PCFG5    | PCFG4                                 | PCFG3 | PCFG2    | PCFG1   | PCFG0 | 0000         |

| ADSTAT   | 0306        | _      | —                       | _      | —       | _      | —         |       | _      | —            | P6RDY  | _        | —                                     | _     | P2RDY    | P1RDY   | P0RDY | 0000         |

| ADBASE   | 0308        |        |                         |        |         |        |           | Α     | DBASE< | 15:1>        |        |          | · · · · · · · · · · · · · · · · · · · |       |          |         | 0000  |              |

| ADCPC0   | 030A        | IRQEN1 | PEND1                   | SWTRG1 |         | TRG    | SRC1<4:0> |       |        | IRQEN0       | PEND0  | SWTRG0   |                                       | TRGS  | RC0<4:0> |         |       | 0000         |

| ADCPC1   | 030C        | _      | —                       | _      | _       | _      | —         |       | _      | IRQEN2       | PEND2  | SWTRG2   | TRGSRC2<4:0>                          |       |          |         | 0000  |              |

| ADCPC3   | 0310        | _      | _                       | _      | _       | _      | _         | _     | _      | IRQEN6       | PEND6  | SWTRG6   |                                       | TRGS  | RC6<4:0> |         |       | 0000         |

| ADCBUF0  | 0320        |        |                         |        |         |        |           |       | ADC D  | ata Buffer 0 | )      |          |                                       |       |          |         |       | XXXX         |

| ADCBUF1  | 0322        |        |                         |        |         |        |           |       | ADC D  | ata Buffer 1 |        |          |                                       |       |          |         |       | XXXX         |

| ADCBUF2  | 0324        |        |                         |        |         |        |           |       | ADC D  | ata Buffer 2 | 2      |          |                                       |       |          |         |       | XXXX         |

| ADCBUF3  | 0326        |        |                         |        |         |        |           |       | ADC D  | ata Buffer 3 | 3      |          |                                       |       |          |         |       | XXXX         |

| ADCBUF4  | 0328        |        |                         |        |         |        |           |       | ADC D  | ata Buffer 4 | ļ      |          |                                       |       |          |         |       | XXXX         |

| ADCBUF5  | 032A        |        | ADC Data Buffer 5       |        |         |        |           |       |        |              | XXXX   |          |                                       |       |          |         |       |              |

| ADCBUF12 | 0338        |        | ADC Data Buffer 12 xxxx |        |         |        |           |       |        |              | XXXX   |          |                                       |       |          |         |       |              |

| ADCBUF13 | 033A        |        | ADC Data Buffer 13 xxxx |        |         |        |           |       |        |              |        | XXXX     |                                       |       |          |         |       |              |

### TABLE 4-21: HIGH-SPEED 10-BIT ADC REGISTER MAP FOR dsPIC33FJ06GS102A AND dsPIC33FJ06GS202A

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE 4- | 26:         | PERIPI | HERAL  | . PIN SE | LECT IN | PUT RE  | GISTER | R MAP | FOR d | sPIC33 | FJ06GS | 202A AN | ID dsP | IC33FJ0 | 9GS302 |       |       |   |

|----------|-------------|--------|--------|----------|---------|---------|--------|-------|-------|--------|--------|---------|--------|---------|--------|-------|-------|---|

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13   | Bit 12  | Bit 11  | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6  | Bit 5   | Bit 4  | Bit 3   | Bit 2  | Bit 1 | Bit 0 |   |

| RPINR0   | 0680        | —      | —      |          |         | INT1R<  | 5:0>   |       |       | —      | —      | -       | —      | —       | —      | —     | -     | Î |

| RPINR1   | 0682        | _      | _      | _        | _       | _       | —      | —     | —     | —      | _      |         |        | INT2R   | <5:0>  |       |       | Ĩ |

| RPINR2   | 0684        | _      | _      |          |         | T1CKR<  | 5:0>   |       |       | —      | _      | _       | —      | _       | _      | _     | _     | Ĩ |

| RPINR3   | 0686        | _      | _      | _        | _       | _       | —      | —     | —     | —      | _      |         |        | T2CKF   | <5:0>  |       |       | Ĩ |

| RPINR7   | 068E        | _      | _      | _        | _       | _       | _      | —     | —     | —      | _      |         |        | IC1R<   | <5:0>  |       |       | Ī |

| RPINR11  | 0696        | _      | _      | _        | _       | _       | —      | _     | —     | —      | _      |         |        | OCFAF   | <5:0>  |       |       | Ī |

| RPINR18  | 06A4        | _      | _      |          |         | U1CTSR- | <5:0>  |       |       | —      | _      |         |        | U1RXF   | <5:0>  |       |       | Ī |

| RPINR20  | 06A8        | _      | _      |          |         | SCK1R<  | 5:0>   |       |       | _      | _      |         |        | SDI1R   | <5:0>  |       |       | Ī |

| RPINR21  | 06AA        | _      | _      | _        | —       | _       | _      | —     | —     | _      |        |         |        | SS1R    | <5:0>  |       |       | Τ |

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

RPINR34 Legend:

RPINR29

RPINR30

RPINR31

RPINR32

RPINR33

06BA

06BC

06BE

06C0

06C2

06C4

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

FLT1R<5:0>

FLT3R<5:0>

FLT5R<5:0>

FLT7R<5:0>

SYNCI1R<5:0>

#### **TABLE 4-27:** PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33FJ06GS001 AND dsPIC33FJ06GS101A

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12    | Bit 11 | Bit 10  | Bit 9 | Bit 8 | Bit 7 | Bit 6     | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|-----------|--------|---------|-------|-------|-------|-----------|-------|-------|-------|-------|-------|-------|---------------|

| RPOR0     | 06D0 | _      | _      |        |           | RP1    | R<5:0>  |       |       | _     | —         |       |       | RP0R< | <5:0> |       |       | 0000          |

| RPOR1     | 06D2 | _      | _      |        |           | RP3    | R<5:0>  |       |       | _     | _         |       |       | RP2R  | <5:0> |       |       | 0000          |

| RPOR2     | 06D4 | _      | _      |        | RP5R<5:0> |        |         |       | _     | _     | RP4R<5:0> |       |       |       |       | 0000  |       |               |

| RPOR3     | 06D6 | _      | —      |        |           | RP7    | R<5:0>  |       |       | —     | _         |       |       | RP6R  | <5:0> |       |       | 0000          |

| RPOR16    | 06F0 | _      | _      |        |           | RP33   | 3R<5:0> |       |       | —     | _         |       |       | RP32R | <5:0> |       |       | 0000          |

| RPOR17    | 06F2 | _      | _      |        |           | RP3    | 5R<5:0> |       |       | _     | -         |       |       | RP34R | <5:0> |       |       | 0000          |

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

All Resets 3F00 003F 3F00 003F 003F 003F 3F3F 3F3F

003F

3F00

3F3F

3F3F

3F3F

3F3F

003F

\_

\_

FLT2R<5:0>

FLT4R<5:0>

FLT6R<5:0>

FLT8R<5:0>

SYNCI2R<5:0>

\_

| Addressing Mode                                           | Description                                                                                            |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the File register is specified explicitly.                                              |

| Register Direct                                           | The contents of a register are accessed directly.                                                      |

| Register Indirect                                         | The contents of Wn forms the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn forms the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.             |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                     |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                              |

#### TABLE 4-39: FUNDAMENTAL ADDRESSING MODES SUPPORTED

# 4.4.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP accumulator class of instructions provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

| Note: | For the MOV instructions, the addressing mode specified in the instruction can differ |

|-------|---------------------------------------------------------------------------------------|

|       | for the source and destination EA.                                                    |

|       | However, the 4-bit Wb (register offset)                                               |

|       | field is shared by both source and                                                    |

|       | destination (but typically only used by                                               |

|       | one).                                                                                 |

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- · Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.4.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the data pointers through register indirect tables.

The two-source operand prefetch registers must be members of the set {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must, therefore, be valid addresses within X data space for W8 and W9 and Y data space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- Register Indirect

- · Register Indirect Post-modified by 2

- · Register Indirect Post-modified by 4

- Register Indirect Post-modified by 6

- Register Indirect with Register Offset (Indexed)

#### 4.4.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ADD Acc, the source of an operand or result is implied by the opcode itself. Certain operations, such as NOP, do not have any operands.

### 5.2 RTSP Operation

The dsPIC33FJ06GS001/101A/102A/202A and dsPIC33FJ09GS302 Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to erase a page of memory, which consists of eight rows (512 instructions) at a time, and to program one row or one word at a time. Table 25-12 shows typical erase and programming times. The 8-row erase pages and single row write rows are edge-aligned from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively.

The program memory implements holding buffers that can contain 64 instructions of programming data. Prior to the actual programming operation, the write data must be loaded into the buffers sequentially. The instruction words loaded must always be from a group of 64 boundary.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register. A total of 64 TBLWTL and TBLWTH instructions are required to load the instructions.

All of the table write operations are single-word writes (two instruction cycles) because only the buffers are written. A programming cycle is required for programming each row.

### 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

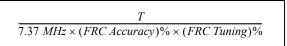

The programming time depends on the FRC accuracy (see Table 25-19) and the value of the FRC Oscillator Tuning register (see Register 8-4). Use the following formula to calculate the minimum and maximum values for the Row Write Time, Page Erase Time and Word Write Cycle Time parameters (see Table 25-12).

#### EQUATION 5-1: PROGRAMMING TIME

For example, if the device is operating at +125°C, the FRC accuracy will be  $\pm 5\%$ . If the TUN<5:0> bits (see Register 8-4) are set to `b111111, the minimum row write time is equal to Equation 5-2.

#### EQUATION 5-2: MINIMUM PAGE ERASE TIME

$$T_{RW} = \frac{168517 \ Cycles}{7.37 \ MHz \times (1 + 0.05) \times (1 - 0.00375)} = 21.85 ms$$

The maximum row write time is equal to Equation 5-3.

#### EQUATION 5-3: MAXIMUM PAGE ERASE TIME

$$T_{RW} = \frac{168517 \text{ Cycles}}{7.37 \text{ MHz} \times (1 - 0.05) \times (1 - 0.00375)} = 24.16 \text{ ms}$$

Setting the WR bit (NVMCON<15>) starts the operation, and the WR bit is automatically cleared when the operation is finished.

### 5.4 Control Registers

Two SFRs are used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to **Section 5.3 "Programming Operations"** for further details.

### 6.2 System Reset

There are two types of Reset:

- Cold Reset

- Warm Reset

A cold Reset is the result of a Power-on Reset (POR) or a Brown-out Reset (BOR). On a cold Reset, the FNOSC Configuration bits in the FOSC Configuration register select the device clock source.

A warm Reset is the result of all the other Reset sources, including the RESET instruction. On warm Reset, the device will continue to operate from the current clock source, as indicated by the Current Oscillator Selection bits (COSC<2:0>) in the Oscillator Control register (OSCCON<14:12>).

The device is kept in a Reset state until the system power supplies have stabilized at appropriate levels and the oscillator clock is ready. The sequence in which this occurs is provided in Figure 6-2.

| Oscillator Mode        | Oscillator<br>Start-up Delay | Oscillator<br>Start-up Timer | PLL Lock Time        | Total Delay                             |

|------------------------|------------------------------|------------------------------|----------------------|-----------------------------------------|

| FRC, FRCDIV16, FRCDIVN | Toscd <sup>(1)</sup>         | _                            | _                    | Toscd <sup>(1)</sup>                    |

| FRCPLL                 | Toscd <sup>(1)</sup>         | —                            | ТLОСК <sup>(3)</sup> | Toscd + Tlock <sup>(1,3)</sup>          |

| XT                     | Toscd <sup>(1)</sup>         | Tost <sup>(2)</sup>          | —                    | Toscd + Tost <sup>(1,2)</sup>           |

| HS                     | Toscd <sup>(1)</sup>         | Tost <sup>(2)</sup>          | —                    | Toscd + Tost <sup>(1,2)</sup>           |

| EC                     | —                            | —                            | —                    | —                                       |

| XTPLL                  | Toscd <sup>(1)</sup>         | Tost <sup>(2)</sup>          | ТLОСК <sup>(3)</sup> | TOSCD + TOST + TLOCK <sup>(1,2,3)</sup> |

| HSPLL                  | Toscd <sup>(1)</sup>         | Tost <sup>(2)</sup>          | ТLOCK <sup>(3)</sup> | TOSCD + TOST + TLOCK <sup>(1,2,3)</sup> |

| ECPLL                  | —                            | —                            | ТLOCK <sup>(3)</sup> | ТLОСК <sup>(3)</sup>                    |

| LPRC                   | Toscd <sup>(1)</sup>         |                              | _                    | Toscd <sup>(1)</sup>                    |

**Note 1:** TOSCD = Oscillator start-up delay (1.1 μs max. for FRC, 70 μs max. for LPRC). Crystal oscillator start-up times vary with crystal characteristics, load capacitance, etc.

**2:** TOST = Oscillator Start-up Timer (OST) delay (1024 oscillator clock period). For example, TOST = 102.4 μs for a 10 MHz crystal and TOST = 32 ms for a 32 kHz crystal.

**3:** TLOCK = PLL lock time (1.5 ms nominal) if PLL is enabled.

TABLE 6-1: OSCILLATOR DELAY

| <b>REGISTER 7</b>    | -1: SR: C               | PU STATUS I          | REGISTER | )              |                  |        |       |

|----------------------|-------------------------|----------------------|----------|----------------|------------------|--------|-------|

| R-0                  | R-0                     | R/C-0                | R/C-0    | R-0            | R/C-0            | R-0    | R/W-0 |

| OA                   | OB                      | SA                   | SB       | OAB            | SAB              | DA     | DC    |

| bit 15               |                         |                      |          |                |                  |        | bit 8 |

|                      |                         |                      |          |                |                  |        |       |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup>    | R/W-0 <sup>(3)</sup> | R-0      | R/W-0          | R/W-0            | R/W-0  | R/W-0 |

|                      | IPL<2:0> <sup>(2)</sup> |                      | RA       | N              | OV               | Z      | С     |

| bit 7                |                         |                      |          |                |                  |        | bit 0 |

|                      |                         |                      |          |                |                  |        |       |

| Legend:              |                         | C = Clearable        | bit      | U = Unimpler   | nented bit, read | as '0' |       |

| R = Readable         | bit                     | W = Writable I       | bit      | -n = Value at  | POR              |        |       |

| '1' = Bit is set     |                         | '0' = Bit is clea    | ared     | x = Bit is unk | nown             |        |       |

### (4)

bit 7-5 IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2,3)</sup>

111 = CPU Interrupt Priority Level is 7 (15), user interrupts are disabled

- 110 = CPU Interrupt Priority Level is 6 (14)

- 101 = CPU Interrupt Priority Level is 5 (13)

- 100 = CPU Interrupt Priority Level is 4 (12)

- 011 = CPU Interrupt Priority Level is 3 (11)

- 010 = CPU Interrupt Priority Level is 2 (10) 001 = CPU Interrupt Priority Level is 1 (9)

- 000 = CPU Interrupt Priority Level is 0 (8)

- Note 1: For complete register details, see Register 3-1.

#### 2: The IPL<2:0> bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL3 = 1. User interrupts are disabled when IPL3 = 1.

3: The IPL<2:0> status bits are read-only when NSTDIS (INTCON1<15>) = 1.

#### CORCON: CORE CONTROL REGISTER<sup>(1)</sup> **REGISTER 7-2:**

|         |       | •••••         |        |                     |       |         |       |

|---------|-------|---------------|--------|---------------------|-------|---------|-------|

| U-0     | U-0   | U-0           | R/W-0  | R/W-0               | R-0   | R-0     | R-0   |

| _       | —     | _             | US     | EDT                 |       | DL<2:0> |       |

| bit 15  |       |               |        |                     |       |         | bit 8 |

|         |       |               |        |                     |       |         |       |

| R/W-0   | R/W-0 | R/W-1         | R/W-0  | R/C-0               | R/W-0 | R/W-0   | R/W-0 |

| SATA    | SATB  | SATDW         | ACCSAT | IPL3 <sup>(2)</sup> | PSV   | RND     | IF    |

| bit 7   |       |               |        |                     |       |         | bit 0 |

|         |       |               |        |                     |       |         |       |

| Legend: |       | C = Clearable | e bit  |                     |       |         |       |

|         |       |               |        |                     |       |         |       |

| R = Readable bit    | W = Writable bit    | -n = Value at POR           | '1' = Bit is set |

|---------------------|---------------------|-----------------------------|------------------|

| 0' = Bit is cleared | 'x = Bit is unknown | U = Unimplemented bit, read | 1 as '0'         |

|                     |                     |                             |                  |

IPL3: CPU Interrupt Priority Level Status bit 3(2) bit 3

- 1 = CPU Interrupt Priority Level is greater than 7

- 0 = CPU Interrupt Priority Level is 7 or less

#### Note 1: For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

### 8.1 CPU Clocking System

The devices provide six system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with PLL

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- · Low-Power RC (LPRC) Oscillator

- FRC Oscillator with Postscaler

#### 8.1.1 SYSTEM CLOCK SOURCES

The Fast RC (FRC) internal oscillator runs at a nominal frequency of 7.37 MHz. User software can tune the FRC frequency. User software can optionally specify a factor (ranging from 1:2 to 1:256) by which the FRC clock frequency is divided. This factor is selected using the FRCDIV<2:0> (CLKDIV<10:8>) bits.

The primary oscillator can use one of the following as its clock source:

- XT (Crystal): Crystals and ceramic resonators in the range of 3 MHz to 10 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- HS (High-Speed Crystal): Crystals in the range of 10 MHz to 32 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- EC (External Clock): The external clock signal is directly applied to the OSC1 pin.

The LPRC internal oscIllator runs at a nominal frequency of 32.768 kHz. It is also used as a reference clock by the Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The clock signals generated by the FRC and primary oscillators can be optionally applied to an on-chip Phase Lock Loop (PLL) to provide a wide range of

output frequencies for device operation. PLL configuration is described in **Section 8.1.3 "PLL Configuration"**.

The FRC frequency depends on the FRC accuracy (see Table 25-20) and the value of the FRC Oscillator Tuning register (see Register 8-4).

#### 8.1.2 SYSTEM CLOCK SELECTION

The oscillator source used at a device Power-on Reset event is selected using Configuration bit settings. The Oscillator Configuration bit settings are located in the Configuration registers in the program memory. (Refer to Section 22.1 "Configuration Bits" for further details.) The initial Oscillator Selection Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), and the Primary Oscillator Mode Select Configuration bits. POSCMD<1:0> (FOSC<1:0>), select the oscillator source that is used at a Power-on Reset. The FRC primary oscillator is the default (unprogrammed) selection.

The Configuration bits allow users to choose among 12 different clock modes, shown in Table 8-1.

The output of the oscillator (or the output of the PLL if a PLL mode has been selected), FOSC, is divided by 2 to generate the device instruction clock (FCY) and the peripheral clock time base (FP). FCY defines the operating speed of the device and speeds up to 40 MHz are supported by the device architecture.

Instruction execution speed or device operating frequency, FCY, is given by Equation 8-1.

# EQUATION 8-1: DEVICE OPERATING FREQUENCY

FCY = FOSC/2

| Oscillator Mode                                 | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See Note |

|-------------------------------------------------|-------------------|-------------|------------|----------|

| Fast RC Oscillator with Divide-by-N (FRCDIVN)   | Internal          | XX          | 111        | 1, 2     |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16) | Internal          | XX          | 110        | 1        |

| Low-Power RC Oscillator (LPRC)                  | Internal          | XX          | 101        | 1        |

| Reserved                                        | Reserved          | XX          | 100        | —        |

| Primary Oscillator (HS) with PLL (HSPLL)        | Primary           | 10          | 011        | _        |

| Primary Oscillator (XT) with PLL (XTPLL)        | Primary           | 01          | 011        | —        |

| Primary Oscillator (EC) with PLL (ECPLL)        | Primary           | 00          | 011        | 1        |

| Primary Oscillator (HS)                         | Primary           | 10          | 010        | _        |

| Primary Oscillator (XT)                         | Primary           | 01          | 010        | —        |

| Primary Oscillator (EC)                         | Primary           | 00          | 010        | 1        |

| Fast RC Oscillator with PLL (FRCPLL)            | Internal          | XX          | 001        | 1        |

| Fast RC Oscillator (FRC)                        | Internal          | XX          | 000        | 1        |

### TABLE 8-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

#### 8.5 Clock Switching Operation

Applications are free to switch among any of the four clock sources (primary, LP, FRC and LPRC) under software control at any time. To limit the possible side effects of this flexibility, devices have a safeguard lock built into the switch process.

Note: Primary Oscillator mode has three different submodes (XT, HS and EC), which are determined by the POSCMD<1:0> Configuration bits. While an application can switch to and from Primary Oscillator mode in software, it cannot switch among the different primary submodes without reprogramming the device.

#### 8.5.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the FOSC Configuration register must be programmed to '0'. (Refer to **Section 22.1 "Configuration Bits"** for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and Fail-Safe Clock Monitor function are disabled. This is the default setting.

The NOSC<2:0> control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSC<2:0> bits (OSCCON<14:12>) reflect the clock source selected by the FNOSC Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled. It is held at '0' at all times.

#### 8.5.2 OSCILLATOR SWITCHING SEQUENCE

To perform a clock switch, the following basic sequence is required:

- 1. If desired, read the COSC<2:0> bits to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- Write the appropriate value to the NOSC<2:0> control bits for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit (OSCCON<0>) to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically as follows:

- The clock switching hardware compares the COSC<2:0> status bits with the new value of the NOSC<2:0> control bits. If they are the same, the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the LOCK (OSCCON<5>) and the CF (OSCCON<3>) status bits are cleared.

- The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware waits until the Oscillator Start-up Timer (OST) expires. If the new source is using the PLL, the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSC<2:0> bit values are transferred to the COSC<2:0> status bits.

- The old clock source is turned off at this time, with the exception of LPRC (if WDT or FSCM is enabled).

Note 1: The processor continues to execute code throughout the clock switching sequence. Timing-sensitive code should not be executed during this time.

- 2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- 3: Refer to Section 42. "Oscillator (Part IV)" (DS70307) in the "dsPIC33F/ PIC24H Family Reference Manual" for details.

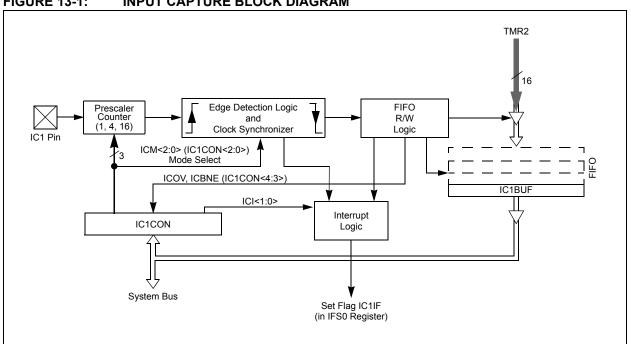

#### 13.0 INPUT CAPTURE

- **Note 1:** This data sheet summarizes the features of the dsPIC33FJ06GS001/101A/102A/ 202A and dsPIC33FJ09GS302 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "Input Capture" (DS70198) in the "dsPIC33F/ PIC24H Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The input capture module is useful in applications requiring frequency (period) and pulse measurement.

The input capture module captures the 16-bit value of the selected Time Base register when an event occurs at the IC1 pin. The events that cause a capture event are listed below in three categories:

- · Simple Capture Event modes:

- Capture timer value on every falling edge of input at IC1 pin

- Capture timer value on every rising edge of input at IC1 pin

- Capture timer value on every edge (rising and falling)

- · Prescaler Capture Event modes:

- Capture timer value on every 4th rising edge of input at IC1 pin

- Capture timer value on every 16th rising edge of input at IC1 pin

The input capture module uses the Timer2 module as its timer; however, it can use either an internal or external clock.

Other operational features include:

- · Device wake-up from capture pin during CPU Sleep and Idle modes

- · Interrupt on input capture event

- 4-word FIFO buffer for capture values:

- Interrupt optionally generated after 1, 2, 3 or 4 buffer locations are filled

- · Use of input capture to provide additional sources of external interrupts

#### **FIGURE 13-1: INPUT CAPTURE BLOCK DIAGRAM**

#### REGISTER 16-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- - 00 = Primary prescale 64:1

- Note 1: This bit is not used in Framed SPI modes. Program this bit to '0' for the Framed SPI modes (FRMEN = 1).

- 2: Do not set both Primary and Secondary prescalers to a value of 1:1.

- **3:** This bit must be cleared when FRMEN = 1.

#### 24.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

#### 24.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

### 24.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

#### 24.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

#### 24.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB IDE compatibility

| DC CHARACTERISTICS |                        |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |               |        |                                |  |  |  |

|--------------------|------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------|--------------------------------|--|--|--|

| Param.             | Typical <sup>(1)</sup> | Max. | Units                                                                                                                                                                                                                                                                         | ts Conditions |        |                                |  |  |  |

| Operating          | Current (IDD)          | (2)  |                                                                                                                                                                                                                                                                               |               |        |                                |  |  |  |

| DC20d              | 15                     | 23   | mA                                                                                                                                                                                                                                                                            | -40°C         |        |                                |  |  |  |

| DC20a              | 15                     | 23   | mA                                                                                                                                                                                                                                                                            | +25°C         | 3.3V   |                                |  |  |  |

| DC20b              | 15                     | 23   | mA                                                                                                                                                                                                                                                                            | +85°C         | - 3.3V | 10 MIPS                        |  |  |  |

| DC20c              | 15                     | 23   | mA                                                                                                                                                                                                                                                                            | +125°C        |        |                                |  |  |  |

| DC21d              | 23                     | 34   | mA                                                                                                                                                                                                                                                                            | -40°C         |        |                                |  |  |  |

| DC21a              | 23                     | 34   | mA                                                                                                                                                                                                                                                                            | +25°C         | 2.21/  | 16 MIPS <sup>(3)</sup>         |  |  |  |

| DC21b              | 23                     | 34   | mA                                                                                                                                                                                                                                                                            | +85°C         | - 3.3V |                                |  |  |  |

| DC21c              | 23                     | 34   | mA                                                                                                                                                                                                                                                                            | +125°C        |        |                                |  |  |  |

| DC22d              | 25                     | 38   | mA                                                                                                                                                                                                                                                                            | -40°C         |        |                                |  |  |  |

| DC22a              | 25                     | 38   | mA                                                                                                                                                                                                                                                                            | +25°C         | 3.3V   | 20 MIPS <sup>(3)</sup>         |  |  |  |

| DC22b              | 25                     | 38   | mA                                                                                                                                                                                                                                                                            | +85°C         | - 3.3V | 20 MIPS*/                      |  |  |  |

| DC22c              | 25                     | 38   | mA                                                                                                                                                                                                                                                                            | +125°C        |        |                                |  |  |  |

| DC23d              | 34                     | 51   | mA                                                                                                                                                                                                                                                                            | -40°C         |        | 30 MIPS <sup>(3)</sup>         |  |  |  |

| DC23a              | 34                     | 51   | mA                                                                                                                                                                                                                                                                            | +25°C         | 3.3V   |                                |  |  |  |

| DC23b              | 34                     | 51   | mA                                                                                                                                                                                                                                                                            | +85°C         | 3.3V   |                                |  |  |  |

| DC23c              | 34                     | 51   | mA                                                                                                                                                                                                                                                                            | +125°C        |        |                                |  |  |  |

| DC24d              | 43                     | 64   | mA                                                                                                                                                                                                                                                                            | -40°C         |        |                                |  |  |  |

| DC24a              | 43                     | 64   | mA                                                                                                                                                                                                                                                                            | +25°C         | 3.3V   | 40 MIPS <sup>(3)</sup>         |  |  |  |

| DC24b              | 43                     | 64   | mA                                                                                                                                                                                                                                                                            | +85°C         | 3.3V   | 40 MIF 5 7                     |  |  |  |

| DC24c              | 43                     | 64   | mA                                                                                                                                                                                                                                                                            | +125°C        |        |                                |  |  |  |

| DC25d              | 83                     | 125  | mA                                                                                                                                                                                                                                                                            | -40°C         |        | 40 MIPS                        |  |  |  |

| DC25a              | 83                     | 125  | mA                                                                                                                                                                                                                                                                            | +25°C         | 3.3V   | See Note 2, except PWM and ADC |  |  |  |

| DC25b              | 83                     | 125  | mA                                                                                                                                                                                                                                                                            | +85°C         | 5.3V   | are operating at maximum speed |  |  |  |

| DC25c              | 83                     | 125  | mA                                                                                                                                                                                                                                                                            | +125°C        |        | (PTCON2 = 0x0000)              |  |  |  |

#### TABLE 25-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

2: IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

- Oscillator is configured in EC mode, OSC1 is driven with external square wave from rail-to-rail

- CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD; WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (PMDx bits are all zeroed)

- CPU is executing while (1) statement

- **3:** These parameters are characterized but not tested in manufacturing.

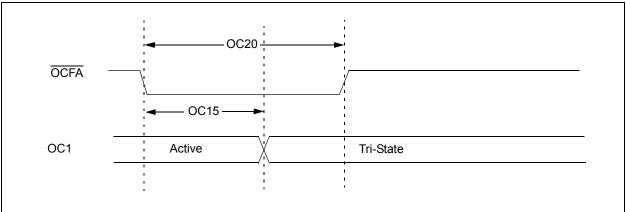

#### FIGURE 25-8: OC/PWM MODULE TIMING CHARACTERISTICS

#### TABLE 25-27: SIMPLE OC/PWM MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                  | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |      |          |       |            |  |  |

|--------------------|--------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|-------|------------|--|--|

| Param.             | Symbol | Characteristic <sup>(1)</sup>    | Min.                                                                                                                                                                                                                                                                                | Тур. | Max.     | Units | Conditions |  |  |

| OC15               | Tfd    | Fault Input to PWM I/O<br>Change | —                                                                                                                                                                                                                                                                                   | _    | Tcy + 20 | ns    |            |  |  |

| OC20               | TFLT   | Fault Input Pulse Width          | Tcy + 20                                                                                                                                                                                                                                                                            | _    | _        | ns    |            |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

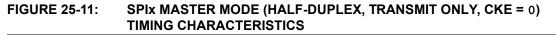

| AC CHARAG            | CTERISTICS                               |                                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |     |     |     |  |  |

|----------------------|------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|--|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)                                                                                                                                                                                                                                            | СКЕ | СКР | SMP |  |  |

| 15 MHz               | Table 25-30                              | _                                           | _                                                                                                                                                                                                                                                                                     | 0,1 | 0,1 | 0,1 |  |  |

| 9 MHz                | _                                        | Table 25-31                                 | —                                                                                                                                                                                                                                                                                     | 1   | 0,1 | 1   |  |  |

| 9 MHz                | _                                        | Table 25-32                                 | —                                                                                                                                                                                                                                                                                     | 0   | 0,1 | 1   |  |  |

| 15 MHz               | _                                        | —                                           | Table 25-33                                                                                                                                                                                                                                                                           | 1   | 0   | 0   |  |  |

| 11 MHz               | —                                        | —                                           | Table 25-34                                                                                                                                                                                                                                                                           | 1   | 1   | 0   |  |  |

| 15 MHz               | _                                        | —                                           | Table 25-35                                                                                                                                                                                                                                                                           | 0   | 1   | 0   |  |  |

| 11 MHz               | _                                        | —                                           | Table 25-36                                                                                                                                                                                                                                                                           | 0   | 0   | 0   |  |  |

#### TABLE 25-29: SPIx MAXIMUM DATA/CLOCK RATE SUMMARY

| DC CHARACTERISTICS <sup>(2)</sup> |                       |                                                   | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature: $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                      |      |       |                                                                                                                         |  |  |

|-----------------------------------|-----------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------|-------|-------------------------------------------------------------------------------------------------------------------------|--|--|

| Param.                            | Symbol Characteristic |                                                   | Min.                                                                                                                                                                                            | Min. Typ. Max. Units |      | Units | Comments                                                                                                                |  |  |

| CM10                              | VIOFF                 | Input Offset Voltage                              | -58                                                                                                                                                                                             | +14/-40              | 66   | mV    |                                                                                                                         |  |  |

| CM11                              | VICM                  | Input Common-Mode<br>Voltage Range <sup>(1)</sup> | 0                                                                                                                                                                                               | —                    | AVdd | V     |                                                                                                                         |  |  |

| CM14                              | TRESP                 | Large Signal Response                             | 21                                                                                                                                                                                              | 30                   | 49   | ns    | V+ input step of 100 mv while<br>V- input held at AVDD/2. Delay<br>measured from analog input pin to<br>PWM output pin. |  |  |

Note 1: These parameters are for design guidance only and are not tested in manufacturing.

2: Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device analog modules, such as the ADC, etc., will function but with degraded performance below VDDMIN. Refer to Parameter BO10 in Table 25-11 for BOR values.

| AC and DC CHARACTERISTICS <sup>(2)</sup> |        |                                           | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature: $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                |            |       |                                                                                                         |  |

|------------------------------------------|--------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------|-------|---------------------------------------------------------------------------------------------------------|--|

| Param.                                   | Symbol | Characteristic                            | Min.                                                                                                                                                                                            | Min. Typ. Max. |            | Units | Comments                                                                                                |  |

| DA01                                     | EXTREF | External Voltage Reference <sup>(1)</sup> | 0                                                                                                                                                                                               |                | AVDD - 1.6 | V     |                                                                                                         |  |

| DA08                                     | INTREF | Internal Voltage Reference <sup>(1)</sup> | 1.15                                                                                                                                                                                            | 1.25           | 1.35       | V     |                                                                                                         |  |

| DA02                                     | CVRES  | Resolution                                | 10                                                                                                                                                                                              |                |            | Bits  |                                                                                                         |  |

| DA03                                     | INL    | Integral Nonlinearity Error               | -7                                                                                                                                                                                              | -1             | +7         | LSB   | AVDD = 3.3V,<br>DACREF = (AVDD/2)V                                                                      |  |

| DA04                                     | DNL    | Differential Nonlinearity Error           | -5                                                                                                                                                                                              | -0.5           | +5         | LSB   |                                                                                                         |  |

| DA05                                     | EOFF   | Offset Error                              | 0.4                                                                                                                                                                                             | -0.8           | 2.6        | %     |                                                                                                         |  |

| DA06                                     | EG     | Gain Error                                | 0.4                                                                                                                                                                                             | -1.8           | 5.2        | %     |                                                                                                         |  |

| DA07                                     | TSET   | Settling Time <sup>(1)</sup>              | 711                                                                                                                                                                                             | 1551           | 2100       | ns    | Measured when<br>RANGE = 1 (high range)<br>and the CMREF<9:0> bits<br>transition from 0x1FF to<br>0x300 |  |

#### TABLE 25-42: DAC MODULE SPECIFICATIONS

Note 1: Parameters are for design guidance only and are not tested in manufacturing.

2: Overall functional device operation at VBORMIN < VDD < VDDMIN is tested but not characterized. All device analog modules such as the ADC, etc., will function but with degraded performance below VDDMIN. Refer to Parameter BO10 in Table 25-11 for BOR values.

### APPENDIX A: REVISION HISTORY

#### Revision A (July 2011)

This is the initial released version of this document.

#### **Revision B (February 2012)**

This revision includes formatting changes and minor typographical updates throughout the data sheet text.

Where applicable, new sections were added to each peripheral chapter that provide information and links to related resources, as well as helpful tips. For examples, see Section 18.1 "UART Helpful Tips" and Section 18.1 "UART Helpful Tips".

The data sheet status was updated from Advance Information to Preliminary.

In addition, all occurrences to the package known as TLA were updated to VTLA.

All other major changes are referenced by their respective section in Table A-1.

| Section Name                                                                               | Update Description                                                                                                                                                      |  |  |  |  |  |

|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| "16-Bit Microcontrollers and<br>Digital Signal Controllers with<br>High-Speed PWM, ADC and | The previous content was reorganized and is now presented as the first page of the data sheet.                                                                          |  |  |  |  |  |

| Comparators"                                                                               | Relocated the Referenced Sources content, which was previously presented in <b>Section 1.0 "Device Overview"</b> .                                                      |  |  |  |  |  |

| Section 2.0 "Guidelines for<br>Getting Started with 16-Bit<br>Digital Signal Controllers"  | Updated the Recommended Minimum Connection diagram (see Figure 2-1).                                                                                                    |  |  |  |  |  |

| Section 4.0 "Memory                                                                        | Updated the Program Memory Map (see Figure 4-1).                                                                                                                        |  |  |  |  |  |

| Organization"                                                                              | Updated bits 10-8 in IPC27 of the Interrupt Controller Register Map for dsPIC33FJ06GS001 Devices (see Table 4-4).                                                       |  |  |  |  |  |

|                                                                                            | Renamed the CHOPCLK<6:0> bits in the CHOP register to: CHOP<6:0> in the High-Speed PWM Register Map (see Table 4-12).                                                   |  |  |  |  |  |