Welcome to E-XFL.COM

Microchip Technology - DSPIC33FJ06GS202AT-E/TL Datasheet

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 6KB (2K x 24)                                                                     |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | ·                                                                                 |

| RAM Size                   | 1K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 6x10b; D/A 2x10b                                                              |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 36-VFTLA Exposed Pad                                                              |

| Supplier Device Package    | 36-VTLA (5x5)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs202at-e-tl |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

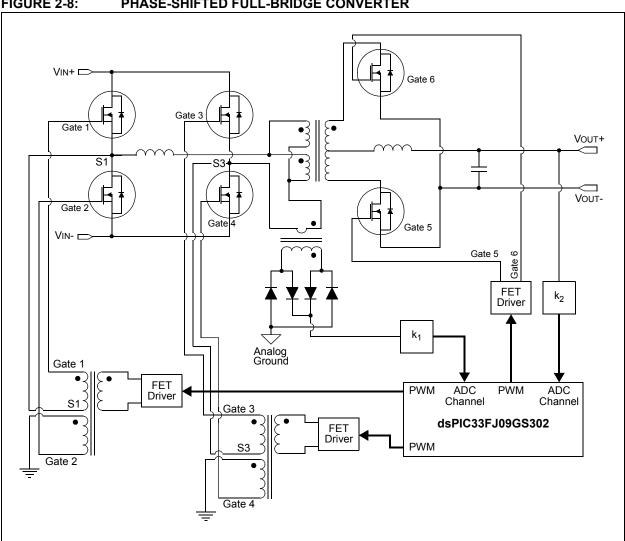

FIGURE 2-8: PHASE-SHIFTED FULL-BRIDGE CONVERTER

#### REGISTER 3-1: SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup>                                                                        |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------|

|         | 111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled                                                                     |

|         | 110 = CPU Interrupt Priority Level is 6 (14)                                                                                               |

|         | 101 = CPU Interrupt Priority Level is 5 (13)<br>100 = CPU Interrupt Priority Level is 4 (12)                                               |

|         | 011 = CPU Interrupt Priority Level is 3 (11)                                                                                               |

|         | 010 = CPU Interrupt Priority Level is 2 (10)                                                                                               |

|         | 001 = CPU Interrupt Priority Level is 1 (9)                                                                                                |

|         | 000 = CPU Interrupt Priority Level is 0 (8)                                                                                                |

| bit 4   | RA: REPEAT Loop Active bit                                                                                                                 |

|         | 1 = REPEAT loop in progress                                                                                                                |

|         | 0 = REPEAT loop not in progress                                                                                                            |

| bit 3   | N: MCU ALU Negative bit                                                                                                                    |

|         | 1 = Result was negative                                                                                                                    |

|         | 0 = Result was non-negative (zero or positive)                                                                                             |

| bit 2   | OV: MCU ALU Overflow bit                                                                                                                   |

|         | This bit is used for signed arithmetic (2's complement). It indicates an overflow of a magnitude that causes the sign bit to change state. |

|         | <ul> <li>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)</li> <li>0 = No overflow occurred</li> </ul>           |

| bit 1   | <b>Z</b> : MCU ALU Zero bit                                                                                                                |

|         | 1 = An operation that affects the Z bit has set it at some time in the past                                                                |

|         | 0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)                                              |

| bit 0   | C: MCU ALU Carry/Borrow bit                                                                                                                |

|         | 1 = A carry-out from the Most Significant bit of the result occurred                                                                       |

|         | 0 = No carry-out from the Most Significant bit of the result occurred                                                                      |

|         |                                                                                                                                            |

Note 1: This bit can be read or cleared (not set).

- 2: The IPL<2:0> bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU Interrupt Priority Level (IPL). The value in parentheses indicates the IPL if IPL3 = 1. User interrupts are disabled when IPL3 = 1.

- 3: The IPL<2:0> Status bits are read-only when NSTDIS = 1 (INTCON1<15>).

- 4: Clearing this bit will clear SA and SB.

#### TABLE 4-29: PORTA REGISTER MAP

| SFR N | Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-------|------|-------------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA |      | 02C0        | _      | _      |        | —      |        |        | _     |       | _     |       | —     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 001F          |

| PORTA | A    | 02C2        |        | —      | _      | _      | _      | _      | _     | _     | _     | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | XXXX          |

| LATA  |      | 02C4        |        | —      | _      | _      | _      | _      | _     | _     | _     | _     | _     | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | 0000          |

| ODCA  |      | 02C6        | —      | —      | _      | —      | _      | _      | _     | _     | _     | _     | —     | ODCA4  | ODCA3  | —      | -      | _      | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-30: PORTB REGISTER MAP FOR dsPIC33FJ06GS001 AND dsPIC33FJ06GS101A

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB    | 02C8        | _      | _      |        | _      | _      |        | —     |       | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | OOFF          |

| PORTB    | 02CA        | —      | _      | _      | —      | _      |        | _     | _     | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | XXXX          |

| LATB     | 02CC        | _      |        | _      | _      | _      | _      | _     | _     | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | 0000          |

| ODCB     | 02CE        | _      | _      | _      | _      | _      | _      | _     | -     | ODCB7  | ODCB6  | _      | _      | _      | —      | _      | _      | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-31: PORTB REGISTER MAP FOR dsPIC33FJ06GS102A, dsPIC33FJ06GS202A AND dsPIC33FJ09GS302

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB       | 02C8        | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB       | 02CA        | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | XXXX          |

| LATB        | 02CC        | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | 0000          |

| ODCB        | 02CE        | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | _       | _      | ODCB8  | ODCB7  | ODCB6  | _      | _      |        | _      | _      | _      | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| REGISTER 7-2     | 4: IPC5: | INTERRUPT        | PRIORITY | CONTROL RI       | EGISTER 5        |                 |       |

|------------------|----------|------------------|----------|------------------|------------------|-----------------|-------|

| U-0              | U-0      | U-0              | U-0      | U-0              | U-0              | U-0             | U-0   |

| —                | —        | —                | —        | —                | —                | —               | _     |

| bit 15           |          |                  |          |                  |                  |                 | bit 8 |

|                  |          |                  |          |                  |                  |                 |       |

| U-0              | U-0      | U-0              | U-0      | U-0              | R/W-1            | R/W-0           | R/W-0 |

| —                | _        | _                | _        |                  |                  | INT1IP<2:0>     |       |

| bit 7            |          |                  |          |                  |                  |                 | bit 0 |

|                  |          |                  |          |                  |                  |                 |       |

| Legend:          |          |                  |          |                  |                  |                 |       |

| R = Readable bit |          | W = Writable     | bit      | U = Unimpler     | nented bit, read | d as '0'        |       |

| -n = Value at PO | R        | '1' = Bit is set |          | '0' = Bit is cle | ared             | x = Bit is unkn | own   |

####

bit 2-0 INT1IP<2:0>: External Interrupt 1 Priority bits 111 = Interrupt is Priority 7 (highest priority interrupt) ٠ 001 = Interrupt is Priority 1

000 = Interrupt source is disabled

#### REGISTER 7-25: IPC7: INTERRUPT PRIORITY CONTROL REGISTER 7

| U-0    | U-1   | U-0         | U-0   | U-0 | U-0 | U-0 | U-0   |

|--------|-------|-------------|-------|-----|-----|-----|-------|

| —      | —     | —           | _     | _   | —   | —   | —     |

| bit 15 |       |             |       |     |     |     | bit 8 |

|        |       |             |       |     |     |     |       |

| U-0    | R/W-1 | R/W-0       | R/W-0 | U-0 | U-0 | U-0 | U-0   |

| —      |       | INT2IP<2:0> |       | —   | —   | —   | —     |

| bit 7  |       |             |       |     |     |     | bit 0 |

|        |       |             |       |     |     |     |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-7 Unimplemented: Read as '0' bit 6-4 INT2IP<2:0>: External Interrupt 2 Priority bits 111 = Interrupt is Priority 7 (highest priority interrupt) 001 = Interrupt is Priority 1 000 = Interrupt source is disabled bit 3-0 Unimplemented: Read as '0'

| REGISTER 7      | -30: IPC24:    |                       |                 |                     | REGISTER 24      |                 |       |

|-----------------|----------------|-----------------------|-----------------|---------------------|------------------|-----------------|-------|

| U-0             | U-0            | U-0                   | U-0             | U-0                 | U-0              | U-0             | U-0   |

|                 | —              | —                     | _               | —                   | —                | —               | _     |

| bit 15          |                |                       |                 |                     |                  |                 | bit 8 |

|                 |                |                       |                 |                     |                  |                 |       |

| U-0             | R/W-1          | R/W-0                 | R/W-0           | U-0                 | U-0              | U-0             | U-0   |

| _               |                | PWM4IP <sup>(1)</sup> |                 |                     | —                | —               |       |

| bit 7           |                |                       |                 |                     |                  |                 | bit 0 |

|                 |                |                       |                 |                     |                  |                 |       |

| Legend:         |                |                       |                 |                     |                  |                 |       |

| R = Readable    | bit            | W = Writable          | bit             | U = Unimpler        | mented bit, read | l as '0'        |       |

| -n = Value at F | OR             | '1' = Bit is set      |                 | '0' = Bit is cle    | ared             | x = Bit is unkr | iown  |

|                 |                |                       |                 |                     |                  |                 |       |

| bit 15-7        | -              | ted: Read as '        |                 |                     |                  |                 |       |

| bit 6-4         | PWM4IP<2:0     | >: PWM4 Inter         | rupt Priority b | oits <sup>(1)</sup> |                  |                 |       |

|                 | 111 = Interrup | ot is Priority 7 (    | highest priori  | ty)                 |                  |                 |       |

|                 | •              |                       |                 |                     |                  |                 |       |

|                 | •              |                       |                 |                     |                  |                 |       |

|                 | •              |                       |                 |                     |                  |                 |       |

|                 | 001 = Interrup | ot is Priority 1      |                 |                     |                  |                 |       |

|                 |                | ot source is dis      | abled           |                     |                  |                 |       |

|                 |                |                       |                 |                     |                  |                 |       |

#### Note 1: These bits are not implemented in dsPIC33FJ06GS102A/202A devices.

| R/W-0            | R/W-0                                                                                                                      | R/W-1                                                                           | R/W-1          | R/W-0                                   | R/W-0         | R/W-0                 | R/W-0      |

|------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------|-----------------------------------------|---------------|-----------------------|------------|

| ROI              |                                                                                                                            | DOZE<2:0>                                                                       |                | DOZEN <sup>(1)</sup>                    |               | FRCDIV<2:0>           |            |

| bit 15           |                                                                                                                            |                                                                                 |                | · · · · · · · · · · · · · · · · · · ·   |               |                       | bit        |

| R/W-0            | R/W-1                                                                                                                      | U-0                                                                             | R/W-0          | R/W-0                                   | R/W-0         | R/W-0                 | R/W-0      |

| PLLP             | OST<1:0>                                                                                                                   | _                                                                               |                | F                                       | PLLPRE<4:     | 0>                    |            |

| bit 7            |                                                                                                                            |                                                                                 |                |                                         |               |                       | bit        |

| Legend:          |                                                                                                                            |                                                                                 |                |                                         |               |                       |            |

| R = Readab       | le bit                                                                                                                     | W = Writable                                                                    | bit            | U = Unimpleme                           | ented bit, re | ad as '0'             |            |

| -n = Value a     | t POR                                                                                                                      | '1' = Bit is set                                                                |                | '0' = Bit is clear                      | red           | x = Bit is unkno      | own        |

| bit 15           | 1 = Interrupts                                                                                                             | on Interrupt bi<br>will clear the I<br>have no effec                            | DOZEN bit a    |                                         | clock/periph  | eral clock ratio is : | set to 1:1 |

|                  | 111 = FCY/12<br>110 = FCY/64<br>101 = FCY/32<br>100 = FCY/16<br>011 = FCY/8 (<br>010 = FCY/4<br>001 = FCY/2<br>000 = FCY/1 | -                                                                               |                |                                         |               |                       |            |

| bit 11           | <b>DOZEN:</b> Doze<br>1 = DOZE<2                                                                                           |                                                                                 | es the ratio b | between the perip<br>o is forced to 1:1 | heral clocks  | and the processo      | or clocks  |

| bit 10-8         | 111 = FRC di<br>110 = FRC di<br>101 = FRC di<br>100 = FRC di<br>011 = FRC di<br>010 = FRC di<br>001 = FRC di               | vide-by-256<br>vide-by-64<br>vide-by-32<br>vide-by-16<br>vide-by-8<br>vide-by-4 |                | or Postscaler bits                      |               |                       |            |

| bit 7-6          |                                                                                                                            | <b>0&gt;:</b> PLL VCO (<br>d<br>(default)                                       | -              | er Select bits (also                    | o denoted a   | s 'N2', PLL postsc    | aler)      |

| bit 5<br>bit 4-0 | Unimplemen<br>PLLPRE<4:0<br>11111 = Inpu<br>•<br>•                                                                         | ted: Read as 'i<br>>: PLL Phase I<br>t/33                                       |                | ıt Divider bits (als                    | o denoted a   | is 'N1', PLL presca   | aler)      |

|                  | 00001 = Inpu<br>00000 = Inpu                                                                                               |                                                                                 |                |                                         |               |                       |            |

#### Note 1: This bit is cleared when the ROI bit is set and an interrupt occurs.

**2:** This register is reset only on a Power-on Reset (POR).

#### 10.6.2.3 Virtual Pins

Four virtual RPn pins (RP32, RP33, RP34 and RP35) are supported, which are identical in functionality to all other RPn pins, with the exception of pinouts. These four pins are internal to the devices and are not connected to a physical device pin.

These pins provide a simple way for inter-peripheral connection without utilizing a physical pin. For example, the output of the analog comparator can be connected to RP32 and the PWM Fault input can be configured for RP32 as well. This configuration allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

# 10.6.3 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. dsPIC33F devices include three features to prevent alterations to the peripheral map:

- · Control register lock sequence

- Continuous state monitoring

- Configuration bit pin select lock

#### 10.6.3.1 Control Register Lock

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (OSCCON<6>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear IOLOCK, a specific command sequence must be executed:

- 1. Write 0x46 to OSCCON<7:0>.

- 2. Write 0x57 to OSCCON<7:0>.

- 3. Clear (or set) IOLOCK as a single operation.

Unlike the similar sequence with the oscillator's LOCK bit, IOLOCK remains in one state until changed. This allows all of the Peripheral Pin Selects to be configured with a single unlock sequence, followed by an update to all control registers, then locked with a second lock sequence.

#### 10.6.3.2 Continuous State Monitoring

In addition to being protected from direct writes, the contents of the RPINRx and RPORx registers are constantly monitored in hardware by shadow registers. If an unexpected change in any of the registers occurs (such as cell disturbances caused by ESD or other external events), a Configuration Mismatch Reset will be triggered.

#### 10.6.3.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPINRx and RPORx registers. The IOL1WAY (FOSC<5>) Configuration bit blocks the IOLOCK bit from being cleared, after it has been set once. If IOLOCK remains set, the register unlock procedure will not execute and the Peripheral Pin Select Control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session. Programming IOL1WAY allows user applications unlimited access (with the proper use of the unlock sequence) to the Peripheral Pin Select registers.

| U-0                | U-0                                                                                                                       | R/W-1                                                                                                                                                                      | R/W-1                              | R/W-1                       | R/W-1            | R/W-1           | R/W-1 |

|--------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------------|------------------|-----------------|-------|

| _                  | —                                                                                                                         |                                                                                                                                                                            |                                    | FLT7                        | R<5:0>           |                 |       |

| bit 15             |                                                                                                                           |                                                                                                                                                                            |                                    |                             |                  |                 | bit 8 |

|                    |                                                                                                                           |                                                                                                                                                                            |                                    |                             |                  |                 |       |

| U-0                | U-0                                                                                                                       | R/W-1                                                                                                                                                                      | R/W-1                              | R/W-1                       | R/W-1            | R/W-1           | R/W-1 |

| _                  | —                                                                                                                         |                                                                                                                                                                            |                                    | FLT6                        | R<5:0>           |                 |       |

| bit 7              |                                                                                                                           |                                                                                                                                                                            |                                    |                             |                  |                 | bit ( |

| Legend:            |                                                                                                                           |                                                                                                                                                                            |                                    |                             |                  |                 |       |

| R = Readab         | le bit                                                                                                                    | W = Writable I                                                                                                                                                             | oit                                | U = Unimplen                | nented bit, read | d as '0'        |       |

| -n = Value a       | t POR                                                                                                                     | '1' = Bit is set                                                                                                                                                           |                                    | '0' = Bit is clea           |                  | x = Bit is unkr | nown  |

|                    |                                                                                                                           |                                                                                                                                                                            |                                    |                             |                  |                 |       |

| bit 15-14          | Unimpleme                                                                                                                 | nted: Read as '(                                                                                                                                                           | )'                                 |                             |                  |                 |       |

| bit 13-8           | •                                                                                                                         | : Assign PWM F                                                                                                                                                             |                                    | =I T7) to the Co            | orresponding R   | Pn Pin hits     |       |

|                    |                                                                                                                           | put tied to Vss                                                                                                                                                            |                                    |                             | incoponding is   |                 |       |

|                    |                                                                                                                           | put tied to RP35                                                                                                                                                           |                                    |                             |                  |                 |       |

|                    |                                                                                                                           |                                                                                                                                                                            |                                    |                             |                  |                 |       |

|                    | 100010 <b>= ln</b>                                                                                                        | put tied to RP34                                                                                                                                                           |                                    |                             |                  |                 |       |

|                    |                                                                                                                           | put tied to RP34<br>put tied to RP33                                                                                                                                       |                                    |                             |                  |                 |       |

|                    | 100001 <b>= In</b>                                                                                                        |                                                                                                                                                                            | 1                                  |                             |                  |                 |       |

|                    | 100001 <b>= In</b>                                                                                                        | put tied to RP33                                                                                                                                                           | 1                                  |                             |                  |                 |       |

|                    | 100001 <b>= In</b>                                                                                                        | put tied to RP33                                                                                                                                                           | 1                                  |                             |                  |                 |       |

|                    | 100001 <b>= In</b>                                                                                                        | put tied to RP33                                                                                                                                                           | 1                                  |                             |                  |                 |       |

|                    | 100001 = In<br>100000 = In<br>•                                                                                           | put tied to RP33<br>put tied to RP32                                                                                                                                       | 1                                  |                             |                  |                 |       |

| bit 7-6            | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>00000 = Inp                                                                  | put tied to RP33<br>put tied to RP32<br>ut tied to RP0                                                                                                                     |                                    |                             |                  |                 |       |

| bit 7-6            | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | put tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0                                                                                                 | ;<br>;<br>;                        | ELT6) to the Co             | prresponding P   | PDn Din hits    |       |

| bit 7-6<br>bit 5-0 | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | put tied to RP33<br>put tied to RP32<br>ut tied to RP0<br><b>nted:</b> Read as '0<br>:: Assign PWM F                                                                       | ;<br>;<br>;                        | FLT6) to the Co             | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | put tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss                                                            | <sub>)</sub> ,<br>Fault Input 6 (I | FLT6) to the Co             | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | put tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35                                        | ) <sup>)</sup><br>Fault Input 6 (I | FLT6) to the Co             | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34                     | ) <sup>)</sup><br>Fault Input 6 (I | <sup>-</sup> LT6) to the Co | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33 | o'<br>Fault Input 6 (I             | <sup>-</sup> LT6) to the Co | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34                     | o'<br>Fault Input 6 (I             | <sup>-</sup> LT6) to the Co | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33 | o'<br>Fault Input 6 (I             | <sup>-</sup> LT6) to the Co | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33 | o'<br>Fault Input 6 (I             | FLT6) to the Co             | prresponding R   | Pn Pin bits     |       |

|                    | 100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to RP33<br>put tied to RP32<br>ut tied to RP0<br>nted: Read as '0<br>: Assign PWM F<br>put tied to Vss<br>put tied to RP35<br>put tied to RP34<br>put tied to RP33 | o'<br>Fault Input 6 (I             | <sup>=</sup> LT6) to the Co | prresponding R   | Pn Pin bits     |       |

## REGISTER 10-13: RPINR32: PERIPHERAL PIN SELECT INPUT REGISTER 32

#### REGISTER 15-4: SEVTCMP: PWM SPECIAL EVENT COMPARE REGISTER

| R/W-0  | R/W-0 | R/W-0        | R/W-0  | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|--------------|--------|-----------|-------|-------|-------|

|        |       |              | SEVTCM | IP <15:8> |       |       |       |

| bit 15 |       |              |        |           |       |       | bit 8 |

| R/W-0  | R/W-0 | R/W-0        | R/W-0  | R/W-0     | U-0   | U-0   | U-0   |

|        | SE    | EVTCMP <7:3> | •      |           | _     | —     | _     |

| bit 7  |       |              |        |           |       |       | bit 0 |

| Legena:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-3 SEVTCMP<15:3>: Special Event Compare Count Value bits bit 2-0 Unimplemented: Read as '0'

#### REGISTER 15-5: MDC: PWM MASTER DUTY CYCLE REGISTER

| R/W-0                              | R/W-0 | R/W-0                                  | R/W-0                              | R/W-0                  | R/W-0 | R/W-0 | R/W-0 |

|------------------------------------|-------|----------------------------------------|------------------------------------|------------------------|-------|-------|-------|

|                                    |       |                                        | MDC<                               | 15:8> <sup>(1,2)</sup> |       |       |       |

| bit 15                             |       |                                        |                                    |                        |       |       | bit 8 |

| R/W-0                              | R/W-0 | R/W-0                                  | R/W-0                              | R/W-0                  | R/W-0 | R/W-0 | R/W-0 |

|                                    |       |                                        | MDC                                | <7:0> <sup>(1,2)</sup> |       |       |       |

| bit 7                              |       |                                        |                                    |                        |       |       | bit 0 |

|                                    |       |                                        |                                    |                        |       |       |       |

| Legend:                            |       |                                        |                                    |                        |       |       |       |

| R = Readable bit W = Writable bit  |       | bit                                    | U = Unimplemented bit, read as '0' |                        |       |       |       |

| -n = Value at POR '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknow |                                    | nown                   |       |       |       |

bit 15-0 MDC<15:0>: Master PWM Duty Cycle Value bits<sup>(1,2)</sup>

**Note 1:** The smallest pulse width that can be generated on the PWM output corresponds to a value of 0x0009, while the maximum pulse width generated corresponds to a value of Period – 0x0008.

2: As the duty cycle gets closer to 0% or 100% of the PWM period (0 ns-40 ns, depending on the mode of operation), the PWM duty cycle resolution will degrade from 1 LSb to 3 LSbs.

| REGISTER 15-7: | PDCx: PWMx GENERATOR DUTY CYCLE REGISTER <sup>(1)</sup> |

|----------------|---------------------------------------------------------|

|                |                                                         |

| R/W-0                              | R/W-0 | R/W-0                                   | R/W-0                              | R/W-0                 | R/W-0 | R/W-0 | R/W-0 |

|------------------------------------|-------|-----------------------------------------|------------------------------------|-----------------------|-------|-------|-------|

|                                    |       |                                         | PDCx                               | <15:8> <sup>(2)</sup> |       |       |       |

| bit 15                             |       |                                         |                                    |                       |       |       | bit 8 |

|                                    |       |                                         |                                    |                       |       |       |       |

| R/W-0                              | R/W-0 | R/W-0                                   | R/W-0                              | R/W-0                 | R/W-0 | R/W-0 | R/W-0 |

|                                    |       |                                         | PDC                                | <7:0> <sup>(2)</sup>  |       |       |       |

| bit 7                              |       |                                         |                                    |                       |       |       | bit 0 |

|                                    |       |                                         |                                    |                       |       |       |       |

| Legend:                            |       |                                         |                                    |                       |       |       |       |

| R = Readable bit W = Writable bit  |       | bit                                     | U = Unimplemented bit, read as '0' |                       |       |       |       |

| -n = Value at POR '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |                                    | nown                  |       |       |       |

bit 15-0 PDCx<15:0>: PWMx Generator # Duty Cycle Value bits<sup>(2)</sup>

- **Note 1:** In Independent PWM mode, the PDCx register controls the PWMxH duty cycle only. In Complementary, Redundant and Push-Pull PWM modes, the PDCx register controls the duty cycle of both the PWMxH and PWMxL. The smallest pulse width that can be generated on the PWM output corresponds to a value of 0x0009, while the maximum pulse width generated corresponds to a value of Period-0x0008.

- 2: As the duty cycle gets closer to 0% or 100% of the PWM period (0 ns-40 ns, depending on the mode of operation), the PWM duty cycle resolution will degrade from 1 LSB to 3 LSBs.

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                              | R/W-0                 | R/W-0           | R/W-0 | R/W-0 |

|------------------------------------|-------|-------|------------------------------------|-----------------------|-----------------|-------|-------|

|                                    |       |       | SDCx                               | <15:8> <sup>(2)</sup> |                 |       |       |

| bit 15                             |       |       |                                    |                       |                 |       | bit 8 |

|                                    |       |       |                                    |                       |                 |       |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                              | R/W-0                 | R/W-0           | R/W-0 | R/W-0 |

|                                    |       |       | SDC>                               | <7:0> <sup>(2)</sup>  |                 |       |       |

| bit 7                              |       |       |                                    |                       |                 |       | bit 0 |

|                                    |       |       |                                    |                       |                 |       |       |

| Legend:                            |       |       |                                    |                       |                 |       |       |

| R = Readable bit W = Writable bit  |       | oit   | U = Unimplemented bit, read as '0' |                       |                 |       |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cle                   | ared                  | x = Bit is unkr | nown  |       |

#### REGISTER 15-8: SDCx: PWMx SECONDARY DUTY CYCLE REGISTER<sup>(1)</sup>

bit 15-0 SDCx<15:0>: Secondary Duty Cycle for PWMxL Output Pin bits<sup>(2)</sup>

- **Note 1:** The SDCx register is used in Independent PWM mode only. When used in Independent PWM mode, the SDCx register controls the PWMxL duty cycle. The smallest pulse width that can be generated on the PWM output corresponds to a value of 0x0009, while the maximum pulse width generated corresponds to a value of Period-0x0008.

- 2: As the duty cycle gets closer to 0% or 100% of the PWM period (0 ns-40 ns, depending on the mode of operation), the PWM duty cycle resolution will degrade from 1 LSB to 3 LSBs.

| R/W-0         | R/W-0                                                                      | R/W-0                                                                                     | U-0            | U-0                                | U-0             | U-0                | U-0   |  |  |  |

|---------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------|------------------------------------|-----------------|--------------------|-------|--|--|--|

| FRMEN         | SPIFSD                                                                     | FRMPOL                                                                                    | —              | —                                  | —               | —                  | —     |  |  |  |

| bit 15        |                                                                            |                                                                                           |                |                                    |                 |                    | bit 8 |  |  |  |

|               |                                                                            |                                                                                           |                |                                    |                 |                    |       |  |  |  |

| U-0           | U-0                                                                        | U-0                                                                                       | U-0            | U-0                                | U-0             | R/W-0              | U-0   |  |  |  |

| —             | —                                                                          |                                                                                           | —              | —                                  |                 | FRMDLY             | _     |  |  |  |

| bit 7         |                                                                            |                                                                                           |                |                                    |                 |                    | bit C |  |  |  |

|               |                                                                            |                                                                                           |                |                                    |                 |                    |       |  |  |  |

| _egend:       |                                                                            |                                                                                           |                |                                    |                 |                    |       |  |  |  |

| R = Readable  | e bit                                                                      | W = Writable                                                                              | bit            | U = Unimplemented bit, read as '0' |                 |                    |       |  |  |  |

| -n = Value at | POR                                                                        | '1' = Bit is set                                                                          |                | '0' = Bit is cleared               |                 | x = Bit is unknown |       |  |  |  |

|               |                                                                            |                                                                                           |                |                                    |                 |                    |       |  |  |  |

| bit 15        | FRMEN: Fran                                                                | med SPIx Supp                                                                             | ort bit        |                                    |                 |                    |       |  |  |  |

|               |                                                                            | Framed SPIx support enabled ( $\overline{SSx}$ pin used as Frame Sync pulse input/output) |                |                                    |                 |                    |       |  |  |  |

|               |                                                                            | Plx support dis                                                                           |                |                                    |                 |                    |       |  |  |  |

| bit 14        |                                                                            | me Sync Pulse                                                                             |                | ntrol bit                          |                 |                    |       |  |  |  |

|               | 1 = Frame Sync pulse input (slave)<br>0 = Frame Sync pulse output (master) |                                                                                           |                |                                    |                 |                    |       |  |  |  |

| bit 13        | ,                                                                          | • •                                                                                       | ( )            |                                    |                 |                    |       |  |  |  |

| DIL 15        |                                                                            | FRMPOL: Frame Sync Pulse Polarity bit <pre>L = Frame Sync pulse is active-high</pre>      |                |                                    |                 |                    |       |  |  |  |

|               | ,                                                                          | inc pulse is act                                                                          | •              |                                    |                 |                    |       |  |  |  |

| bit 12-2      | -                                                                          | ted: Read as '                                                                            |                |                                    |                 |                    |       |  |  |  |

| bit 1         | •                                                                          | ame Sync Pulse                                                                            |                | t bit                              |                 |                    |       |  |  |  |

|               |                                                                            | nc pulse coinc                                                                            | •              |                                    |                 |                    |       |  |  |  |

|               |                                                                            | nc pulse prece                                                                            |                |                                    |                 |                    |       |  |  |  |

| bit 0         | Unimplemen                                                                 | ted: This bit m                                                                           | ust not be set | t to '1' by the us                 | ser application |                    |       |  |  |  |

|               |                                                                            |                                                                                           |                |                                    |                 |                    |       |  |  |  |

## REGISTER 16-3: SPIxCON2: SPIx CONTROL REGISTER 2

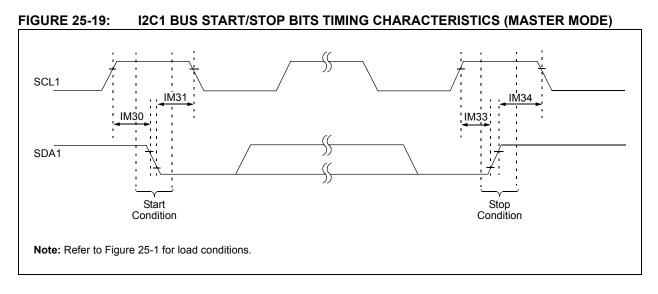

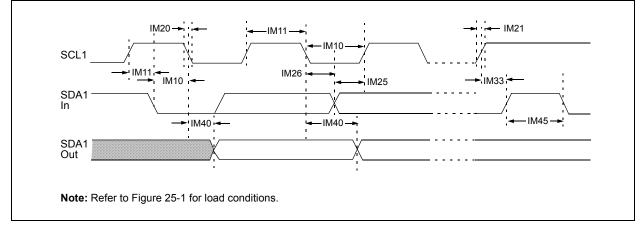

# 17.2 I<sup>2</sup>C Registers

I2C1CON and I2C1STAT are control and status registers, respectively. The I2C1CON register is readable and writable. The lower six bits of I2C1STAT are read-only. The remaining bits of the I2CSTAT are read/write:

- I2C1RSR is the shift register used for shifting data internal to the module and the user application has no access to it

- I2C1RCV is the receive buffer and the register to which data bytes are written, or from which data bytes are read

- I2C1TRN is the transmit register to which bytes are written during a transmit operation

- The I2C1ADD register holds the slave address

- A status bit, ADD10, indicates 10-Bit Address mode

- The I2C1BRG acts as the Baud Rate Generator (BRG) reload value

In receive operations, I2C1RSR and I2C1RCV together form a double-buffered receiver. When I2C1RSR receives a complete byte, it is transferred to I2C1RCV, and an interrupt pulse is generated.

### REGISTER 17-1: I2C1CON: I2C1 CONTROL REGISTER

| R/W-0  | U-0 | R/W-0   | R/W-1, HC | R/W-0  | R/W-0 | R/W-0  | R/W-0 |

|--------|-----|---------|-----------|--------|-------|--------|-------|

| I2CEN  | —   | I2CSIDL | SCLREL    | IPMIEN | A10M  | DISSLW | SMEN  |

| bit 15 |     |         |           |        |       |        | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0, HC |

|-------|-------|-------|-----------|-----------|-----------|-----------|-----------|

| GCEN  | STREN | ACKDT | ACKEN     | RCEN      | PEN       | RSEN      | SEN       |

| bit 7 |       |       |           |           |           |           | bit 0     |

| Legend:           | HC = Hardware Clearable | e bit                       |                    |

|-------------------|-------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared        | x = Bit is unknown |

| I2CEN: I2C1 Enable bit                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 = Enables the I2C1 module and configures the SDA1 and SCL1 pins as serial port pins<br>0 = Disables the I2C1 module; all I <sup>2</sup> C pins are controlled by port functions                                           |

| Unimplemented: Read as '0'                                                                                                                                                                                                  |

| I2CSIDL: Stop in Idle Mode bit                                                                                                                                                                                              |

| <ul> <li>1 = Discontinues module operation when device enters an Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul>                                                                                  |

| SCLREL: SCL1 Release Control bit (when operating as I <sup>2</sup> C slave)                                                                                                                                                 |

| <ul><li>1 = Releases SCL1 clock</li><li>0 = Holds SCL1 clock low (clock stretch)</li></ul>                                                                                                                                  |

| <u>If STREN = 1:</u><br>Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware is clear<br>at beginning of slave transmission. Hardware is clear at end of slave reception. |

| <u>If STREN = 0:</u><br>Bit is R/S (i.e., software can only write '1' to release clock). Hardware is clear at beginning of slave transmission.                                                                              |

| IPMIEN: Intelligent Peripheral Management Interface (IPMI) Enable bit                                                                                                                                                       |

| <ul><li>1 = IPMI mode is enabled; all addresses Acknowledged</li><li>0 = IPMI mode is disabled</li></ul>                                                                                                                    |

| A10M: 10-Bit Slave Address bit                                                                                                                                                                                              |

| <ul> <li>1 = I2C1ADD is a 10-bit slave address</li> <li>0 = I2C1ADD is a 7-bit slave address</li> </ul>                                                                                                                     |

| DISSLW: Disable Slew Rate Control bit                                                                                                                                                                                       |

| 1 = Slew rate control is disabled                                                                                                                                                                                           |

| 0 = Slew rate control is enabled                                                                                                                                                                                            |

|                                                                                                                                                                                                                             |

## REGISTER 17-1: I2C1CON: I2C1 CONTROL REGISTER (CONTINUED)

| bit 8 | SMEN: SMBus Input Levels bit                                                                                                                                                                                                 |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Enables I/O pin thresholds compliant with SMBus specification</li> <li>0 = Disables SMBus input thresholds</li> </ul>                                                                                           |

| bit 7 | GCEN: General Call Enable bit (when operating as I <sup>2</sup> C slave)                                                                                                                                                     |

|       | <ul> <li>1 = Enables interrupt when a general call address is received in the I2C1RSR<br/>(module is enabled for reception)</li> <li>0 = General call address is disabled</li> </ul>                                         |

| bit 6 | STREN: SCL1 Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)                                                                                                                                              |

|       | Used in conjunction with SCLREL bit.<br>1 = Enables software or receives clock stretching<br>0 = Disables software or receives clock stretching                                                                              |

| bit 5 | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                    |

|       | Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends NACK during Acknowledge<br>0 = Sends ACK during Acknowledge                                                                      |

| bit 4 | <b>ACKEN:</b> Acknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                  |

|       | <ul> <li>1 = Initiates Acknowledge sequence on SDA1 and SCL1 pins and transmits ACKDT data bit.<br/>Hardware is clear at end of master Acknowledge sequence.</li> <li>0 = Acknowledge sequence is not in progress</li> </ul> |

| bit 3 | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                  |

|       | <ul> <li>1 = Enables Receive mode for I<sup>2</sup>C. Hardware is clear at end of eighth bit of master receive data byte.</li> <li>0 = Receive sequence is not in progress</li> </ul>                                        |

| bit 2 | <b>PEN:</b> Stop Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                            |

|       | <ul> <li>1 = Initiates Stop condition on SDA1 and SCL1 pins. Hardware is clear at end of master Stop sequence.</li> <li>0 = Stop condition is not in progress</li> </ul>                                                     |

| bit 1 | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                 |

|       | <ul> <li>1 = Initiates Repeated Start condition on SDA1 and SCL1 pins. Hardware is clear at end of master<br/>Repeated Start sequence.</li> </ul>                                                                            |

|       | 0 = Repeated Start condition is not in progress                                                                                                                                                                              |

| bit 0 | <b>SEN:</b> Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                           |

|       | 1 = Initiates Start condition on SDA1 and SCL1 pins. Hardware is clear at end of master Start sequence.                                                                                                                      |

|       | 0 = Start condition is not in progress                                                                                                                                                                                       |

| DC CHARA  | ACTERISTICS            |      | Standard | Operating Co<br>temperature | $\begin{array}{ll} \mbox{Conditions: 3.0V to 3.6V (unless otherwise stated)} \\ \mbox{re} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                                |  |

|-----------|------------------------|------|----------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--|

| Param.    | Typical <sup>(1)</sup> | Max. | Units    |                             | Conditions                                                                                                                                                                                                                               |                                |  |

| Operating | Current (IDD)          | (2)  |          |                             |                                                                                                                                                                                                                                          |                                |  |

| DC20d     | 15                     | 23   | mA       | -40°C                       |                                                                                                                                                                                                                                          |                                |  |

| DC20a     | 15                     | 23   | mA       | +25°C                       | 3.3V                                                                                                                                                                                                                                     | 10 MIPS                        |  |

| DC20b     | 15                     | 23   | mA       | +85°C                       | 3.3V                                                                                                                                                                                                                                     | TO MIPS                        |  |

| DC20c     | 15                     | 23   | mA       | +125°C                      |                                                                                                                                                                                                                                          |                                |  |

| DC21d     | 23                     | 34   | mA       | -40°C                       |                                                                                                                                                                                                                                          |                                |  |

| DC21a     | 23                     | 34   | mA       | +25°C                       | 0.01/                                                                                                                                                                                                                                    | 16 MIPS <sup>(3)</sup>         |  |

| DC21b     | 23                     | 34   | mA       | +85°C                       | - 3.3V                                                                                                                                                                                                                                   | 16 MIPS(*)                     |  |

| DC21c     | 23                     | 34   | mA       | +125°C                      |                                                                                                                                                                                                                                          |                                |  |

| DC22d     | 25                     | 38   | mA       | -40°C                       |                                                                                                                                                                                                                                          |                                |  |

| DC22a     | 25                     | 38   | mA       | +25°C                       | 2.21/                                                                                                                                                                                                                                    | 20 MIPS <sup>(3)</sup>         |  |

| DC22b     | 25                     | 38   | mA       | +85°C                       | - 3.3V                                                                                                                                                                                                                                   | 20 MIPS(*)                     |  |