#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 6КВ (2К х 24)                                                                     |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 1K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 6x10b; D/A 2x10b                                                              |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                    |

| Supplier Device Package    | 28-SOIC                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs202at-i-so |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

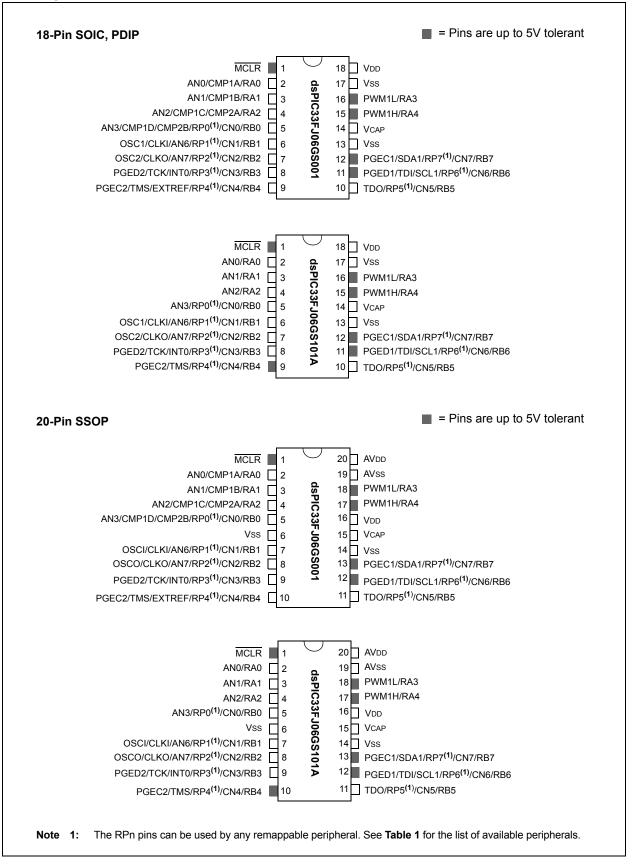

#### **Pin Diagrams**

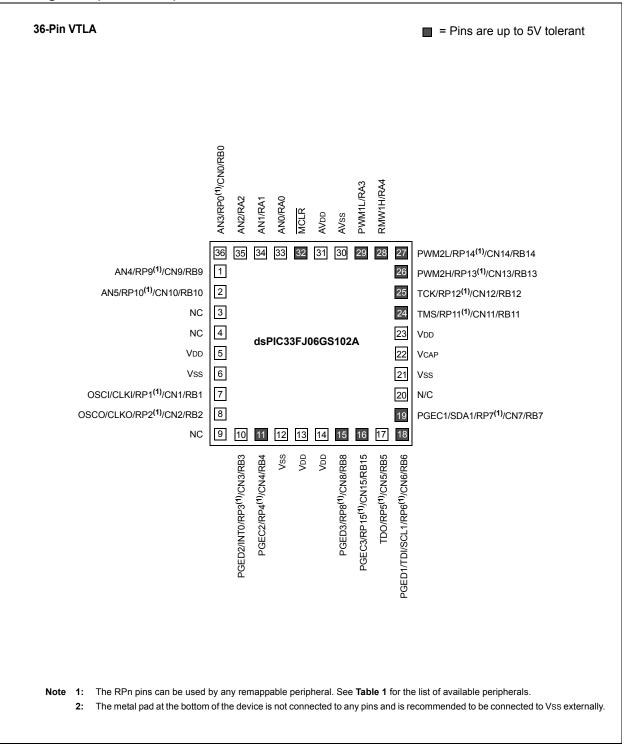

### Pin Diagrams (Continued)

# 3.4 CPU Control Registers

| R-0                  | R-0                                               | R/C-0                                  | R/C-0             | R-0                    | R/C-0                | R -0             | R/W-0         |

|----------------------|---------------------------------------------------|----------------------------------------|-------------------|------------------------|----------------------|------------------|---------------|

| OA                   | OB                                                | SA <sup>(1)</sup>                      | SB <sup>(1)</sup> | OAB                    | SAB <sup>(1,4)</sup> | DA               | DC            |

| bit 15               |                                                   |                                        |                   |                        | •                    |                  | bit 8         |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup>                              | R/W-0 <sup>(3)</sup>                   | R-0               | R/W-0                  | R/W-0                | R/W-0            | R/W-0         |

|                      | IPL<2:0> <sup>(2)</sup>                           |                                        | RA                | N                      | OV                   | Z                | C             |

| bit 7                |                                                   |                                        |                   |                        |                      |                  | bit (         |

| Legend:              |                                                   |                                        |                   |                        |                      |                  |               |

| C = Clearab          | le bit                                            | R = Readable                           | e bit             | U = Unimple            | mented bit, read     | as '0'           |               |

| S = Settable         | bit                                               | W = Writable                           | bit               | -n = Value at          | POR                  |                  |               |

| '1' = Bit is se      | et                                                | '0' = Bit is clea                      | ared              | x = Bit is unk         | nown                 |                  |               |

| bit 15               | OA: Accumul                                       | lator A Overflow                       | v Status bit      |                        |                      |                  |               |

|                      |                                                   | ator A overflowe                       |                   |                        |                      |                  |               |

| 1.1.4.4              |                                                   | ator A has not c                       |                   |                        |                      |                  |               |

| bit 14               |                                                   | lator B Overflow<br>ator B overflowe   |                   |                        |                      |                  |               |

|                      |                                                   | ator B has not c                       |                   |                        |                      |                  |               |

| bit 13               | SA: Accumul                                       | ator A Saturatio                       | on 'Sticky' Sta   | tus bit <sup>(1)</sup> |                      |                  |               |

|                      | 1 = Accumula                                      | ator A is saturat<br>ator A is not sat | ed or has bee     |                        | some time            |                  |               |

| bit 12               | SB: Accumul                                       | ator B Saturatio                       | on 'Sticky' Sta   | tus bit <sup>(1)</sup> |                      |                  |               |

|                      |                                                   | ator B is saturat<br>ator B is not sat |                   | en saturated at        | some time            |                  |               |

| bit 11               | <b>0AB:</b> 0A    0                               | DB Combined A                          | ccumulator O      | verflow Status         | bit                  |                  |               |

|                      | 1 = Accumula                                      | ators A or B hav                       | ve overflowed     |                        |                      |                  |               |

| bit 10               | <b>SAB:</b> SA    S                               | B Combined A                           | ccumulator 'St    | icky' Status bit       | (1,4)                |                  |               |

|                      | 1 = Accumula                                      |                                        | saturated or      | have been sat          | urated at some       | time in the past | t             |

| bit 9                | DA: DO Loop                                       | Active bit                             |                   |                        |                      |                  |               |

|                      | 1 = DO <b>loop ir</b>                             |                                        |                   |                        |                      |                  |               |

|                      | -                                                 | ot in progress                         |                   |                        |                      |                  |               |

| bit 8                |                                                   | U Half Carry/B                         |                   |                        |                      |                  |               |

|                      | of the res                                        | sult occurred                          |                   | -                      | data) or 8th low-o   |                  |               |

|                      | •                                                 | -out from the 4 the result occur       |                   | bit (for byte-siz      | ed data) or 8th      | low-order bit (1 | for word-size |

| Note 1: ⊤            | his bit can be rea                                | ad or cleared (n                       | ot set).          |                        |                      |                  |               |

| L                    | he IPL<2:0> bits<br>evel (IPL). The v<br>PL3 = 1. |                                        |                   |                        |                      |                  |               |

|                      |                                                   |                                        |                   |                        |                      |                  |               |

#### REGISTER 3-1: SR: CPU STATUS REGISTER

**3:** The IPL<2:0> Status bits are read-only when NSTDIS = 1 (INTCON1<15>).

**4:** Clearing this bit will clear SA and SB.

# TABLE 4-12: HIGH-SPEED PWM REGISTER MAP

| File Name | Addr<br>Offset | Bit 15   | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9    | Bit 8   | Bit 7  | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2 | Bit 1      | Bit 0 | All<br>Resets |

|-----------|----------------|----------|--------|--------|--------|--------|--------|----------|---------|--------|-------|-------|---------|-------|-------|------------|-------|---------------|

| PTCON     | 0400           | PTEN     | _      | PTSIDL | SESTAT | SEIEN  | EIPU   | SYNCPOL  | SYNCOEN | SYNCEN | _     | SYNCS | RC<1:0> |       | SEVT  | PS<3:0>    |       | 0000          |

| PTCON2    | 0402           | _        | _      | _      | —      | _      | _      | _        | _       | _      | —     | _     | _       | —     | PC    | CLKDIV<2:0 | )>    | 0000          |

| PTPER     | 0404           |          |        |        |        |        |        | PTPE     | R<15:0> |        |       |       |         |       |       |            |       | FFF8          |

| SEVTCMP   | 0406           |          |        |        |        |        | SEVTCM | 1P<15:3> |         |        |       |       |         |       | _     |            | _     | 0000          |

| MDC       | 040A           |          |        |        |        |        |        | MDO      | C<15:0> |        |       |       |         |       |       |            |       | 0000          |

| CHOP      | 041A           | CHPCLKEN |        | _      | _      | _      | _      |          |         | CHOPCL | <6:0> |       |         |       | —     |            | _     | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-13: HIGH-SPEED PWM GENERATOR 1 REGISTER MAP

| File Name | Addr<br>Offset | Bit 15  | Bit 14 | Bit 13  | Bit 12   | Bit 11   | Bit 10  | Bit 9  | Bit 8     | Bit 7    | Bit 6  | Bit 5   | Bit 4  | Bit 3   | Bit 2     | Bit 1   | Bit 0   | All<br>Resets |

|-----------|----------------|---------|--------|---------|----------|----------|---------|--------|-----------|----------|--------|---------|--------|---------|-----------|---------|---------|---------------|

| PWMCON1   | 0420           | FLTSTAT | CLSTAT | TRGSTAT | FLTIEN   | CLIEN    | TRGIEN  | ITB    | MDCS      | DTC<     | :1:0>  | _       | —      | _       | CAM       | XPRES   | IUE     | 0000          |

| IOCON1    | 0422           | PENH    | PENL   | POLH    | POLL     | PMOD     | <1:0>   | OVRENH | OVRENL    | OVRDA    | T<1:0> | FLTDA   | T<1:0> | CLD     | \T<1:0>   | SWAP    | OSYNC   | 0000          |

| FCLCON1   | 0424           | IFLTMOD |        |         | CLSRC<4: | 0>       |         | CLPOL  | CLMOD     |          | F      | LTSRC<4 | :0>    |         | FLTPOL    | FLTMO   | D<1:0>  | 0000          |

| PDC1      | 0426           |         |        |         |          |          |         | PD     | C1<15:0>  |          |        |         |        |         |           |         |         | 0000          |

| PHASE1    | 0428           |         |        |         |          |          |         | PHA    | SE1<15:0> |          |        |         |        |         |           |         |         | 0000          |

| DTR1      | 042A           | _       | _      |         |          |          |         |        | D         | TR1<13:0 | )>     |         |        |         |           |         |         | 0000          |

| ALTDTR1   | 042C           | _       | _      |         |          |          |         |        | ALT       | DTR1<1   | 3:0>   |         |        |         |           |         |         | 0000          |

| SDC1      | 042E           |         |        |         |          |          |         | SD     | C1<15:0>  |          |        |         |        |         |           |         |         | 0000          |

| SPHASE1   | 0430           |         |        |         |          |          |         | SPH    | ASE1<15:0 | >        |        |         |        |         |           |         |         | 0000          |

| TRIG1     | 0432           |         |        |         |          |          | TRGCMP  | <15:3> |           |          |        |         |        |         | _         | _       | _       | 0000          |

| TRGCON1   | 0434           |         | TRGDI  | /<3:0>  |          | _        |         | —      | —         | DTM      |        |         |        | TRO     | GSTRT<5:0 | )>      |         | 0000          |

| STRIG1    | 0436           |         |        |         |          |          | STRGCMP | <15:3> |           |          |        |         |        |         | _         | _       | _       | 0000          |

| PWMCAP1   | 0438           |         |        |         |          |          | PWMCAP1 | <15:3> |           |          |        |         |        |         | _         | _       | _       | 0000          |

| LEBCON1   | 043A           | PHR     | PHF    | PLR     | PLF      | FLTLEBEN | CLLEBEN |        |           | LEE      | B<6:0> |         |        |         | —         | _       | —       | 0000          |

| AUXCON1   | 043E           | HRPDIS  | HRDDIS | _       | _        | _        | _       | _      | _         |          | _      |         | CHOPSE | EL<3:0> |           | CHOPHEN | CHOPLEN | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-19: CONSTANT CURRENT SOURCE REGISTER MAP

| File Na | me AD  | R  | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|---------|--------|----|--------|--------|--------|--------|--------|--------|-----------|-------|-------|-------|-------|-------|--------|--------|-------|-------|---------------|

| ISRCCO  | ON 050 | 00 | ISRCEN | _      |        | —      | _      | 0      | UTSEL<2:( | )>    | —     |       |       |       | ISRCCA | L<5:0> |       |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-20: HIGH-SPEED 10-BIT ADC REGISTER MAP FOR dsPIC33FJ06GS001 AND dsPIC33FJ06GS101A

| SFR Name | SFR<br>Addr | Bit 15             | Bit 14             | Bit 13 | Bit 12  | Bit 11 | Bit 10    | Bit 9 | Bit 8  | Bit 7        | Bit 6 | Bit 5   | Bit 4     | Bit 3 | Bit 2    | Bit 1   | Bit 0 | All<br>Resets |

|----------|-------------|--------------------|--------------------|--------|---------|--------|-----------|-------|--------|--------------|-------|---------|-----------|-------|----------|---------|-------|---------------|

| ADCON    | 0300        | ADON               |                    | ADSIDL | SLOWCLK |        | GSWTRG    |       | FORM   | EIE          | ORDER | SEQSAMP | ASYNCSAMP | _     | A        | DCS<2:0 | >     | 0003          |

| ADPCFG   | 0302        | -                  | _                  | _      | _       | _      | _         | _     | _      | PCFG7        | PCFG6 | _       | —         | PCFG3 | PCFG2    | PCFG1   | PCFG0 | 0000          |

| ADSTAT   | 0306        | _                  | _                  | _      | _       | _      | _         | _     | _      | _            | P6RDY | _       | —         | P3RDY | _        | P1RDY   | PORDY | 0000          |

| ADBASE   | 0308        |                    |                    |        |         |        |           | А     | DBASE< | 15:1>        |       |         |           |       |          |         | _     | 0000          |

| ADCPC0   | 030A        | IRQEN1             | PEND1              | SWTRG1 |         | TRO    | SRC1<4:0> |       |        | IRQEN0       | PEND0 | SWTRG0  |           | TRGS  | RC0<4:0> |         |       | 0000          |

| ADCPC1   | 030C        | IRQEN3             | PEND3              | SWTRG3 |         | TRO    | SRC3<4:0> |       |        | _            | _     | _       | —         | _     | _        | _       | _     | 0000          |

| ADCPC3   | 0310        | -                  | _                  | _      | _       | _      | _         | _     | _      | IRQEN6       | PEND6 | SWTRG6  |           | TRGS  | RC6<4:0> |         |       | 0000          |

| ADCBUF0  | 0320        |                    |                    |        |         |        |           |       | ADC Da | ata Buffer 0 |       |         |           |       |          |         |       | XXXX          |

| ADCBUF1  | 0322        |                    |                    |        |         |        |           |       | ADC Da | ata Buffer 1 |       |         |           |       |          |         |       | XXXX          |

| ADCBUF2  | 0324        |                    |                    |        |         |        |           |       | ADC Da | ata Buffer 2 |       |         |           |       |          |         |       | XXXX          |

| ADCBUF3  | 0326        |                    |                    |        |         |        |           |       | ADC Da | ata Buffer 3 |       |         |           |       |          |         |       | XXXX          |

| ADCBUF6  | 032C        |                    | ADC Data Buffer 6  |        |         |        |           |       |        |              |       | XXXX    |           |       |          |         |       |               |

| ADCBUF7  | 032E        |                    | ADC Data Buffer 7  |        |         |        |           |       |        |              | XXXX  |         |           |       |          |         |       |               |

| ADCBUF12 | 0338        |                    | ADC Data Buffer 12 |        |         |        |           |       |        |              | XXXX  |         |           |       |          |         |       |               |

| ADCBUF13 | 033A        | ADC Data Buffer 13 |                    |        |         |        |           |       |        | XXXX         |       |         |           |       |          |         |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### **Flash Memory Control Registers** 5.5

| bit 15       Invariant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/SO-0            | R/W-0                       | R/W-0                          | U-0                                   | U-0                         | U-0                | U-0                    | U-0           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------|--------------------------------|---------------------------------------|-----------------------------|--------------------|------------------------|---------------|

| U-0       R/W-0       U-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         Image: Image                                                                                                                                                                                                                                                                                                        | WR <sup>(1)</sup> | WREN <sup>(1)</sup>         | WRERR <sup>(1)</sup>           | _                                     | —                           | _                  | —                      | _             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | bit 15            |                             | · · ·                          |                                       |                             |                    |                        | bit 8         |

| -         ERASE <sup>(1)</sup> -         NVMOP<3:0::         1.2           bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | U-0               | R/W-0                       | U-0                            | U-0                                   | R/W-0                       | R/W-0              | R/W-0                  | R/W-0         |

| bit 7       bit 7         Legend:       SO = Settable Only bit         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       WR: Write Control bit <sup>(1)</sup> 1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the b cleared by hardware once operation is complete. This bit can only be set (not cleared) in software once operation is complete and inactive         bit 14       WREN: Write Enable bit <sup>(1)</sup> 1 = Enables Flash program/erase operations         o = Inhibits Flash program/erase operations       o = Inhibits Flash program/erase operations         bit 13       WRERR: Write Sequence Error Flag bit <sup>(1)</sup> 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation sepecified by NVMOP<3:0> on the next WR command         bit 6       ERASE: Erase/Program Enable bit <sup>(1)</sup> 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         bit 5-4       Unimplemented: Read as '0'         bit 3-0       NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1:       1111 = No operation         1011 = No operation       0010 = Memory page erase operation         0011 = No oper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                 |                             | _                              | _                                     |                             | NVMOP              | <3:0> <sup>(1,2)</sup> | -             |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       WR: Write Control bit <sup>(1)</sup> 1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the bic cleared by hardware once operation is complete. This bit can only be set (not cleared) in software one operation is complete and inactive         bit 14       WREN: Write Enable bit <sup>(1)</sup> 1 = Enables Flash program/erase operations         0 = Inhibits Flash program/erase operations       0 = Inhibits Flash program/erase operations         bit 13       WRERR: Write Sequence Error Flag bit <sup>(1)</sup> 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation selectified by NVMOP<3:0> on the next WR command         0 = Performs the program operation Select bits <sup>(1,2)</sup> If ERASE = 1:         1111 = No operation         1010 = Erase general segment         0011 = Memory page erase operation         0011 = No operation         0011 = No operation         1011 = No operation         1011 = No operatio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | bit 7             |                             |                                |                                       |                             |                    |                        | bit           |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       WR: Write Control bit <sup>(1)</sup> 1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the bic cleared by hardware once operation is complete. This bit can only be set (not cleared) in software once operation is complete and inactive         bit 14       WREN: Write Enable bit <sup>(1)</sup> 1 = Enables Flash program/erase operations         0 = Inhibits Flash program/erase operations       0 = Inhibits Flash program/erase operations         bit 13       WRERR: Write Sequence Error Flag bit <sup>(1)</sup> 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         0 = Depration       1101 = Erase general segment         0101 = No operation       1101 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Legend:           |                             | SO = Settab                    | le Only bit                           |                             |                    |                        |               |

| bit 15 WR: Write Control bit <sup>(1)</sup><br>1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the b<br>cleared by hardware once operation is complete. This bit can only be set (not cleared) in softwa<br>0 = Program or erase operation is complete and inactive<br>bit 14 WREN: Write Enable bit <sup>(1)</sup><br>1 = Enables Flash program/erase operations<br>0 = Inhibits Flash program/erase operations<br>bit 13 WRERR: Write Sequence Error Flag bit <sup>(1)</sup><br>1 = An improper program or erase sequence attempt or termination has occurred (bit is<br>automatically on any set attempt of the WR bit)<br>0 = The program or erase operation completed normally<br>bit 6 ERASE: Erase/Program Enable bit <sup>(1)</sup><br>1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command<br>0 = Performs the program operation specified by NVMOP<3:0> on the next WR command<br>0 = Performs the program operation specified by NVMOP<3:0> on the next WR command<br>bit 5-4 Unimplemented: Read as 'o'<br>bit 3-0 NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup><br><u>If ERASE = 1:</u><br>1111 = No operation<br>1001 = Erase general segment<br>0010 = Reserved<br>0000 = Reserved<br><u>If ERASE = 0:</u><br>1111 = No operation<br>1001 = No operation                                                                                                                                                                                                                                                               | R = Readable      | e bit                       | W = Writable                   | e bit                                 | U = Unimple                 | mented bit, read   | l as '0'               |               |

| 1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the bicleared by hardware once operation is complete. This bit can only be set (not cleared) in software or erase operation is complete and inactive         0 = Program or erase operation is complete and inactive         bit 14       WREN: Write Enable bit <sup>(1)</sup> 1 = Enables Flash program/erase operations         0 = Inhibits Flash program/erase operations         0 = Inhibits Flash program/erase operations         bit 13       WRERR: Write Sequence Error Flag bit <sup>(1)</sup> 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation specified hy NVMOP<3:0> on the next WR command         0 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation Select bits <sup>(1,2)</sup> If ERASE = 1:         1111 = No operation         1101 = Erase general segment         011 = No operation         1101 = Reserved         0000 = Reserved         If ERASE = 0:         1111 = No operation         1101 = No operation         1101 = No operation         1111 = No operation         1101 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -n = Value at     | POR                         | '1' = Bit is se                | et                                    | '0' = Bit is cle            | eared              | x = Bit is unkr        | iown          |

| cleared by hardware once operation is complete. This bit can only be set (not cleared) in softwa<br>0 = Program or erase operation is complete and inactive<br>bit 14 WREN: Write Enable bit <sup>(1)</sup><br>1 = Enables Flash program/erase operations<br>0 = Inhibits Flash program/erase operations<br>bit 13 WRERR: Write Sequence Error Flag bit <sup>(1)</sup><br>1 = An improper program or erase sequence attempt or termination has occurred (bit is<br>automatically on any set attempt of the WR bit)<br>0 = The program or erase operation completed normally<br>bit 12-7 Unimplemented: Read as '0'<br>bit 6 ERASE: Erase/Program Enable bit <sup>(1)</sup><br>1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command<br>0 = Performs the program operation specified by NVMOP<3:0> on the next WR command<br>0 = Performs the program operation specified by NVMOP<3:0> on the next WR command<br>bit 5-4 Unimplemented: Read as '0'<br>bit 3-0 NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup><br>If ERASE = 1:<br>1111 = No operation<br>1010 = Erase general segment<br>0011 = No operation<br>0010 = Memory page erase operation<br>0010 = Reserved<br>0000 = Reserved<br>1111 = No operation<br>1011 | bit 15            |                             |                                |                                       | r orono oporati             | on The operation   | an is colf timed       | and the bit i |

| bit 14 WREN: Write Enable bit <sup>(1)</sup> 1 = Enables Flash program/erase operations 0 = Inhibits Flash program/erase operations bit 13 WRERR: Write Sequence Error Flag bit <sup>(1)</sup> 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit) 0 = The program or erase operation completed normally bit 12-7 Unimplemented: Read as '0' bit 6 ERASE: Erase/Program Enable bit <sup>(1)</sup> 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command 0 = Performs the program operation specified by NVMOP<3:0> on the next WR command 0 = Performs the program operation specified by NVMOP<3:0> on the next WR command 0 = Performs the program operation Select bits <sup>(1,2)</sup> bit 3-0 NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1: 1111 = No operation 1101 = Erase general segment 0011 = No operation 0010 = Memory page erase operation 0010 = Reserved 0000 = Reserved 0000 = Reserved 1111 = No operation 1011 = No operation 1011 = No operation 1011 = No operation 1011 = No operation 0010 = Memory word program operation 0011 = Memory word program operation 0010 = No operation 0011 = No operation 0010 = No operati                                                                                                                              |                   | cleared by                  | hardware onc                   | eoperation                            | is complete. Th             | is bit can only be |                        |               |

| 1 = Enables Flash program/erase operations         0 = Inhibits Flash program/erase operations         bit 13       WRERR: Write Sequence Error Flag bit <sup>(1)</sup> 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation completed normally         bit 12-7       Unimplemented: Read as '0'         bit 6       ERASE: Erase/Program Enable bit <sup>(1)</sup> 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         bit 5-4       Unimplemented: Read as '0'         bit 3-0       NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1:       1111 = No operation         1101 = Erase general segment       0011 = No operation         0010 = Memory page erase operation       0000 = Reserved         0000 = Reserved       If ERASE = 0:         1111 = No operation       1101 = No operation         1101 = No operation       0011 = No operation         1011 = No operation       10011 = No operation         1001 = No operation       0011 = No operation         1011 = No operation       1011 = No operation         1001 = No operation       0011 = Ne operation         0011 = Ne operatio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 14            | •                           |                                | · · · · · · · · · · · · · · · · · · · |                             |                    |                        |               |

| 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation completed normally         bit 12-7       Unimplemented: Read as '0'         bit 6       ERASE: Erase/Program Enable bit <sup>(1)</sup> 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         bit 5-4       Unimplemented: Read as '0'         bit 3-0       NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1:       1111 = No operation         101 = Erase general segment       0011 = No operation         0010 = Memory page erase operation       0010 = Reserved         If ERASE = 0:       1111 = No operation         1101 = No operation       1001 = Reserved         0000 = Reserved       If ERASE = 0:         1111 = No operation       1101 = No operation         0101 = No operation       0011 = Nemory word program operation         011 = No operation       0011 = Nemory word program operation         0011 = Nemory word program operation       0011 = Nemory word program operation         0010 = No operation       0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |                             |                                |                                       |                             |                    |                        |               |

| 1 = An improper program or erase sequence attempt or termination has occurred (bit is automatically on any set attempt of the WR bit)         0 = The program or erase operation completed normally         bit 12-7       Unimplemented: Read as '0'         bit 6       ERASE: Erase/Program Enable bit <sup>(1)</sup> 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         bit 5-4       Unimplemented: Read as '0'         bit 3-0       NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1:       1111 = No operation         101 = Erase general segment       0011 = Reserved         0010 = Memory page erase operation       0011 = Reserved         1111 = No operation       1101 = No operation         0010 = Reserved       If ERASE = 0:         11111 = No operation       1101 = No operation         0011 = Reserved       0000 = Reserved         1101 = No operation       1101 = No operation         1101 = No operation       1101 = No operation         1101 = No operation       1101 = No operation         0011 = Nemory word program operation       0011 = Memory word program operation         0011 = No operation       011 = No operation         0110 = No operation       011 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit 13            | WRERR: Write                | Sequence Er                    | ror Flag bit <sup>(</sup>             | 1)                          |                    |                        |               |

| bit 12-7 Unimplemented: Read as '0'<br>bit 6 ERASE: Erase/Program Enable bit <sup>(1)</sup><br>1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command<br>0 = Performs the program operation specified by NVMOP<3:0> on the next WR command<br>bit 5-4 Unimplemented: Read as '0'<br>bit 3-0 NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup><br>If ERASE = 1:<br>1111 = No operation<br>1101 = Erase general segment<br>0011 = No operation<br>0010 = Memory page erase operation<br>0010 = Reserved<br>0000 = Reserved<br>If ERASE = 0:<br>1111 = No operation<br>101 = No operation<br>101 = No operation<br>0011 = Memory word program operation<br>0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   | 1 = An improp<br>automatica | per program of ally on any set | or erase se<br>attempt of t           | equence attem<br>he WR bit) |                    | on has occurre         | ed (bit is se |

| bit 6       ERASE: Erase/Program Enable bit <sup>(1)</sup> 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         bit 5-4       Unimplemented: Read as '0'         bit 3-0       NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1:       1111 = No operation         1011 = Erase general segment       0011 = Kno operation         0010 = Memory page erase operation       0001 = Reserved         0000 = Reserved       If ERASE = 0:         1111 = No operation       1101 = No operation         0010 = Memory page erase operation       0011 = Reserved         0000 = Reserved       If ERASE = 0:         1111 = No operation       1001 = No operation         1001 = No operation       0010 = No operation         0011 = No operation       0011 = No operation         0010 = No operation       0011 = No operation         0011 = No operation       0010 = No operation <td>hit 10 7</td> <td></td> <td></td> <td></td> <td>ipieted normali</td> <td>у</td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | hit 10 7          |                             |                                |                                       | ipieted normali             | у                  |                        |               |

| 1 = Performs the erase operation specified by NVMOP<3:0> on the next WR command         0 = Performs the program operation specified by NVMOP<3:0> on the next WR command         bit 5-4       Unimplemented: Read as '0'         bit 3-0       NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1:       1111 = No operation         1011 = Erase general segment       0011 = No operation         0010 = Memory page erase operation       0001 = Reserved         0000 = Reserved       If ERASE = 0:         1111 = No operation       1101 = No operation         0101 = No operation       0001 = Reserved         0000 = Reserved       If ERASE = 0:         1111 = No operation       1001 = No operation         0011 = No operation       0011 = No operation         0010 = No operation       0011 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   | -                           |                                |                                       |                             |                    |                        |               |

| <ul> <li>0 = Performs the program operation specified by NVMOP&lt;3:0&gt; on the next WR command</li> <li>bit 5-4 Unimplemented: Read as '0'</li> <li>bit 3-0 NVMOP&lt;3:0&gt;: NVM Operation Select bits<sup>(1,2)</sup></li> <li>If ERASE = 1:<br/>1111 = No operation<br/>1101 = Erase general segment<br/>0011 = No operation<br/>0010 = Memory page erase operation<br/>0001 = Reserved<br/>0000 = Reserved</li> <li>If ERASE = 0:<br/>1111 = No operation<br/>1101 = No operation<br/>0011 = Memory word program operation<br/>0010 = No operation</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DILO              |                             | •                              |                                       |                             | <3:0> on the new   | vt WP comman           | d             |

| bit 5-4 Unimplemented: Read as '0'<br>bit 3-0 NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup><br>If ERASE = 1:<br>1111 = No operation<br>1101 = Erase general segment<br>0011 = No operation<br>0010 = Memory page erase operation<br>0001 = Reserved<br>0000 = Reserved<br>If ERASE = 0:<br>1111 = No operation<br>1101 = No operation<br>1101 = No operation<br>0011 = Memory word program operation<br>0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                   |                             |                                |                                       |                             |                    |                        |               |

| bit 3-0 NVMOP<3:0>: NVM Operation Select bits <sup>(1,2)</sup> If ERASE = 1: 1111 = No operation 1101 = Erase general segment 0011 = No operation 0010 = Memory page erase operation 0001 = Reserved 0000 = Reserved If ERASE = 0: 1111 = No operation 1101 = No operation 1101 = No operation 0011 = Memory word program operation 0010 = No operation 0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 5-4           |                             |                                |                                       | ,                           |                    |                        |               |

| If ERASE = 1:         1111 = No operation         101 = Erase general segment         0011 = No operation         0010 = Memory page erase operation         0001 = Reserved         0000 = Reserved         If ERASE = 0:         1111 = No operation         1101 = No operation         0011 = Memory word program operation         0011 = Memory word program operation         0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bit 3-0           | -                           |                                |                                       | ts <sup>(1,2)</sup>         |                    |                        |               |

| <pre>1101 = Erase general segment<br/>0011 = No operation<br/>0010 = Memory page erase operation<br/>0001 = Reserved<br/>0000 = Reserved<br/><u>If ERASE = 0:</u><br/>1111 = No operation<br/>1101 = No operation<br/>0011 = Memory word program operation<br/>0010 = No operation</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |                             |                                |                                       |                             |                    |                        |               |

| 0011 = No operation         0010 = Memory page erase operation         0001 = Reserved         0000 = Reserved         If ERASE = 0:         1111 = No operation         1101 = No operation         0011 = Memory word program operation         0010 = No operation         0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   | •                           |                                |                                       |                             |                    |                        |               |

| 0010 = Memory page erase operation<br>0001 = Reserved<br>0000 = Reserved<br><u>If ERASE = 0:</u><br>1111 = No operation<br>1101 = No operation<br>0011 = Memory word program operation<br>0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |                             |                                | ent                                   |                             |                    |                        |               |

| 0001 = Reserved<br>0000 = Reserved<br><u>If ERASE = 0:</u><br>1111 = No operation<br>1101 = No operation<br>0011 = Memory word program operation<br>0010 = No operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |                             |                                | oneration                             |                             |                    |                        |               |