Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 6КВ (2К х 24)                                                                     |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 1K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 6x10b; D/A 2x10b                                                              |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 36-VFTLA Exposed Pad                                                              |

| Supplier Device Package    | 36-VTLA (5x5)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj06gs202at-i-tl |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

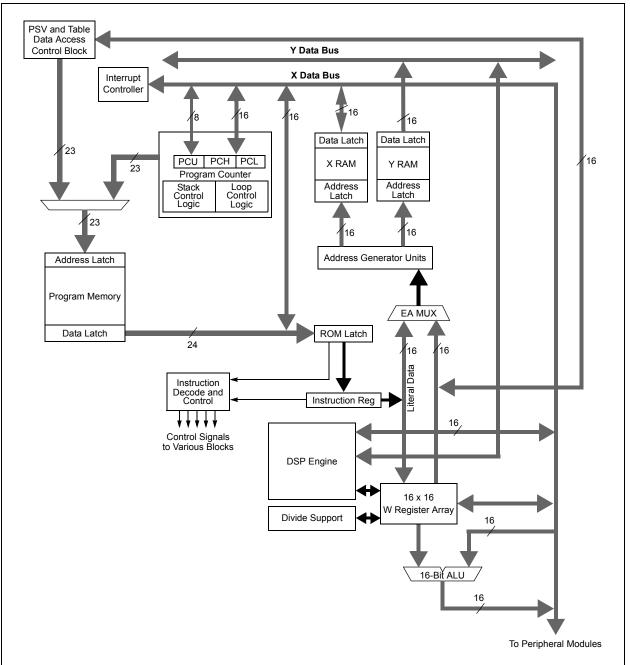

#### 3.3 Special MCU Features

A 17-bit by 17-bit single-cycle multiplier is shared by both the MCU ALU and DSP engine. The multiplier can perform signed, unsigned and mixed-sign multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication not only allows you to perform mixed-sign multiplication, it also achieves accurate results for special operations, such as (-1.0) x (-1.0). The 16/16 and 32/16 divide operations are supported, both fractional and integer. All divide instructions are iterative operations. They must be executed within a REPEAT loop, resulting in a total execution time of 19 instruction cycles. The divide operation can be interrupted during any of those 19 cycles without loss of data.

A 40-bit barrel shifter is used to perform up to a 16-bit left or right shift in a single cycle. The barrel shifter can be used by both MCU and DSP instructions.

### FIGURE 3-1: CPU CORE BLOCK DIAGRAM

# 4.3 Special Function Register Maps

#### TABLE 4-1: CPU CORE REGISTER MAP

| IABLE 4-1 | 1:          |          | LE KEGI  |          |          |          |           |                 |              |       |         |          |               |           |           |           |       |               |

|-----------|-------------|----------|----------|----------|----------|----------|-----------|-----------------|--------------|-------|---------|----------|---------------|-----------|-----------|-----------|-------|---------------|

| SFR Name  | SFR<br>Addr | Bit 15   | Bit 14   | Bit 13   | Bit 12   | Bit 11   | Bit 10    | Bit 9           | Bit 8        | Bit 7 | Bit 6   | Bit 5    | Bit 4         | Bit 3     | Bit 2     | Bit 1     | Bit 0 | All<br>Resets |

| WREG0     | 0000        |          |          |          |          |          | V         | Vorking Regist  | er 0         |       |         |          |               |           |           |           |       | 0000          |

| WREG1     | 0002        |          |          |          |          |          | V         | Vorking Regist  | er 1         |       |         |          |               |           |           |           |       | 0000          |

| WREG2     | 0004        |          |          |          |          |          | V         | Vorking Regist  | er 2         |       |         |          |               |           |           |           |       | 0000          |

| WREG3     | 0006        |          |          |          |          |          | V         | Vorking Regist  | er 3         |       |         |          |               |           |           |           |       | 0000          |

| WREG4     | 0008        |          |          |          |          |          | V         | Vorking Regist  | er 4         |       |         |          |               |           |           |           |       | 0000          |

| WREG5     | 000A        |          |          |          |          |          | V         | Vorking Regist  | er 5         |       |         |          |               |           |           |           |       | 0000          |

| WREG6     | 000C        |          |          |          |          |          | V         | Vorking Regist  | er 6         |       |         |          |               |           |           |           |       | 0000          |

| WREG7     | 000E        |          |          |          |          |          | V         | Vorking Regist  | er 7         |       |         |          |               |           |           |           |       | 0000          |

| WREG8     | 0010        |          |          |          |          |          | V         | Vorking Regist  | er 8         |       |         |          |               |           |           |           | ,     | 0000          |

| WREG9     | 0012        |          |          |          |          |          | V         | Vorking Regist  | er 9         |       |         |          |               |           |           |           |       | 0000          |

| WREG10    | 0014        |          |          |          |          |          | W         | orking Registe  | er 10        |       |         |          |               |           |           |           | ,     | 0000          |

| WREG11    | 0016        |          |          |          |          |          | W         | /orking Registe | er 11        |       |         |          |               |           |           |           | ,     | 0000          |

| WREG12    | 0018        |          |          |          |          |          | W         | orking Registe  | er 12        |       |         |          |               |           |           |           |       | 0000          |

| WREG13    | 001A        |          |          |          |          |          | W         | orking Registe  | er 13        |       |         |          |               |           |           |           | ,     | 0000          |

| WREG14    | 001C        |          |          |          |          |          | W         | orking Registe  | er 14        |       |         |          |               |           |           |           |       | 0000          |

| WREG15    | 001E        |          |          |          |          |          | W         | orking Registe  | er 15        |       |         |          |               |           |           |           | ,     | 0800          |

| SPLIM     | 0020        |          |          |          |          |          | Stack     | Pointer Limit   | Register     |       |         |          |               |           |           |           | ,     | XXXX          |

| ACCAL     | 0022        |          |          |          |          |          |           | ACCAL           |              |       |         |          |               |           |           |           |       | XXXX          |

| ACCAH     | 0024        |          |          |          |          |          |           | ACCAH           |              |       |         |          |               |           |           |           | ,     | XXXX          |

| ACCAU     | 0026        | ACCA<39> | ACCA<39> | ACCA<39> | ACCA<39> | ACCA<39> | ACCA<39>  | ACCA<39>        | ACCA<39>     |       |         |          | ACCA          | Ú         |           |           |       | XXXX          |

| ACCBL     | 0028        |          |          |          |          |          |           | ACCBL           |              | •     |         |          |               |           |           |           | ,     | XXXX          |

| ACCBH     | 002A        |          |          |          |          |          |           | ACCBH           |              |       |         |          |               |           |           |           |       | XXXX          |

| ACCBU     | 002C        | ACCB<39> | ACCB<39> | ACCB<39> | ACCB<39> | ACCB<39> | ACCB<39>  | ACCB<39>        | ACCB<39>     |       |         |          | ACCB          | U         |           |           |       | XXXX          |

| PCL       | 002E        |          |          |          |          | •        | Program C | Counter Low W   | ord Register | r     |         |          |               |           |           |           |       | 0000          |

| PCH       | 0030        | _        | _        | _        | _        | _        | _         | _               | _            |       |         | Program  | Counter Hig   | gh Byte I | Register  |           |       | 0000          |

| TBLPAG    | 0032        | _        | _        | _        | _        | _        | _         | _               | _            |       |         | Table Pa | ge Address    | Pointer I | Register  |           |       | 0000          |

| PSVPAG    | 0034        | _        | _        | _        | _        | _        | _         | _               | _            |       | Program | Memory V | isibility Pag | e Addres  | ss Pointe | er Regist | er    | 0000          |

| RCOUNT    | 0036        |          |          |          |          |          | Repea     | t Loop Counte   | r Register   |       |         |          |               |           |           |           |       | XXXX          |

| DCOUNT    | 0038        |          |          |          |          |          |           | DCOUNT<15:      | 0>           |       |         |          |               |           |           |           |       | XXXX          |

| DOSTARTL  | 003A        |          |          |          |          |          | DOST      | TARTL<15:1>     |              |       |         |          |               |           |           |           | 0     | XXXX          |

| DOSTARTH  | 003C        | —        | —        | _        | _        | _        | _         | _               | —            | —     | —       |          | DC            | START     | H<5:0>    |           |       | 00xx          |

| DOENDL    | 003E        |          |          |          |          |          | DOE       | NDL<15:1>       |              |       |         |          |               |           |           |           | 0     | XXXX          |

| DOENDH    | 0040        | —        | —        | _        | _        | _        | _         | _               | —            | —     | —       |          |               | DOEN      | DH        |           |       | 00xx          |

|           | 0042        | OA       | OB       | SA       | SB       | 1        |           | -               |              |       | IPL<2:0 |          | 1             | -         | -         | -         |       | +             |

dsPIC33FJ06GS001/101A/102A/202A and dsPIC33FJ09GS302

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| File Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|-------------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| CNEN1     | 0060        | —      | _      |        | —      |        | _      | _     | _     | CN7IE  | CN6IE  | CN5IE  | CN4IE  | CN3IE  | CN2IE  | CN1IE  | CN0IE  | 0000          |

| CNPU1     | 0068        | _      | _      |        | _      | _      |        |       |       | CN7PUE | CN6PUE | CN5PUE | CN4PUE | CN3PUE | CN2PUE | CN1PUE | CN0PUE | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-3: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJ06GS102A, dsPIC33FJ06GS202A, AND dsPIC33FJ09GS302

| File<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| CNEN1        | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE  | CN8IE  | CN7IE  | CN6IE  | CN5IE  | CN4IE  | CN3IE  | CN2IE  | CN1IE  | CN0IE  | 0000          |

| CNPU1        | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE | CN8PUE | CN7PUE | CN6PUE | CN5PUE | CN4PUE | CN3PUE | CN2PUE | CN1PUE | CN0PUE | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-9: TIMER REGISTER MAP

| SFR<br>Name | SFR<br>Addr | Bit 15     | Bit 14      | Bit 13      | Bit 12      | Bit 11       | Bit 10     | Bit 9       | Bit 8       | Bit 7    | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|------------|-------------|-------------|-------------|--------------|------------|-------------|-------------|----------|-------|-------|--------|-------|-------|-------|-------|---------------|

| TMR1        | 0100        |            |             |             |             |              |            |             | Timer1 Re   | egister  |       |       |        |       |       |       |       | 0000          |

| PR1         | 0102        |            |             |             |             |              |            |             | Period Reg  | gister 1 |       |       |        |       |       |       |       | FFFF          |

| T1CON       | 0104        | TON        | _           | TSIDL       | _           | —            | _          | _           | —           | —        | TGATE | TCKPS | 6<1:0> | —     | TSYNC | TCS   | _     | 0000          |

| TMR2        | 0106        |            |             |             |             |              |            |             | Timer2 Re   | egister  |       |       |        |       |       |       |       | 0000          |

| PR2         | 010C        |            |             |             |             |              |            |             | Period Reg  | gister 2 |       |       |        |       |       |       |       | FFFF          |

| T2CON       | 0110        | TON        | _           | TSIDL       | _           | —            | _          | _           | —           | —        | TGATE | TCKPS | 6<1:0> | —     | —     | TCS   | _     | 0000          |

| Legend:     | x = unkr    | nown value | on Reset. – | - = unimple | mented, rea | d as '0'. Re | set values | are shown i | n hexadecir | nal.     |       |       |        |       |       |       |       |               |

#### TABLE 4-10: INPUT CAPTURE REGISTER MAP FOR dsPIC33FJ06GS202A AND dsPIC33FJ09GS302

| SFR<br>Name | SFR Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7      | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1   | Bit 0 | All<br>Resets |

|-------------|----------|--------|--------|--------|--------|--------|--------|-------|-----------|------------|-------|-------|-------|-------|-------|---------|-------|---------------|

| IC1BUF      | 0140     |        |        |        |        |        |        | Inpu  | t Capture | 1 Register |       |       |       |       |       |         |       | XXXX          |

| IC1CON      | 0142     | _      | —      | ICSIDL | —      | _      |        | _     |           |            | ICI<1 | :0>   | ICOV  | ICBNE | 10    | CM<2:0> |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-11: OUTPUT COMPARE REGISTER MAP FOR dsPIC33FJ06GS101A, dsPIC33FJ06GS102A, dsPIC33FJ06GS202A AND dsPIC33FJ09GS302

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8       | Bit 7      | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1   | Bit 0 | All<br>Resets |

|-------------|-------------|--------|--------|--------|--------|--------|--------|------------|-------------|------------|--------|-------|-------|-------|-------|---------|-------|---------------|

| OC1RS       | 0180        |        |        |        |        |        |        | Output Con | pare 1 Seco | ondary Reg | gister |       |       |       |       |         |       | XXXX          |

| OC1R        | 0182        |        |        |        |        |        |        | Outpu      | t Compare ? | 1 Register |        |       |       |       |       |         |       | XXXX          |

| OC1CON      | 0184        | _      | _      | OCSIDL | _      | _      | _      | _          | _           | _          | _      | _     | OCFLT | _     | 0     | CM<2:0> |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 1 BOR: Brown-out Reset Flag bit

- 1 = A Brown-out Reset has occurred

- 0 = A Brown-out Reset has not occurred

#### bit 0 POR: Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

# 6.2 System Reset

There are two types of Reset:

- Cold Reset

- Warm Reset

A cold Reset is the result of a Power-on Reset (POR) or a Brown-out Reset (BOR). On a cold Reset, the FNOSC Configuration bits in the FOSC Configuration register select the device clock source.

A warm Reset is the result of all the other Reset sources, including the RESET instruction. On warm Reset, the device will continue to operate from the current clock source, as indicated by the Current Oscillator Selection bits (COSC<2:0>) in the Oscillator Control register (OSCCON<14:12>).

The device is kept in a Reset state until the system power supplies have stabilized at appropriate levels and the oscillator clock is ready. The sequence in which this occurs is provided in Figure 6-2.

| Oscillator Mode        | Oscillator<br>Start-up Delay | Oscillator<br>Start-up Timer | PLL Lock Time        | Total Delay                             |

|------------------------|------------------------------|------------------------------|----------------------|-----------------------------------------|

| FRC, FRCDIV16, FRCDIVN | Toscd <sup>(1)</sup>         | _                            | _                    | Toscd <sup>(1)</sup>                    |

| FRCPLL                 | Toscd <sup>(1)</sup>         | —                            | ТLОСК <sup>(3)</sup> | Toscd + Tlock <sup>(1,3)</sup>          |

| XT                     | Toscd <sup>(1)</sup>         | Tost <sup>(2)</sup>          | —                    | Toscd + Tost <sup>(1,2)</sup>           |

| HS                     | Toscd <sup>(1)</sup>         | Tost <sup>(2)</sup>          | —                    | Toscd + Tost <sup>(1,2)</sup>           |

| EC                     | —                            | —                            | —                    | —                                       |

| XTPLL                  | Toscd <sup>(1)</sup>         | Tost <sup>(2)</sup>          | ТLОСК <sup>(3)</sup> | TOSCD + TOST + TLOCK <sup>(1,2,3)</sup> |

| HSPLL                  | Toscd <sup>(1)</sup>         | Tost <sup>(2)</sup>          | ТLOCK <sup>(3)</sup> | TOSCD + TOST + TLOCK <sup>(1,2,3)</sup> |

| ECPLL                  | —                            | —                            | ТLOCK <sup>(3)</sup> | ТLОСК <sup>(3)</sup>                    |

| LPRC                   | Toscd <sup>(1)</sup>         |                              | _                    | Toscd <sup>(1)</sup>                    |

**Note 1:** TOSCD = Oscillator start-up delay (1.1 μs max. for FRC, 70 μs max. for LPRC). Crystal oscillator start-up times vary with crystal characteristics, load capacitance, etc.

**2:** TOST = Oscillator Start-up Timer (OST) delay (1024 oscillator clock period). For example, TOST = 102.4 μs for a 10 MHz crystal and TOST = 32 ms for a 32 kHz crystal.

**3:** TLOCK = PLL lock time (1.5 ms nominal) if PLL is enabled.

TABLE 6-1: OSCILLATOR DELAY

# REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 2 | STKERR: Stack Error Trap Status bit                |

|-------|----------------------------------------------------|

|       | 1 = Stack error trap has occurred                  |

|       | 0 = Stack error trap has not occurred              |

| bit 1 | <b>OSCFAIL:</b> Oscillator Failure Trap Status bit |

|       | 1 = Oscillator failure trap has occurred           |

|       | 0 = Oscillator failure trap has not occurred       |

| bit 0 | Unimplemented: Read as '0'                         |

© 2011-2012 Microchip Technology Inc.

| <b>REGISTER 7</b>                                                                                                                                         | -10: IFS6: I                                      | NTERRUPT                                                                               | FLAG STAT                             | US REGISTE       | ER 6             |                       |       |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------|------------------|------------------|-----------------------|-------|--|--|

| R/W-0                                                                                                                                                     | R/W-0                                             | U-0                                                                                    | U-0                                   | U-0              | U-0              | U-0                   | U-0   |  |  |

| ADCP1IF                                                                                                                                                   | ADCP0IF                                           | _                                                                                      |                                       | _                |                  | —                     | _     |  |  |

| bit 15                                                                                                                                                    |                                                   |                                                                                        |                                       |                  |                  |                       | bit 8 |  |  |

|                                                                                                                                                           |                                                   |                                                                                        |                                       |                  |                  |                       |       |  |  |

| R/W-0                                                                                                                                                     | U-0                                               | U-0                                                                                    | U-0                                   | U-0              | U-0              | R/W-0                 | U-0   |  |  |

| AC2IF <sup>(1)</sup>                                                                                                                                      |                                                   |                                                                                        |                                       |                  |                  | PWM4IF <sup>(2)</sup> |       |  |  |

| bit 7                                                                                                                                                     |                                                   |                                                                                        |                                       |                  |                  |                       | bit 0 |  |  |

|                                                                                                                                                           |                                                   |                                                                                        |                                       |                  |                  |                       | 1     |  |  |

| Legend:                                                                                                                                                   |                                                   |                                                                                        |                                       |                  |                  |                       |       |  |  |

| R = Readable                                                                                                                                              | bit                                               | W = Writable                                                                           | bit                                   | U = Unimpler     | mented bit, read | d as '0'              |       |  |  |

| -n = Value at F                                                                                                                                           | POR                                               | '1' = Bit is set                                                                       |                                       | '0' = Bit is cle | ared             | x = Bit is unkno      | own   |  |  |

| bit 14                                                                                                                                                    | 0 = Interrupt r<br>ADCP0IF: AD<br>1 = Interrupt r | equest has occ<br>equest has not<br>OC Pair 0 Conv<br>equest has occ<br>equest has not | t occurred<br>ersion Done I<br>curred | nterrupt Flag S  | itatus bit       |                       |       |  |  |

| bit 13-8                                                                                                                                                  | Unimplemen                                        | ted: Read as '                                                                         | 0'                                    |                  |                  |                       |       |  |  |

| bit 7 AC2IF: Analog Comparator 2 Interrupt Flag Status bit <sup>(1)</sup><br>1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred |                                                   |                                                                                        |                                       |                  |                  |                       |       |  |  |

| bit 6-2                                                                                                                                                   | Unimplemen                                        | ted: Read as '                                                                         | 0'                                    |                  |                  |                       |       |  |  |

| bit 1                                                                                                                                                     | PWM4IF: PW                                        | M4 Interrupt F                                                                         | lag Status bit <sup>(;</sup>          | 2)               |                  |                       |       |  |  |

|                                                                                                                                                           |                                                   | equest has oc<br>equest has not                                                        |                                       |                  |                  |                       |       |  |  |

| bit 0                                                                                                                                                     | Unimplemen                                        | ted: Read as '                                                                         | 0'                                    |                  |                  |                       |       |  |  |

# \_\_\_\_\_

Note 1: This bit is not implemented in dsPIC33FJ06GS101A/102A devices.

2: This bit is not implemented in dsPIC33FJ06GS102A/202A devices.

| U-0          | R/W-1       | R/W-0                                     | R/W-0          | U-0                          | R/W-1            | R/W-0           | R/W-0 |

|--------------|-------------|-------------------------------------------|----------------|------------------------------|------------------|-----------------|-------|

| —            |             | U1RXIP<2:0>(1)                            |                |                              |                  | SPI1IP<2:0>(1)  |       |

| oit 15       |             |                                           |                |                              |                  |                 | bit   |

|              |             |                                           |                |                              |                  |                 |       |

| U-0          | R/W-1       | R/W-0                                     | R/W-0          | U-0                          | U-0              | U-0             | U-0   |

|              |             | SPI1EIP<2:0>(1)                           | )              | —                            |                  | —               | _     |

| bit 7        |             |                                           |                |                              |                  |                 | bit   |

|              |             |                                           |                |                              |                  |                 |       |

| Legend:      |             |                                           |                |                              |                  |                 |       |

| R = Readab   | le bit      | W = Writable b                            | oit            | U = Unimpler                 | nented bit, read | d as '0'        |       |

| -n = Value a | t POR       | '1' = Bit is set                          |                | '0' = Bit is cle             | ared             | x = Bit is unkn | own   |

|              |             |                                           |                |                              |                  |                 |       |

| bit 15       | Unimplem    | ented: Read as 'o                         | )'             |                              |                  |                 |       |

| bit 14-12    | U1RXIP<2:   | 0>: UART1 Rece                            | iver Interrupt | Priority bits <sup>(1)</sup> |                  |                 |       |

|              | 111 = Inter | rupt is Priority 7 (ł                     | nighest priori | ty interrupt)                |                  |                 |       |

|              | •           |                                           |                |                              |                  |                 |       |

|              | •           |                                           |                |                              |                  |                 |       |

|              | 001 = Inter | rupt is Priority 1                        |                |                              |                  |                 |       |

|              |             | rupt source is disa                       | abled          |                              |                  |                 |       |

| bit 11       | Unimplem    | ented: Read as 'o                         | )'             |                              |                  |                 |       |

| bit 10-8     | SPI1IP<2:0  | >: SPI1 Event Int                         | errupt Priorit | y bits <sup>(1)</sup>        |                  |                 |       |

|              | 111 = Inter | rupt is Priority 7 (ł                     | nighest priori | ty interrupt)                |                  |                 |       |

|              | •           |                                           |                |                              |                  |                 |       |

|              | •           |                                           |                |                              |                  |                 |       |

|              | 001 = Inter | rupt is Priority 1                        |                |                              |                  |                 |       |

|              |             | rupt source is disa                       | abled          |                              |                  |                 |       |

| bit 7        | Unimplem    | ented: Read as 'o                         | )'             |                              |                  |                 |       |

| bit 6-4      | SPI1EIP<2   | :0>: SPI1 Error In                        | terrupt Priori | ty bits <sup>(1)</sup>       |                  |                 |       |

|              | 111 = Inter | rupt is Priority 7 (I                     | nighest priori | ty interrupt)                |                  |                 |       |

|              | •           |                                           |                |                              |                  |                 |       |

|              | •           |                                           |                |                              |                  |                 |       |

|              |             | rupt is Priority 1<br>rupt source is disa | abled          |                              |                  |                 |       |

|              |             | •                                         |                |                              |                  |                 |       |

# Note 1: These bits are not implemented in the dsPIC33FJ06GS001 device.

| REGISTER                                                   | R 7-26: IPC14: | INTERRUPT        |                |                                         | REGISTER 14 |     |       |

|------------------------------------------------------------|----------------|------------------|----------------|-----------------------------------------|-------------|-----|-------|

| U-0                                                        | U-0            | U-0              | U-0            | U-0                                     | U-0         | U-0 | U-0   |

|                                                            | —              | —                | —              | —                                       |             |     | —     |

| bit 15                                                     |                |                  |                |                                         |             |     | bit 8 |

|                                                            |                |                  |                |                                         |             |     |       |

| U-0                                                        | R/W-1          | R/W-0            | R/W-0          | U-0                                     | U-0         | U-0 | U-0   |

| —                                                          |                | PSEMIP<2:0>      |                | —                                       | _           |     | —     |

| bit 7                                                      |                |                  |                |                                         |             |     | bit 0 |

|                                                            |                |                  |                |                                         |             |     |       |

| Legend:                                                    |                |                  |                |                                         |             |     |       |

| R = Readat                                                 | ole bit        | W = Writable     | bit            | U = Unimplemented bit, read as '0'      |             |     |       |

| -n = Value a                                               | at POR         | '1' = Bit is set |                | '0' = Bit is cleared x = Bit is unknown |             |     | nown  |

|                                                            |                |                  |                |                                         |             |     |       |

| bit 15-7                                                   | Unimplemen     | ted: Read as '   | 0'             |                                         |             |     |       |

| bit 6-4                                                    | PSEMIP<2:0     | PWM Special      | al Event Match | n Interrupt Prio                        | rity bits   |     |       |

| 111 = Interrupt is Priority 7 (highest priority interrupt) |                |                  |                |                                         |             |     |       |

|                                                            | •              |                  |                |                                         |             |     |       |

|                                                            | •              |                  |                |                                         |             |     |       |

|                                                            | •              |                  |                |                                         |             |     |       |

- 001 = Interrupt is Priority 1

- 000 = Interrupt source is disabled

bit 3-0 Unimplemented: Read as '0'

#### REGISTER 7-27: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| U-0     | U-0                       | U-0   | U-0   | U-0 | U-0 | U-0 | U-0   |

|---------|---------------------------|-------|-------|-----|-----|-----|-------|

| —       | —                         | —     | _     | —   | —   | —   | —     |

| bit 15  |                           |       |       |     |     |     | bit 8 |

|         |                           |       |       |     |     |     |       |

| U-0     | R/W-1                     | R/W-0 | R/W-0 | U-0 | U-0 | U-0 | U-0   |

| —       | U1EIP<2:0> <sup>(1)</sup> |       |       | —   | —   | —   | —     |

| bit 7   |                           |       |       |     |     | •   | bit 0 |

|         |                           |       |       |     |     |     |       |

| Legend: |                           |       |       |     |     |     |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                     |

|----------|----------------------------------------------------------------|

| bit 6-4  | U1EIP<2:0>: UART1 Error Interrupt Priority bits <sup>(1)</sup> |

|          | 111 = Interrupt is Priority 7 (highest priority interrupt)     |

|          | •                                                              |

|          | •                                                              |

|          | •                                                              |

|          | 001 = Interrupt is Priority 1                                  |

|          | 000 = Interrupt source is disabled                             |

| bit 3-0  | Unimplemented: Read as '0'                                     |

|          |                                                                |

**Note 1:** These bits are not implemented in the dsPIC33FJ06GS001 device.

#### 10.9 Peripheral Pin Select Registers

The following registers are implemented for remappable peripheral configuration:

- 15 Input Remappable Peripheral Registers

- 19 Output Remappable Peripheral Registers

- Note: Input and output register values can only be changed if IOLOCK (OSCCON<6>) = 0. See Section 10.6.3.1 "Control Register Lock" for a specific command sequence.

Not all Output Remappable Peripheral registers are implemented on all devices. See the register description of the specific register for further details.

#### REGISTER 10-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0    | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1  | R/W-1 | R/W-1 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | INT1  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

|        |     |       |       |       |        |       |       |

| U-0    | U-0 | U-0   | U-0   | U-0   | U-0    | U-0   | U-0   |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   |     | —   | —   | —   | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 INT1R<5:0>: Assign External Interrupt 1 (INTR1) to the Corresponding RPn Pin bits

bit 7-0

### REGISTER 10-16: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0                                | U-0          | R/W-0              | R/W-0          | R/W-0                              | R/W-0          | R/W-0  | R/W-0 |

|------------------------------------|--------------|--------------------|----------------|------------------------------------|----------------|--------|-------|

|                                    | —            |                    |                | RP1                                | R<5:0>         |        |       |

| bit 15                             |              |                    |                |                                    |                |        | bit 8 |

|                                    |              |                    |                |                                    |                |        |       |

| U-0                                | U-0          | R/W-0              | R/W-0          | R/W-0                              | R/W-0          | R/W-0  | R/W-0 |

| —                                  | —            |                    |                | RPO                                | R<5:0>         |        |       |

| bit 7                              |              |                    |                |                                    |                |        | bit 0 |

|                                    |              |                    |                |                                    |                |        |       |

| Legend:                            |              |                    |                |                                    |                |        |       |

| R = Readabl                        | e bit        | W = Writable       | bit            | U = Unimplemented bit, read as '0' |                |        |       |

| -n = Value at POR '1' = Bit is set |              | '0' = Bit is cle   | ared           | x = Bit is unkr                    | nown           |        |       |

|                                    |              |                    |                |                                    |                |        |       |

| bit 15-14                          | Unimpleme    | ented: Read as '   | 0'             |                                    |                |        |       |

| bit 13-8                           | RP1R<5:0>    | : Peripheral Out   | put Function   | is Assigned to F                   | RP1 Output Pir | n bits |       |

|                                    | (see Table ? | 10-2 for periphera | al function nu | umbers)                            |                |        |       |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP0R<5:0>:** Peripheral Output Function is Assigned to RP0 Output Pin bits (see Table 10-2 for peripheral function numbers)

#### REGISTER 10-17: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP3F  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP2F  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

- bit 13-8 **RP3R<5:0>:** Peripheral Output Function is Assigned to RP3 Output Pin bits (see Table 10-2 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP2R<5:0>:** Peripheral Output Function is Assigned to RP2 Output Pin bits (see Table 10-2 for peripheral function numbers)

| REGISTER 15-2: | PTCON2: PWM CLOCK DIVIDER SELECT REGISTER 2 |

|----------------|---------------------------------------------|

|----------------|---------------------------------------------|

| U-0                                | U-0      | U-0                                     | U-0                                                | U-0                                                                                                                             | U-0                                                                                                                            | U-0                                                                                                                                   |

|------------------------------------|----------|-----------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| —                                  | —        | —                                       | —                                                  | —                                                                                                                               | —                                                                                                                              | —                                                                                                                                     |

|                                    |          |                                         |                                                    |                                                                                                                                 |                                                                                                                                | bit 8                                                                                                                                 |

|                                    |          |                                         |                                                    |                                                                                                                                 |                                                                                                                                |                                                                                                                                       |

| U-0                                | U-0      | U-0                                     | U-0                                                | R/W-0                                                                                                                           | R/W-0                                                                                                                          | R/W-0                                                                                                                                 |

| _                                  | —        | _                                       | —                                                  | P                                                                                                                               | CLKDIV<2:0> <sup>(1</sup>                                                                                                      | 1)                                                                                                                                    |

|                                    |          |                                         |                                                    |                                                                                                                                 |                                                                                                                                | bit 0                                                                                                                                 |

|                                    |          |                                         |                                                    |                                                                                                                                 |                                                                                                                                |                                                                                                                                       |

|                                    |          |                                         |                                                    |                                                                                                                                 |                                                                                                                                |                                                                                                                                       |

| R = Readable bit W = Writable bit  |          |                                         | U = Unimplemented bit, read as '0'                 |                                                                                                                                 |                                                                                                                                |                                                                                                                                       |

| -n = Value at POR '1' = Bit is set |          | '0' = Bit is cleared x = Bit is unknown |                                                    |                                                                                                                                 | nown                                                                                                                           |                                                                                                                                       |

|                                    | U-0<br>— | U-0 U-0<br>— — —                        | U-0     U-0     U-0       wit     W = Writable bit | -     -     -     -       U-0     U-0     U-0     U-0       -     -     -     -       wit     W = Writable bit     U = Unimpler | U-0     U-0     U-0     U-0     R/W-0       —     —     —     —       bit     W = Writable bit     U = Unimplemented bit, read | U-0     U-0     U-0     U-0     R/W-0       -     -     -     -       wit     W = Writable bit     U = Unimplemented bit, read as '0' |

bit 15-3 Unimplemented: Read as '0'

- bit 2-0 PCLKDIV<2:0>: PWM Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

- 111 = Reserved

- 110 = Divide-by-64, maximum PWM timing resolution

- 101 = Divide-by-32, maximum PWM timing resolution

- 100 = Divide-by-16, maximum PWM timing resolution

- 011 = Divide-by-8, maximum PWM timing resolution

- 010 = Divide-by-4, maximum PWM timing resolution

- 001 = Divide-by-2, maximum PWM timing resolution

- 000 = Divide-by-1, maximum PWM timing resolution (power-on default)

- **Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

# REGISTER 15-3: PTPER: PWM MASTER TIME BASE REGISTER<sup>(1)</sup>

| R/W-1                             | R/W-1 | R/W-1            | R/W-1 | R/W-1                              | R/W-1 | R/W-1              | R/W-1 |

|-----------------------------------|-------|------------------|-------|------------------------------------|-------|--------------------|-------|

|                                   |       |                  | PTPE  | २ <15:8>                           |       |                    |       |

| bit 15                            |       |                  |       |                                    |       |                    | bit 8 |

| R/W-1                             | R/W-1 | R/W-1            | R/W-1 | R/W-1                              | R/W-0 | R/W-0              | R/W-0 |

|                                   |       |                  | PTPE  | R <7:0>                            |       |                    |       |

| bit 7                             |       |                  |       |                                    |       |                    | bit 0 |

| Legend:                           |       |                  |       |                                    |       |                    |       |

| R = Readable bit W = Writable bit |       |                  | bit   | U = Unimplemented bit, read as '0' |       |                    |       |

| -n = Value at POR '1' :           |       | '1' = Bit is set |       | '0' = Bit is cle                   | ared  | x = Bit is unknown |       |

bit 15-0 PTPER<15:0>: PWM Master Time Base (PMTMR) Period Value bits

Note 1: The minimum value that can be loaded into the PTPER register is 0x0010 and the maximum value is 0xFFF8.

### REGISTER 15-16: TRIGX: PWMx PRIMARY TRIGGER COMPARE VALUE REGISTER

| R/W-0                              | R/W-0 | R/W-0      | R/W-0            | R/W-0            | R/W-0           | R/W-0 | R/W-0 |

|------------------------------------|-------|------------|------------------|------------------|-----------------|-------|-------|

|                                    |       |            | TRGCI            | MP<15:8>         |                 |       |       |

| bit 15                             |       |            |                  |                  |                 |       | bit 8 |

|                                    |       |            |                  |                  |                 |       |       |

| R/W-0                              | R/W-0 | R/W-0      | R/W-0            | R/W-0            | U-0             | U-0   | U-0   |

|                                    | Т     | RGCMP<7:3> |                  |                  | —               | _     | —     |

| bit 7                              |       |            |                  |                  |                 |       | bit 0 |

|                                    |       |            |                  |                  |                 |       |       |

| Legend:                            |       |            |                  |                  |                 |       |       |

| R = Readable bit W = Writable bit  |       |            | U = Unimplei     | mented bit, read | 1 as '0'        |       |       |

| -n = Value at POR '1' = Bit is set |       |            | '0' = Bit is cle | eared            | x = Bit is unkr | nown  |       |

| bit 15-3 | TRGCMP<15:3>: Trigger Control Value bits                                                          |

|----------|---------------------------------------------------------------------------------------------------|

|          | When primary PWM functions in local time base, this register contains the compare values that can |

|          | trigger the ADC module.                                                                           |

| bit 2-0  | Unimplemented: Read as '0'                                                                        |

#### REGISTER 15-17: STRIGX: PWMx SECONDARY TRIGGER COMPARE VALUE REGISTER

| R/W-0            | R/W-0 | R/W-0          | R/W-0 | R/W-0        | R/W-0           | R/W-0    | R/W-0 |

|------------------|-------|----------------|-------|--------------|-----------------|----------|-------|

|                  |       |                | STRGC | MP<15:8>     |                 |          |       |

| bit 15           |       |                |       |              |                 |          | bit 8 |

|                  |       |                |       |              |                 |          |       |

| R/W-0            | R/W-0 | R/W-0          | R/W-0 | R/W-0        | U-0             | U-0      | U-0   |

|                  | ST    | rrgcmp<7:3>    |       |              | —               | —        | —     |

| bit 7            |       |                |       |              |                 |          | bit 0 |

|                  |       |                |       |              |                 |          |       |

| Legend:          |       |                |       |              |                 |          |       |

| R = Readable bit |       | W = Writable b | it    | U = Unimpler | mented bit read | l as '0' |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-3

STRGCMP<15:3>: Secondary Trigger Control Value bits

When secondary PWM functions in local time base, this register contains the compare values that can trigger the ADC module.

bit 2-0

Unimplemented: Read as '0'

# 17.0 INTER-INTEGRATED CIRCUIT™ (I<sup>2</sup>C™)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS001/101A/102A/ 202A and dsPIC33FJ09GS302 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 19. "Inter-Integrated Circuit (I<sup>2</sup>C™)" (DS70195) in the "dsPIC33F/ PIC24H Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Inter-Integrated Circuit<sup>TM</sup> ( $I^2C^{TM}$ ) module provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard with a 16-bit interface.

The I<sup>2</sup>C module has a 2-pin interface:

- The SCL1 pin is the clock

- The SDA1 pin is data

The I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both Master and Slave modes of operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation, detects bus collision and arbitrates accordingly

# 17.1 Operating Modes

The hardware fully implements all the master and slave functions of the  $I^2C$  Standard and Fast mode specifications, as well as 7-bit and 10-bit addressing.

The  $l^2C$  module can operate either as a slave or a master on an  $l^2C$  bus.

The following types of I<sup>2</sup>C operation are supported:

- I<sup>2</sup>C slave operation with 7-bit addressing

- I<sup>2</sup>C slave operation with 10-bit addressing

- I<sup>2</sup>C master operation with 7-bit or 10-bit addressing

For details about the communication sequence in each of these modes, please see the Microchip web site (www.microchip.com) for the latest *"dsPIC33F/PIC24H Family Reference Manual"* sections.

#### REGISTER 20-1: CMPCONx: COMPARATOR CONTROL x REGISTER (CONTINUED)

| bit 5   | EXTREF: Enable External Reference bit <sup>(1)</sup>                                                                                                                      |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = External source provides reference to DAC (maximum DAC voltage determined by external<br/>voltage source)</li> </ul>                                         |

|         | <ul> <li>Internal reference sources provide reference to DAC (maximum DAC voltage determined by<br/>RANGE bit setting)</li> </ul>                                         |

| bit 4   | HYSPOL: Comparator Hysteresis Polarity Select bit <sup>(1)</sup>                                                                                                          |

|         | <ul> <li>1 = Hysteresis is applied to the falling edge of the comparator output</li> <li>0 = Hysteresis is applied to the rising edge of the comparator output</li> </ul> |

| bit 3   | CMPSTAT: Current State of Comparator Output Including CMPPOL Selection bit <sup>(1)</sup>                                                                                 |

| bit 2   | HGAIN: DAC Gain Enable bit <sup>(1)</sup>                                                                                                                                 |

|         | <ul> <li>1 = Reference DAC output to comparator is scaled at 1.8x</li> <li>0 = Reference DAC output to comparator is scaled at 1.0x</li> </ul>                            |

| bit 1   | <b>CMPPOL:</b> Comparator Output Polarity Control bit <sup>(1)</sup>                                                                                                      |

|         | <ul><li>1 = Output is inverted</li><li>0 = Output is non-inverted</li></ul>                                                                                               |

| bit 0   | <b>RANGE:</b> Selects DAC Output Voltage Range bit <sup>(1)</sup>                                                                                                         |

|         | 1 = High Range: Max DAC Value = AVDD/2, 1.65V at 3.3V AVDD<br>0 = Low Range: Max DAC Value = INTREF <sup>(3)</sup>                                                        |

| Note 1: | This bit is not implemented in dsPIC33FJ06GS101A/102A devices.                                                                                                            |

- 2: DACOUT can be associated only with a single comparator at any given time. The software must ensure that multiple comparators do not enable the DAC output by setting their respective DACOE bit.

- **3:** For the INTREF value, refer to the DAC Module Specifications (Table 25-42) in **Section 25.0 "Electrical Characteristics"**.

# 21.0 CONSTANT CURRENT SOURCE

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS001/101A/102A/ 202A and dsPIC33FJ09GS302 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 19. "Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)" (DS70195) in the "dsPIC33F/PIC24H Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

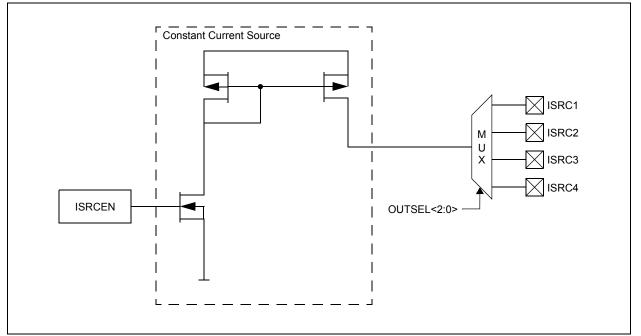

The constant current source module is a precision current generator and is used in conjunction with ADC to measure the resistance of external resistors connected to device pins.

## 21.1 Features Overview

The constant current source module offers the following major features:

- Constant current generator (10 µA nominal)

- Internal selectable connection to one out of four pins

- Enable/disable bit

# 21.2 Module Description

Figure 21-1 shows a functional block diagram of the constant current source module. It consists of a precision current generator with a nominal value of 10  $\mu$ A. The module can be enabled and disabled using the ISRCEN bit in the ISRCCON register. The output of the current generator is internally connected to one out of up to 4 pins. The OUTSEL<2:0> bits in the ISRCCON register allow selection of the target pin.

The current source is calibrated during testing.

#### FIGURE 21-1: CONSTANT CURRENT SOURCE MODULE BLOCK DIAGRAM

# 27.0 PACKAGING INFORMATION

### 27.1 Package Marking Information

#### 18-Lead PDIP

#### 18-Lead SOIC (.300")

#### 20-Lead SSOP

#### Example

#### Example

#### Example

| Legend | : XXX      | Customer-specific information                                                                                                                                     |

|--------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | Y          | Year code (last digit of calendar year)                                                                                                                           |

|        | ΥY         | Year code (last 2 digits of calendar year)                                                                                                                        |

|        | WW         | Week code (week of January 1 is week '01')                                                                                                                        |

|        | NNN        | Alphanumeric traceability code                                                                                                                                    |

|        | <b>e</b> 3 | Pb-free JEDEC designator for Matte Tin (Sn)                                                                                                                       |

|        | *          | This package is Pb-free. The Pb-free JEDEC designator ((e3))                                                                                                      |

|        |            | can be found on the outer packaging for this package.                                                                                                             |

| Note:  |            | Aicrochip part number cannot be marked on one line, it is carried over to the next limiting the number of available characters for customer-specific information. |

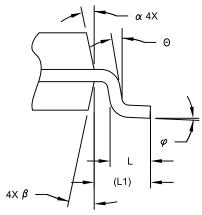

## 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

VIEW C

|                          | MILLIMETERS |           |           |      |  |  |  |

|--------------------------|-------------|-----------|-----------|------|--|--|--|

| Dimension                | Limits      | MIN       | NOM       | MAX  |  |  |  |

| Number of Pins           | Ν           |           | 28        |      |  |  |  |

| Pitch                    | е           |           | 1.27 BSC  |      |  |  |  |

| Overall Height           | А           | -         | -         | 2.65 |  |  |  |

| Molded Package Thickness | A2          | 2.05      | -         | -    |  |  |  |

| Standoff §               | A1          | 0.10      | -         | 0.30 |  |  |  |

| Overall Width            | E           |           | 10.30 BSC |      |  |  |  |

| Molded Package Width     | E1          | 7.50 BSC  |           |      |  |  |  |

| Overall Length           | D           | 17.90 BSC |           |      |  |  |  |

| Chamfer (Optional)       | h           | 0.25      | -         | 0.75 |  |  |  |

| Foot Length              | L           | 0.40      | -         | 1.27 |  |  |  |

| Footprint                | L1          |           | 1.40 REF  |      |  |  |  |

| Lead Angle               | Θ           | 0°        | -         | -    |  |  |  |

| Foot Angle               | φ           | 0°        | -         | 8°   |  |  |  |

| Lead Thickness           | С           | 0.18      | -         | 0.33 |  |  |  |

| Lead Width               | b           | 0.31      | -         | 0.51 |  |  |  |

| Mold Draft Angle Top     | α           | 5°        | -         | 15°  |  |  |  |

| Mold Draft Angle Bottom  | β           | 5°        | -         | 15°  |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing C04-052C Sheet 2 of 2