Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 9КВ (3К х 24)                                                                   |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 8x10b; D/A 2x10b                                                            |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj09gs302-e-mm |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

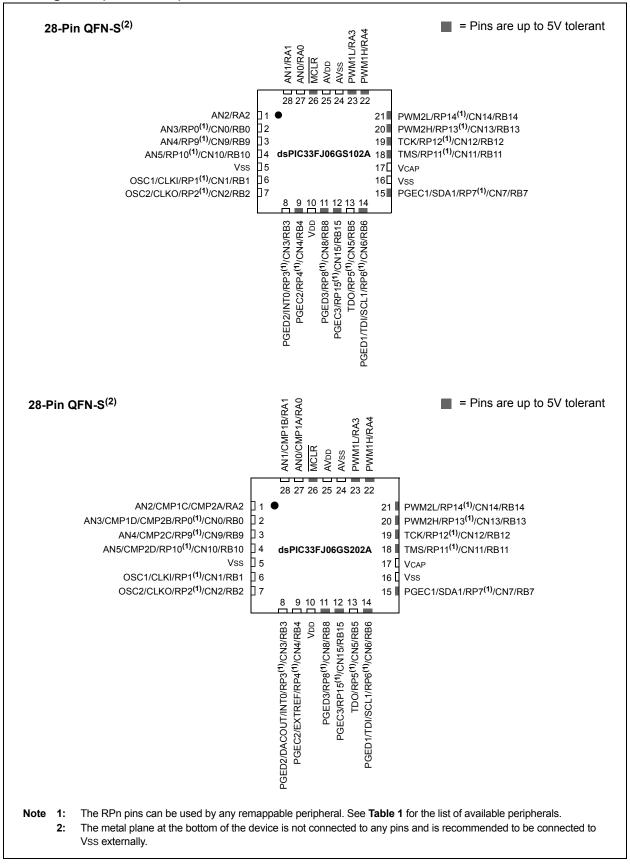

# Pin Diagrams (Continued)

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

# Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

## Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPlC33F/PlC24H Family Reference Manual"*. These documents should be considered the primary reference for the operation of a particular module or device feature.

| Note: | To access the documents listed below, |        |           |     |      |  |  |  |  |

|-------|---------------------------------------|--------|-----------|-----|------|--|--|--|--|

|       | visit                                 | the    | Microchip | web | site |  |  |  |  |

|       | (www.                                 | microc | hip.com). |     |      |  |  |  |  |

- Section 1. "Introduction" (DS70197)

- Section 2. "CPU" (DS70204)

- Section 3. "Data Memory" (DS70202)

- Section 4. "Program Memory" (DS70203)

- Section 5. "Flash Programming" (DS70191)

- Section 8. "Reset" (DS70192)

- Section 9. "Watchdog Timer (WDT) and Power-Saving Modes" (DS70196)

- Section 10. "I/O Ports" (DS70193)

- Section 11. "Timers" (DS70205)

- Section 12. "Input Capture" (DS70198)

- Section 13. "Output Compare" (DS70209)

- Section 17. "UART" (DS70188)

- Section 18. "Serial Peripheral Interface (SPI)" (DS70206)

- Section 19. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70195)

- Section 24. "Programming and Diagnostics" (DS70207)

- Section 25. "Device Configuration" (DS70194)

- Section 41. "Interrupts (Part IV)" (DS70300)

- Section 42. "Oscillator (Part IV)" (DS70307)

- Section 43. "High-Speed PWM" (DS70323)

- Section 44. "High-Speed 10-Bit ADC" (DS70321)

- Section 45. "High-Speed Analog Comparator" (DS70296)

| Pin Name             | Pin<br>Type | Buffer<br>Type             | PPS<br>Capable | Description                                                                                                                     |  |  |  |  |

|----------------------|-------------|----------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| CMP1A                | I           | Analog                     | No             | Comparator 1 Channel A.                                                                                                         |  |  |  |  |

| CMP1B                | 1           | Analog                     | No             | Comparator 1 Channel B.                                                                                                         |  |  |  |  |

| CMP1C                | 1           | Analog                     | No             | Comparator 1 Channel C.                                                                                                         |  |  |  |  |

| CMP1D                | 1           | Analog                     | No             | Comparator 1 Channel D.                                                                                                         |  |  |  |  |

| CMP2A                | 1           | Analog                     | No             | Comparator 2 Channel A.                                                                                                         |  |  |  |  |

| CMP2B                | I           | Analog                     | No             | Comparator 2 Channel B.                                                                                                         |  |  |  |  |

| CMP2C                | I           | Analog                     | No             | Comparator 2 Channel C.                                                                                                         |  |  |  |  |

| CMP2D                | I           | Analog                     | No             | Comparator 2 Channel D.                                                                                                         |  |  |  |  |

| DACOUT               | 0           | _                          | No             | DAC output voltage.                                                                                                             |  |  |  |  |

| ACMP1-ACMP2          | 0           | —                          | Yes            | DAC trigger to PWM module.                                                                                                      |  |  |  |  |

| ISRC1 <sup>(2)</sup> | 0           | _                          | No             | Constant Current Source Output 1.                                                                                               |  |  |  |  |

| ISRC2 <sup>(2)</sup> | 0           | —                          | No             | Constant Current Source Output 2.                                                                                               |  |  |  |  |

| ISRC3 <sup>(2)</sup> | 0           | —                          | No             | Constant Current Source Output 3.                                                                                               |  |  |  |  |

| ISRC4 <sup>(2)</sup> | 0           | _                          | No             | Constant Current Source Output 4.                                                                                               |  |  |  |  |

| EXTREF               | I           | Analog                     | No             | External voltage reference input for the reference DACs.                                                                        |  |  |  |  |

| REFCLKO              | 0           | _                          | Yes            | REFCLKO output signal is a postscaled derivative of the system clock.                                                           |  |  |  |  |

| FLT1-FLT8            | I           | ST                         | Yes            | Fault inputs to PWM module.                                                                                                     |  |  |  |  |

| SYNCI1-SYNCI2        | I           | ST                         | Yes            | External synchronization signal to PWM master time base.                                                                        |  |  |  |  |

| SYNCO1               | 0           | _                          | Yes            | PWM master time base for external device synchronization.                                                                       |  |  |  |  |

| PWM1L                | 0           | _                          | No             | PWM1 low output.                                                                                                                |  |  |  |  |

| PWM1H                | 0           | _                          | No             | PWM1 high output.                                                                                                               |  |  |  |  |

| PWM2L                | 0           | _                          | No             | PWM2 low output.                                                                                                                |  |  |  |  |

| PWM2H                | 0           | —                          | No             | PWM2 high output.                                                                                                               |  |  |  |  |

| PWM4L                | 0           | —                          | Yes            | PWM4 low output.                                                                                                                |  |  |  |  |

| PWM4H                | 0           | —                          | Yes            | PWM4 high output.                                                                                                               |  |  |  |  |

| PGED1                | I/O         | ST                         | No             | Data I/O pin for programming/debugging Communication Channel 1                                                                  |  |  |  |  |

| PGEC1                | I           | ST                         | No             | Clock input pin for programming/debugging Communication Channel 1.                                                              |  |  |  |  |

| PGED2                | I/O         | ST                         | No             | Data I/O pin for programming/debugging Communication Channel 2                                                                  |  |  |  |  |

| PGEC2                | I           | ST                         | No             | Clock input pin for programming/debugging Communication                                                                         |  |  |  |  |

|                      |             |                            |                | Channel 2.                                                                                                                      |  |  |  |  |

| PGED3 <sup>(1)</sup> | I/O         | ST                         | No             | Data I/O pin for programming/debugging Communication Channel 3                                                                  |  |  |  |  |

| PGEC3 <sup>(1)</sup> | I           | ST                         | No             | Clock input pin for programming/debugging Communication<br>Channel 3.                                                           |  |  |  |  |

| MCLR                 | I/P         | ST                         | No             | Master Clear (Reset) input. This pin is an active-low Reset to the device.                                                      |  |  |  |  |

| AVDD                 | Р           | Р                          | No             | Positive supply for analog modules. This pin must be connected at all times. AVDD is connected to VDD on 18 and 28-pin devices. |  |  |  |  |

| AVSS                 | Р           | Р                          | No             | Ground reference for analog modules. AVss is connected to Vss on 18 and 28-pin devices.                                         |  |  |  |  |

| VDD                  | Р           | _                          | No             | Positive supply for peripheral logic and I/O pins.                                                                              |  |  |  |  |

| VCAP                 | Р           |                            | No             | CPU logic filter capacitor connection.                                                                                          |  |  |  |  |

| Vss                  | P           |                            | No             | Ground reference for logic and I/O pins.                                                                                        |  |  |  |  |

| Legend: CMOS         |             | compatible<br>gger input v | input or o     | utput Analog = Analog input I = Input                                                                                           |  |  |  |  |

#### TABLE 1-1. PINOLIT I/O DESCRIPTIONS (CONTINUED)

TTL = Transistor-Transistor Logic

PPS = Peripheral Pin Select — = Does not apply

Note 1: Not all pins are available on all devices. Refer to the specific device in the "Pin Diagrams" section for availability.

2: This pin is available on dsPIC33FJ09GS302 devices only.

NOTES:

# 3.4 CPU Control Registers

| R-0                  | R-0                                                                    | R/C-0                                  | R/C-0             | R-0                    | R/C-0                | R -0             | R/W-0         |  |

|----------------------|------------------------------------------------------------------------|----------------------------------------|-------------------|------------------------|----------------------|------------------|---------------|--|

| OA                   | OB                                                                     | SA <sup>(1)</sup>                      | SB <sup>(1)</sup> | OAB                    | SAB <sup>(1,4)</sup> | DA               | DC            |  |

| bit 15               |                                                                        |                                        |                   |                        | •                    |                  | bit 8         |  |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup>                                                   | R/W-0 <sup>(3)</sup>                   | R-0               | R/W-0                  | R/W-0                | R/W-0            | R/W-0         |  |

|                      | IPL<2:0> <sup>(2)</sup>                                                |                                        | RA                | N                      | OV                   | Z                | С             |  |

| bit 7                |                                                                        |                                        |                   |                        |                      |                  | bit (         |  |

| Legend:              |                                                                        |                                        |                   |                        |                      |                  |               |  |

| C = Clearab          | le bit                                                                 | R = Readable                           | e bit             | U = Unimple            | mented bit, read     | as '0'           |               |  |

| S = Settable         | bit                                                                    | W = Writable                           | bit               | -n = Value at          | POR                  |                  |               |  |

| '1' = Bit is se      | et                                                                     | '0' = Bit is clea                      | ared              | x = Bit is unk         | nown                 |                  |               |  |

| bit 15               | OA: Accumul                                                            | lator A Overflow                       | v Status bit      |                        |                      |                  |               |  |

|                      |                                                                        | ator A overflowe                       |                   |                        |                      |                  |               |  |

| 1.1.4.4              |                                                                        | ator A has not c                       |                   |                        |                      |                  |               |  |

| bit 14               |                                                                        | lator B Overflow<br>ator B overflowe   |                   |                        |                      |                  |               |  |

|                      |                                                                        | ator B has not c                       |                   |                        |                      |                  |               |  |

| bit 13               | <b>SA:</b> Accumulator A Saturation 'Sticky' Status bit <sup>(1)</sup> |                                        |                   |                        |                      |                  |               |  |

|                      | 1 = Accumula                                                           | ator A is saturat<br>ator A is not sat | ed or has bee     |                        | some time            |                  |               |  |

| bit 12               | SB: Accumul                                                            | ator B Saturatio                       | on 'Sticky' Sta   | tus bit <sup>(1)</sup> |                      |                  |               |  |

|                      |                                                                        | ator B is saturat<br>ator B is not sat |                   | en saturated at        | some time            |                  |               |  |

| bit 11               | <b>0AB:</b> 0A    0                                                    | DB Combined A                          | ccumulator O      | verflow Status         | bit                  |                  |               |  |

|                      | 1 = Accumula                                                           | ators A or B hav                       | ve overflowed     |                        |                      |                  |               |  |

| bit 10               | <b>SAB:</b> SA    S                                                    | B Combined A                           | ccumulator 'St    | icky' Status bit       | (1,4)                |                  |               |  |

|                      | 1 = Accumula                                                           |                                        | saturated or      | have been sat          | urated at some t     | time in the past | t             |  |

| bit 9                | DA: DO Loop                                                            | Active bit                             |                   |                        |                      |                  |               |  |

|                      | 1 = DO <b>loop ir</b>                                                  |                                        |                   |                        |                      |                  |               |  |

|                      | -                                                                      | ot in progress                         |                   |                        |                      |                  |               |  |

| bit 8                |                                                                        | U Half Carry/B                         |                   |                        |                      |                  |               |  |

|                      | of the res                                                             | sult occurred                          |                   | -                      | data) or 8th low-o   |                  |               |  |

|                      | •                                                                      | -out from the 4<br>the result occur    |                   | bit (for byte-siz      | ed data) or 8th      | low-order bit (1 | for word-size |  |

| Note 1: ⊤            | his bit can be rea                                                     | ad or cleared (n                       | ot set).          |                        |                      |                  |               |  |

| L                    | he IPL<2:0> bits<br>evel (IPL). The v<br>PL3 = 1.                      |                                        |                   |                        |                      |                  |               |  |

|                      |                                                                        |                                        |                   |                        |                      |                  |               |  |

#### REGISTER 3-1: SR: CPU STATUS REGISTER

**3:** The IPL<2:0> Status bits are read-only when NSTDIS = 1 (INTCON1<15>).

**4:** Clearing this bit will clear SA and SB.

# 3.6.3.2 Data Space Write Saturation

In addition to adder/subtracter saturation, writes to data space can also be saturated, but without affecting the contents of the source accumulator. The data space write saturation logic block accepts a 16-bit, 1.15 fractional value from the round logic block as its input, together with overflow status from the original source (accumulator) and the 16-bit round adder. These inputs are combined and used to select the appropriate 1.15 fractional value as output to write to data space memory.

If the SATDW bit in the CORCON register is set, data (after rounding or truncation) is tested for overflow and adjusted accordingly:

- For input data greater than 0x007FFF, data written to memory is forced to the maximum positive 1.15 value, 0x7FFF

- For input data less than 0xFF8000, data written to memory is forced to the maximum negative 1.15 value, 0x8000

The Most Significant bit of the source (bit 39) is used to determine the sign of the operand being tested.

If the SATDW bit in the CORCON register is not set, the input data is always passed through unmodified under all conditions.

# 3.6.4 BARREL SHIFTER

The barrel shifter can perform up to 16-bit arithmetic or logic right shifts, or up to 16-bit left shifts in a single cycle. The source can be either of the two DSP accumulators or the X bus (to support multi-bit shifts of register or memory data).

The shifter requires a signed binary value to determine both the magnitude (number of bits) and direction of the shift operation. A positive value shifts the operand right. A negative value shifts the operand left. A value of '0' does not modify the operand.

The barrel shifter is 40 bits wide, thereby obtaining a 40-bit result for DSP shift operations and a 16-bit result for MCU shift operations. Data from the X bus is presented to the barrel shifter between bit positions 16 and 31 for right shifts, and between bit positions 0 and 15 for left shifts.

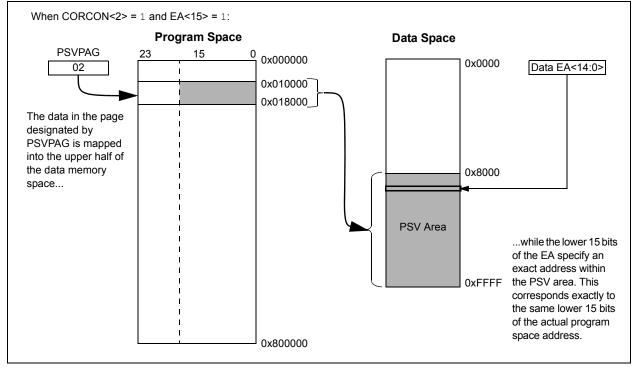

#### 4.7.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word page of the program space. This option provides transparent access to stored constant data from the data space without the need to use special instructions (such as TBLRDL or TBLRDH).

Program space access through the data space occurs if the Most Significant bit of the data space EA is '1' and program space visibility is enabled by setting the PSV bit in the Core Control register (CORCON<2>). The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits. By incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads to this area add a cycle to the instruction being executed, since two program memory fetches are required. Although each data space address 0x8000 and higher maps directly into a corresponding program memory address (see Figure 4-10), only the lower 16 bits of the 24-bit program word are used to contain the data. The upper 8 bits of any program space location used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

Note: PSV access is temporarily disabled during table reads/writes.

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV. D instructions require one instruction cycle in addition to the specified execution time. All other instructions require two instruction cycles in addition to the specified execution time.

For operations that use PSV, and are executed inside a REPEAT loop, these instances require two instruction cycles in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction using PSV to access data, to execute in a single cycle.

# FIGURE 4-10: PROGRAM SPACE VISIBILITY OPERATION

# 6.1 Reset Control Register

| REGISTE    | R 6-1: RCON                               | I: RESET COI                         | NTROL REG     | SISTER <sup>(1)</sup> |                   |                  |               |

|------------|-------------------------------------------|--------------------------------------|---------------|-----------------------|-------------------|------------------|---------------|

| R/W-0      |                                           | U-0                                  | U-0           | U-0                   | U-0               | R/W-0            | R/W-0         |

| TRAPF      | R IOPUWR                                  |                                      | —             |                       |                   | СМ               | VREGS         |

| bit 15     |                                           |                                      |               |                       |                   |                  | bit 8         |

|            |                                           | DAALO                                | DANO          | DAMO                  |                   |                  |               |

| R/W-0      |                                           |                                      | R/W-0         | R/W-0                 | R/W-0             | R/W-1            | R/W-1         |

| EXTR       | SWR                                       | SWDTEN <sup>(2)</sup>                | WDTO          | SLEEP                 | IDLE              | BOR              | POR           |

| bit 7      |                                           |                                      |               |                       |                   |                  | bit 0         |

| Legend:    |                                           |                                      |               |                       |                   |                  |               |

| R = Reada  | able bit                                  | W = Writable                         | oit           | U = Unimpler          | mented bit, read  | d as '0'         |               |

| -n = Value | at POR                                    | '1' = Bit is set                     |               | '0' = Bit is cle      | ared              | x = Bit is unki  | nown          |

|            |                                           |                                      |               |                       |                   |                  |               |

| bit 15     | •                                         | Reset Flag bit                       |               |                       |                   |                  |               |

|            |                                           | onflict Reset ha<br>onflict Reset ha |               | d                     |                   |                  |               |

| bit 14     | •                                         | egal Opcode or                       |               |                       | et Flag bit       |                  |               |

|            |                                           | al opcode deter                      |               |                       | •                 | lized W registe  | er used as ar |

|            |                                           | Pointer caused                       |               |                       |                   |                  |               |

| 1.1.40.40  | -                                         | l opcode or unii                     |               | leset has not o       | ccurred           |                  |               |

| bit 13-10  | -                                         | ted: Read as '                       |               |                       |                   |                  |               |

| bit 9      | -                                         | ration Mismatch                      | -             | a a a una d           |                   |                  |               |

|            | •                                         | uration Mismatc<br>uration Mismatc   |               |                       |                   |                  |               |

| bit 8      | •                                         | age Regulator S                      |               |                       |                   |                  |               |

|            |                                           | egulator is activ                    | •             | •                     |                   |                  |               |

|            |                                           | egulator goes ir                     |               |                       | ер                |                  |               |

| bit 7      |                                           | nal Reset Pin (N                     | ,             |                       |                   |                  |               |

|            |                                           | Clear (pin) Res<br>Clear (pin) Res   |               |                       |                   |                  |               |

| bit 6      |                                           | are Reset Flag (                     |               |                       |                   |                  |               |

| DILO       |                                           | instruction has                      |               |                       |                   |                  |               |

|            |                                           | instruction has                      |               |                       |                   |                  |               |

| bit 5      | SWDTEN: So                                | oftware Enable/                      | Disable of W  | DT bit <sup>(2)</sup> |                   |                  |               |

|            | 1 = WDT is e<br>0 = WDT is d              |                                      |               |                       |                   |                  |               |

| bit 4      |                                           | hdog Timer Tim                       | e-out Flag bi | t                     |                   |                  |               |

| Dit 4      |                                           | e-out has occur                      | -             | L                     |                   |                  |               |

|            |                                           | e-out has not or                     |               |                       |                   |                  |               |

| bit 3      | SLEEP: Wak                                | e-up from Slee                       | o Flag bit    |                       |                   |                  |               |

|            |                                           | as been in Slee                      |               |                       |                   |                  |               |

|            |                                           | as not been in S                     | •             |                       |                   |                  |               |

| bit 2      |                                           | up from Idle Fla                     | -             |                       |                   |                  |               |

|            |                                           | as in Idle mode<br>as not in Idle m  |               |                       |                   |                  |               |

| Note 1:    | All of the Reset sta<br>cause a device Re |                                      | set or cleare | d in software. S      | Setting one of th | ese bits in soft | ware does not |

| 2:         | If the FWDTEN Co                          |                                      | a (1) (       |                       |                   |                  |               |

####

# 6.10 Using the RCON Status Bits

The user application can read the Reset Control (RCON) register after any device Reset to determine the cause of the Reset.

| Note: | The status bits in the RCON register       |

|-------|--------------------------------------------|

|       | should be cleared after they are read so   |

|       | that the next RCON register value, after a |

|       | device Reset, will be meaningful.          |

## TABLE 6-3: RESET FLAG BIT OPERATION

Flag Bit Set by: Cleared by: TRAPR (RCON<15>) Trap conflict event POR, BOR IOPWR (RCON<14>) POR, BOR Illegal opcode or uninitialized W register access or Security Reset CM (RCON<9>) **Configuration Mismatch** POR, BOR EXTR (RCON<7>) MCLR Reset POR SWR (RCON<6>) RESET instruction POR, BOR WDTO (RCON<4>) WDT time-out PWRSAV instruction, CLRWDT instruction, POR, BOR SLEEP (RCON<3>) PWRSAV #SLEEP instruction POR, BOR POR, BOR IDLE (RCON<2>) PWRSAV #IDLE instruction BOR (RCON<1>) POR, BOR POR (RCON<0>) POR

Note: All Reset flag bits can be set or cleared by user software.

Table 6-3 provides a summary of the Reset flag bit operation.

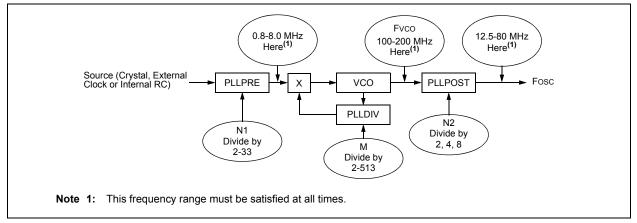

# 8.1.3 PLL CONFIGURATION

The primary oscillator and internal FRC oscillator can optionally use an on-chip PLL to obtain higher speeds of operation. The PLL provides significant flexibility in selecting the device operating speed. A block diagram of the PLL is shown in Figure 8-2.

The output of the primary oscillator or FRC, denoted as 'FIN', is divided down by a prescale factor (N1) of 2, 3, ... or 33 before being provided to the PLL's Voltage Controlled Oscillator (VCO). The input to the VCO must be selected in the range of 0.8 MHz to 8 MHz. The prescale factor, 'N1', is selected using the PLLPRE<4:0> bits (CLKDIV<4:0>).

The PLL Feedback Divisor, selected using the PLLDIV<8:0> bits (PLLFBD<8:0>), provides a factor, 'M', by which the input to the VCO is multiplied. This factor must be selected such that the resulting VCO output frequency is in the range of 100 MHz to 200 MHz.

The VCO output is further divided by a postscale factor, 'N2'. This factor is selected using the PLLPOST<1:0> bits (CLKDIV<7:6>). 'N2' can be either 2, 4, or 8, and must be selected such that the PLL output frequency (Fosc) is in the range of 12.5 MHz to 80 MHz, which generates device operating speeds of 6.25-40 MIPS.

For a primary oscillator or FRC oscillator, output 'FIN', the PLL output 'FOSC', is given by Equation 8-2.

# EQUATION 8-2: Fosc CALCULATION

$$FOSC = FIN * \left(\frac{M}{N1 * N2}\right)$$

For example, suppose a 10 MHz crystal is being used with the selected oscillator mode of XT with PLL (see Equation 8-3).

- If PLLPRE<4:0> = 0, then N1 = 2. This yields a VCO input of 10/2 = 5 MHz, which is within the acceptable range of 0.8-8 MHz.

- If PLLDIV<8:0> = 0x1E, then M = 32. This yields a VCO output of 5 x 32 = 160 MHz, which is within the 100-200 MHz ranged needed.

• If PLLPOST<1:0> = 00, then N2 = 2. This provides a Fosc of 160/2 = 80 MHz. The resultant device operating speed is 80/2 = 40 MIPS.

## EQUATION 8-3: XT WITH PLL MODE EXAMPLE

$$F_{CY} = \frac{F_{OSC}}{2} = \frac{1}{2} \left( \frac{10000000 * 32}{2 * 2} \right) = 40 \text{ MIPS}$$

# 8.2 Auxiliary Clock Generation

The auxiliary clock generation is used for a peripherals that need to operate at a frequency unrelated to the system clock, such as a PWM or ADC.

The primary oscillator and internal FRC oscillator sources can be used with an auxiliary PLL to obtain the auxiliary clock. The auxiliary PLL has a fixed 16x multiplication factor.

The auxiliary clock has the following configuration restrictions:

- For proper PWM operation, auxiliary clock generation must be configured for 120 MHz (see Parameter OS56 in Table 25-18 in Section 25.0 "Electrical Characteristics"). If a slower frequency is desired, the PWM Input Clock Prescaler (Divider) Select bits (PCLKDIV<2:0>) should be used.

- To achieve 1.04 ns PWM resolution, the auxiliary clock must use the 16x auxiliary PLL (APLL). All other clock sources will have a minimum PWM resolution of 8 ns.

- If the primary PLL is used as a source for the auxiliary clock, the primary PLL should be configured up to a maximum operation of 30 MIPS or less

# 8.3 Reference Clock Generation

The reference clock output logic provides the user with the ability to output a clock signal based on the system clock or the crystal oscillator on a device pin. The user application can specify a wide range of clock scaling prior to outputting the reference clock.

# FIGURE 8-2: dsPIC33FJ06GS001/101A/102A/202A and dsPIC33FJ09GS302 PLL BLOCK DIAGRAM

# 13.1 Input Capture Registers

| U-0                  | U-0                         | R/W-0                                 | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | U-0              | U-0             | U-0                | U-0           |

|----------------------|-----------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|--------------------|---------------|

|                      | —                           | ICSIDL                                | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | —                | _               | —                  | _             |

| bit 15               |                             |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                 |                    | bit 8         |

| R/W-0                | R/W-0                       | R/W-0                                 | R-0, HC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R-0, HC          | R/W-0           | R/W-0              | R/W-0         |

| ICTMR <sup>(1)</sup> |                             | <1:0>                                 | ICOV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ICBNE            | 10,00-0         | ICM<2:0>           | 10/00-0       |

| bit 7                |                             | \$1.02                                | 1007                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IODINE           |                 | 10101-2.02         | bit           |

|                      |                             |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                 |                    |               |

| Legend:              |                             | HC = Hardwar                          | e Clearable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                 |                    |               |

| R = Readat           | ole bit                     | W = Writable b                        | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | U = Unimple      | mented bit, re  | ead as '0'         |               |

| -n = Value a         | at POR                      | '1' = Bit is set                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | '0' = Bit is cle | eared           | x = Bit is unkn    | iown          |

| bit 15-14            | Unimplemer                  | ited: Read as '0                      | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |                 |                    |               |

| bit 13               | -                           | t Capture Modu                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Control bit      |                 |                    |               |

|                      | •                           | ture module hal                       | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |                 |                    |               |

|                      | 0 = Input cap               | ture module cor                       | ntinues to opera                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ate in CPU Idle  | mode            |                    |               |

| bit 12-8             | Unimplemer                  | ted: Read as '0                       | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |                 |                    |               |

| bit 7                | ICTMR: Inpu                 | t Capture Timer                       | Select bit <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  |                 |                    |               |

|                      | 1 = TMR2 co<br>0 = Reserved | ntents are captu<br>I                 | ired on capture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | e event          |                 |                    |               |