Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 9KB (3K x 24)                                                                   |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 8x10b; D/A 2x10b                                                            |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-UQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-UQFN (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj09gs302-e-mx |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

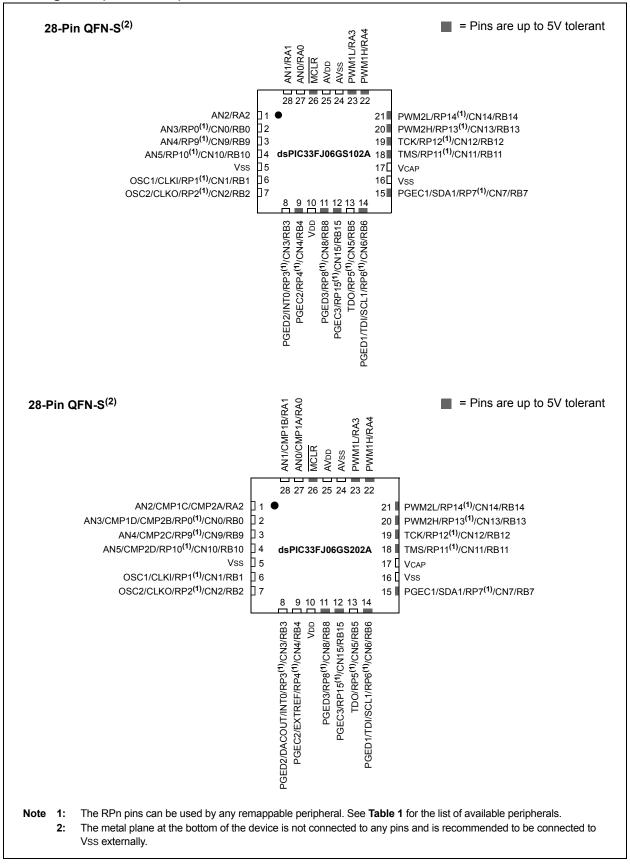

## Pin Diagrams (Continued)

| Pin Name             | Pin<br>Type | Buffer<br>Type             | PPS<br>Capable | Description                                                                                                                     |

|----------------------|-------------|----------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------|

| CMP1A                | I           | Analog                     | No             | Comparator 1 Channel A.                                                                                                         |

| CMP1B                | 1           | Analog                     | No             | Comparator 1 Channel B.                                                                                                         |

| CMP1C                | 1           | Analog                     | No             | Comparator 1 Channel C.                                                                                                         |

| CMP1D                | 1           | Analog                     | No             | Comparator 1 Channel D.                                                                                                         |

| CMP2A                | 1           | Analog                     | No             | Comparator 2 Channel A.                                                                                                         |

| CMP2B                | I           | Analog                     | No             | Comparator 2 Channel B.                                                                                                         |

| CMP2C                | I           | Analog                     | No             | Comparator 2 Channel C.                                                                                                         |

| CMP2D                | I           | Analog                     | No             | Comparator 2 Channel D.                                                                                                         |

| DACOUT               | 0           | _                          | No             | DAC output voltage.                                                                                                             |

| ACMP1-ACMP2          | 0           | —                          | Yes            | DAC trigger to PWM module.                                                                                                      |

| ISRC1 <sup>(2)</sup> | 0           | _                          | No             | Constant Current Source Output 1.                                                                                               |

| ISRC2 <sup>(2)</sup> | 0           | —                          | No             | Constant Current Source Output 2.                                                                                               |

| ISRC3 <sup>(2)</sup> | 0           | —                          | No             | Constant Current Source Output 3.                                                                                               |

| ISRC4 <sup>(2)</sup> | 0           | _                          | No             | Constant Current Source Output 4.                                                                                               |

| EXTREF               | I           | Analog                     | No             | External voltage reference input for the reference DACs.                                                                        |

| REFCLKO              | 0           | _                          | Yes            | REFCLKO output signal is a postscaled derivative of the system clock.                                                           |

| FLT1-FLT8            | I           | ST                         | Yes            | Fault inputs to PWM module.                                                                                                     |

| SYNCI1-SYNCI2        | I           | ST                         | Yes            | External synchronization signal to PWM master time base.                                                                        |

| SYNCO1               | 0           | _                          | Yes            | PWM master time base for external device synchronization.                                                                       |

| PWM1L                | 0           | _                          | No             | PWM1 low output.                                                                                                                |

| PWM1H                | 0           | _                          | No             | PWM1 high output.                                                                                                               |

| PWM2L                | 0           | _                          | No             | PWM2 low output.                                                                                                                |

| PWM2H                | 0           | —                          | No             | PWM2 high output.                                                                                                               |

| PWM4L                | 0           | —                          | Yes            | PWM4 low output.                                                                                                                |

| PWM4H                | 0           | —                          | Yes            | PWM4 high output.                                                                                                               |

| PGED1                | I/O         | ST                         | No             | Data I/O pin for programming/debugging Communication Channel 1                                                                  |

| PGEC1                | I           | ST                         | No             | Clock input pin for programming/debugging Communication Channel 1.                                                              |

| PGED2                | I/O         | ST                         | No             | Data I/O pin for programming/debugging Communication Channel 2                                                                  |

| PGEC2                | I           | ST                         | No             | Clock input pin for programming/debugging Communication                                                                         |

|                      |             |                            |                | Channel 2.                                                                                                                      |

| PGED3 <sup>(1)</sup> | I/O         | ST                         | No             | Data I/O pin for programming/debugging Communication Channel 3                                                                  |

| PGEC3 <sup>(1)</sup> | I           | ST                         | No             | Clock input pin for programming/debugging Communication<br>Channel 3.                                                           |

| MCLR                 | I/P         | ST                         | No             | Master Clear (Reset) input. This pin is an active-low Reset to the device.                                                      |

| AVDD                 | Р           | Р                          | No             | Positive supply for analog modules. This pin must be connected at all times. AVDD is connected to VDD on 18 and 28-pin devices. |

| AVSS                 | Р           | Р                          | No             | Ground reference for analog modules. AVss is connected to Vss on 18 and 28-pin devices.                                         |

| VDD                  | Р           | _                          | No             | Positive supply for peripheral logic and I/O pins.                                                                              |

| VCAP                 | Р           |                            | No             | CPU logic filter capacitor connection.                                                                                          |

| Vss                  | P           |                            | No             | Ground reference for logic and I/O pins.                                                                                        |

| Legend: CMOS         |             | compatible<br>gger input v | input or o     | utput Analog = Analog input I = Input                                                                                           |

#### TABLE 1-1. PINOLIT I/O DESCRIPTIONS (CONTINUED)

TTL = Transistor-Transistor Logic

PPS = Peripheral Pin Select — = Does not apply

Note 1: Not all pins are available on all devices. Refer to the specific device in the "Pin Diagrams" section for availability.

2: This pin is available on dsPIC33FJ09GS302 devices only.

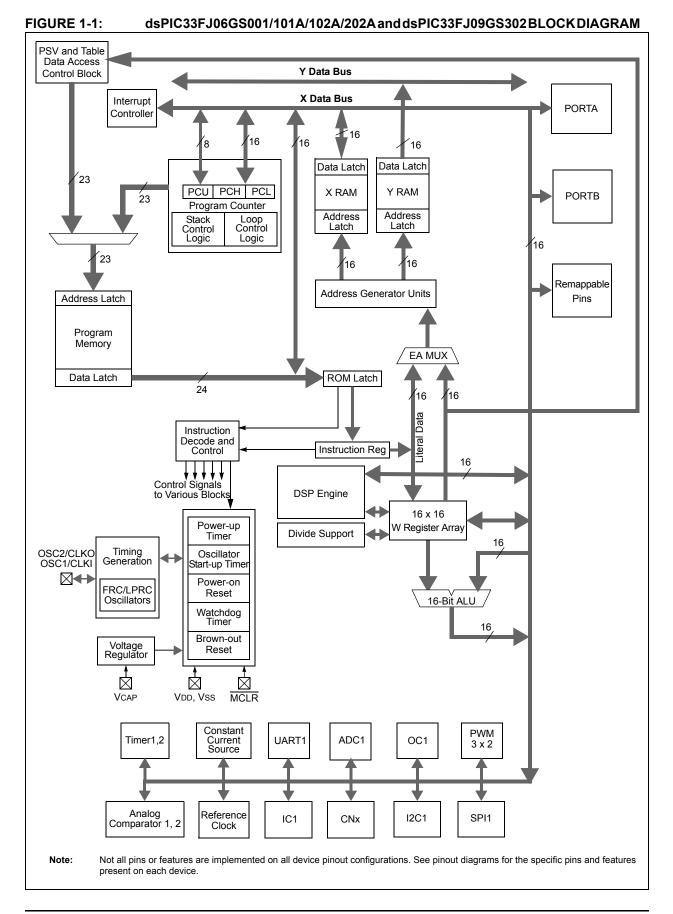

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS001/101A/102A/ 202A and dsPIC33FJ09GS302 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

## 2.1 Basic Connection Requirements

Getting started with the dsPIC33FJ06GS001/101A/ 102A/202A and dsPIC33FJ09GS302 family of 16-bit Digital Signal Controllers (DSCs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins, regardless if ADC module is not used

- (see Section 2.2 "Decoupling Capacitors")

VCAP

- (see Section 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP<sup>™</sup> Pins"**)

- OSC1 and OSC2 pins when external oscillator source is used (see Section 2.6 "External Oscillator Pins")

# 2.2 Decoupling Capacitors

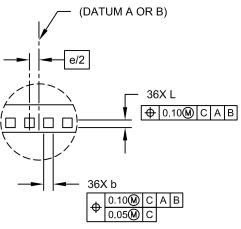

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS, is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, upward of tens of MHz, add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible; for example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

### TABLE 4-22: HIGH-SPEED 10-BIT ADC REGISTER MAP FOR dsPIC33FJ09GS302

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11 | Bit 10    | Bit 9 | Bit 8  | Bit 7        | Bit 6 | Bit 5   | Bit 4     | Bit 3 | Bit 2    | Bit 1   | Bit 0 | All<br>Resets |

|----------|-------------|--------|--------|--------|---------|--------|-----------|-------|--------|--------------|-------|---------|-----------|-------|----------|---------|-------|---------------|

| ADCON    | 0300        | ADON   | —      | ADSIDL | SLOWCLK | —      | GSWTRG    | _     | FORM   | EIE          | ORDER | SEQSAMP | ASYNCSAMP | —     | A        | DCS<2:0 | >     | 0003          |

| ADPCFG   | 0302        | _      | —      | _      | —       | -      | _         | _     | _      | PCFG7        | PCFG6 | PCFG5   | PCFG4     | PCFG3 | PCFG2    | PCFG1   | PCFG0 | 0000          |

| ADSTAT   | 0306        |        | —      | —      | —       |        | _         | _     | —      | _            | P6RDY | —       | —         | P3RDY | P2RDY    | P1RDY   | PORDY | 0000          |

| ADBASE   | 0308        |        |        |        |         |        |           | Α     | DBASE< | 15:1>        |       |         |           |       |          |         | _     | 0000          |

| ADCPC0   | 030A        | IRQEN1 | PEND1  | SWTRG1 |         | TRO    | SRC1<4:0> |       |        | IRQEN0       | PEND0 | SWTRG0  |           | TRGS  | RC0<4:0> |         |       | 0000          |

| ADCPC1   | 030C        | IRQEN3 | PEND3  | SWTRG3 |         | TRO    | SRC3<4:0> |       |        | IRQEN2       | PEND2 | SWTRG2  |           | TRGS  | RC2<4:0> |         |       | 0000          |

| ADCPC3   | 0310        |        | —      | —      | _       |        | _         | _     | —      | IRQEN6       | PEND6 | SWTRG6  |           | TRGS  | RC6<4:0> |         |       | 0000          |

| ADCBUF0  | 0320        |        |        |        |         |        |           |       | ADC Da | ata Buffer 0 |       |         |           |       |          |         |       | XXXX          |

| ADCBUF1  | 0322        |        |        |        |         |        |           |       | ADC Da | ata Buffer 1 |       |         |           |       |          |         |       | XXXX          |

| ADCBUF2  | 0324        |        |        |        |         |        |           |       | ADC Da | ata Buffer 2 |       |         |           |       |          |         |       | XXXX          |

| ADCBUF3  | 0326        |        |        |        |         |        |           |       | ADC Da | ata Buffer 3 |       |         |           |       |          |         |       | XXXX          |

| ADCBUF4  | 0328        |        |        |        |         |        |           |       | ADC Da | ata Buffer 4 |       |         |           |       |          |         |       | XXXX          |

| ADCBUF5  | 032A        |        |        |        |         |        |           |       | ADC Da | ata Buffer 5 |       |         |           |       |          |         |       | XXXX          |

| ADCBUF6  | 032C        |        |        |        |         |        |           |       | ADC Da | ata Buffer 6 |       |         |           |       |          |         |       | XXXX          |

| ADCBUF7  | 032E        |        |        |        |         |        |           |       | ADC Da | ata Buffer 7 |       |         |           |       |          |         |       | xxxx          |

| ADCBUF12 | 0338        |        |        |        |         |        |           |       | ADC Da | ta Buffer 12 | 2     |         |           |       |          |         |       | xxxx          |

| ADCBUF13 | 033A        |        |        |        |         |        |           |       | ADC Da | ta Buffer 13 | 3     |         |           |       |          |         |       | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-23: ANALOG COMPARATOR CONTROL REGISTER MAP FOR dsPIC33FJ06GS001, dsPIC33FJ06GS202A AND dsPIC33FJ09GS302

| File Name | ADR  | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11  | Bit 10 | Bit 9   | Bit 8                | Bit 7 | Bit 6  | Bit 5  | Bit 4   | Bit 3   | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|---------|--------|---------|--------|---------|----------------------|-------|--------|--------|---------|---------|-------|--------|-------|---------------|

| CMPCON1   | 0540 | CMPON  | _      | CMPSIDL | HYSSI  | EL<1:0> | FLTREN | FCLKSEL | DACOE <sup>(1)</sup> | INSEL | .<1:0> | EXTREF | HYSPOL  | CMPSTAT | HGAIN | CMPPOL | RANGE | 0000          |

| CMPDAC1   | 0542 | _      | _      | _       | _      | _       | _      |         |                      |       |        | CMR    | EF<9:0> |         |       |        |       | 0000          |

| CMPCON2   | 0544 | CMPON  | _      | CMPSIDL | HYSSI  | EL<1:0> | FLTREN | FCLKSEL | DACOE <sup>(1)</sup> | INSEL | .<1:0> | EXTREF | HYSPOL  | CMPSTAT | HGAIN | CMPPOL | RANGE | 0000          |

| CMPDAC2   | 0546 | —      | _      | _       | _      | _       | _      |         |                      |       |        | CMR    | EF<9:0> |         |       |        |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note 1:** This bit is not available in the dsPIC33FJ06GS001 device.

| TABLE 4- | 26:         | PERIPI | HERAL  | . PIN SE | LECT IN | PUT RE  | GISTER | R MAP | FOR d | sPIC33 | FJ06GS | 202A AN | ID dsP | IC33FJ0 | 9GS302 |       |       |   |

|----------|-------------|--------|--------|----------|---------|---------|--------|-------|-------|--------|--------|---------|--------|---------|--------|-------|-------|---|

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13   | Bit 12  | Bit 11  | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6  | Bit 5   | Bit 4  | Bit 3   | Bit 2  | Bit 1 | Bit 0 |   |

| RPINR0   | 0680        | —      | —      |          |         | INT1R<  | 5:0>   |       |       | —      | —      | -       | —      | —       | —      | —     | -     | Î |

| RPINR1   | 0682        | _      | _      | _        | _       | _       | —      | —     | —     | —      | _      |         |        | INT2R   | <5:0>  |       |       | Ĩ |

| RPINR2   | 0684        | _      | _      |          |         | T1CKR<  | 5:0>   |       |       | —      | _      | _       | —      | _       | _      | _     | _     | Ĩ |

| RPINR3   | 0686        | _      | _      | _        | _       | _       | —      | —     | —     | —      | _      |         |        | T2CKF   | <5:0>  |       |       | Ĩ |

| RPINR7   | 068E        | _      | _      | _        | _       | _       | _      | —     | —     | —      | _      |         |        | IC1R<   | <5:0>  |       |       | Ī |

| RPINR11  | 0696        | _      | _      | _        | _       | _       | —      | _     | —     | —      | _      |         |        | OCFAF   | <5:0>  |       |       | Ī |

| RPINR18  | 06A4        | _      | _      |          |         | U1CTSR- | <5:0>  |       |       | —      | _      |         |        | U1RXF   | <5:0>  |       |       | Ī |

| RPINR20  | 06A8        | _      | _      |          |         | SCK1R<  | 5:0>   |       |       | _      | _      |         |        | SDI1R   | <5:0>  |       |       | Ī |

| RPINR21  | 06AA        | _      | _      | _        | —       | _       | —      | —     | —     | _      |        |         |        | SS1R    | <5:0>  |       |       | T |

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

RPINR34 Legend:

RPINR29

RPINR30

RPINR31

RPINR32

RPINR33

06BA

06BC

06BE

06C0

06C2

06C4

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

FLT1R<5:0>

FLT3R<5:0>

FLT5R<5:0>

FLT7R<5:0>

SYNCI1R<5:0>

#### **TABLE 4-27:** PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33FJ06GS001 AND dsPIC33FJ06GS101A

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|---------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| RPOR0     | 06D0 | _      | _      |        |        | RP1    | R<5:0>  |       |       | _     | —     |       |       | RP0R< | <5:0> |       |       | 0000          |

| RPOR1     | 06D2 | _      | _      |        |        | RP3    | R<5:0>  |       |       | _     | _     |       |       | RP2R  | <5:0> |       |       | 0000          |

| RPOR2     | 06D4 | _      | _      |        |        | RP5    | R<5:0>  |       |       | _     | _     |       |       | RP4R  | <5:0> |       |       | 0000          |

| RPOR3     | 06D6 | _      | —      |        |        | RP7    | R<5:0>  |       |       | —     | _     |       |       | RP6R  | <5:0> |       |       | 0000          |

| RPOR16    | 06F0 | _      | _      |        |        | RP33   | 3R<5:0> |       |       | —     | _     |       |       | RP32R | <5:0> |       |       | 0000          |

| RPOR17    | 06F2 | _      | _      |        |        | RP3    | 5R<5:0> |       |       | _     | -     |       |       | RP34R | <5:0> |       |       | 0000          |

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

All Resets 3F00 003F 3F00 003F 003F 003F 3F3F 3F3F

003F

3F00

3F3F

3F3F

3F3F

3F3F

003F

\_

\_

FLT2R<5:0>

FLT4R<5:0>

FLT6R<5:0>

FLT8R<5:0>

SYNCI2R<5:0>

\_

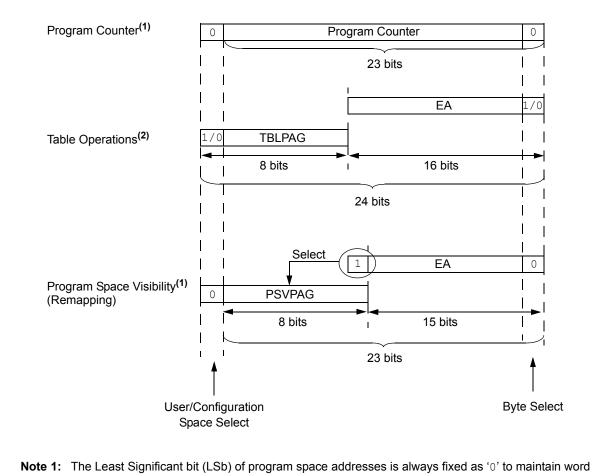

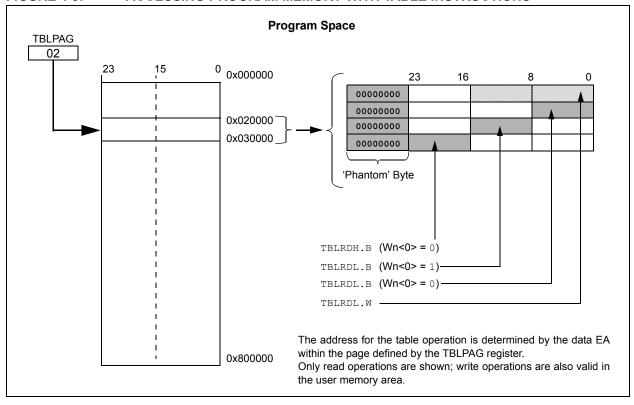

#### FIGURE 4-8: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

- alignment of data in the program and data spaces.

- 2: Table operations are not required to be word-aligned. Table read operations are permitted in the configuration memory space.

### 4.7.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>)

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when byte select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom byte', will always be '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address, in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

Similarly, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in Section 5.0 "Flash Program Memory".

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

# FIGURE 4-9: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

| REGISTER 8      | -5: ACLK                                                                                                                             | CON: AUXILI                                                           | ARY CLOCI      |                             | ONTROL RE        |                 |       |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------|-----------------------------|------------------|-----------------|-------|

| R/W-0           | R-0                                                                                                                                  | R/W-1                                                                 | U-0            | U-0                         | R/W-1            | R/W-1           | R/W-1 |

| ENAPLL          | APLLCK                                                                                                                               | SELACLK                                                               |                | —                           | AF               | PSTSCLR<2:0>    | (2)   |

| bit 15          |                                                                                                                                      |                                                                       |                |                             |                  |                 | bit 8 |

|                 |                                                                                                                                      |                                                                       |                |                             |                  |                 |       |

| R/W-0           | R/W-0                                                                                                                                | U-0                                                                   | U-0            | U-0                         | U-0              | U-0             | U-0   |

| ASRCSEL         | FRCSEL                                                                                                                               |                                                                       | —              | —                           |                  |                 | —     |

| bit 7           |                                                                                                                                      |                                                                       |                |                             |                  |                 | bit 0 |

| Legend:         |                                                                                                                                      |                                                                       |                |                             |                  |                 |       |

| R = Readable    | bit                                                                                                                                  | W = Writable I                                                        | hit            | U = Unimpler                | mented bit, read | 1 as '0'        |       |

| -n = Value at F |                                                                                                                                      | '1' = Bit is set                                                      |                | '0' = Bit is cle            |                  | x = Bit is unkr | nown  |

|                 |                                                                                                                                      |                                                                       |                |                             |                  |                 |       |

| bit 15          | ENAPLL: Aux                                                                                                                          | xiliary PLL Enal                                                      | ble bit        |                             |                  |                 |       |

|                 | 1 = APLL is e                                                                                                                        | nabled                                                                |                |                             |                  |                 |       |

|                 | 0 = APLL is d                                                                                                                        | lisabled                                                              |                |                             |                  |                 |       |

| bit 14          | APLLCK: AP                                                                                                                           | LL Locked Stat                                                        | us bit (read-o | nly)                        |                  |                 |       |

|                 |                                                                                                                                      | that auxiliary P that auxiliary P                                     |                | ck                          |                  |                 |       |

| bit 13          | SELACLK: S                                                                                                                           | elect Auxiliary                                                       | Clock Source   | for Auxiliary C             | lock Divider bit |                 |       |

|                 |                                                                                                                                      | oscillators provi<br>PLL (Fvco) prov                                  |                |                             |                  |                 |       |

| bit 12-11       | -                                                                                                                                    | ted: Read as '                                                        |                |                             |                  |                 |       |

| bit 10-8        | -                                                                                                                                    | 2:0>: Auxiliary                                                       |                | Divider bits <sup>(2)</sup> |                  |                 |       |

|                 | 111 = Divideo<br>110 = Divideo<br>101 = Divideo<br>100 = Divideo<br>011 = Divideo<br>010 = Divideo<br>001 = Divideo<br>001 = Divideo | d by 1<br>d by 2<br>d by 4<br>d by 8<br>d by 16<br>d by 32<br>d by 64 |                |                             |                  |                 |       |

| bit 7           | ASRCSEL: S                                                                                                                           | elect Reference                                                       | e Clock Sourc  | e for Auxiliary             | Clock bit        |                 |       |

|                 | •                                                                                                                                    | scillator is the o                                                    |                |                             |                  |                 |       |

| bit 6           | FRCSEL: Sel                                                                                                                          | lect Reference                                                        | Clock Source   | for Auxiliary P             | LL bit           |                 |       |

|                 | 1 = Selects F                                                                                                                        | RC clock for au<br>k source is dete                                   | ixiliary PLL   | -                           |                  |                 |       |

|                 | Unimplemen                                                                                                                           |                                                                       |                |                             | B                |                 |       |

#### (1) \_

2: The auxiliary clock postscaler must be configured to divide-by-1 (APSTSCLR<2:0> = 111) for proper operation of the PWM module.

# 9.5 PMD Control Registers

| U-0    | U-0 | U-0                 | R/W-0 | R/W-0                 | U-0 | R/W-0                | U-0   |

|--------|-----|---------------------|-------|-----------------------|-----|----------------------|-------|

| _      |     |                     | T2MD  | T1MD                  | _   | PWMMD <sup>(1)</sup> |       |

| bit 15 |     |                     |       |                       |     |                      | bit 8 |

|        |     |                     |       |                       |     |                      |       |

| R/W-0  | U-0 | R/W-0               | U-0   | R/W-0                 | U-0 | U-0                  | R/W-0 |

| I2C1MD | _   | U1MD <sup>(2)</sup> | _     | SPI1MD <sup>(2)</sup> | _   | —                    | ADCMD |

| bit 7  |     |                     |       |                       |     |                      | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                                             |

|-----------|--------------------------------------------------------------------------------------------------------|

| bit 12    | T2MD: Timer2 Module Disable bit                                                                        |

|           | 1 = Timer2 module is disabled                                                                          |

|           | 0 = Timer2 module is enabled                                                                           |

| bit 11    | T1MD: Timer1 Module Disable bit                                                                        |

|           | 1 = Timer1 module is disabled                                                                          |

|           | 0 = Timer1 module is enabled                                                                           |

| bit 10    | Unimplemented: Read as '0'                                                                             |

| bit 9     | <b>PWMMD:</b> PWM Module Disable bit <sup>(1)</sup>                                                    |

|           | 1 = PWM module is disabled                                                                             |

|           | 0 = PWM module is enabled                                                                              |

| bit 8     | Unimplemented: Read as '0'                                                                             |

| bit 7     | I2C1MD: I2C1 Module Disable bit                                                                        |

|           | 1 = I2C1 module is disabled                                                                            |

| 1.11.0    | 0 = I2C1 module is enabled                                                                             |

| bit 6     | Unimplemented: Read as '0'                                                                             |

| bit 5     | U1MD: UART1 Module Disable bit <sup>(2)</sup>                                                          |

|           | 1 = UART1 module is disabled<br>0 = UART1 module is enabled                                            |

| h:t 4     |                                                                                                        |

| bit 4     | Unimplemented: Read as '0'                                                                             |

| bit 3     | SPI1MD: SPI1 Module Disable bit <sup>(2)</sup>                                                         |

|           | 1 = SPI1 module is disabled<br>0 = SPI1 module is enabled                                              |

| bit 2-1   | Unimplemented: Read as '0'                                                                             |

|           | ADCMD: ADC Module Disable bit                                                                          |

| bit 0     |                                                                                                        |

|           | 1 = ADC module is disabled<br>0 = ADC module is enabled                                                |

|           |                                                                                                        |

| Note 1:   | Once the PWM module is re-enabled (PWMMD is set to '1' and then set to '0'), all PWM registers must be |

| 11010 11  |                                                                                                        |

- **Note 1:** Once the PWM module is re-enabled (PWMMD is set to '1' and then set to '0'), all PWM registers must be re-initialized.

- 2: This bit is not implemented in the dsPIC33FJ06GS001 device.

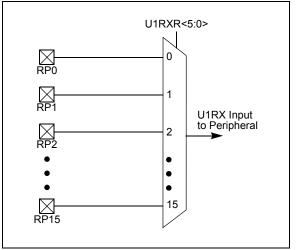

## 10.6 Peripheral Pin Select (PPS)

Peripheral Pin Select configuration enables peripheral set selection and placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, programmers can better tailor the microcontroller to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Programmers can independently map the input and/or output of most digital peripherals to any one of these I/O pins. Peripheral Pin Select is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 10.6.1 AVAILABLE PINS

The Peripheral Pin Select feature is used with a range of up to 16 pins. The number of available pins depends on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the designation, "RPn", in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable pin number.

#### 10.6.2 CONTROLLING PERIPHERAL PIN SELECT

Peripheral Pin Select features are controlled through two sets of Special Function Registers: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

### 10.6.2.1 Input Mapping

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. A control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 10-1 through Register 10-15). Each register contains sets of 6-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 6-bit value maps the RPn pin with that value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selections supported by the device.

Figure 10-2 illustrates the remappable pin selection for the U1RX input.

Note: For input mapping only, the Peripheral Pin Select (PPS) functionality does not have priority over the TRISx settings. Therefore, when configuring the RPx pin for input, the corresponding bit in the TRISx register must also be configured for input (i.e., set to '1').

#### FIGURE 10-2: REMAPPABLE MUX INPUT FOR U1RX

| U-0                   | U-0                  | R/W-1                                | R/W-1         | R/W-1            | R/W-1                 | R/W-1                      | R/W-1   |

|-----------------------|----------------------|--------------------------------------|---------------|------------------|-----------------------|----------------------------|---------|

| _                     | _                    |                                      |               |                  | R<5:0> <sup>(1)</sup> |                            |         |

| bit 15                |                      |                                      |               |                  |                       |                            | bit 8   |

|                       |                      |                                      |               |                  |                       |                            |         |

| U-0                   | U-0                  | R/W-1                                | R/W-1         | R/W-1            | R/W-1                 | R/W-1                      | R/W-1   |

| _                     | _                    |                                      |               | U1RXF            | R<5:0> <sup>(1)</sup> |                            |         |

| bit 7                 |                      |                                      |               |                  |                       |                            | bit (   |

| 1                     |                      |                                      |               |                  |                       |                            |         |

| Legend:<br>R = Readab | le hit               | W = Writable                         | hit           | II = I Inimpler  | nented bit, read      | h as 'O'                   |         |

| -n = Value a          |                      | '1' = Bit is set                     |               | '0' = Bit is cle |                       | x = Bit is unkr            |         |

|                       |                      |                                      |               |                  | arcu                  |                            |         |

| bit 15-14             | Unimplemen           | ted: Read as '                       | ∩ <b>'</b>    |                  |                       |                            |         |

| bit 13-8              | •                    |                                      |               |                  | a tha Carroona        | onding RPn Pin             | hita(1) |

| DIT 13-8              |                      | •                                    | TT Clear-to-S |                  | o the Correspo        | inding RPh Pin             | DIIS    |

|                       |                      | out tied to Vss                      | _             |                  |                       |                            |         |

|                       |                      | out tied to RP35                     |               |                  |                       |                            |         |

|                       |                      | out tied to RP34                     |               |                  |                       |                            |         |

|                       |                      | out tied to RP33<br>out tied to RP32 |               |                  |                       |                            |         |

|                       | 100000 <b>– III</b>  |                                      | <u>-</u>      |                  |                       |                            |         |

|                       | •                    |                                      |               |                  |                       |                            |         |

|                       | •                    |                                      |               |                  |                       |                            |         |

|                       | •                    |                                      |               |                  |                       |                            |         |

|                       | 00000 <b>= Inp</b>   | ut tied to RP0                       |               |                  |                       |                            |         |

| bit 7-6               | Unimplemen           | nted: Read as '                      | 0'            |                  |                       |                            |         |

| bit 5-0               | U1RXR<5:0>           | . Assign UART                        | 1 Receive (U  | 1RX) to the Co   | rresponding RI        | Pn Pin bits <sup>(1)</sup> |         |

|                       |                      | out tied to Vss                      | · ·           |                  |                       |                            |         |

|                       |                      | out tied to RP35                     | 5             |                  |                       |                            |         |

|                       |                      | out tied to RP34                     |               |                  |                       |                            |         |

|                       | 100001 <b>= In</b>   | out tied to RP33                     | 3             |                  |                       |                            |         |

|                       | 100000 <b>= In</b>   | out tied to RP32                     | 2             |                  |                       |                            |         |

|                       | •                    |                                      |               |                  |                       |                            |         |

|                       | •                    |                                      |               |                  |                       |                            |         |

|                       | •                    |                                      |               |                  |                       |                            |         |

|                       | 00000 <b>= Inn</b>   | ut tied to RP0                       |               |                  |                       |                            |         |

|                       | 00000 – m <b>p</b> t |                                      |               |                  |                       |                            |         |

|                       |                      |                                      |               |                  |                       |                            |         |

### REGISTER 10-7: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

**Note 1:** These bits are not implemented in the dsPIC33FJ06GS001 device.

| U-0          | U-0                                                                                                                                                                           | R/W-1                                                                                                                                                                                                                               | R/W-1                                                     | R/W-1            | R/W-1          | R/W-1           | R/W-1 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------|----------------|-----------------|-------|

|              |                                                                                                                                                                               |                                                                                                                                                                                                                                     |                                                           | FLT5             | R<5:0>         |                 |       |

| bit 15       |                                                                                                                                                                               |                                                                                                                                                                                                                                     |                                                           |                  |                |                 | bit   |

|              |                                                                                                                                                                               |                                                                                                                                                                                                                                     |                                                           |                  |                |                 |       |

| U-0          | U-0                                                                                                                                                                           | R/W-1                                                                                                                                                                                                                               | R/W-1                                                     | R/W-1            | R/W-1          | R/W-1           | R/W-1 |

|              |                                                                                                                                                                               |                                                                                                                                                                                                                                     |                                                           | FLT4             | R<5:0>         |                 |       |

| bit 7        |                                                                                                                                                                               |                                                                                                                                                                                                                                     |                                                           |                  |                |                 | bit   |

| Legend:      |                                                                                                                                                                               |                                                                                                                                                                                                                                     |                                                           |                  |                |                 |       |

| R = Readab   | le bit                                                                                                                                                                        | W = Writable                                                                                                                                                                                                                        | bit                                                       | U = Unimpler     | nented bit rea | ad as '0'       |       |

| -n = Value a |                                                                                                                                                                               | '1' = Bit is set                                                                                                                                                                                                                    |                                                           | '0' = Bit is cle |                | x = Bit is unkr | าดพท  |

|              |                                                                                                                                                                               |                                                                                                                                                                                                                                     |                                                           |                  |                |                 |       |

| bit 15-14    | Unimpleme                                                                                                                                                                     | nted: Read as '                                                                                                                                                                                                                     | 0'                                                        |                  |                |                 |       |

|              | •                                                                                                                                                                             |                                                                                                                                                                                                                                     |                                                           | (ELTE) to the C  |                | DDn Din hite    |       |

| bit 13-8     | FLT5R<5:0>                                                                                                                                                                    | >: Assian PWM I                                                                                                                                                                                                                     | -ault indut 5 i                                           | гнэлю ше с       | orresponding   |                 |       |

| bit 13-8     |                                                                                                                                                                               | Assign PWM I<br>apput tied to Vss                                                                                                                                                                                                   | -ault Input 5                                             | (FL15) to the C  | orresponding   |                 |       |

| bit 13-8     | 111111 <b>= In</b>                                                                                                                                                            | put tied to Vss                                                                                                                                                                                                                     |                                                           |                  | orresponding   |                 |       |

| bit 13-8     | 111111 = In<br>100011 = In                                                                                                                                                    | nput tied to Vss<br>nput tied to RP35                                                                                                                                                                                               | 5                                                         |                  | orresponding   |                 |       |

| bit 13-8     | 111111 = In<br>100011 = In<br>100010 = In                                                                                                                                     | nput tied to Vss<br>nput tied to RP35<br>nput tied to RP34                                                                                                                                                                          | 5                                                         |                  | orresponding   |                 |       |

| bit 13-8     | 111111 = In<br>100011 = In<br>100010 = In<br>100001 = In                                                                                                                      | nput tied to Vss<br>nput tied to RP35                                                                                                                                                                                               | 5<br>4<br>3                                               |                  | presponding    |                 |       |

| bit 13-8     | 111111 = In<br>100011 = In<br>100010 = In<br>100001 = In                                                                                                                      | nput tied to Vss<br>nput tied to RP35<br>nput tied to RP34<br>nput tied to RP33                                                                                                                                                     | 5<br>4<br>3                                               |                  | presponding    |                 |       |

| bit 13-8     | 111111 = In<br>100011 = In<br>100010 = In<br>100001 = In                                                                                                                      | nput tied to Vss<br>nput tied to RP35<br>nput tied to RP34<br>nput tied to RP33                                                                                                                                                     | 5<br>4<br>3                                               |                  | presponding    |                 |       |

| bit 13-8     | 111111 = In<br>100011 = In<br>100010 = In<br>100001 = In                                                                                                                      | nput tied to Vss<br>nput tied to RP35<br>nput tied to RP34<br>nput tied to RP33                                                                                                                                                     | 5<br>4<br>3                                               |                  | presponding    |                 |       |

| bit 13-8     | 111111 = In<br>100011 = In<br>100010 = In<br>100001 = In<br>100000 = In                                                                                                       | nput tied to Vss<br>nput tied to RP35<br>nput tied to RP34<br>nput tied to RP33                                                                                                                                                     | 5<br>4<br>3                                               |                  | presponding    |                 |       |

|              | 111111 = In<br>100011 = In<br>100010 = In<br>100001 = In<br>100000 = In<br>•                                                                                                  | nput tied to Vss<br>nput tied to RP35<br>nput tied to RP34<br>nput tied to RP33<br>nput tied to RP33                                                                                                                                | 5<br>4<br>3<br>2                                          |                  | presponding    |                 |       |

| bit 7-6      | 111111 = In<br>100011 = In<br>100010 = In<br>100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                 | aput tied to Vss<br>aput tied to RP35<br>aput tied to RP35<br>aput tied to RP35<br>aput tied to RP35<br>but tied to RP36<br>anted: Read as f                                                                                        | 5<br>4<br>3<br>2                                          |                  |                |                 |       |

|              | 111111 = In<br>100011 = In<br>100010 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                       | put tied to Vss<br>aput tied to RP35<br>aput tied to RP35<br>aput tied to RP35<br>aput tied to RP35<br>but tied to RP0<br><b>nted:</b> Read as 'e                                                                                   | 5<br>4<br>3<br>2                                          |                  |                |                 |       |

| bit 7-6      | 111111 = In<br>100011 = In<br>100010 = In<br>100000 = In<br>00000 = Inp<br>Unimpleme<br>FLT4R<5:0><br>111111 = In                                                             | put tied to Vss<br>aput tied to RP35<br>aput tied to RP35<br>aput tied to RP35<br>aput tied to RP35<br>but tied to RP0<br><b>nted:</b> Read as 'n<br>>: Assign PWM F<br>aput tied to Vss                                            | 5<br>4<br>3<br>2<br>0'<br>=ault Input 4                   |                  |                |                 |       |

| bit 7-6      | 111111 = In<br>100011 = In<br>100010 = In<br>100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                      | put tied to Vss<br>aput tied to RP35<br>aput tied to RP35<br>aput tied to RP35<br>aput tied to RP35<br>but tied to RP0<br><b>nted:</b> Read as '<br>>: Assign PWM F<br>aput tied to Vss<br>aput tied to RP35                        | 5<br>4<br>3<br>2<br>0'<br>=ault Input 4                   |                  |                |                 |       |

| bit 7-6      | 111111 = In<br>100011 = In<br>100010 = In<br>100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                      | put tied to Vss<br>aput tied to RP35<br>aput tied to RP35<br>aput tied to RP35<br>aput tied to RP35<br>but tied to RP0<br><b>nted:</b> Read as 'n<br>>: Assign PWM F<br>aput tied to Vss                                            | 5<br>4<br>3<br>2<br>0'<br>=ault Input 4 (<br>5<br>4       |                  |                |                 |       |

| bit 7-6      | 111111 = In<br>100011 = In<br>100010 = In<br>100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                      | put tied to Vss<br>aput tied to RP35<br>aput tied to RP35<br>aput tied to RP35<br>aput tied to RP35<br>but tied to RP36<br><b>nted:</b> Read as 'n<br>>: Assign PWM F<br>aput tied to Vss<br>aput tied to RP35<br>aput tied to RP35 | 5<br>4<br>3<br>2<br>0'<br>= ault Input 4 (<br>5<br>4<br>3 |                  |                |                 |       |

| bit 7-6      | 111111 = In<br>100011 = In<br>100010 = In<br>100001 = In<br>100000 = In<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                      | put tied to Vss<br>aput tied to RP33<br>aput tied to RP33<br>aput tied to RP33<br>aput tied to RP33<br>but tied to RP34<br><b>nted:</b> Read as 'n<br>>: Assign PWM F<br>aput tied to Vss<br>aput tied to RP34<br>aput tied to RP34 | 5<br>4<br>3<br>2<br>0'<br>= ault Input 4 (<br>5<br>4<br>3 |                  |                |                 |       |

| bit 7-6      | 111111 = In<br>100011 = In<br>100010 = In<br>100000 = In<br>•<br>•<br>•<br>00000 = Inp<br>Unimpleme<br>FLT4R<5:0><br>111111 = In<br>100011 = In<br>100010 = In<br>100001 = In | put tied to Vss<br>aput tied to RP33<br>aput tied to RP33<br>aput tied to RP33<br>aput tied to RP33<br>but tied to RP34<br><b>nted:</b> Read as 'n<br>>: Assign PWM F<br>aput tied to Vss<br>aput tied to RP34<br>aput tied to RP34 | 5<br>4<br>3<br>2<br>0'<br>= ault Input 4 (<br>5<br>4<br>3 |                  |                |                 |       |

| bit 7-6      | 111111 = In<br>100011 = In<br>100010 = In<br>100000 = In<br>•<br>•<br>•<br>00000 = Inp<br>Unimpleme<br>FLT4R<5:0><br>111111 = In<br>100011 = In<br>100010 = In<br>100001 = In | put tied to Vss<br>aput tied to RP33<br>aput tied to RP33<br>aput tied to RP33<br>aput tied to RP33<br>but tied to RP34<br><b>nted:</b> Read as 'n<br>>: Assign PWM F<br>aput tied to Vss<br>aput tied to RP34<br>aput tied to RP34 | 5<br>4<br>3<br>2<br>0'<br>= ault Input 4 (<br>5<br>4<br>3 |                  |                |                 |       |

## REGISTER 15-9: PHASEX: PWMx PRIMARY PHASE SHIFT REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0   | R/W-0                  | R/W-0  | R/W-0 | R/W-0  |

|--------|-------|-------|---------|------------------------|--------|-------|--------|

| 10000  | 10000 | 10000 | -       | -                      | 1000 0 | 10000 | 1000 0 |

|        |       |       | PHASEx• | <15:8> <b>(1,2)</b>    |        |       |        |

| bit 15 |       |       |         |                        |        |       | bit 8  |

|        |       |       |         |                        |        |       |        |

| R/W-0  | R/W-0 | R/W-0 | R/W-0   | R/W-0                  | R/W-0  | R/W-0 | R/W-0  |

|        |       |       | PHASEx  | <7:0> <sup>(1,2)</sup> |        |       |        |

| bit 7  |       |       |         |                        |        |       | bit 0  |

|        |       |       |         |                        |        |       |        |

|        |       |       |         |                        |        |       |        |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **PHASEx<15:0>:** PWMx Phase Shift Value or Independent Time Base Period for PWM Generator bits<sup>(1,2)</sup>

**Note 1:** If the ITB (PWMCONx<9>) bit = 0, the following applies based on the mode of operation:

- Complementary, Redundant and Push-Pull Output mode (PMOD<1:0> (IOCONx<11:10>) = 00, 01 or 10), PHASEx<15:0> = Phase shift value for PWMxH and PWMxL outputs.

- True Independent Output mode PMOD<1:0> (IOCONx<11:10>) = 11), PHASEx<15:0> = Phase shift value for PWMxL only.

**2:** If the ITB (PWMCONx<9>) bit = 1, the following applies based on the mode of operation:

• Complementary, Redundant and Push-Pull Output mode (PMOD<1:0> (IOCONx<11:10>) = 00, 01 or 10), PHASEx<15:0> = Independent time base period value for PWMxH and PWMxL.

- True Independent Output mode PMOD<1:0> (IOCONx<11:10>) = 11), PHASEx<15:0> = Independent time base period value for PWMxL only.

- The smallest pulse width that can be generated on the PWM output corresponds to a value of 0x0008, while the maximum pulse width generated corresponds to a value of Period-0x0008.

#### REGISTER 16-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- - 00 = Primary prescale 64:1

- Note 1: This bit is not used in Framed SPI modes. Program this bit to '0' for the Framed SPI modes (FRMEN = 1).

- 2: Do not set both Primary and Secondary prescalers to a value of 1:1.

- **3:** This bit must be cleared when FRMEN = 1.

# **19.4 ADC Control Registers**

The ADC module uses the following control and status registers:

- ADCON: ADC Control Register

- ADSTAT: ADC Status Register

- ADBASE: ADC Base Register(1)

- ADPCFG: ADC Port Configuration Register

- ADCPC0: ADC Convert Pair Control Register 0

- ADCPC1: ADC Convert Pair Control Register 1

- ADCPC3: ADC Convert Pair Control Register 3(1)

The ADCON register controls the operation of the ADC module. The ADSTAT register displays the status of the conversion processes. The ADPCFG register configures the port pins as analog inputs or as digital I/Os. The ADCPCx registers control the triggering of the ADC conversions. See Register 19-1 through Register 19-7 for detailed bit configurations.

**Note:** A unique feature of the ADC module is its ability to sample inputs in an asynchronous manner. Individual Sample-and-Hold circuits can be triggered independently of each other.

# REGISTER 19-1: ADCON: ADC CONTROL REGISTER

| R/W-0  | U-0 | R/W-0  | R/W-0                  | U-0 | R/W-0  | U-0 | R/W-0               |

|--------|-----|--------|------------------------|-----|--------|-----|---------------------|

| ADON   | —   | ADSIDL | SLOWCLK <sup>(1)</sup> | —   | GSWTRG | _   | FORM <sup>(1)</sup> |

| bit 15 |     |        |                        |     |        |     | bit 8               |

| R/W-0              | R/W-0                | R/W-0                  | R/W-0                    | U-0 | R/W-0 | R/W-1        | R/W-1 |

|--------------------|----------------------|------------------------|--------------------------|-----|-------|--------------|-------|

| EIE <sup>(1)</sup> | ORDER <sup>(1)</sup> | SEQSAMP <sup>(1)</sup> | ASYNCSAMP <sup>(1)</sup> | _   |       | ADCS<2:0>(1) |       |

| bit 7              |                      |                        |                          |     |       |              | bit 0 |

| Legend:                                                                                                                       |                                                       |                                                                                                                          |                                    |                    |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bitW = Writable bit-n = Value at POR'1' = Bit is set                                                             |                                                       | U = Unimplemented bi                                                                                                     | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

|                                                                                                                               |                                                       | '1' = Bit is set                                                                                                         | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

| bit 15                                                                                                                        | ADON: A                                               | ADC Operating Mode bit                                                                                                   |                                    |                    |  |  |  |  |

| <ul><li>1 = ADC module is operating</li><li>0 = ADC module is off</li></ul>                                                   |                                                       |                                                                                                                          |                                    |                    |  |  |  |  |