Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 9KB (3K x 24)                                                                   |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 8x10b; D/A 2x10b                                                            |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                  |

| Supplier Device Package    | 28-SSOP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj09gs302-e-ss |

#### REGISTER 3-2: CORCON: CORE CONTROL REGISTER

| U-0    | U-0 | U-0 | R/W-0 | R/W-0              | R-0 | R-0     | R-0   |

|--------|-----|-----|-------|--------------------|-----|---------|-------|

| _      | _   | _   | US    | EDT <sup>(1)</sup> |     | DL<2:0> |       |

| bit 15 |     |     |       |                    |     |         | bit 8 |

| R/W-0 | R/W-0 | R/W-1 | R/W-0  | R/C-0               | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|--------|---------------------|-------|-------|-------|

| SATA  | SATB  | SATDW | ACCSAT | IPL3 <sup>(2)</sup> | PSV   | RND   | IF    |

| bit 7 |       |       |        |                     |       |       | bit 0 |

Legend:C = Clearable bitR = Readable bitW = Writable bit-n = Value at POR'1' = Bit is set0' = Bit is cleared'x = Bit is unknownU = Unimplemented bit, read as '0'

bit 15-13 **Unimplemented:** Read as '0'

bit 12 US: DSP Multiply Unsigned/Signed Control bit

1 = DSP engine multiplies are unsigned0 = DSP engine multiplies are signed

bit 11 **EDT:** Early DO Loop Termination Control bit<sup>(1)</sup>

1 = Terminate executing DO loop at end of current loop iteration

0 = No effect

bit 10-8 **DL<2:0>:** DO Loop Nesting Level Status bits

111 **= 7** DO **loops** active

•

001 = 1 DO loop active 000 = 0 DO loops active

bit 7 SATA: ACCA Saturation Enable bit

1 = Accumulator A saturation is enabled0 = Accumulator A saturation is disabled

bit 6 SATB: ACCB Saturation Enable bit

1 = Accumulator B saturation is enabled0 = Accumulator B saturation is disabled

bit 5 SATDW: Data Space Write from DSP Engine Saturation Enable bit

1 = Data space write saturation is enabled0 = Data space write saturation is disabled

bit 4 ACCSAT: Accumulator Saturation Mode Select bit

1 = 9.31 saturation (super saturation)0 = 1.31 saturation (normal saturation)

bit 3 **IPL3:** CPU Interrupt Priority Level Status bit 3<sup>(2)</sup>

1 = CPU Interrupt Priority Level is greater than 7 0 = CPU Interrupt Priority Level is 7 or less

**PSV:** Program Space Visibility in Data Space Enable bit

1 = Program space is visible in data space0 = Program space is not visible in data space

bit 1 RND: Rounding Mode Select bit

1 = Biased (conventional) rounding is enabled0 = Unbiased (convergent) rounding is enabled

1 = Integer mode enabled for DSP multiply ops

0 = Fractional mode enabled for DSP multiply ops

Note 1: This bit will always read as '0'.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

bit 2

| o        |

|----------|

| S75      |

| <u>ŏ</u> |

| င္ပ      |

| pag      |

| e 49     |

|          |

**TABLE 4-7:** INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33FJ06GS202A DEVICES ONLY

| File<br>Name | SFR<br>Addr. | Bit 15  | Bit 14  | Bit 13     | Bit 12  | Bit 11  | Bit 10 | Bit 9      | Bit 8 | Bit 7    | Bit 6   | Bit 5       | Bit 4   | Bit 3      | Bit 2  | Bit 1       | Bit 0   | All<br>Resets |

|--------------|--------------|---------|---------|------------|---------|---------|--------|------------|-------|----------|---------|-------------|---------|------------|--------|-------------|---------|---------------|

| INTCON1      | 0080         | NSTDIS  | OVAERR  | OVBERR     | COVAERR | COVBERR | OVATE  | OVBTE      | COVTE | SFTACERR | DIV0ERR | _           | MATHERR | ADDRERR    | STKERR | OSCFAIL     | _       | 0000          |

| INTCON2      | 0082         | ALTIVT  | DISI    | _          | _       | 1       | -      | _          | _     | _        | _       | _           | _       | _          | INT2EP | INT1EP      | INT0EP  | 0000          |

| IFS0         | 0084         | _       | _       | ADIF       | U1TXIF  | U1RXIF  | SPI1IF | SPI1EIF    |       | T2IF     | _       | _           | _       | T1IF       | OC1IF  | IC1IF       | INT0IF  | 0000          |

| IFS1         | 0086         | -       | _       | INT2IF     | _       | -       | _      | _          |       | _        | _       | _           | INT1IF  | CNIF       | AC1IF  | MI2C1IF     | SI2C1IF | 0000          |

| IFS3         | A800         | -       | _       | _          | _       | -       | _      | PSEMIF     |       | _        | _       | _           | _       | _          | _      | _           | _       | 0000          |

| IFS4         | 008C         | -       | ı       | -          | ı       | 1       | I      | _          | _     | _        | ı       | -           | _       | _          | ı      | U1EIF       | _       | 0000          |

| IFS5         | 008E         | PWM2IF  | PWM1IF  | -          | ı       | 1       | I      | _          | _     | _        | ı       | -           | _       | _          | ı      | -           | JTAGIF  | 0000          |

| IFS6         | 0090         | ADCP1IF | ADCP0IF | -          | ı       | ı       |        | _          | _     | AC2IF    | ı       | 1           | _       | _          | ı      | _           | _       | 0000          |

| IFS7         | 0092         | I       | ı       | -          | ı       | ı       |        | _          | _     | _        | ı       | 1           | ADCP6IF | _          | ı      | _           | ADCP2IF | 0000          |

| IEC0         | 0094         |         |         | ADIE       | U1TXIE  | U1RXIE  | SPI1IE | SPI1EIE    | _     | T2IE     |         | ı           | _       | T1IE       | OC1IE  | IC1IE       | INT0IE  | 0000          |

| IEC1         | 0096         |         |         | INT2IE     | ı       | -       | -      | _          | _     | _        |         | ı           | INT1IE  | CNIE       | AC1IE  | MI2C1IE     | SI2C1IE | 0000          |

| IEC3         | 009A         | I       | ı       | -          | ı       | ı       |        | PSEMIE     | _     | _        | ı       | 1           | _       | _          | ı      | _           | _       | 0000          |

| IEC4         | 009C         | I       | ı       | -          | ı       | ı       |        | _          | _     | _        | ı       | 1           | _       | _          | ı      | U1EIE       | _       | 0000          |

| IEC5         | 009E         | PWM2IE  | PWM1IE  | -          | ı       | ı       |        | _          | _     | _        | ı       | 1           | _       | _          | ı      | _           | JTAGIE  | 0000          |

| IEC6         | 00A0         | ADCP1IE | ADCP0IE | -          | ı       | ı       |        | _          | _     | AC2IE    | ı       | 1           | _       | _          | ı      | _           | _       | 0000          |

| IEC7         | 00A2         | I       | ı       | -          | ı       | ı       |        | _          | _     | _        | ı       | 1           | ADCP6IE | _          | ı      | _           | ADCP2IE | 0000          |

| IPC0         | 00A4         | I       |         | T1IP<2:0>  |         | ı       | Ī      | OC1IP<2:0  | >     | _        |         | IC1IP<2:0>  | •       | _          |        | NT0IP<2:0>  |         | 4444          |

| IPC1         | 00A6         | I       |         | T2IP<2:0>  |         | ı       |        | _          | _     | _        | ı       | 1           | _       | _          | ı      | _           | _       | 4000          |

| IPC2         | 00A8         | I       |         | U1RXIP<2:0 | >       | ı       | •      | SPI1IP<2:0 | >     | _        | 33      | SPI1EIP<2:0 | )>      | _          | ı      | _           | _       | 4440          |

| IPC3         | 00AA         | I       | ı       | -          | ı       | ı       |        | _          | _     | _        |         | ADIP<2:0>   |         | _          | J      | J1TXIP<2:0> | •       | 0044          |

| IPC4         | 00AC         | I       |         | CNIP<2:0>  | •       | ı       |        | AC1IP<2:0  | >     | _        | N       | ЛI2C1IP<2:( | )>      | _          | S      | 12C1IP<2:0> | >       | 4444          |

| IPC5         | 00AE         | I       | ı       | -          | ı       | ı       |        | _          | _     | _        | ı       | 1           | _       | _          |        | NT1IP<2:0>  |         | 0004          |

| IPC7         | 00B2         | -       | ı       | -          | ı       | 1       | I      | _          | _     | _        |         | INT2IP<2:0  | >       | _          | ı      | -           | _       | 0040          |

| IPC14        | 00C0         | -       | _       | _          | _       | -       | _      | _          |       | _        | F       | PSEMIP<2:0  | )>      | _          | _      | _           | _       | 0040          |

| IPC16        | 00C4         | -       | _       | _          | _       | -       | _      | _          |       | _        |         | U1EIP<2:0   | >       | _          | _      | _           | _       | 0040          |

| IPC20        | 00CC         | -       | 1       | _          | _       | -       | I      | _          | _     | _        | -       | _           | _       | _          |        | TAGIP<2:0>  | •       | 0004          |

| IPC23        | 00D2         | _       | F       | PWM2IP<2:0 | )>      | _       | Р      | WM1IP<2:   | 0>    | _        | -       | _           | _       | _          | -      |             | _       | 4400          |

| IPC25        | 00D6         | _       |         | AC2IP<2:0> | >       | _       | _      | _          |       | _        | -       | _           | _       | _          | _      |             | _       | 4000          |

| IPC27        | 00DA         | -       | A       | DCP1IP<2:  | 0>      | -       | A      | DCP0IP<2   | :0>   | _        | 1       | _           | _       | _          | -      |             | _       | 4400          |

| IPC28        | 00DC         | -       | _       |            | _       | -       | _      | _          |       |          | 1       |             | _       |            | А      | DCP2IP<2:0  | >       | 0004          |

| IPC29        | 00DE         | _       | _       | _          | _       | _       | _      |            | _     | _        | -       | _           | _       | _          | А      | DCP6IP<2:0  | >       | 0004          |

| INTTREG      | 00E0         | -       | ı       | -          | ı       |         | ILR<   | 3:0>       |       | _        |         |             |         | /ECNUM<6:0 | )>     |             |         | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. **TABLE 4-19:**

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### HIGH-SPEED 10-BIT ADC REGISTER MAP FOR dsPIC33FJ06GS001 AND dsPIC33FJ06GS101A **TABLE 4-20:**

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                  | Bit 13 | Bit 12  | Bit 11 | Bit 10    | Bit 9 | Bit 8  | Bit 7        | Bit 6 | Bit 5               | Bit 4     | Bit 3 | Bit 2    | Bit 1   | Bit 0 | All<br>Resets |

|----------|-------------|--------|-------------------------|--------|---------|--------|-----------|-------|--------|--------------|-------|---------------------|-----------|-------|----------|---------|-------|---------------|

| ADCON    | 0300        | ADON   |                         | ADSIDL | SLOWCLK | -      | GSWTRG    | _     | FORM   | EIE          | ORDER | SEQSAMP             | ASYNCSAMP | -     | А        | DCS<2:0 | >     | 0003          |

| ADPCFG   | 0302        | -      | _                       | -      | _       | _      | -         | _     | _      | PCFG7        | PCFG6 | _                   | _         | PCFG3 | PCFG2    | PCFG1   | PCFG0 | 0000          |

| ADSTAT   | 0306        | -      | _                       | -      | _       | _      | -         | _     | _      | _            | P6RDY | _                   | _         | P3RDY | _        | P1RDY   | P0RDY | 0000          |

| ADBASE   | 0308        |        |                         |        |         |        |           | Α     | DBASE< | 15:1>        |       |                     | _         |       |          |         |       | 0000          |

| ADCPC0   | 030A        | IRQEN1 | PEND1                   | SWTRG1 |         | TRG    | SRC1<4:0> |       |        | IRQEN0       | PEND0 | SWTRG0 TRGSRC0<4:0> |           |       |          |         |       |               |

| ADCPC1   | 030C        | IRQEN3 | PEND3                   | SWTRG3 |         | TRG    | SRC3<4:0> |       |        | _            | _     | _                   |           |       |          |         |       | 0000          |

| ADCPC3   | 0310        | _      | _                       | _      | _       | _      | _         | _     | _      | IRQEN6       | PEND6 | SWTRG6              |           | TRGS  | RC6<4:0> |         |       | 0000          |

| ADCBUF0  | 0320        |        |                         |        |         |        |           |       | ADC Da | ata Buffer 0 |       |                     |           |       |          |         |       | xxxx          |

| ADCBUF1  | 0322        |        |                         |        |         |        |           |       | ADC Da | ata Buffer 1 |       |                     |           |       |          |         |       | xxxx          |

| ADCBUF2  | 0324        |        |                         |        |         |        |           |       | ADC Da | ata Buffer 2 | !     |                     |           |       |          |         |       | xxxx          |

| ADCBUF3  | 0326        |        |                         |        |         |        |           |       | ADC Da | ata Buffer 3 |       |                     |           |       |          |         |       | xxxx          |

| ADCBUF6  | 032C        |        |                         |        |         |        |           |       | ADC Da | ata Buffer 6 | i     |                     |           |       |          |         |       | xxxx          |

| ADCBUF7  | 032E        |        | ADC Data Buffer 7 xxx   |        |         |        |           |       |        |              |       | xxxx                |           |       |          |         |       |               |

| ADCBUF12 | 0338        |        |                         |        |         |        |           |       | ADC Da | ta Buffer 12 | 2     |                     |           |       |          |         |       | xxxx          |

| ADCBUF13 | 033A        |        | ADC Data Buffer 13 xxxx |        |         |        |           |       |        |              |       |                     | xxxx      |       |          |         |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-34: PMD REGISTER MAP FOR dsPIC33FJ06GS001

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| PMD1        | 0770        | _      |        | 1      | T2MD   | T1MD   | -      | PWMMD  | -      | I2C1MD | _     | _     | _     | _      | _     | -     | ADCMD | 0000          |

| PMD3        | 0774        | _      | _      | ı      | -      | _      | CMPMD  | ı      | ı      | _      | _     | _     | _     | _      | _     | _     | _     | 0000          |

| PMD4        | 0776        | _      | _      | ı      | -      | _      | -      | ı      | ı      | _      | _     | _     | _     | REFOMD | _     | _     | _     | 0000          |

| PMD6        | 077A        |        | _      | -      | -      | PWM4MD | -      | ı      | PWM1MD |        | _     | _     | _     | _      | 1     | -     | _     | 0000          |

| PMD7        | 077C        | _      | _      | _      | _      | _      | _      | CMPMD2 | CMPMD1 | _      | _     | _     | _     | _      | _     | _     | _     | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-35: PMD REGISTER MAP FOR dsPIC33FJ06GS101A

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|--------|--------|--------|--------|--------|--------|-------|--------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| PMD1        | 0770        | _      | _      | _      | T2MD   | T1MD   | -      | PWMMD | _      | I2C1MD | _     | U1MD  | _     | SPI1MD | _     | _     | ADCMD | 0000          |

| PMD2        | 0772        | ı      | _      | ı      | _      | -      |        | ı     | -      | _      | -     | _     | _     | _      | _     | _     | OC1MD | 0000          |

| PMD4        | 0776        | ı      | -      | Ι      | _      | 1      |        |       |        | _      |       | _     | _     | REFOMD | _     | -     | _     | 0000          |

| PMD6        | 077A        |        |        | ı      | _      | PWM4MD |        | I     | PWM1MD | _      | 1     | _     | _     | _      | _     | -     | _     | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-36: PMD REGISTER MAP FOR dsPIC33FJ06GS102A

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| PMD1        | 0770        | _      | _      |        | T2MD   | T1MD   | _      | PWMMD  | _      | I2C1MD | _     | U1MD  | _     | SPI1MD | _     | _     | ADCMD | 0000          |

| PMD2        | 0772        | -      | -      | -      | _      | _      | _      | _      | _      | _      | _     | _     | _     | _      | _     | _     | OC1MD | 0000          |

| PMD4        | 0776        | -      | -      | -      | _      | _      | _      | _      | _      | _      | _     | _     | _     | REFOMD | _     | _     | _     | 0000          |

| PMD6        | 077A        | _      | _      | ı      | -      | -      | ı      | PWM2MD | PWM1MD | _      | _     | _     | _     | _      | _     | _     | _     | 0000          |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 4.5.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- · Upper boundary addresses for incrementing buffers

- · Lower boundary addresses for decrementing buffers

It is important to realize that the address boundaries check for addresses less than or greater than the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note

The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (such as [W7 + W2]) is used, Modulo Addressing correction is performed but the contents of the register remain unchanged.

#### 4.6 Bit-Reversed Addressing

Bit-Reversed Addressing mode is intended to simplify data re-ordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

# 4.6.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled when all of these conditions are met:

- BWMx bits (W register selection) in the MODCON register are any value other than '15' (the stack cannot be accessed using Bit-Reversed Addressing)

- · BREN bit is set in the XBREV register

- Addressing mode used is Register Indirect with Pre-increment or Post-increment

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the Bit-Reversed Address modifier, or 'pivot point,' which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

Note:

All bit-reversed EA calculations assume word-sized data (LSb of every EA is always clear). The XB value is scaled accordingly to generate compatible (byte) addresses.

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It will not function for any other addressing mode or for byte-sized data, and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB), and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

Note:

Modulo Addressing and Bit-Reversed Addressing should not be enabled together. If an application attempts to do so, Bit-Reversed Addressing will assume priority when active for the X WAGU and X WAGU; Modulo Addressing will be disabled. However, Modulo Addressing will continue to function in the X RAGU.

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

#### REGISTER 7-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1

| U-0    | U-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|--------|-----|-----|-----|-----|-------|

| _      | _   | INT2IF | _   | _   | _   | _   | _     |

| bit 15 |     |        |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-0  | R/W-0 | R/W-0               | R/W-0   | R/W-0   |

|-------|-----|-----|--------|-------|---------------------|---------|---------|

| _     | _   | _   | INT1IF | CNIF  | AC1IF <sup>(1</sup> | MI2C1IF | SI2C1IF |

| bit 7 |     |     |        |       |                     |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13 INT2IF: External Interrupt 2 Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 12-5 Unimplemented: Read as '0'

bit 4 INT1IF: External Interrupt 1 Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 3 CNIF: Input Change Notification Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 2 AC1IF: Analog Comparator 1 Interrupt Flag Status bit<sup>(1)</sup>

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 1 MI2C1IF: I2C1 Master Events Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 0 SI2C1IF: I2C1 Slave Events Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

Note 1: This bit is not implemented in dsPIC33FJ06GS101A/102A devices.

## REGISTER 8-5: ACLKCON: AUXILIARY CLOCK DIVISOR CONTROL REGISTER<sup>(1)</sup>

| R/W-0  | R-0    | R/W-1   | U-0 | U-0 | R/W-1 | R/W-1       | R/W-1 |

|--------|--------|---------|-----|-----|-------|-------------|-------|

| ENAPLL | APLLCK | SELACLK | _   | _   | AP    | STSCLR<2:0> | (2)   |

| bit 15 |        |         |     |     |       |             | bit 8 |

| R/W-0   | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------|--------|-----|-----|-----|-----|-----|-------|

| ASRCSEL | FRCSEL | _   | _   | _   | _   | _   | _     |

| bit 7   |        |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **ENAPLL:** Auxiliary PLL Enable bit

1 = APLL is enabled

0 = APLL is disabled

bit 14 APLLCK: APLL Locked Status bit (read-only)

1 = Indicates that auxiliary PLL is in lock

0 = Indicates that auxiliary PLL is not in lock

bit 13 SELACLK: Select Auxiliary Clock Source for Auxiliary Clock Divider bit

1 = Auxiliary oscillators provides the source clock for auxiliary clock divider

0 = Primary PLL (Fvco) provides the source clock for auxiliary clock divider

bit 12-11 **Unimplemented:** Read as '0'

bit 10-8 **APSTSCLR<2:0>:** Auxiliary Clock Output Divider bits<sup>(2)</sup>

111 = Divided by 1

110 = Divided by 2

101 = Divided by 4

100 = Divided by 8

011 = Divided by 16

010 **= Divided by 32**

001 = Divided by 64

000 = Divided by 256

bit 7 ASRCSEL: Select Reference Clock Source for Auxiliary Clock bit

1 = Primary oscillator is the clock source

0 = No clock input is selected

bit 6 FRCSEL: Select Reference Clock Source for Auxiliary PLL bit

1 = Selects FRC clock for auxiliary PLL

0 = Input clock source is determined by ASRCSEL bit setting

bit 5-0 **Unimplemented:** Read as '0'

Note 1: This register is reset only on a Power-on Reset (POR).

2: The auxiliary clock postscaler must be configured to divide-by-1 (APSTSCLR<2:0> = 111) for proper operation of the PWM module.

#### 8.6 Fail-Safe Clock Monitor (FSCM)

The Fail-Safe Clock Monitor (FSCM) allows the device to continue to operate, even in the event of an oscillator failure. The FSCM function is enabled by programming. If the FSCM function is enabled, the LPRC internal oscillator runs at all times (except during Sleep mode) and is not subject to control by the Watchdog Timer.

In the event of an oscillator failure, the FSCM generates a clock failure trap event and switches the system clock over to the FRC oscillator. Then, the application program can either attempt to restart the oscillator or execute a controlled shutdown. The trap can be treated as a warm Reset by simply loading the Reset address into the oscillator fail trap vector.

If the PLL multiplier is used to scale the system clock, the internal FRC is also multiplied by the same factor on clock failure. Essentially, the device switches to FRC with PLL on a clock failure.

#### 8.7 Pseudo-Random Generator

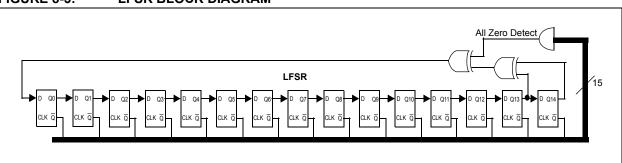

The pseudo-random generator is implemented with a 15-bit Linear Feedback Shift Register (LFSR), which is a shift register with a few exclusive OR gates. The shift register is clocked by the PWM clock and is a read-only register. The purpose of this feature is to provide the ability to randomly change the period or the active portion of the PWM.

A firmware routine can be used to read "n" random bits from the LFSR register and combine them, by either summing or performing another logical operation with the PWM period of the Duty Cycle registers. The result will be a PWM signal whose nominal period (or duty cycle) is the desired one, but whose effective value changes randomly. This capability will help in reducing the EMI/EMC emissions by spreading the power over a wider frequency range.

Figure 8-3 provides a block diagram of the LFSR.

FIGURE 8-3: LFSR BLOCK DIAGRAM

#### REGISTER 10-14: RPINR33: PERIPHERAL PIN SELECT INPUT REGISTER 33

| U-0    | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1   | R/W-1 | R/W-1 |

|--------|-----|-------|-------|-------|---------|-------|-------|

| _      | _   |       |       | SYNCI | 1R<5:0> |       |       |

| bit 15 |     |       |       |       |         |       | bit 8 |

| U-0   | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1  | R/W-1 | R/W-1 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| _     | _   |       |       | FLT8  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-8 SYNCI1R<5:0>: Assign PWM Master Time Base External Synchronization Signal to the

Corresponding RPn Pin bits

111111 = Input tied to Vss 100011 = Input tied to RP35

100011 = Input tied to RP35 100010 = Input tied to RP34

100001 = Input tied to RP33

100000 = Input tied to RP32

•

•

•

00000 = Input tied to RP0

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 FLT8R<5:0>: Assign PWM Fault Input 8 (FLT8) to the Corresponding RPn Pin bits

111111 = Input tied to Vss

100011 = Input tied to RP35

100010 = Input tied to RP34

100001 = Input tied to RP33

100000 = Input tied to RP32

•

•

00000 = Input tied to RP0

#### REGISTER 16-3: SPIXCON2: SPIX CONTROL REGISTER 2

| R/W-0  | R/W-0  | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|--------|--------|-----|-----|-----|-----|-------|

| FRMEN  | SPIFSD | FRMPOL | _   | _   | _   | _   | _     |

| bit 15 |        |        |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  | U-0   |

|-------|-----|-----|-----|-----|-----|--------|-------|

| _     | _   | _   | _   | _   | _   | FRMDLY | _     |

| bit 7 |     |     |     |     |     |        | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 FRMEN: Framed SPIx Support bit

1 = Framed SPIx support enabled ( $\overline{SSx}$  pin used as Frame Sync pulse input/output)

0 = Framed SPIx support disabled

bit 14 SPIFSD: Frame Sync Pulse Direction Control bit

1 = Frame Sync pulse input (slave)0 = Frame Sync pulse output (master)

bit 13 FRMPOL: Frame Sync Pulse Polarity bit

1 = Frame Sync pulse is active-high0 = Frame Sync pulse is active-low

bit 12-2 Unimplemented: Read as '0'

bit 1 FRMDLY: Frame Sync Pulse Edge Select bit

1 = Frame Sync pulse coincides with first bit clock0 = Frame Sync pulse precedes first bit clock

bit 0 **Unimplemented:** This bit must not be set to '1' by the user application

#### REGISTER 19-5: ADCPC0: ADC CONVERT PAIR CONTROL REGISTER 0

| R/W-0  | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 |

|--------|-------|--------|-------|-------|-------------|-------|-------|

| IRQEN1 | PEND1 | SWTRG1 |       |       | TRGSRC1<4:0 | >     |       |

| bit 15 |       |        |       |       |             |       | bit 8 |

| R/W-0  | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 |

|--------|-------|--------|-------|-------|-------------|-------|-------|

| IRQEN0 | PEND0 | SWTRG0 |       |       | TRGSRC0<4:0 | >     |       |

| bit 7  |       |        |       |       |             |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15 IRQEN1: Interrupt Request Enable 1 bit

1 = Enables IRQ generation when requested conversion of channels AN3 and AN2 is completed

0 = IRQ is not generated

bit 14 PEND1: Pending Conversion Status 1 bit

1 = Conversion of channels AN3 and AN2 is pending; set when selected trigger is asserted

0 = Conversion is complete

bit 13 SWTRG1: Software Trigger 1 bit

1 = Starts conversion of AN3 and AN2 (if selected by the TRGSRCx bits)<sup>(1)</sup> This bit is automatically cleared by hardware when the PEND1 bit is set.

0 = Conversion has not started

bit 12-8 TRGSRC1<4:0>: Trigger 1 Source Selection bits

Selects trigger source for conversion of analog channels AN3 and AN2.

11111 = Timer2 period match

•

11011 = Reserved

11010 = PWM Generator 4 current-limit ADC trigger

11001 **= Reserved**

11000 = PWM Generator 2 current-limit ADC trigger

10111 = PWM Generator 1 current-limit ADC trigger

10110 = Reserved

•

•

10010 = Reserved

10001 = PWM Generator 4 secondary trigger is selected

10000 = Reserved

01111 = PWM Generator 2 secondary trigger is selected

01110 = PWM Generator 1 secondary trigger is selected

01101 = Reserved

01100 = Timer1 period match

•

01000 = Reserved

00111 = PWM Generator 4 primary trigger is selected

00110 = Reserved

00101 = PWM Generator 2 primary trigger is selected

00100 = PWM Generator 1 primary trigger is selected

00011 = PWM Special Event Trigger is selected

00010 = Global software trigger is selected

00001 = Individual software trigger is selected

00000 = No conversion is enabled

**Note 1:** The trigger source must be set as a global software trigger prior to setting this bit to '1'. If other conversions are in progress, then conversion will be performed when the conversion resources are available.

TABLE 23-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Base<br>Instr<br># | Assembly<br>Mnemonic |                  | Assembly Syntax                    | Description                                    | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|------------------|------------------------------------|------------------------------------------------|---------------|----------------|--------------------------|

| 48                 | MPY                  | MPY<br>Wm*Wn,A   | cc, Wx, Wxd, Wy, Wyd               | Multiply Wm by Wn to Accumulator               | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | MPY<br>Wm*Wm, A  | cc,Wx,Wxd,Wy,Wyd                   | Square Wm to Accumulator                       | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 49                 | MPY.N                | MPY.N<br>Wm*Wn,A | cc, Wx, Wxd, Wy, Wyd               | -(Multiply Wm by Wn) to Accumulator            | 1             | 1              | None                     |

| 50                 | MSC                  | MSC              | Wm*Wm, Acc, Wx, Wxd, Wy, Wyd , AWB | Multiply and Subtract from Accumulator         | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 51                 | MUL                  | MUL.SS           | Wb, Ws, Wnd                        | {Wnd + 1, Wnd} = signed(Wb) * signed(Ws)       | 1             | 1              | None                     |

|                    |                      | MUL.SU           | Wb, Ws, Wnd                        | {Wnd + 1, Wnd} = signed(Wb) * unsigned(Ws)     | 1             | 1              | None                     |

|                    |                      | MUL.US           | Wb, Ws, Wnd                        | {Wnd + 1, Wnd} = unsigned(Wb) * signed(Ws)     | 1             | 1              | None                     |

|                    |                      | MUL.UU           | Wb, Ws, Wnd                        | {Wnd + 1, Wnd} = unsigned(Wb) * unsigned(Ws)   | 1             | 1              | None                     |

|                    |                      | MUL.SU           | Wb,#lit5,Wnd                       | {Wnd + 1, Wnd} = signed(Wb) * unsigned(lit5)   | 1             | 1              | None                     |

|                    |                      | MUL.UU           | Wb,#lit5,Wnd                       | {Wnd + 1, Wnd} = unsigned(Wb) * unsigned(lit5) | 1             | 1              | None                     |

|                    |                      | MUL              | f                                  | W3:W2 = f * WREG                               | 1             | 1              | None                     |

| 52                 | NEG                  | NEG              | Acc                                | Negate Accumulator                             | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | NEG              | f                                  | $f = \overline{f} + 1$                         | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | NEG              | f,WREG                             | WREG = <del>f</del> + 1                        | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | NEG              | Ws,Wd                              | Wd = Ws + 1                                    | 1             | 1              | C,DC,N,OV,Z              |

| 53                 | NOP                  | NOP              |                                    | No Operation                                   | 1             | 1              | None                     |

|                    |                      | NOPR             |                                    | No Operation                                   | 1             | 1              | None                     |

| 54                 | POP                  | POP              | f                                  | Pop f from Top-of-Stack (TOS)                  | 1             | 1              | None                     |

|                    |                      | POP              | Wdo                                | Pop from Top-of-Stack (TOS) to Wdo             | 1             | 1              | None                     |

|                    |                      | POP.D            | Wnd                                | Pop from Top-of-Stack (TOS) to W(nd):W(nd + 1) | 1             | 2              | None                     |

|                    |                      | POP.S            |                                    | Pop Shadow Registers                           | 1             | 1              | All                      |

| 55                 | PUSH                 | PUSH             | f                                  | Push f to Top-of-Stack (TOS)                   | 1             | 1              | None                     |

|                    |                      | PUSH             | Wso                                | Push Wso to Top-of-Stack (TOS)                 | 1             | 1              | None                     |

|                    |                      | PUSH.D           | Wns                                | Push W(ns):W(ns + 1) to Top-of-Stack (TOS)     | 1             | 2              | None                     |

|                    |                      | PUSH.S           |                                    | Push Shadow Registers                          | 1             | 1              | None                     |

| 56                 | PWRSAV               | PWRSAV           | #lit1                              | Go into Sleep or Idle mode                     | 1             | 1              | WDTO,Sleep               |

| 57                 | RCALL                | RCALL            | Expr                               | Relative Call                                  | 1             | 2              | None                     |

|                    |                      | RCALL            | Wn                                 | Computed Call                                  | 1             | 2              | None                     |

| 58                 | REPEAT               | REPEAT           | #lit14                             | Repeat Next Instruction lit14 + 1 times        | 1             | 1              | None                     |

|                    |                      | REPEAT           | Wn                                 | Repeat Next Instruction (Wn) + 1 times         | 1             | 1              | None                     |

| 59                 | RESET                | RESET            |                                    | Software Device Reset                          | 1             | 1              | None                     |

| 60                 | RETFIE               | RETFIE           |                                    | Return from interrupt                          | 1             | 3 (2)          | None                     |

| 61                 | RETLW                | RETLW            | #lit10,Wn                          | Return with Literal in Wn                      | 1             | 3 (2)          | None                     |

| 62                 | RETURN               | RETURN           |                                    | Return from Subroutine                         | 1             | 3 (2)          | None                     |

| 63                 | RLC                  | RLC              | f                                  | f = Rotate Left through Carry f                | 1             | 1              | C,N,Z                    |

|                    |                      | RLC              | f,WREG                             | WREG = Rotate Left through Carry f             | 1             | 1              | C,N,Z                    |

|                    |                      | RLC              | Ws,Wd                              | Wd = Rotate Left through Carry Ws              | 1             | 1              | C,N,Z                    |

| 64                 | RLNC                 | RLNC             | f                                  | f = Rotate Left (No Carry) f                   | 1             | 1              | N,Z                      |

|                    |                      | RLNC             | f,WREG                             | WREG = Rotate Left (No Carry) f                | 1             | 1              | N,Z                      |

|                    |                      | RLNC             | Ws,Wd                              | Wd = Rotate Left (No Carry) Ws                 |               | 1              | N,Z                      |

| 65                 | RRC                  | RRC              | f                                  | f = Rotate Right through Carry f               | 1             | 1              | C,N,Z                    |

|                    |                      | RRC              | f,WREG                             | WREG = Rotate Right through Carry f            | 1             | 1              | C,N,Z                    |

|                    |                      | RRC              | Ws,Wd                              | Wd = Rotate Right through Carry Ws             | 1             | 1              | C,N,Z                    |

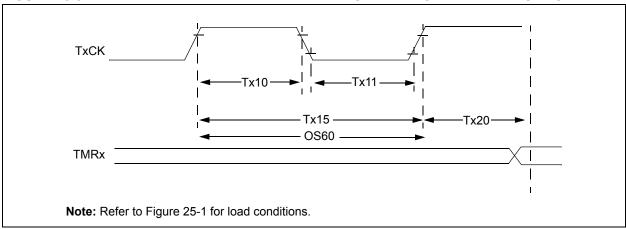

FIGURE 25-5: TIMER1 AND TIMER2 EXTERNAL CLOCK TIMING CHARACTERISTICS

TABLE 25-23: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS<sup>(1)</sup>

| AC CHA    | ARACTERIST   | гісѕ                                                                                      |                             | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |      |               |                       |                                          |  |

|-----------|--------------|-------------------------------------------------------------------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|-----------------------|------------------------------------------|--|

| Param.    | Symbol       | Chara                                                                                     | acteristic                  | Min.                                                                                                                                                                                                                                             | Тур. | Max.          | Units                 | Conditions                               |  |

| TA10 TTXH |              | TxCK High<br>Time                                                                         | Synchronous, no prescaler   | Tcy + 20                                                                                                                                                                                                                                         |      | _             | ns                    | Must also meet Parameter TA15,           |  |

|           |              | Synchronous, with prescaler                                                               | (Tcy + 20)/N                |                                                                                                                                                                                                                                                  | _    | ns            | N = prescale<br>value |                                          |  |

|           |              |                                                                                           | Asynchronous                | 20                                                                                                                                                                                                                                               | _    | _             | ns                    | (1, 8, 64, 256)                          |  |

| TA11      | TA11 TTXL TX |                                                                                           | Synchronous, no prescaler   | Tcy + 20                                                                                                                                                                                                                                         | _    | _             | ns                    | Must also meet Parameter TA15,           |  |

|           |              |                                                                                           | Synchronous, with prescaler | (Tcy + 20)/N                                                                                                                                                                                                                                     | _    | _             | ns                    | N = prescale<br>value                    |  |

|           |              |                                                                                           | Asynchronous                | 20                                                                                                                                                                                                                                               | _    | _             | ns                    | (1, 8, 64, 256)                          |  |

| TA15      | ТтхР         | TxCK Input   Synchronous   Period   no prescaler                                          |                             | 2 Tcy + 40                                                                                                                                                                                                                                       | _    | _             | ns                    |                                          |  |

|           |              |                                                                                           | Synchronous, with prescaler | Greater of:<br>40 ns or<br>(2 Tcy + 40)/N                                                                                                                                                                                                        | _    | _             | _                     | N = prescale<br>value<br>(1, 8, 64, 256) |  |

|           |              |                                                                                           | Asynchronous                | 40                                                                                                                                                                                                                                               | _    | _             | ns                    |                                          |  |

| OS60      | Ft1          | T1CK Oscillator Input Frequency Range (oscillator enabled by setting bit, TCS (T1CON<1>)) |                             | DC                                                                                                                                                                                                                                               | _    | 50            | kHz                   |                                          |  |

| TA20      | TCKEXTMRL    | Delay from E<br>Clock Edge                                                                | External TxCK<br>to Timer   | 0.75 Tcy + 40                                                                                                                                                                                                                                    | _    | 1.75 Tcy + 40 | _                     |                                          |  |

Note 1: Timer1 is a Type A.

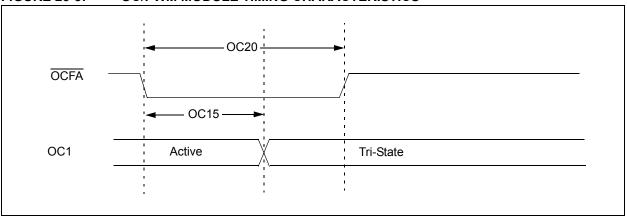

FIGURE 25-8: OC/PWM MODULE TIMING CHARACTERISTICS

TABLE 25-27: SIMPLE OC/PWM MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                               | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |   |          |    |  |  |

|--------------------|--------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------|----|--|--|

| Param.             | Symbol | Characteristic <sup>(1)</sup> | Min. Typ. Max. Units Conditions                                                                                                                                                                                                                     |   |          |    |  |  |

| OC15               | TFD    | Fault Input to PWM I/O Change | _                                                                                                                                                                                                                                                   | _ | Tcy + 20 | ns |  |  |

| OC20               | TFLT   | Fault Input Pulse Width       | Tcy + 20                                                                                                                                                                                                                                            | _ |          | ns |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

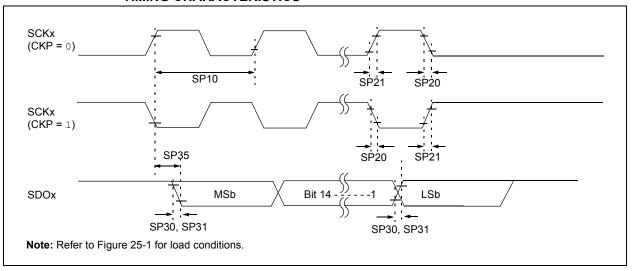

TABLE 25-29: SPIx MAXIMUM DATA/CLOCK RATE SUMMARY

| AC CHARA             | CTERISTICS                               |                                             | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |     |     |     |  |

|----------------------|------------------------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)                                                                                                                                                                                                       | CKE | СКР | SMP |  |

| 15 MHz               | Table 25-30                              | _                                           | _                                                                                                                                                                                                                                                | 0,1 | 0,1 | 0,1 |  |

| 9 MHz                |                                          | Table 25-31                                 |                                                                                                                                                                                                                                                  | 1   | 0,1 | 1   |  |

| 9 MHz                |                                          | Table 25-32                                 |                                                                                                                                                                                                                                                  | 0   | 0,1 | 1   |  |

| 15 MHz               | 1                                        |                                             | Table 25-33                                                                                                                                                                                                                                      | 1   | 0   | 0   |  |

| 11 MHz               |                                          |                                             | Table 25-34                                                                                                                                                                                                                                      | 1   | 1   | 0   |  |

| 15 MHz               |                                          | _                                           | Table 25-35                                                                                                                                                                                                                                      | 0   | 1   | 0   |  |

| 11 MHz               | _                                        | _                                           | Table 25-36                                                                                                                                                                                                                                      | 0   | 0   | 0   |  |

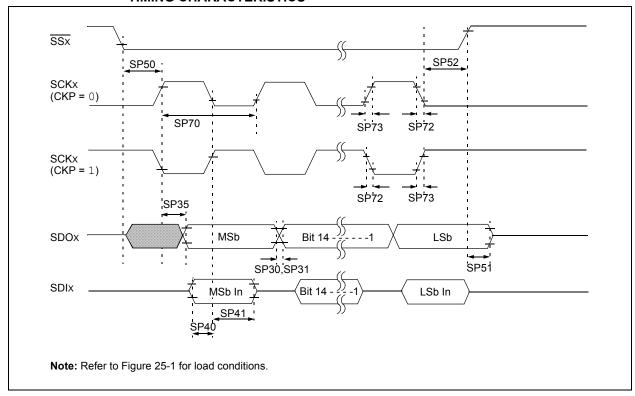

FIGURE 25-11: SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS

FIGURE 25-18: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

| dsPIC33FJ06GS001/101A/102A/202A and dsPIC33FJ09GS302 |

|------------------------------------------------------|

| NOTES:                                               |

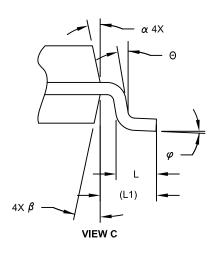

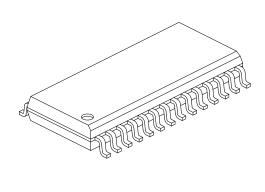

### 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units     | MILLIMETERS |           |      |  |

|--------------------------|-----------|-------------|-----------|------|--|

| Dimension                | Limits    | MIN         | NOM       | MAX  |  |

| Number of Pins           | N         | 28          |           |      |  |

| Pitch                    | е         | 1.27 BSC    |           |      |  |

| Overall Height           | Α         | -           | -         | 2.65 |  |

| Molded Package Thickness | A2        | 2.05        | -         | -    |  |

| Standoff §               | A1        | 0.10        | -         | 0.30 |  |

| Overall Width            | Е         |             | 10.30 BSC |      |  |

| Molded Package Width     | E1        | 7.50 BSC    |           |      |  |

| Overall Length           | D         | 17.90 BSC   |           |      |  |

| Chamfer (Optional)       | h         | 0.25        | -         | 0.75 |  |

| Foot Length              | L         | 0.40        | 1         | 1.27 |  |

| Footprint                | L1        | 1.40 REF    |           |      |  |

| Lead Angle               | Θ         | 0°          | -         | -    |  |

| Foot Angle               | $\varphi$ | 0°          | -         | 8°   |  |

| Lead Thickness           | С         | 0.18        | -         | 0.33 |  |

| Lead Width               | b         | 0.31        | -         | 0.51 |  |

| Mold Draft Angle Top     | α         | 5°          | -         | 15°  |  |

| Mold Draft Angle Bottom  | β         | 5°          | -         | 15°  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing C04-052C Sheet 2 of 2

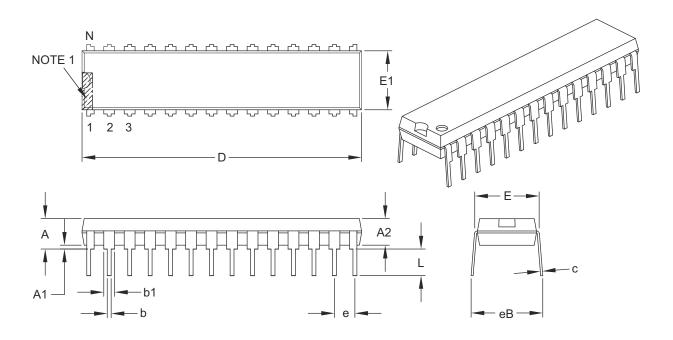

## 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    |          | INCHES |       |

|----------------------------|----------|----------|--------|-------|

| Dimension                  | n Limits | MIN      | NOM    | MAX   |

| Number of Pins             | N        |          | 28     |       |

| Pitch                      | е        | .100 BSC |        |       |

| Top to Seating Plane       | Α        | _        | _      | .200  |

| Molded Package Thickness   | A2       | .120     | .135   | .150  |

| Base to Seating Plane      | A1       | .015     | _      | _     |

| Shoulder to Shoulder Width | Е        | .290     | .310   | .335  |

| Molded Package Width       | E1       | .240     | .285   | .295  |

| Overall Length             | D        | 1.345    | 1.365  | 1.400 |

| Tip to Seating Plane       | L        | .110     | .130   | .150  |

| Lead Thickness             | С        | .008     | .010   | .015  |

| Upper Lead Width           | b1       | .040     | .050   | .070  |

| Lower Lead Width           | b        | .014     | .018   | .022  |

| Overall Row Spacing §      | eB       | -        | _      | .430  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

| RPINR7 (Peripheral Pin Select Input 7)     | 157  | High-Speed PWM Generator 2 for                     |      |

|--------------------------------------------|------|----------------------------------------------------|------|

| RPOR0 (Peripheral Pin Select Output 0)     | 168  | dsPIC33FJ06GS102A, dsPIC33FJ06GS202A,              |      |

| RPOR1 (Peripheral Pin Select Output 1)     | 168  | dsPIC33FJ09GS302                                   | 53   |

| RPOR16 (Peripheral Pin Select Output 16)   | 172  | High-Speed PWM Generator 4 for dsPIC33FJ06GS00     | )1,  |

| RPOR17 (Peripheral Pin Select Output 17)   | 172  | dsPIC33FJ06GS101A, dsPIC33FJ09GS302                | 54   |

| RPOR2 (Peripheral Pin Select Output 2)     |      | I2C1                                               |      |

| RPOR3 (Peripheral Pin Select Output 3)     |      | Input Capture for dsPIC33FJ06GS202A,               |      |

| RPOR4 (Peripheral Pin Select Output 4)     |      | dsPIC33FJ09GS302                                   | 5    |

| RPOR5 (Peripheral Pin Select Output 5)     |      | Interrupt Controller for dsPIC33FJ06GS001          |      |

| RPOR6 (Peripheral Pin Select Output 6)     |      | Interrupt Controller for dsPIC33FJ06GS002A         | 48   |

| RPOR7 (Peripheral Pin Select Output 7)     |      | Interrupt Controller for dsPIC33FJ06GS101A         |      |

|                                            |      |                                                    |      |

| SDCx (PWMx Secondary Duty Cycle)           |      | Interrupt Controller for dsPIC33FJ06GS202A         |      |

| SEVTCMP (PWM Special Event Compare)        |      | Interrupt Controller for dsPIC33FJ09GS302          |      |

| SPHASEx (PWMx Secondary Phase Shift)       |      | NVM                                                | 63   |

| SPIxCON1 (SPIx Control 1)                  |      | Output Compare for dsPIC33FJ06GS101A,              |      |

| SPIxCON2 (SPIx Control 2)                  |      | dsPIC33FJ06GS102A, dsPIC33FJ06GS202A,              |      |

| SPIxSTAT (SPIx Status and Control)         | 207  | dsPIC33FJ09GS302                                   | 5′   |

| SR (CPU STATUS)                            | 91   | Peripheral Pin Select Input for dsPIC33FJ06GS001   | 59   |

| SR (CPU Status)                            | 28   | Peripheral Pin Select Input for dsPIC33FJ06GS101A, |      |

| STRIGx (PWMx Secondary Trigger             |      | dsPIC33FJ06GS102A                                  | 59   |

| Compare Value)                             | 201  | Peripheral Pin Select Input for dsPIC33FJ06GS202A, |      |

| T1CON (Timer1 Control)                     |      | dsPIC33FJ09GS302                                   | 60   |

| T2CON (Timer2 Control)                     |      | Peripheral Pin Select Output for dsPIC33FJ06GS001, |      |

|                                            |      | dsPIC33FJ06GS101A                                  |      |

| TRGCONx (PWMx Trigger Control)             |      |                                                    |      |

| TRIGx (PWMx Primary Trigger Compare Value) |      | Peripheral Pin Select Output for dsPIC33FJ06GS102A |      |

| U1MODE (UART1 Mode)                        |      | dsPIC33FJ06GS202A, dsPIC33FJ09GS302                |      |

| U1STA (UART1 Status and Control)           | 223  | PMD for dsPIC33FJ06GS001                           |      |

| Reset                                      |      | PMD for dsPIC33FJ06GS101A                          |      |

| Brown-out Reset (BOR)                      |      | PMD for dsPIC33FJ06GS102A                          |      |

| Configuration Mismatch Reset (CM)          | 79   | PMD for dsPIC33FJ06GS202A                          | . 65 |

| Illegal Condition Device Reset (IOPUWR)    | 79   | PMD for dsPIC33FJ09GS302                           | . 65 |

| Illegal Opcode                             | 79   | PORTA                                              | . 62 |

| Security                                   |      | PORTB for dsPIC33FJ06GS001,                        |      |

| Uninitialized W Register                   |      | dsPIC33FJ06GS101A                                  | 62   |

| Illegal Device Reset                       |      | PORTB for dsPIC33FJ06GS102A,                       |      |

| Illegal Opcode                             |      | dsPIC33FJ06GS202A, dsPIC33FJ09GS302                | 62   |

| Master Clear Reset (MCLR)                  |      | SPI1 for dsPIC33FJ06GS101A, dsPIC33FJ06GS102A      |      |

| Power-on Reset (POR)                       |      |                                                    |      |

|                                            |      | dsPIC33FJ09GS202A, dsPIC33FJ09GS302                |      |

| Power-up Timer Reset (PWRT)                |      | System Control                                     |      |

| Software RESET Instruction                 | 79   | Timers                                             | 5    |

| System Reset                               |      | UART1 for dsPIC33FJ06GS101A,                       |      |

| Cold Reset                                 |      | dsPIC33FJ06GS102A, dsPIC33FJ06GS202A,              |      |

| Warm Reset                                 |      | dsPIC33FJ09GS302                                   |      |

| Trap Conflict                              | 85   | Software RESET Instruction (SWR)                   |      |

| Trap Conflict Reset (TRAPR)                | 79   | Software Simulator (MPLAB SIM)                     | 269  |

| Uninitialized W Register                   | 85   | Software Stack Pointer, Frame Pointer              |      |

| Watchdog Timer Out Reset (WDTO)            |      | CALL Stack Frame                                   | . 66 |

| Reset Sequence                             |      | Symbols Used in Opcode Descriptions                |      |

| Revision History                           |      | -,                                                 |      |

| toviolon rilotory                          |      | T                                                  |      |

| S                                          |      | Thermal Packaging Characteristics                  | 272  |

| Serial Peripheral Interface (SPI)          | 205  | Timer1                                             |      |

|                                            | 203  | Timer2                                             |      |

| SFR Maps                                   |      |                                                    | 175  |

| Change Notification for                    |      | Timing Diagrams                                    |      |

| dsPIC33FJ06GS001, dsPIC33FJ06GS101         | A 45 | Analog-to-Digital Conversion per Input             |      |

| Change Notification for dsPIC33FJ06GS102A, |      | Brown-out Situations                               |      |

| dsPIC33FJ06GS202A, dsPIC33FJ09GS30         | 245  | External Clock                                     | 283  |

| Constant Current Source                    | 56   | High-Speed PWM                                     | 292  |

| CPU Core                                   | 43   | High-Speed PWM Fault                               | 292  |

| High-Speed 10-Bit ADC for dsPIC33FJ06GS001 | 1,   | I/O                                                |      |

| dsPIC33FJ06GS101A                          |      | I2C1 Bus Data (Master Mode)                        |      |

| High-Speed 10-Bit ADC for dsPIC33FJ06GS102 |      | I2C1 Bus Data (Slave Mode)                         |      |

| dsPIC33FJ06GS202A                          |      | I2C1 Bus Start/Stop Bits (Master Mode)             |      |

| High-Speed 10-Bit ADC for dsPIC33FJ09GS302 |      | I2C1 Bus Start/Stop Bits (Slave Mode)              |      |

| • .                                        |      | Input Capture (CAP1)                               |      |

| High-Speed PWM Congretor 1                 |      |                                                    |      |

| High-Speed PWM Generator 1                 |      | OC/PWM                                             | ∠9   |