Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 9KB (3K x 24)                                                                   |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 8x10b; D/A 2x10b                                                            |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 36-VFTLA Exposed Pad                                                            |

| Supplier Device Package    | 36-VTLA (5x5)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj09gs302-e-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

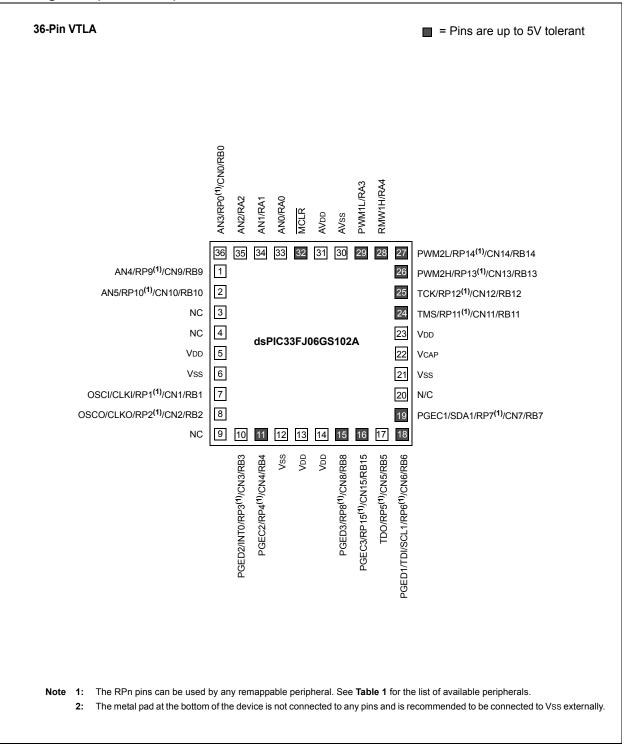

### Pin Diagrams (Continued)

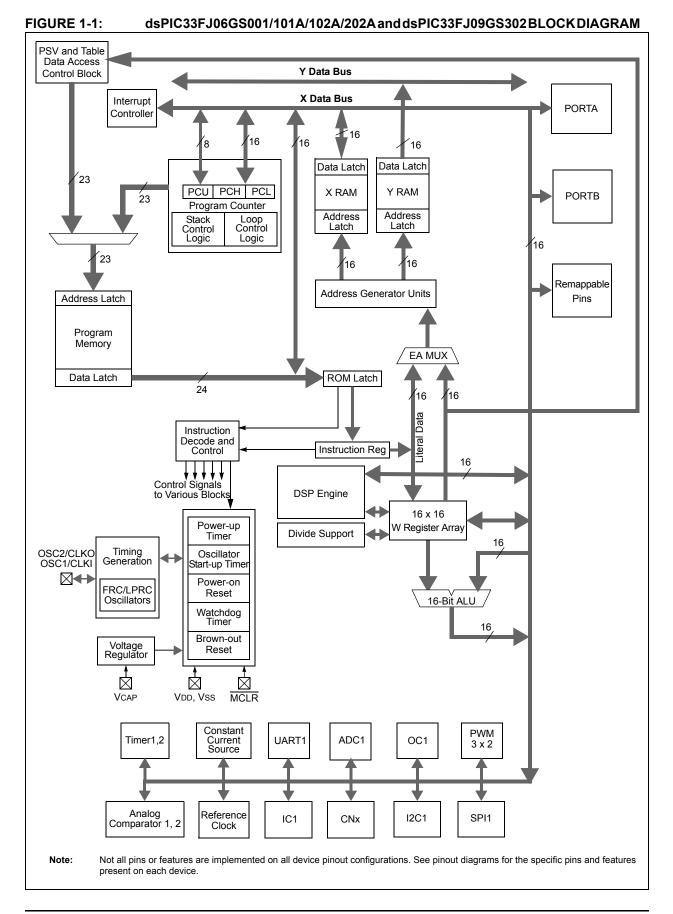

### 3.5 Arithmetic Logic Unit (ALU)

The ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the *"16-Bit MCU and DSC Programmer's Reference Manual"* (DS70157) for information on the SR bits affected by each instruction.

The CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

### 3.5.1 MULTIPLIER

Using the high-speed, 17-bit x 17-bit multiplier of the DSP engine, the ALU supports unsigned, signed or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

### 3.5.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/ 16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

### 3.6 DSP Engine

The DSP engine consists of a high-speed, 17-bit x 17-bit multiplier, a barrel shifter and a 40-bit adder/subtracter (with two target accumulators, round and saturation logic).

The dsPIC33FJ06GS001/101A/102A/202A and dsPIC33FJ09GS302 devices feature a single-cycle instruction flow architecture; therefore, concurrent operation of the DSP engine with MCU instruction flow is not possible. However, some MCU ALU and DSP engine resources can be used concurrently by the same instruction (for example, ED, EDAC).

The DSP engine can also perform inherent accumulator-to-accumulator operations that require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON), as listed below:

- Fractional or Integer DSP Multiply (IF)

- Signed or Unsigned DSP Multiply (US)

- Conventional or Convergent Rounding (RND)

- Automatic Saturation On/Off for ACCA (SATA)

- Automatic Saturation On/Off for ACCB (SATB)

- Automatic Saturation On/Off for Writes to Data Memory (SATDW)

- Accumulator Saturation mode Selection (ACCSAT)

A block diagram of the DSP engine is shown in Figure 3-3.

| SUMMARY     |                        |                   |  |  |  |  |  |  |  |  |  |

|-------------|------------------------|-------------------|--|--|--|--|--|--|--|--|--|

| Instruction | Algebraic<br>Operation | ACC Write<br>Back |  |  |  |  |  |  |  |  |  |

| CLR         | A = 0                  | Yes               |  |  |  |  |  |  |  |  |  |

| ED          | $A = (x - y)^2$        | No                |  |  |  |  |  |  |  |  |  |

| EDAC        | $A = A + (x - y)^2$    | No                |  |  |  |  |  |  |  |  |  |

| MAC         | A = A + (x * y)        | Yes               |  |  |  |  |  |  |  |  |  |

| MAC         | $A = A + x^2$          | No                |  |  |  |  |  |  |  |  |  |

| MOVSAC      | No change in A         | Yes               |  |  |  |  |  |  |  |  |  |

| MPY         | A = x * y              | No                |  |  |  |  |  |  |  |  |  |

| MPY         | $A = x^2$              | No                |  |  |  |  |  |  |  |  |  |

| MPY.N       | A = -x * y             | No                |  |  |  |  |  |  |  |  |  |

| MSC         | A = A - x * y          | Yes               |  |  |  |  |  |  |  |  |  |

### TABLE 3-1: DSP INSTRUCTIONS SUMMARY

NOTES:

### 4.2.5 X AND Y DATA SPACES

The core has two data spaces, X and Y. These data spaces can be considered either separate (for some DSP instructions), or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms, such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X data space is used by all instructions and supports all addressing modes. X data space has separate read and write data buses. The X read data bus is the read data path for all instructions that view data space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y data space is used in concert with the X data space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y data spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X data space.

All data memory writes, included in DSP instructions, view data space as combined X and Y address space. The boundary between the X and Y data spaces is device-dependent and is not user-programmable.

All Effective Addresses are 16 bits wide and point to bytes within the data space. Therefore, the data space address range is 64 Kbytes, or 32K words, though the implemented memory locations vary by device.

| IABLE        | E 4-6: INTERRUPT CONTROLLER REGISTER MAP FOR 05PIC33FJ06G5102A DEVICES ONLY |         |         |            |         |         |            |            |       |          |         |           |         |             |        |              |               |               |

|--------------|-----------------------------------------------------------------------------|---------|---------|------------|---------|---------|------------|------------|-------|----------|---------|-----------|---------|-------------|--------|--------------|---------------|---------------|

| File<br>Name | SFR<br>Addr.                                                                | Bit 15  | Bit 14  | Bit 13     | Bit 12  | Bit 11  | Bit 10     | Bit 9      | Bit 8 | Bit 7    | Bit 6   | Bit 5     | Bit 4   | Bit 3       | Bit 2  | Bit 1        | Bit 0         | All<br>Resets |

| INTCON1      | 0080                                                                        | NSTDIS  | OVAERR  | OVBERR     | COVAERR | COVBERR | OVATE      | OVBTE      | COVTE | SFTACERR | DIV0ERR | _         | MATHERR | ADDRERR     | STKERR | OSCFAIL      | _             | 0000          |

| INTCON2      | 0082                                                                        | ALTIVT  | DISI    | _          |         | _       |            | —          |       | _        | _       | I         | _       | _           | INT2EP | INT1EP       | INT0EP        | 0000          |

| IFS0         | 0084                                                                        | _       | _       | ADIF       | U1TXIF  | U1RXIF  | SPI1IF     | SPI1EIF    |       | T2IF     |         | I         | _       | T1IF        | OC1IF  | _            | <b>INT0IF</b> | 0000          |

| IFS1         | 0086                                                                        | _       | _       | INT2IF     | _       | —       | _          | —          | _     | _        | _       | _         | INT1IF  | CNIF        | _      | MI2C1IF      | SI2C1IF       | 0000          |

| IFS3         | 008A                                                                        | —       | _       | _          | _       | —       | _          | PSEMIF     | _     | _        | _       | _         | _       | _           | _      | _            | —             | 0000          |

| IFS4         | 008C                                                                        | _       | _       | _          | _       | _       | _          | —          | _     | _        | _       | _         | _       | _           | _      | U1EIF        | _             | 0000          |

| IFS5         | 008E                                                                        | PWM2IF  | PWM1IF  | _          | _       | _       | _          | —          | _     | _        | _       | _         | _       | _           | _      | _            | JTAGIF        | 0000          |

| IFS6         | 0090                                                                        | ADCP1IF | ADCP0IF | _          | _       | _       | _          | —          | _     | _        | _       | _         | _       | _           | _      | _            | _             | 0000          |

| IFS7         | 0092                                                                        | _       | _       | _          | _       | _       | _          | —          | _     | _        | _       | _         | _       | _           | _      | _            | ADCP2IF       | 0000          |

| IEC0         | 0094                                                                        | _       | _       | ADIE       | U1TXIE  | U1RXIE  | SPI1IE     | SPI1EIE    | _     | T2IE     | _       | _         | _       | T1IE        | OC1IE  | _            | INT0IE        | 0000          |

| IEC1         | 0096                                                                        | _       | _       | INT2IE     | _       | _       | _          | —          | _     | _        | _       | _         | INT1IE  | CNIE        | _      | MI2C1IE      | SI2C1IE       | 0000          |

| IEC3         | 009A                                                                        | _       | _       | _          | _       | _       | _          | PSEMIE     | _     | _        | _       | _         | _       | _           | _      | _            | _             | 0000          |

| IEC4         | 009C                                                                        | _       | _       | _          | _       | _       | _          | —          | _     | _        | _       | _         | _       | _           | _      | U1EIE        | _             | 0000          |

| IEC5         | 009E                                                                        | PWM2IE  | PWM1IE  | _          | _       | _       | _          | —          | _     | _        | _       | _         | _       | _           | _      | _            | JTAGIE        | 0000          |

| IEC6         | 00A0                                                                        | ADCP1IE | ADCP0IE | _          | _       | _       | _          | —          | _     | _        | _       | _         | _       | _           | _      | _            | _             | 0000          |

| IEC7         | 00A2                                                                        | —       | —       | —          |         | —       |            | —          |       | —        | _       |           | —       | —           |        |              | ADCP2IE       | 0000          |

| IPC0         | 00A4                                                                        | —       |         | T1IP<2:0>  |         | —       | C          | OC1IP<2:0  | >     | —        |         |           | —       | INT0IP<2:0> |        |              | 4404          |               |

| IPC1         | 00A6                                                                        | —       |         | T2IP<2:0>  |         | —       |            | —          |       | —        | _       |           | —       | —           |        |              |               | 4000          |

| IPC2         | 00A8                                                                        | —       |         | U1RXIP<2:0 | >       | —       | <b>u</b> , | SPI1IP<2:0 | >     | —        | SI      | PI1EIP<2  | :0>     | —           |        |              |               | 4440          |

| IPC3         | 00AA                                                                        | —       | —       | —          |         | —       |            | —          |       |          |         | ADIP<2:0  | >       | —           | ι      | J1TXIP<2:0>  |               | 0044          |

| IPC4         | 00AC                                                                        | —       |         | CNIP<2:0>  |         | —       |            | —          |       | —        | М       | I2C1IP<2  | :0>     | —           | S      | SI2C1IP<2:0> | •             | 4044          |

| IPC5         | 00AE                                                                        | —       | —       | —          |         | —       |            | —          |       | —        | _       |           | —       | —           | l      | NT1IP<2:0>   |               | 0004          |

| IPC7         | 00B2                                                                        | —       | —       | —          | -       | —       | -          | —          | _     | —        | II      | NT2IP<2:  | 0>      | —           | —      | -            | _             | 0040          |

| IPC14        | 00C0                                                                        | —       | —       | —          | -       | —       | -          | —          | _     | —        | P       | SEMIP<2   | :0>     | —           | —      | -            | _             | 0040          |

| IPC16        | 00C4                                                                        | _       | _       | —          |         | —       |            | —          |       | —        | ι       | J1EIP<2:( | )>      | —           | _      |              |               | 0040          |

| IPC20        | 00CC                                                                        | _       | _       | —          |         | —       |            | —          |       | —        | _       | I         | —       | —           | L.     | ITAGIP<2:0>  |               | 0004          |

| IPC23        | 00D2                                                                        | -       |         | PWM2IP<2:0 | )>      | —       | P          | WM1IP<2:   | 0>    | _        | _       |           | —       | —           | _      | _            |               | 4400          |

| IPC27        | 00DA                                                                        | -       | A       | ADCP1IP<2: | 0>      | —       | A          | DCP0IP<2:  | 0>    | _        | _       |           | —       | —           | _      | _            | —             | 4400          |

| IPC28        | 00DC                                                                        | -       | _       | —          | _       | —       | _          | —          | —     | —        | _       | _         | —       | —           | A      | DCP2IP<2:0   | >             | 0004          |

| INTTREG      | 00E0                                                                        | —       | —       | —          |         |         | ILR<       | 3:0>       |       | —        |         |           |         | VECNUM<6:   | 0>     |              |               | 0000          |

### TABLE 4-6: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33FJ06GS102A DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| IABLE 4  | -21.        | nion                                                              | SFEEL          |        |         | GISTEI |        | OK US | FICJJI | 30003         | IUZA A | UD USFIC | 33210002     | ZUZA  |       |         |       |              |

|----------|-------------|-------------------------------------------------------------------|----------------|--------|---------|--------|--------|-------|--------|---------------|--------|----------|--------------|-------|-------|---------|-------|--------------|

| SFR Name | SFR<br>Addr | Bit 15                                                            | Bit 14         | Bit 13 | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7         | Bit 6  | Bit 5    | Bit 4        | Bit 3 | Bit 2 | Bit 1   | Bit 0 | All<br>Reset |

| ADCON    | 0300        | ADON                                                              | _              | ADSIDL | SLOWCLK | _      | GSWTRG | —     | FORM   | EIE           | ORDER  | SEQSAMP  | ASYNCSAMP    | _     | A     | DCS<2:0 | >     | 0003         |

| ADPCFG   | 0302        | _                                                                 | —              | _      | —       | _      | —      | _     | _      | —             |        | PCFG5    | PCFG4        | PCFG3 | PCFG2 | PCFG1   | PCFG0 | 0000         |

| ADSTAT   | 0306        | _                                                                 | —              | _      | —       | _      | —      |       | _      | —             | P6RDY  | _        | —            | _     | P2RDY | P1RDY   | P0RDY | 0000         |

| ADBASE   | 0308        |                                                                   | ADBASE<15:1> — |        |         |        |        |       |        |               |        |          |              |       | 0000  |         |       |              |

| ADCPC0   | 030A        | IRQEN1 PEND1 SWTRG1 TRGSRC1<4:0> IRQEN0 PEND0 SWTRG0 TRGSRC0<4:0> |                |        |         |        |        |       |        | 0000          |        |          |              |       |       |         |       |              |

| ADCPC1   | 030C        | _                                                                 | —              | _      | _       | _      | —      |       | _      | IRQEN2        | PEND2  | SWTRG2   | TRGSRC2<4:0> |       |       |         | 0000  |              |

| ADCPC3   | 0310        | _                                                                 | _              | _      | _       | _      | _      | _     | _      | IRQEN6        | PEND6  | SWTRG6   | TRGSRC6<4:0> |       |       |         | 0000  |              |

| ADCBUF0  | 0320        |                                                                   |                |        |         |        |        |       | ADC D  | ata Buffer 0  | )      |          |              |       |       |         |       | XXXX         |

| ADCBUF1  | 0322        |                                                                   |                |        |         |        |        |       | ADC D  | ata Buffer 1  |        |          |              |       |       |         |       | XXXX         |

| ADCBUF2  | 0324        |                                                                   |                |        |         |        |        |       | ADC D  | ata Buffer 2  | 2      |          |              |       |       |         |       | XXXX         |

| ADCBUF3  | 0326        |                                                                   |                |        |         |        |        |       | ADC D  | ata Buffer 3  | 3      |          |              |       |       |         |       | XXXX         |

| ADCBUF4  | 0328        |                                                                   |                |        |         |        |        |       | ADC D  | ata Buffer 4  | ļ      |          |              |       |       |         |       | XXXX         |

| ADCBUF5  | 032A        |                                                                   |                |        |         |        |        |       | ADC D  | ata Buffer 5  | 5      |          |              |       |       |         |       | XXXX         |

| ADCBUF12 | 0338        |                                                                   |                |        |         |        |        |       | ADC Da | ata Buffer 12 | 2      |          |              |       |       |         |       | XXXX         |

| ADCBUF13 | 033A        |                                                                   |                |        |         |        |        |       | ADC Da | ata Buffer 1  | 3      |          |              |       |       |         |       | XXXX         |

### TABLE 4-21: HIGH-SPEED 10-BIT ADC REGISTER MAP FOR dsPIC33FJ06GS102A AND dsPIC33FJ06GS202A

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

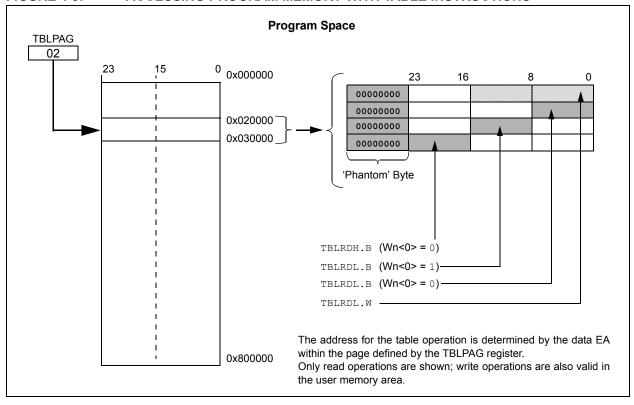

### 4.7.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>)

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when byte select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom byte', will always be '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address, in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

Similarly, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in Section 5.0 "Flash Program Memory".

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

### FIGURE 4-9: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

| REGISTER 7-26: IPC14: INTERRUPT PRIORITY CONTROL REGISTER 14 |                |                    |                 |                                    |           |     |       |  |  |  |  |  |

|--------------------------------------------------------------|----------------|--------------------|-----------------|------------------------------------|-----------|-----|-------|--|--|--|--|--|

| U-0                                                          | U-0            | U-0                | U-0             | U-0                                | U-0       | U-0 | U-0   |  |  |  |  |  |

|                                                              | —              | —                  | —               | —                                  |           |     | —     |  |  |  |  |  |

| bit 15                                                       |                |                    |                 |                                    |           |     | bit 8 |  |  |  |  |  |

|                                                              |                |                    |                 |                                    |           |     |       |  |  |  |  |  |

| U-0                                                          | R/W-1          | R/W-0              | R/W-0           | U-0                                | U-0       | U-0 | U-0   |  |  |  |  |  |

| —                                                            |                | PSEMIP<2:0>        |                 | —                                  | _         |     | —     |  |  |  |  |  |

| bit 7                                                        |                |                    |                 |                                    |           |     | bit 0 |  |  |  |  |  |

|                                                              |                |                    |                 |                                    |           |     |       |  |  |  |  |  |

| Legend:                                                      |                |                    |                 |                                    |           |     |       |  |  |  |  |  |

| R = Readat                                                   | ole bit        | W = Writable       | bit             | U = Unimplemented bit, read as '0' |           |     |       |  |  |  |  |  |

| -n = Value a                                                 | at POR         | '1' = Bit is set   |                 | '0' = Bit is cle                   | nown      |     |       |  |  |  |  |  |

|                                                              |                |                    |                 |                                    |           |     |       |  |  |  |  |  |

| bit 15-7                                                     | Unimplemen     | ted: Read as '     | 0'              |                                    |           |     |       |  |  |  |  |  |

| bit 6-4                                                      | PSEMIP<2:0     | -: PWM Specia      | al Event Match  | n Interrupt Prio                   | rity bits |     |       |  |  |  |  |  |

|                                                              | 111 = Interrup | ot is Priority 7 ( | highest priorit | y interrupt)                       |           |     |       |  |  |  |  |  |

|                                                              | •              |                    |                 |                                    |           |     |       |  |  |  |  |  |

|                                                              | •              |                    |                 |                                    |           |     |       |  |  |  |  |  |

|                                                              | •              |                    |                 |                                    |           |     |       |  |  |  |  |  |

- 001 = Interrupt is Priority 1

- 000 = Interrupt source is disabled

bit 3-0 Unimplemented: Read as '0'

### REGISTER 7-27: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| U-0     | U-0   | U-0                       | U-0   | U-0 | U-0 | U-0 | U-0   |

|---------|-------|---------------------------|-------|-----|-----|-----|-------|

| —       | —     | —                         | _     | —   | —   | —   | —     |

| bit 15  |       |                           |       |     |     |     | bit 8 |

|         |       |                           |       |     |     |     |       |

| U-0     | R/W-1 | R/W-0                     | R/W-0 | U-0 | U-0 | U-0 | U-0   |

| —       |       | U1EIP<2:0> <sup>(1)</sup> |       | —   | —   | —   | —     |

| bit 7   |       |                           |       |     |     | •   | bit 0 |

|         |       |                           |       |     |     |     |       |

| Legend: |       |                           |       |     |     |     |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                     |

|----------|----------------------------------------------------------------|

| bit 6-4  | U1EIP<2:0>: UART1 Error Interrupt Priority bits <sup>(1)</sup> |

|          | 111 = Interrupt is Priority 7 (highest priority interrupt)     |

|          | •                                                              |

|          | •                                                              |

|          | •                                                              |

|          | 001 = Interrupt is Priority 1                                  |

|          | 000 = Interrupt source is disabled                             |

| bit 3-0  | Unimplemented: Read as '0'                                     |

|          |                                                                |

**Note 1:** These bits are not implemented in the dsPIC33FJ06GS001 device.

| REGISTER 7      | -30: IPC24:    |                       |                 |                     | REGISTER 24      |                    |       |  |

|-----------------|----------------|-----------------------|-----------------|---------------------|------------------|--------------------|-------|--|

| U-0             | U-0            | U-0                   | U-0             | U-0                 | U-0              | U-0                | U-0   |  |

|                 | —              | —                     | _               | —                   | —                | —                  | _     |  |

| bit 15          |                |                       |                 |                     |                  |                    | bit 8 |  |

|                 |                |                       |                 |                     |                  |                    |       |  |

| U-0             | R/W-1          | R/W-0                 | R/W-0           | U-0                 | U-0              | U-0                | U-0   |  |

| _               |                | PWM4IP <sup>(1)</sup> |                 |                     | —                | —                  |       |  |

| bit 7           |                |                       |                 |                     |                  |                    | bit 0 |  |

|                 |                |                       |                 |                     |                  |                    |       |  |

| Legend:         |                |                       |                 |                     |                  |                    |       |  |

| R = Readable    | bit            | W = Writable          | bit             | U = Unimpler        | mented bit, read | l as '0'           |       |  |

| -n = Value at F | OR             | '1' = Bit is set      |                 | '0' = Bit is cle    | ared             | x = Bit is unknown |       |  |

|                 |                |                       |                 |                     |                  |                    |       |  |

| bit 15-7        | -              | ted: Read as '        |                 |                     |                  |                    |       |  |

| bit 6-4         | PWM4IP<2:0     | >: PWM4 Inter         | rupt Priority b | oits <sup>(1)</sup> |                  |                    |       |  |

|                 | 111 = Interrup | ot is Priority 7 (    | highest priori  | ty)                 |                  |                    |       |  |

|                 | •              |                       |                 |                     |                  |                    |       |  |

|                 | •              |                       |                 |                     |                  |                    |       |  |

|                 | •              |                       |                 |                     |                  |                    |       |  |

|                 | 001 = Interrup | ot is Priority 1      |                 |                     |                  |                    |       |  |

|                 |                | ot source is dis      | abled           |                     |                  |                    |       |  |

|                 |                |                       |                 |                     |                  |                    |       |  |

### Note 1: These bits are not implemented in dsPIC33FJ06GS102A/202A devices.

### REGISTER 16-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- - 00 = Primary prescale 64:1

- Note 1: This bit is not used in Framed SPI modes. Program this bit to '0' for the Framed SPI modes (FRMEN = 1).

- 2: Do not set both Primary and Secondary prescalers to a value of 1:1.

- **3:** This bit must be cleared when FRMEN = 1.

| R/W-0       | R/W-0                 | R/W-0                   | U-0 | R/W-0, HC             | R/W-0                  | R-0                  | R-1                 |

|-------------|-----------------------|-------------------------|-----|-----------------------|------------------------|----------------------|---------------------|

| UTXISEL1(2) | UTXINV <sup>(2)</sup> | UTXISEL0 <sup>(2)</sup> | —   | UTXBRK <sup>(2)</sup> | UTXEN <sup>(1,2)</sup> | UTXBF <sup>(2)</sup> | TRMT <sup>(2)</sup> |

| bit 15      |                       |                         |     |                       |                        |                      | bit 8               |

| R/W-0   | R/W-0                 | R/W-0                | R-1                  | R-0                 | R-0                 | R/C-0               | R-0                  |

|---------|-----------------------|----------------------|----------------------|---------------------|---------------------|---------------------|----------------------|

| URXISEL | _<1:0> <sup>(2)</sup> | ADDEN <sup>(2)</sup> | RIDLE <sup>(2)</sup> | PERR <sup>(2)</sup> | FERR <sup>(2)</sup> | OERR <sup>(2)</sup> | URXDA <sup>(2)</sup> |

| bit 7   |                       |                      |                      |                     |                     |                     | bit 0                |

| Legend:           | HC = Hardware Clearable bit | C = Clearable bit                  |                    |

|-------------------|-----------------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared               | x = Bit is unknown |

UTXISEL<1:0>: Transmission Interrupt Mode Selection bits<sup>(2)</sup> bit 15,13 11 = Reserved; do not use 10 = Interrupt when a character is transferred to the Transmit Shift Register (TSR), and as a result, the transmit buffer becomes empty 01 = Interrupt when the last character is shifted out of the Transmit Shift Register; all transmit operations are completed 00 = Interrupt when a character is transferred to the Transmit Shift Register (this implies that there is at least one character open in the transmit buffer) bit 14 UTXINV: Transmit Polarity Inversion bit<sup>(2)</sup> If IREN = 0: 1 = U1TX Idle state is '0' 0 = U1TX Idle state is '1' If IREN = 1: 1 = IrDA<sup>®</sup> encoded U1TX Idle state is '1' 0 = IrDA encoded U1TX Idle state is '0' bit 12 Unimplemented: Read as '0' UTXBRK: Transmit Break bit<sup>(2)</sup> bit 11 1 = Send Sync Break on next transmission – Start bit, followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion 0 = Sync Break transmission is disabled or completed UTXEN: Transmit Enable bit<sup>(1,2)</sup> bit 10 1 = Transmit is enabled, U1TX pin is controlled by UART1 0 = Transmit is disabled, any pending transmission is aborted and buffer is reset; U1TX pin is controlled by port bit 9 UTXBF: Transmit Buffer Full Status bit (read-only)<sup>(2)</sup> 1 = Transmit buffer is full 0 = Transmit buffer is not full; at least one more character can be written TRMT: Transmit Shift Register Empty bit (read-only)(2) bit 8 1 = Transmit Shift Register is empty and transmit buffer is empty (the last transmission has completed) 0 = Transmit Shift Register is not empty, a transmission is in progress or queued

- **Note 1:** Refer to **Section 17. "UART"** (DS70188) in the *"dsPIC33F/PIC24H Family Reference Manual"* for information on enabling the UART module for transmit operation.

- 2: This bit is not available in the dsPIC33FJ06GS001 device.

| REGISTER 19-7: ADCPC3: ADC CONVERT PAIR CONTROL REGISTER 3 <sup>(1)</sup> |               |                  |              |                                         |                |                |             |

|---------------------------------------------------------------------------|---------------|------------------|--------------|-----------------------------------------|----------------|----------------|-------------|

| U-0                                                                       | U-0           | U-0              | U-0          | U-0                                     | U-0            | U-0            | U-0         |

| —                                                                         | —             | —                | _            | —                                       | —              | —              | _           |

| bit 15                                                                    |               |                  |              |                                         |                |                | bit 8       |

| R/W-0                                                                     | R/W-0         | R/W-0            | R/W-0        | R/W-0                                   | R/W-0          | R/W-0          | R/W-0       |

| IRQEN6                                                                    | PEND6         | SWTRG6           |              |                                         | TRGSRC6<4      | :0>            |             |

| bit 7                                                                     |               |                  |              |                                         |                |                | bit 0       |

|                                                                           |               |                  |              |                                         |                |                |             |

| Legend:                                                                   |               |                  |              |                                         |                |                |             |

| R = Readable                                                              | bit           | W = Writable b   | bit          | U = Unimplemented bit, read as '0'      |                |                |             |

| -n = Value at F                                                           | POR           | '1' = Bit is set |              | '0' = Bit is cleared x = Bit is unknown |                |                | nown        |

|                                                                           |               |                  |              |                                         |                |                |             |

| bit 15-8                                                                  | Unimplemen    | ted: Read as '0  | ,            |                                         |                |                |             |

| bit 7                                                                     | IRQEN6: Inte  | rrupt Request E  | nable 6 bit  |                                         |                |                |             |

|                                                                           | 1 = Enable IR | Q generation w   | hen requeste | ed conversion o                         | of channels AN | N13 and AN12 i | s completed |

### ADADAA ADA AANNEDT DAID AANTDAL DEGIATED A(1)

|       | 0 = IRQ is not generated                                                                                                                                                                                                                        |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | <b>PEND6:</b> Pending Conversion Status 6 bit<br>1 = Conversion of channels AN13 and AN 12 is pending; set when selected trigger is asserted<br>0 = Conversion is complete                                                                      |

| bit 5 | SWTRG6: Software Trigger 6 bit                                                                                                                                                                                                                  |

|       | <ul> <li>1 = Starts conversion of AN13 (INTREF) and AN12 (EXTREF) if selected by TRGSRC bits<sup>(2)</sup></li> <li>This bit is automatically cleared by hardware when the PEND6 bit is set.</li> <li>0 = Conversion has not started</li> </ul> |

Note 1: If other conversions are in progress, conversion will be performed when the conversion resources are available.

2: AN13 is internally connected to Vref in all devices. AN12 is internally connected to the EXTREF pin in the dsPIC33FJ06001/202A and dsPIC33FJ09GS302 devices. The dsPIC33FJ06GS101A/102A devices not have an EXTREF pin; therefore, any data read on the corresponding AN12 input will be invalid.

| R/W-0                | U-0                          | R/W-0                            | R/W-0                 | R/W-0                  | R/W-0                 | R/W-0                   | R/W-0                |

|----------------------|------------------------------|----------------------------------|-----------------------|------------------------|-----------------------|-------------------------|----------------------|

| CMPON <sup>(1)</sup> | _                            | CMPSIDL <sup>(1)</sup>           | HYSSE                 | L<1:0> <sup>(1)</sup>  | FLTREN <sup>(1)</sup> | FCLKSEL <sup>(1)</sup>  | DACOE <sup>(1)</sup> |

| bit 15               |                              |                                  |                       |                        |                       |                         | bit                  |

|                      |                              |                                  |                       |                        |                       |                         |                      |

| R/W-0                | R/W-0                        | R/W-0                            | R/W-0                 | R/W-0                  | R/W-0                 | R/W-0                   | R/W-0                |

| INSEL                | <1:0> <sup>(1)</sup>         | EXTREF <sup>(1)</sup>            | HYSPOL <sup>(1)</sup> | CMPSTAT <sup>(1)</sup> | HGAIN <sup>(1)</sup>  | CMPPOL <sup>(1)</sup>   | RANGE <sup>(1)</sup> |

| bit 7                |                              |                                  |                       |                        |                       |                         | bit                  |

| Legend:              |                              |                                  |                       |                        |                       |                         |                      |

| R = Readable         | bit                          | W = Writable                     | bit                   | U = Unimplem           | nented bit, read      | l as '0'                |                      |

| -n = Value at I      | POR                          | '1' = Bit is set                 |                       | '0' = Bit is clea      | ared                  | x = Bit is unkn         | own                  |

| hit 1E               |                              | mparator Opera                   | ting Mada bit         | (1)                    |                       |                         |                      |

| bit 15               |                              | itor module is e                 | -                     |                        |                       |                         |                      |

|                      | •                            | tor module is d                  |                       | es power cons          | umption)              |                         |                      |

| bit 14               | Unimplemer                   | nted: Read as '                  | 0'                    |                        |                       |                         |                      |

| bit 13               | CMPSIDL: S                   | top in Idle Mode                 | e bit <sup>(1)</sup>  |                        |                       |                         |                      |

|                      | 1 = Discontin                | ues module op                    | eration when          | device enters lo       | dle mode.             |                         |                      |

|                      | 0 = Continue                 | s module opera                   | ition in Idle mo      | ode                    |                       |                         |                      |

|                      |                              |                                  | parators, any         | CMPSIDL bit th         | at is set to '1' c    | lisables <i>all</i> com | parators whi         |

|                      | in Idle mode.                |                                  |                       | (4)                    |                       |                         |                      |

| bit 12-11            |                              | 0>: Comparator                   | Hysteresis S          | elect bits(")          |                       |                         |                      |

|                      | 11 = 45 mV ł                 | •                                |                       |                        |                       |                         |                      |

|                      | 10 = 30 mV h<br>01 = 15 mV h |                                  |                       |                        |                       |                         |                      |

|                      |                              | eresis is selecte                | ed                    |                        |                       |                         |                      |

| bit 10               | -                            | gital Filter Enabl               |                       |                        |                       |                         |                      |

|                      |                              | ter is enabled                   |                       |                        |                       |                         |                      |

|                      | •                            | ter is disabled                  |                       |                        |                       |                         |                      |

| bit 9                | FCLKSEL: D                   | Digital Filter and               | Pulse Stretch         | er Clock Selec         | t bit <sup>(1)</sup>  |                         |                      |

|                      | 1 = Digital filt             | ter and pulse st                 | retcher operat        | e with the PWN         | /I clock              |                         |                      |

|                      | 0 = Digital filt             | ter and pulse st                 | retcher operat        | e with the syste       | em clock              |                         |                      |

| bit 8                | DACOE: DA                    | C Output Enabl                   | e <sup>(1)</sup>      |                        |                       |                         |                      |

|                      |                              | log voltage is o                 |                       |                        | _                     |                         |                      |

| hit 7 G              |                              | llog voltage is n                |                       |                        | 1                     |                         |                      |

| bit 7-6              |                              | : Input Source S                 |                       | iparator bits ??       |                       |                         |                      |

|                      |                              | CMPxD input pi<br>CMPxC input pi |                       |                        |                       |                         |                      |

|                      |                              | CMPxB input pi                   |                       |                        |                       |                         |                      |

|                      |                              | CMPxA input pi                   |                       |                        |                       |                         |                      |

| Note 1: Thi          | s bit is not impl            | lemented in dsF                  | 21C33F.106G.S         | 101A/102A dev          | vices.                |                         |                      |

|                      | •                            |                                  |                       |                        |                       | The software m          | nust ensure          |

|                      |                              |                                  |                       |                        |                       | ective DACOE b          |                      |

| • -                  |                              |                                  |                       |                        | - '                   |                         |                      |

### REGISTER 20-1: CMPCONX: COMPARATOR CONTROL x REGISTER

3: For the INTREF value, refer to the DAC Module Specifications (Table 25-42) in Section 25.0 "Electrical Characteristics".

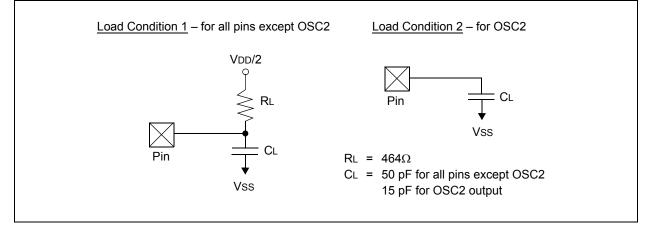

### 25.2 AC Characteristics and Timing Parameters

This section defines dsPIC33FJ06GS001/101A/102A/202A and dsPIC33FJ09GS302 AC characteristics and timing parameters.

### TABLE 25-14: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)                                                            |  |  |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| AC CHARACTERISTICS | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |  |  |  |

|                    | Operating voltage VDD range as described in Table 25-1.                                                                             |  |  |  |

### FIGURE 25-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

### TABLE 25-15: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param. | Symbol | Characteristic        | Min. | Тур. | Max. | Units | Conditions                                                      |

|--------|--------|-----------------------|------|------|------|-------|-----------------------------------------------------------------|

| DO50   | Cosco  | OSC2 Pin              | _    | _    | 15   |       | In XT and HS modes when external<br>clock is used to drive OSC1 |

| DO56   | Сю     | All I/O Pins and OSC2 | —    | —    | 50   | pF    | EC mode                                                         |

| DO58   | Св     | SCL1, SDA1            |      | _    | 400  | pF    | In I <sup>2</sup> C™ mode                                       |

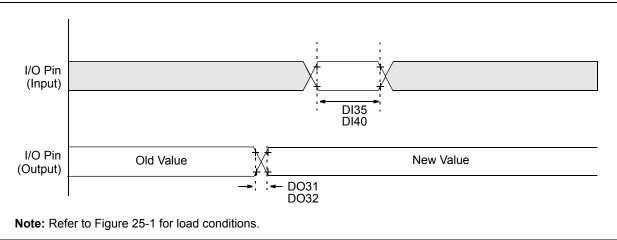

### TABLE 25-21: I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                                                      | (unless | rd Operat<br>otherwis | <b>e statec</b><br>ature - | <b>i)</b><br>-40°C ≤ T | <b>3.0V to 3.6V</b><br>$A \le +85^{\circ}C$ for Industrial<br>$A \le +125^{\circ}C$ for Extended |

|--------------------|--------|----------------------------------------------------------------------|---------|-----------------------|----------------------------|------------------------|--------------------------------------------------------------------------------------------------|

| Param.             | Symbol | Characteristic                                                       | Min.    | Typ. <sup>(1)</sup>   | Max.                       | Units                  | Conditions                                                                                       |

| DO31               | TioR   | I/O Pins: 4x Sink Driver Pins<br>RA0-RA2, RB0-RB2, RB5-RB10,<br>RB15 | _       | 10                    | 25                         | ns                     | Refer to Figure 25-1 for test conditions                                                         |

|                    |        | I/O Pins: 16x Sink Driver Pins<br>RA3, RA4, RB3, RB4, RB11-RB14      | —       | 6                     | 15                         | ns                     |                                                                                                  |

| DO32               | TioF   | I/O Pins: 4x Sink Driver Pins<br>RA0-RA2, RB0-RB2, RB5-RB10,<br>RB15 | _       | 10                    | 25                         | ns                     | Refer to Figure 25-1 for test conditions                                                         |

|                    |        | I/O Pins: 16x Sink Driver Pins<br>RA3, RA4, RB3, RB4, RB11-RB14      | —       | 6                     | 15                         | ns                     |                                                                                                  |

| DI35               | TINP   | INTx Pin High or Low Time (input)                                    | 20      | _                     |                            | ns                     |                                                                                                  |

| DI40               | Trbp   | CNx High or Low Time (input)                                         | 2       |                       | _                          | TCY                    |                                                                                                  |

Note 1: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

| AC CHA | RACTERI    | STICS                     |                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Indus} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extra} \end{array}$ |      |       |                                             |

|--------|------------|---------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|---------------------------------------------|

| Param. | Symbol     | Charac                    | teristic                  | Min.                                                                                                                                                                                                                                                                            | Max. | Units | Conditions                                  |

| IS10   | TLO:SCL    | Clock Low Time            | 100 kHz mode              | 4.7                                                                                                                                                                                                                                                                             | —    | μS    | Device must operate at a minimum of 1.5 MHz |

|        |            |                           | 400 kHz mode              | 1.3                                                                                                                                                                                                                                                                             | —    | μS    | Device must operate at a minimum of 10 MHz  |

|        |            |                           | 1 MHz mode <sup>(1)</sup> | 0.5                                                                                                                                                                                                                                                                             |      | μS    |                                             |

| IS11   | THI:SCL    | Clock High Time           | 100 kHz mode              | 4.0                                                                                                                                                                                                                                                                             | —    | μS    | Device must operate at a minimum of 1.5 MHz |

|        |            |                           | 400 kHz mode              | 0.6                                                                                                                                                                                                                                                                             | —    | μS    | Device must operate at a minimum of 10 MHz  |

|        |            |                           | 1 MHz mode <sup>(2)</sup> | 0.5                                                                                                                                                                                                                                                                             |      | μS    |                                             |

| IS20   | TF:SCL     | SDA1 and SCL1             | 100 kHz mode              | _                                                                                                                                                                                                                                                                               | 300  | ns    | CB is specified to be from                  |

|        |            | Fall Time                 | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                                                                                     | 300  | ns    | 10 pF to 400 pF                             |

|        |            |                           | 1 MHz mode <sup>(2)</sup> | —                                                                                                                                                                                                                                                                               | 100  | ns    |                                             |

| IS21   | TR:SCL     | SDA1 and SCL1             | 100 kHz mode              | —                                                                                                                                                                                                                                                                               | 1000 | ns    | CB is specified to be from                  |

|        |            | Rise Time                 | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                                                                                     | 300  | ns    | 10 pF to 400 pF                             |

|        |            |                           | 1 MHz mode <sup>(2)</sup> | —                                                                                                                                                                                                                                                                               | 300  | ns    |                                             |

| IS25   |            | Data Input                | 100 kHz mode              | 250                                                                                                                                                                                                                                                                             |      | ns    |                                             |

|        | Setup Time | 400 kHz mode              | 100                       |                                                                                                                                                                                                                                                                                 | ns   |       |                                             |

|        |            | 1 MHz mode <sup>(2)</sup> | 100                       |                                                                                                                                                                                                                                                                                 | ns   |       |                                             |

| IS26   | 26 THD:DAT | Data Input                | 100 kHz mode              | 0                                                                                                                                                                                                                                                                               |      | μs    |                                             |

|        | Hold Time  | 400 kHz mode              | 0                         | 0.9                                                                                                                                                                                                                                                                             | μs   |       |                                             |

|        |            |                           | 1 MHz mode <sup>(2)</sup> | 0                                                                                                                                                                                                                                                                               | 0.3  | μS    |                                             |

| IS30   | TSU:STA    | Start Condition           | 100 kHz mode              | 4.7                                                                                                                                                                                                                                                                             |      | μS    | Only relevant for Repeated                  |

|        |            | Setup Time                | 400 kHz mode              | 0.6                                                                                                                                                                                                                                                                             |      | μS    | Start condition                             |

|        |            |                           | 1 MHz mode <sup>(2)</sup> | 0.25                                                                                                                                                                                                                                                                            |      | μS    |                                             |

| IS31   | THD:STA    | Start Condition           | 100 kHz mode              | 4.0                                                                                                                                                                                                                                                                             |      | μS    | After this period, the first                |

|        |            | Hold Time                 | 400 kHz mode              | 0.6                                                                                                                                                                                                                                                                             |      | μS    | clock pulse is generated                    |

|        |            |                           | 1 MHz mode <sup>(2)</sup> | 0.25                                                                                                                                                                                                                                                                            |      | μS    |                                             |

| IS33   | Tsu:sto    | Stop Condition            | 100 kHz mode              | 4.7                                                                                                                                                                                                                                                                             |      | μS    |                                             |

|        |            | Setup Time                | 400 kHz mode              | 0.6                                                                                                                                                                                                                                                                             |      | μS    |                                             |

|        |            |                           | 1 MHz mode <sup>(2)</sup> | 0.6                                                                                                                                                                                                                                                                             |      | μS    |                                             |

| IS34   | THD:STO    | Stop Condition            | 100 kHz mode              | 4000                                                                                                                                                                                                                                                                            |      | ns    |                                             |

|        |            | Hold Time                 | 400 kHz mode              | 600                                                                                                                                                                                                                                                                             |      | ns    |                                             |

|        |            |                           | 1 MHz mode <sup>(2)</sup> | 250                                                                                                                                                                                                                                                                             |      | ns    |                                             |

| IS40   | TAA:SCL    | Output Valid              | 100 kHz mode              | 0                                                                                                                                                                                                                                                                               | 3500 | ns    |                                             |

|        |            | From Clock                | 400 kHz mode              | 0                                                                                                                                                                                                                                                                               | 1000 | ns    |                                             |

|        |            |                           | 1 MHz mode <sup>(2)</sup> | 0                                                                                                                                                                                                                                                                               | 350  | ns    |                                             |

| IS45   | TBF:SDA    | Bus Free Time             | 100 kHz mode              | 4.7                                                                                                                                                                                                                                                                             |      | μS    | Time the bus must be free                   |

|        |            |                           | 400 kHz mode              | 1.3                                                                                                                                                                                                                                                                             |      | μS    | before a new transmission                   |

|        |            |                           | 1 MHz mode <sup>(2)</sup> | 0.5                                                                                                                                                                                                                                                                             |      | μS    | can start                                   |

| IS50   | Св         | Bus Capacitive Lo         | ading                     |                                                                                                                                                                                                                                                                                 | 400  | pF    |                                             |

### TABLE 25-38: I2C1 BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

Note 1: Maximum pin capacitance = 10 pF for all I2C1 pins (for 1 MHz mode only).

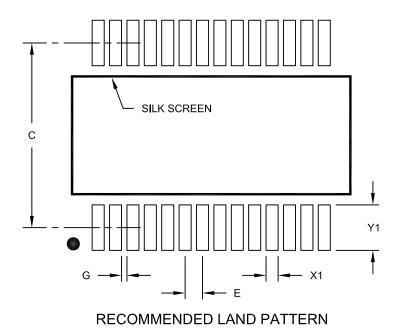

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          |       |      |            | -    |

|--------------------------|-------|------|------------|------|

|                          | Units |      | MILLIMETER | S    |

| Dimension Limits         |       | MIN  | NOM        | MAX  |

| Contact Pitch            | E     |      | 0.65 BSC   |      |

| Contact Pad Spacing      | С     |      | 7.20       |      |

| Contact Pad Width (X28)  | X1    |      |            | 0.45 |

| Contact Pad Length (X28) | Y1    |      |            | 1.75 |

| Distance Between Pads    | G     | 0.20 |            |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A

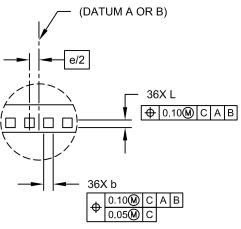

### 36-Terminal Very Thin Thermal Leadless Array Package (TL) – 5x5x0.9 mm Body with Exposed Pad [VTLA]

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**DETAIL A**

|                         | Units       | Ν        |          | S     |  |

|-------------------------|-------------|----------|----------|-------|--|

| Dimens                  | sion Limits | MIN      | NOM      | MAX   |  |

| Number of Pins          | N           | 36       |          |       |  |

| Number of Pins per Side | ND          | 10       |          |       |  |