Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 9KB (3K x 24)                                                                   |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 8x10b; D/A 2x10b                                                            |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj09gs302-i-sp |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

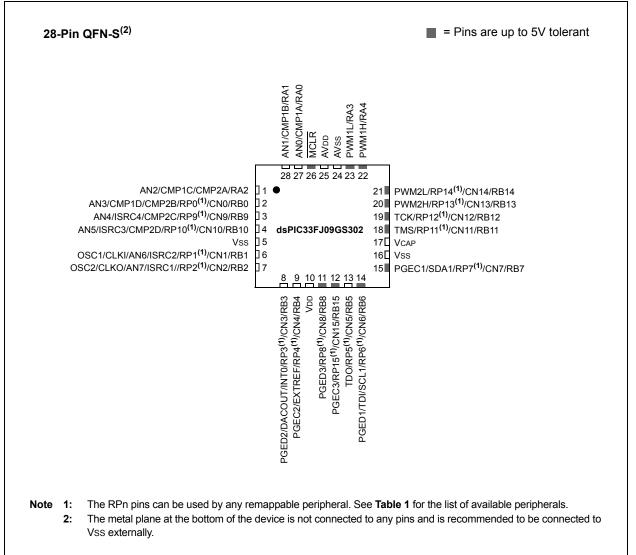

#### **Pin Diagrams (Continued)**

### 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the dsPIC33FJ06GS001/101A/102A/202A and dsPIC33FJ09GS302 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual". Please see the Microchip web site (www.microchip.com) for the latest "dsPIC33F/PIC24H Family Reference Manual" sections.

This document contains device-specific information for the following dsPIC33F Digital Signal Controller (DSC) devices:

- dsPIC33FJ06GS001

- dsPIC33FJ06GS101A

- dsPIC33FJ06GS102A

- dsPIC33FJ06GS202A

- dsPIC33FJ09GS302

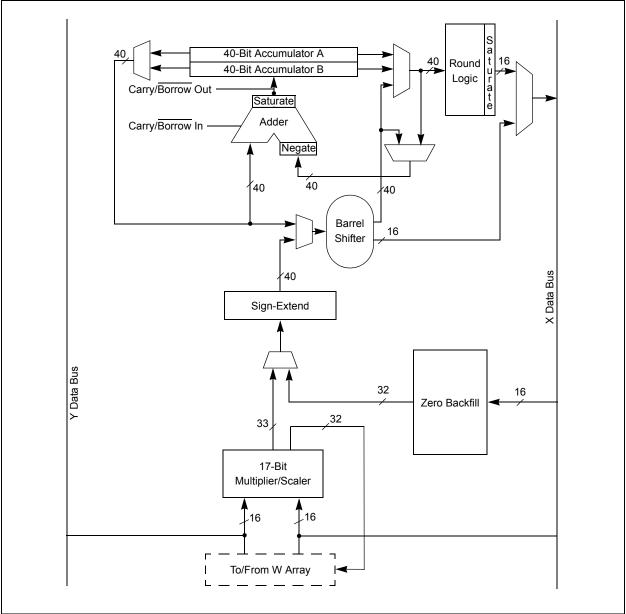

The dsPIC33FJ06GS001/101A/102A/202A and dsPIC33FJ09GS302 devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit microcontroller (MCU) architecture.

Figure 1-1 shows a general block diagram of the core and peripheral modules in the devices. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

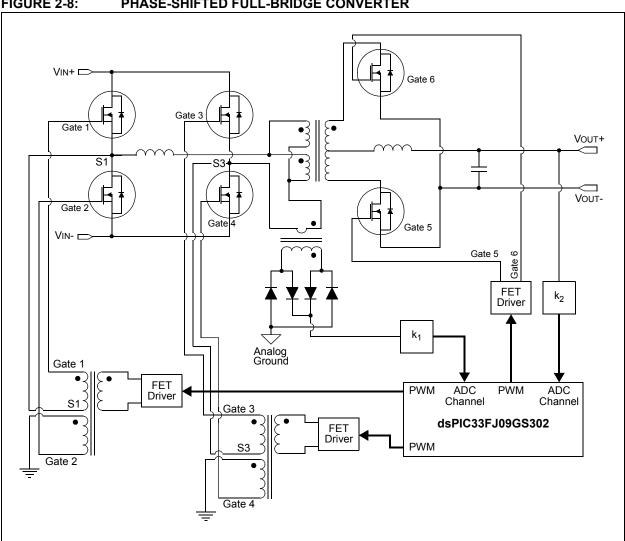

FIGURE 2-8: PHASE-SHIFTED FULL-BRIDGE CONVERTER

#### 4.2 Data Address Space

The CPU has a separate, 16-bit wide data memory space. The data space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory maps are shown in Figure 4-3.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the data space. This arrangement gives a data space address range of 64 Kbytes or 32K words. The lower half of the data memory space (that is, when EA<15>=0) is used for implemented memory addresses, while the upper half (EA<15>=1) is reserved for the Program Space Visibility area (see Section 4.7.3 "Reading Data from Program Memory Using Program Space Visibility").

All devices implement up to 1 Kbyte of data memory. Should an EA point to a location outside of this area, an all-zero word or byte will be returned.

#### 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byteaddressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all data space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

#### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve data space memory usage efficiency, the instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes Post-Modified Register Indirect Addressing mode [Ws++], which results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

Data byte reads will read the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the Least Significant Byte. The Most Significant Byte is not modified.

A Sign-Extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

#### 4.2.3 SFR SPACE

The first 2 Kbytes of the Near Data Space, from 0x0000 to 0x07FF, is primarily occupied by Special Function Registers (SFRs). These are used by the core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control, and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

**Note:** The actual set of peripheral features and interrupts varies by the device. Refer to the corresponding device tables and pinout diagrams for device-specific information.

#### 4.2.4 NEAR DATA SPACE

The 8-Kbyte area between 0x0000 and 0x1FFF is referred to as the Near Data Space. Locations in this space are directly addressable via a 13-bit absolute address field within all memory direct instructions. Additionally, the whole data space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a working register as an Address Pointer.

| IADLE        | 4-1.         |         | LINIOF  |            | NOLLEN  |         |        |            | IN USFI | COOLING  | 002027  |              |         |            |        |             |         |               |

|--------------|--------------|---------|---------|------------|---------|---------|--------|------------|---------|----------|---------|--------------|---------|------------|--------|-------------|---------|---------------|

| File<br>Name | SFR<br>Addr. | Bit 15  | Bit 14  | Bit 13     | Bit 12  | Bit 11  | Bit 10 | Bit 9      | Bit 8   | Bit 7    | Bit 6   | Bit 5        | Bit 4   | Bit 3      | Bit 2  | Bit 1       | Bit 0   | All<br>Resets |

| INTCON1      | 0080         | NSTDIS  | OVAERR  | OVBERR     | COVAERR | COVBERR | OVATE  | OVBTE      | COVTE   | SFTACERR | DIV0ERR | _            | MATHERR | ADDRERR    | STKERR | OSCFAIL     | _       | 0000          |

| INTCON2      | 0082         | ALTIVT  | DISI    | —          | —       | —       | _      | —          | _       | -        | —       | _            | _       | _          | INT2EP | INT1EP      | INT0EP  | 0000          |

| IFS0         | 0084         |         | —       | ADIF       | U1TXIF  | U1RXIF  | SPI1IF | SPI1EIF    | _       | T2IF     | —       | _            | _       | T1IF       | OC1IF  | IC1IF       | INTOIF  | 0000          |

| IFS1         | 0086         | _       | _       | INT2IF     | _       | _       | _      | _          | -       | _        | _       |              | INT1IF  | CNIF       | AC1IF  | MI2C1IF     | SI2C1IF | 0000          |

| IFS3         | 008A         | _       | _       | _          | _       | —       | _      | PSEMIF     | -       |          | _       |              | _       | _          |        | _           |         | 0000          |

| IFS4         | 008C         | _       | _       | _          | _       | _       | _      | _          | _       | _        | _       | _            | _       | —          | _      | U1EIF       |         | 0000          |

| IFS5         | 008E         | PWM2IF  | PWM1IF  | _          | _       | _       |        | _          | _       | _        | _       | _            | _       | _          |        | _           | JTAGIF  | 0000          |

| IFS6         | 0090         | ADCP1IF | ADCP0IF | _          | _       | _       | _      | _          | _       | AC2IF    | _       | _            | _       | —          | _      | _           |         | 0000          |

| IFS7         | 0092         | _       | _       | _          | _       | _       | _      | _          | _       | _        | _       | _            | ADCP6IF | —          | _      | _           | ADCP2IF | 0000          |

| IEC0         | 0094         | _       | _       | ADIE       | U1TXIE  | U1RXIE  | SPI1IE | SPI1EIE    | _       | T2IE     | _       | _            | _       | T1IE       | OC1IE  | IC1IE       | INTOIE  | 0000          |

| IEC1         | 0096         | _       | _       | INT2IE     | _       | _       | _      | _          | _       | _        | _       | _            | INT1IE  | CNIE       | AC1IE  | MI2C1IE     | SI2C1IE | 0000          |

| IEC3         | 009A         | _       | _       | _          | _       | _       | _      | PSEMIE     | _       | _        | _       | _            | _       | _          | _      | _           | _       | 0000          |

| IEC4         | 009C         |         | —       | —          | —       | —       |        | —          |         |          | —       |              | _       | —          | -      | U1EIE       |         | 0000          |

| IEC5         | 009E         | PWM2IE  | PWM1IE  | _          | _       | _       | _      | _          | _       | _        | _       | _            | _       | _          | _      | _           | JTAGIE  | 0000          |

| IEC6         | 00A0         | ADCP1IE | ADCP0IE | —          | —       | —       |        | —          |         | AC2IE    | —       |              | _       | —          | -      | —           | _       | 0000          |

| IEC7         | 00A2         |         | —       | —          | —       | —       |        | —          |         |          | —       |              | ADCP6IE | —          |        | —           | ADCP2IE | 0000          |

| IPC0         | 00A4         |         |         | T1IP<2:0>  |         | —       | U      | OC1IP<2:0  | )>      |          |         | IC1IP<2:0>   | •       | —          |        | INT0IP<2:0> |         | 4444          |

| IPC1         | 00A6         |         |         | T2IP<2:0>  |         | —       |        | —          |         |          | —       |              | —       | —          |        | —           |         | 4000          |

| IPC2         | 00A8         |         |         | U1RXIP<2:0 | )>      | —       |        | SPI1IP<2:0 | )>      |          | 5       | SPI1EIP<2:0  | )>      | —          |        | —           |         | 4440          |

| IPC3         | 00AA         |         | —       | —          | —       | —       |        | —          |         |          |         | ADIP<2:0>    |         | —          | ι      | J1TXIP<2:0> | •       | 0044          |

| IPC4         | 00AC         |         |         | CNIP<2:0>  |         | —       |        | AC1IP<2:0  | >       |          | Ν       | /II2C1IP<2:0 | )>      | —          | 9      | SI2C1IP<2:0 | >       | 4444          |

| IPC5         | 00AE         |         | —       | —          | —       | —       |        | —          |         |          | —       |              | —       | —          |        | INT1IP<2:0> |         | 0004          |

| IPC7         | 00B2         |         | —       | —          | —       | —       |        | —          |         |          |         | INT2IP<2:0   | >       | —          |        | —           |         | 0040          |

| IPC14        | 00C0         |         | —       | —          | —       | —       |        | —          |         |          | F       | PSEMIP<2:0   | )>      | —          |        | —           |         | 0040          |

| IPC16        | 00C4         |         | —       | —          | —       | —       |        | —          |         |          |         | U1EIP<2:0    | >       | —          |        | —           |         | 0040          |

| IPC20        | 00CC         |         | —       | —          | —       | —       |        | —          |         |          | —       |              | —       | —          | ,      | JTAGIP<2:0> | •       | 0004          |

| IPC23        | 00D2         |         | F       | PWM2IP<2:( | )>      | —       | Р      | WM1IP<2:   | 0>      |          | —       |              | —       | —          |        | —           |         | 4400          |

| IPC25        | 00D6         | -       |         | AC2IP<2:0  | >       | _       |        | _          | _       | _        | _       | _            | _       | —          | -      | _           | _       | 4000          |

| IPC27        | 00DA         |         | A       | ADCP1IP<2: | 0>      | —       | A      | DCP0IP<2   | :0>     | -        | -       | -            | _       | —          | -      | —           | _       | 4400          |

| IPC28        | 00DC         | -       | _       | _          | _       | _       |        | _          | _       | _        | _       | _            | _       | —          | A      | DCP2IP<2:0  | >       | 0004          |

| IPC29        | 00DE         | -       | _       | _          | _       | _       | _      | _          | -       | _        | _       | _            | _       | _          | A      | DCP6IP<2:0  | >       | 0004          |

| INTTREG      | 00E0         | _       | _       | _          | —       |         | ILR<   | 3:0>       |         | _        |         |              | ١       | /ECNUM<6:0 | )>     |             |         | 0000          |

#### TABLE 4-7: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33FJ06GS202A DEVICES ONLY

#### TABLE 4-37: PMD REGISTER MAP FOR dsPIC33FJ06GS202A

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| PMD1        | 0770        | _      | —      | _      | T2MD   | T1MD   | —      | PWMMD  | —      | I2C1MD |       | U1MD  | —     | SPI1MD | _     | _     | ADCMD | 0000          |

| PMD2        | 0772        |        | _      | _      | _      | _      | _      | _      | IC1MD  | _      | _     | _     | _     | _      | _     | _     | OC1MD | 0000          |

| PMD3        | 0774        | _      |        |        |        |        | CMPMD  | _      | —      |        |       | —     | —     | —      |       |       | —     | 0000          |

| PMD4        | 0776        | _      |        |        |        |        | _      | _      | —      |        |       | —     | —     | REFOMD |       |       | —     | 0000          |

| PMD6        | 077A        | _      |        |        |        |        | _      | PWM2MD | PWM1MD |        |       | —     | —     | —      |       |       | —     | 0000          |

| PMD7        | 077C        | _      | _      | _      | _      |        | _      | CMP2MD | CMP1MD |        |       | _     | _     | _      |       | _     | —     | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-38: PMD REGISTER MAP FOR dsPIC33FJ09GS302

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| PMD1        | 0770        | -      | _      | _      | T2MD   | T1MD   | _      | PWMMD  | —      | I2C1MD | _     | U1MD  | -     | SPI1MD | —     | -     | ADCMD | 0000          |

| PMD2        | 0772        |        | _      | _      | _      | _      | _      | _      | IC1MD  | _      | _     | —     | _     | _      | _     | _     | OC1MD | 0000          |

| PMD3        | 0774        |        | _      | _      | _      | _      | CMPMD  | _      | _      | _      | _     | —     | _     | _      | _     | _     | _     | 0000          |

| PMD4        | 0776        |        | _      | _      | _      | _      | _      | _      | _      | _      | _     | —     | _     | REFOMD | _     | _     | _     | 0000          |

| PMD6        | 077A        |        | _      | _      | _      | PWM4MD | _      | PWM2MD | PWM1MD | _      | _     | —     | _     | _      | _     | _     | _     | 0000          |

| PMD7        | 077C        |        | _      | _      | _      | _      | _      | CMP2MD | CMP1MD | _      | _     | —     | _     | _      | _     | _     | _     | 0000          |

| PMD8        | 077E        | _      |        | _      |        | —      | _      | —      | —      | —      |       | —     |       | —      |       | CCSMD | _     | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| U-0              | U-0 | U-0              | U-0  | U-0               | U-0             | U-0             | U-0   |

|------------------|-----|------------------|------|-------------------|-----------------|-----------------|-------|

| —                |     | —                | _    | —                 |                 | —               | —     |

| bit 15           |     |                  |      |                   |                 |                 | bit 8 |

|                  |     |                  |      |                   |                 |                 |       |

| W-0              | W-0 | VV-0             | W-0  | W-0               | W-0             | W-0             | W-0   |

|                  |     |                  | NVMK | (EY<7:0>          |                 |                 |       |

| bit 7            |     |                  |      |                   |                 |                 | bit 0 |

|                  |     |                  |      |                   |                 |                 |       |

| Legend:          |     |                  |      |                   |                 |                 |       |

| R = Readable bi  | it  | W = Writable b   | bit  | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value at PC | R   | '1' = Bit is set |      | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

#### REGISTER 5-2: NVMKEY: NONVOLATILE MEMORY KEY REGISTER

bit 15-8 Unimplemented: Read as '0'

bit 7-0 NVMKEY<7:0>: Key Register bits (write-only)

| <b>REGISTER 7-1</b> | 14: IEC3: | INTERRUPT        | ENABLE C | ONTROL RE                               | GISTER 3        |           |       |  |  |

|---------------------|-----------|------------------|----------|-----------------------------------------|-----------------|-----------|-------|--|--|

| U-0                 | U-0       | U-0              | U-0      | U-0                                     | U-0             | R/W-0     | U-0   |  |  |

| —                   | —         | —                | _        | —                                       | —               | PSEMIE    | _     |  |  |

| bit 15              |           |                  |          |                                         |                 |           | bit 8 |  |  |

|                     |           |                  |          |                                         |                 |           |       |  |  |

| U-0                 | U-0       | U-0              | U-0      | U-0                                     | U-0             | U-0       | U-0   |  |  |

| —                   | —         | —                | _        | —                                       | —               | —         | —     |  |  |

| bit 7               |           |                  |          |                                         |                 |           | bit 0 |  |  |

|                     |           |                  |          |                                         |                 |           |       |  |  |

| Legend:             |           |                  |          |                                         |                 |           |       |  |  |

| R = Readable b      | it        | W = Writable     | bit      | U = Unimplei                            | mented bit, rea | ad as '0' |       |  |  |

| -n = Value at PC    | DR        | '1' = Bit is set | :        | '0' = Bit is cleared x = Bit is unknown |                 |           |       |  |  |

| bit 15-10 | Unimplemented: Read as '0'                           |

|-----------|------------------------------------------------------|

| bit 9     | PSEMIE: PWM Special Event Match Interrupt Enable bit |

|           | 1 = Interrupt request is enabled                     |

|           | 0 = Interrupt request is not enabled                 |

| bit 8-0   | Unimplemented: Read as '0'                           |

#### REGISTER 7-15: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | _   |     | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0                | U-0   |

|-------|-----|-----|-----|-----|-----|----------------------|-------|

| —     | —   | —   | _   | _   | —   | U1EIE <sup>(1)</sup> | —     |

| bit 7 |     |     |     |     |     |                      | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-2 | Unimplemented: Read as '0'                             |

|----------|--------------------------------------------------------|

| bit 1    | U1EIE: UART1 Error Interrupt Enable bit <sup>(1)</sup> |

|          | 1 = Interrupt request is enabled                       |

|          | 0 = Interrupt request is not enabled                   |

| bit 0    | Unimplemented: Read as '0'                             |

**Note 1:** This bit is not implemented in the dsPIC33FJ06GS001 device.

### 8.1 CPU Clocking System

The devices provide six system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with PLL

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- · Low-Power RC (LPRC) Oscillator

- FRC Oscillator with Postscaler

#### 8.1.1 SYSTEM CLOCK SOURCES

The Fast RC (FRC) internal oscillator runs at a nominal frequency of 7.37 MHz. User software can tune the FRC frequency. User software can optionally specify a factor (ranging from 1:2 to 1:256) by which the FRC clock frequency is divided. This factor is selected using the FRCDIV<2:0> (CLKDIV<10:8>) bits.

The primary oscillator can use one of the following as its clock source:

- XT (Crystal): Crystals and ceramic resonators in the range of 3 MHz to 10 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- HS (High-Speed Crystal): Crystals in the range of 10 MHz to 32 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- EC (External Clock): The external clock signal is directly applied to the OSC1 pin.

The LPRC internal oscIllator runs at a nominal frequency of 32.768 kHz. It is also used as a reference clock by the Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The clock signals generated by the FRC and primary oscillators can be optionally applied to an on-chip Phase Lock Loop (PLL) to provide a wide range of

output frequencies for device operation. PLL configuration is described in **Section 8.1.3 "PLL Configuration"**.

The FRC frequency depends on the FRC accuracy (see Table 25-20) and the value of the FRC Oscillator Tuning register (see Register 8-4).

#### 8.1.2 SYSTEM CLOCK SELECTION

The oscillator source used at a device Power-on Reset event is selected using Configuration bit settings. The Oscillator Configuration bit settings are located in the Configuration registers in the program memory. (Refer to Section 22.1 "Configuration Bits" for further details.) The initial Oscillator Selection Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), and the Primary Oscillator Mode Select Configuration bits. POSCMD<1:0> (FOSC<1:0>), select the oscillator source that is used at a Power-on Reset. The FRC primary oscillator is the default (unprogrammed) selection.

The Configuration bits allow users to choose among 12 different clock modes, shown in Table 8-1.

The output of the oscillator (or the output of the PLL if a PLL mode has been selected), FOSC, is divided by 2 to generate the device instruction clock (FCY) and the peripheral clock time base (FP). FCY defines the operating speed of the device and speeds up to 40 MHz are supported by the device architecture.

Instruction execution speed or device operating frequency, FCY, is given by Equation 8-1.

#### EQUATION 8-1: DEVICE OPERATING FREQUENCY

FCY = FOSC/2

| Oscillator Mode                                 | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See Note |

|-------------------------------------------------|-------------------|-------------|------------|----------|

| Fast RC Oscillator with Divide-by-N (FRCDIVN)   | Internal          | XX          | 111        | 1, 2     |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16) | Internal          | XX          | 110        | 1        |

| Low-Power RC Oscillator (LPRC)                  | Internal          | XX          | 101        | 1        |

| Reserved                                        | Reserved          | XX          | 100        | —        |

| Primary Oscillator (HS) with PLL (HSPLL)        | Primary           | 10          | 011        | _        |

| Primary Oscillator (XT) with PLL (XTPLL)        | Primary           | 01          | 011        | —        |

| Primary Oscillator (EC) with PLL (ECPLL)        | Primary           | 00          | 011        | 1        |

| Primary Oscillator (HS)                         | Primary           | 10          | 010        | _        |

| Primary Oscillator (XT)                         | Primary           | 01          | 010        | —        |

| Primary Oscillator (EC)                         | Primary           | 00          | 010        | 1        |

| Fast RC Oscillator with PLL (FRCPLL)            | Internal          | XX          | 001        | 1        |

| Fast RC Oscillator (FRC)                        | Internal          | XX          | 000        | 1        |

#### TABLE 8-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

#### 10.6.2.2 Output Mapping

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 6-bit fields, with each set associated with one RPn pin (see Register 10-16 through Register 10-25). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 10-2 and Figure 10-3).

The list of peripherals for output mapping also includes a null value of '00000' because of the mapping technique. This permits any given pin to remain unconnected from the output of any of the pin selectable peripherals.

#### **FIGURE 10-3:** MULTIPLEXING OF **REMAPPABLE OUTPUT** FOR RPn RPORn<5:0> Default 0 U1TX Output Enable 3 **U1RTS** Output Enable 4 **Output Enable** • • • OC1 Output Enable 18 PWM4L Output Enable 45 Default 0 U1TX Output 3 **U1RTS** Output 4 RPn Output Data • Х • • OC1 Output 18 PWM4L Output 45

#### TABLE 10-2: OUTPUT SELECTION FOR REMAPPABLE PIN (RPn)

| Function | RPORn<5:0> | Output Name                                                                 |

|----------|------------|-----------------------------------------------------------------------------|

| NULL     | 000000     | RPn tied to default port pin                                                |

| U1TX     | 000011     | RPn tied to UART1 transmit                                                  |

| U1RTS    | 000100     | RPn tied to UART1 Ready-to-Send                                             |

| SDO1     | 000111     | RPn tied to SPI1 data output                                                |

| SCK1     | 001000     | RPn tied to SPI1 clock output                                               |

| SS1      | 001001     | RPn tied to SPI1 slave select output                                        |

| OC1      | 010010     | RPn tied to Output Compare 1                                                |

| SYNCO1   | 100101     | RPn tied to external device synchronization signal via PWM master time base |

| REFCLKO  | 100110     | REFCLK output signal                                                        |

| ACMP1    | 100111     | RPn tied to Analog Comparator 1 output                                      |

| ACMP2    | 101000     | RPn tied to Analog Comparator 2 output                                      |

| PWM4H    | 101100     | RPn tied to PWM output pins associated with PWM Generator 4                 |

| PWM4L    | 101101     | RPn tied to PWM output pins associated with PWM Generator 4                 |

|                 |     |                                                     |                                                          |       |          | -     |       |

|-----------------|-----|-----------------------------------------------------|----------------------------------------------------------|-------|----------|-------|-------|

| U-0             | U-0 | U-0                                                 | U-0                                                      | U-0   | U-0      | U-0   | U-0   |

| _               |     | _                                                   |                                                          | —     | —        | —     | —     |

| bit 15          |     |                                                     |                                                          |       |          |       | bit 8 |

|                 |     |                                                     |                                                          |       |          |       |       |

| U-0             | U-0 | R/W-1                                               | R/W-1                                                    | R/W-1 | R/W-1    | R/W-1 | R/W-1 |

| _               |     |                                                     |                                                          | SYNC  | l2R<5:0> |       |       |

| bit 7           |     |                                                     |                                                          |       |          |       | bit 0 |

|                 |     |                                                     |                                                          |       |          |       |       |

| Legend:         |     |                                                     |                                                          |       |          |       |       |

| R = Readable I  | oit | W = Writable bit U = Unimplemented bit, read as '0' |                                                          |       | d as '0' |       |       |

| -n = Value at P | OR  | '1' = Bit is set                                    | '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |       |          |       | nown  |

#### REGISTER 10-15: RPINR34: PERIPHERAL PIN SELECT INPUT REGISTER 34

bit 15-6 Unimplemented: Read as '0'

bit 5-0

**SYNCI2R<5:0>:** Assign PWM Master Time Base External Synchronization Signal to the Corresponding RPn Pin bits

111111 = Input tied to Vss 100011 = Input tied to RP35 100010 = Input tied to RP34 100001 = Input tied to RP33 100000 = Input tied to RP32 •

00000 = Input tied to RP0

© 2011-2012 Microchip Technology Inc.

#### REGISTER 10-16: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0                                | U-0                                                                      | R/W-0            | R/W-0            | R/W-0                              | R/W-0           | R/W-0 | R/W-0 |  |

|------------------------------------|--------------------------------------------------------------------------|------------------|------------------|------------------------------------|-----------------|-------|-------|--|

|                                    | —                                                                        |                  |                  | RP1                                | R<5:0>          |       |       |  |

| bit 15                             |                                                                          |                  |                  |                                    |                 |       | bit 8 |  |

|                                    |                                                                          |                  |                  |                                    |                 |       |       |  |

| U-0                                | U-0                                                                      | R/W-0            | R/W-0            | R/W-0                              | R/W-0           | R/W-0 | R/W-0 |  |

| —                                  | —                                                                        |                  | RP0R<5:0>        |                                    |                 |       |       |  |

| bit 7                              |                                                                          |                  |                  |                                    |                 |       | bit 0 |  |

|                                    |                                                                          |                  |                  |                                    |                 |       |       |  |

| Legend:                            |                                                                          |                  |                  |                                    |                 |       |       |  |

| R = Readabl                        | e bit                                                                    | W = Writable     | bit              | U = Unimplemented bit, read as '0' |                 |       |       |  |

| -n = Value at POR '1' = Bit is set |                                                                          |                  | '0' = Bit is cle | ared                               | x = Bit is unkr | nown  |       |  |

|                                    |                                                                          |                  |                  |                                    |                 |       |       |  |

| bit 15-14                          | Unimpleme                                                                | ented: Read as ' | 0'               |                                    |                 |       |       |  |

| bit 13-8                           | RP1R<5:0>: Peripheral Output Function is Assigned to RP1 Output Pin bits |                  |                  |                                    |                 |       |       |  |

|                                    | (see Table 10-2 for peripheral function numbers)                         |                  |                  |                                    |                 |       |       |  |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP0R<5:0>:** Peripheral Output Function is Assigned to RP0 Output Pin bits (see Table 10-2 for peripheral function numbers)

#### REGISTER 10-17: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP3F  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP2F  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

- bit 13-8 **RP3R<5:0>:** Peripheral Output Function is Assigned to RP3 Output Pin bits (see Table 10-2 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP2R<5:0>:** Peripheral Output Function is Assigned to RP2 Output Pin bits (see Table 10-2 for peripheral function numbers)

#### 16.1 SPI Helpful Tips

- 1. In Frame mode, if there is a possibility that the master may not be initialized before the slave:

- a) If FRMPOL (SPIxCON2<13>) = 1, use a pull-down resistor on SSx.

- b) If FRMPOL = 0, use a pull-up resistor on  $\frac{1}{SSx}$ .

| Note: | This                  | insures | that  | the       | first | fr | ame |

|-------|-----------------------|---------|-------|-----------|-------|----|-----|

|       | transmission          |         | after | initializ | ation | is | not |

|       | shifted or corrupted. |         |       |           |       |    |     |

- 2. In Non-Framed 3-Wire mode, (i.e., not using SSx from a master):

- a) If CKP (SPIxCON1<6>) = 1, always place a pull-up resistor on SSx.

- b) If CKP = <u>0</u>, always place a pull-down resistor on SSx.

- **Note:** This will insure that during power-up and initialization the master/slave will not lose Sync due to an errant SCK transition that would cause the slave to accumulate data shift errors for both transmit and receive appearing as corrupted data.

- FRMEN (SPIxCON2<15>) = 1 and SSEN (SPIxCON1<7>) = 1 are exclusive and invalid. In Frame mode, SCKx is continuous and the Frame Sync pulse is active on the SSx pin, which indicates the start of a data frame.

- Note: Not all third-party devices support Frame mode timing. Refer to the SPI electrical characteristics for details.

- In Master mode only, set the SMP bit (SPIxCON1<9>) to a '1' for the fastest SPI data rate possible. The SMP bit can only be set at the same time or after the MSTEN bit (SPIxCON1<5>) is set.

To avoid invalid slave read data to the master, the user's master software must ensure enough time for slave software to fill its write buffer before the user application initiates a master write/read cycle. It is always advisable to preload the SPIxBUF Transmit register in advance of the next master transaction cycle. SPIxBUF is transferred to the SPI Shift register and is empty once the data transmission begins.

#### 16.2 SPI Resources

Many useful resources related to SPI are provided on the Microchip web site (www.microchip.com).

#### 16.2.1 KEY RESOURCES

- Section 18. "Serial Peripheral Interface (SPI)" (DS70206)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related *"dsPIC33F/PIC24H Family Reference Manual"* Sections

- · Development Tools

| R/W-0         | R/W-0                                                                  | R/W-0                            | U-0     | U-0              | U-0              | U-0                | U-0   |

|---------------|------------------------------------------------------------------------|----------------------------------|---------|------------------|------------------|--------------------|-------|

| FRMEN         | SPIFSD                                                                 | FRMPOL                           | —       | —                | —                | —                  | —     |

| bit 15        |                                                                        |                                  |         |                  |                  |                    | bit 8 |

|               |                                                                        |                                  |         |                  |                  |                    |       |

| U-0           | U-0                                                                    | U-0                              | U-0     | U-0              | U-0              | R/W-0              | U-0   |

| —             | —                                                                      |                                  | —       | —                | _                | FRMDLY             | _     |

| bit 7         |                                                                        |                                  |         |                  |                  |                    | bit C |

|               |                                                                        |                                  |         |                  |                  |                    |       |

| _egend:       |                                                                        |                                  |         |                  |                  |                    |       |

| R = Readable  | e bit                                                                  | W = Writable                     | bit     | U = Unimpler     | mented bit, read | l as '0'           |       |

| -n = Value at | POR                                                                    | '1' = Bit is set                 |         | '0' = Bit is cle | ared             | x = Bit is unknown |       |

|               |                                                                        |                                  |         |                  |                  |                    |       |

| bit 15        | FRMEN: Fran                                                            | med SPIx Supp                    | ort bit |                  |                  |                    |       |

|               |                                                                        |                                  |         | in used as Frar  | ne Sync pulse i  | nput/output)       |       |

|               |                                                                        | Plx support dis                  |         |                  |                  |                    |       |

| bit 14        |                                                                        | me Sync Pulse                    |         | ntrol bit        |                  |                    |       |

|               | •                                                                      | nc pulse input<br>nc pulse outpu | • •     |                  |                  |                    |       |

| bit 13        | ,                                                                      | • •                              | ( )     |                  |                  |                    |       |

| DIL 15        |                                                                        | ame Sync Puls<br>nc pulse is act | •       |                  |                  |                    |       |

|               | ,                                                                      | inc pulse is act                 | •       |                  |                  |                    |       |

| bit 12-2      | -                                                                      | ted: Read as '                   |         |                  |                  |                    |       |

| bit 1         | FRMDLY: Frame Sync Pulse Edge Select bit                               |                                  |         |                  |                  |                    |       |

|               |                                                                        | nc pulse coinc                   | •       |                  |                  |                    |       |

|               |                                                                        | nc pulse prece                   |         |                  |                  |                    |       |

| bit 0         | Unimplemented: This bit must not be set to '1' by the user application |                                  |         |                  |                  |                    |       |

|               | •                                                                      |                                  |         |                  |                  |                    |       |

### REGISTER 16-3: SPIxCON2: SPIx CONTROL REGISTER 2

| Field | Description                                                                                                                                                                                                                                                          |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wm*Wm | Multiplicand and Multiplier Working register pair for Square instructions ∈ {W4 * W4,W5 * W5,W6 * W6,W7 * W7}                                                                                                                                                        |

| Wm*Wn | Multiplicand and Multiplier Working register pair for DSP instructions $\in$ {W4 * W5,W4 * W6,W4 * W7,W5 * W6,W5 * W7,W6 * W7}                                                                                                                                       |

| Wn    | One of 16 Working registers ∈ {W0W15}                                                                                                                                                                                                                                |

| Wnd   | One of 16 Destination Working registers ∈ {W0W15}                                                                                                                                                                                                                    |

| Wns   | One of 16 Source Working registers ∈ {W0W15}                                                                                                                                                                                                                         |

| WREG  | W0 (Working register used in file register instructions)                                                                                                                                                                                                             |

| Ws    | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                                                                                                                                                                                                         |

| Wso   | Source W register ∈<br>{ Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }                                                                                                                                                                                      |

| Wx    | X Data Space Prefetch Address register for DSP instructions<br>∈ {[W8] + = 6, [W8] + = 4, [W8] + = 2, [W8], [W8] - = 6, [W8] - = 4, [W8] - = 2,<br>[W9] + = 6, [W9] + = 4, [W9] + = 2, [W9], [W9] - = 6, [W9] - = 4, [W9] - = 2,<br>[W9 + W12], none}                |

| Wxd   | X Data Space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                             |

| Wy    | Y Data Space Prefetch Address register for DSP instructions<br>∈ {[W10] + = 6, [W10] + = 4, [W10] + = 2, [W10], [W10] - = 6, [W10] - = 4, [W10] - = 2,<br>[W11] + = 6, [W11] + = 4, [W11] + = 2, [W11], [W11] - = 6, [W11] - = 4, [W11] - = 2,<br>[W11 + W12], none} |

| Wyd   | Y Data Space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                             |

#### TABLE 23-1: SYMBOLS USED IN OPCODE DESCRIPTIONS (CONTINUED)

#### 24.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows® programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit<sup>™</sup> 2 enables in-circuit debugging on most PIC® microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

#### 24.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

#### 24.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

| DC CHARACTERISTICS |                        |      | $\begin{array}{ll} \mbox{Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |        |       |                                              |  |

|--------------------|------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|----------------------------------------------|--|

| Param.             | Typical <sup>(1)</sup> | Max. | Units                                                                                                                                                                                                                                                                        |        |       | Conditions                                   |  |

| Power-Down         | Current (IPD)          | 2,4) |                                                                                                                                                                                                                                                                              |        |       |                                              |  |

| DC60d              | 125                    | 500  | μA                                                                                                                                                                                                                                                                           | -40°C  |       |                                              |  |

| DC60a              | 135                    | 500  | μA                                                                                                                                                                                                                                                                           | +25°C  | 3.3V  | Base Power-Down Current                      |  |

| DC60b              | 235                    | 500  | μA                                                                                                                                                                                                                                                                           | +85°C  | 3.3V  |                                              |  |

| DC60c              | 565                    | 950  | μA                                                                                                                                                                                                                                                                           | +125°C |       |                                              |  |

| DC61d              | 40                     | 50   | μA                                                                                                                                                                                                                                                                           | -40°C  |       |                                              |  |

| DC61a              | 40                     | 50   | μA                                                                                                                                                                                                                                                                           | +25°C  | 2 21/ | Watchdog Timer Current: ∆IwDT <sup>(3)</sup> |  |

| DC61b              | 40                     | 50   | μA                                                                                                                                                                                                                                                                           | +85°C  | 3.3V  |                                              |  |

| DC61c              | 80                     | 90   | μΑ                                                                                                                                                                                                                                                                           | +125°C |       |                                              |  |

#### TABLE 25-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

**Note 1:** Data in the Typical column is at 3.3V, +25°C unless otherwise stated.

- 2: IPD current is measured as follows:

- CPU core is off, oscillator is configured in EC mode, OSC1 is driven with external square wave from rail-to-rail

- CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- All peripheral modules are disabled (PMDx bits are all '1's)

- VREGS bit (RCON<8>) = 1 (i.e., core regulator is set to standby while the device is in Sleep mode)

- **3:** The ∆ current is the additional current consumed when the WDT module is enabled. This current should be added to the base IPD current.

- 4: These currents are measured on the device containing the most memory in this family.

| DC Specifications             |     |

|-------------------------------|-----|

| DAC Output (DACOUT Pin)       |     |

| Development Support           |     |

| Doze Mode                     | 138 |

| DSC Guidelines                | 17  |

| Basic Connection Requirements | 17  |

| Decoupling Capacitors         | 17  |

| DSP Engine                    | 31  |

| Multiplier                    |     |

### Е

| Electrical Characteristics |    |

|----------------------------|----|

| Absolute Maximum Ratings   |    |

| Equations                  |    |

| Device Operating Frequency |    |

| Fosc Calculation           |    |

| Maximum Page Erase Time    | 76 |

| Minimum Page Erase Time    |    |

| XT with PLL Mode Example   |    |

| Errata                     |    |

#### F

| Fail-Safe Clock Monitor (FSCM) | 135 |

|--------------------------------|-----|

| Flash Program Memory           | 75  |

| Control Registers              |     |

| Operations                     | 76  |

| Table Instructions             | 75  |

| Flexible Configuration         |     |

#### Н

| High-Speed 10-Bit ADC        |     |

|------------------------------|-----|

| Description                  |     |

| Features                     |     |

| Functionality                |     |

| High-Speed Analog Comparator |     |

| Applications                 |     |

| Control Registers            |     |

| DAC                          |     |

| Digital Logic                |     |

| Hysteresis                   |     |

| Input Range                  |     |

| Interaction with I/O Buffers |     |

| High-Speed PWM               | 183 |

| Control Registers            | 186 |

|                              |     |

### I

| I/O Ports                            |     |

|--------------------------------------|-----|

| Helpful Tips                         | 152 |

| Parallel I/O (PIO)                   |     |

| Resources                            |     |

| Write/Read Timing                    |     |

| I <sup>2</sup> C                     |     |

| Operating Modes                      | 211 |

| Registers                            |     |

| In-Circuit Debugger                  |     |

| In-Circuit Emulation                 | 251 |

| In-Circuit Serial Programming (ICSP) |     |

| Analog, Digital Pins Configuration   |     |

| Pins                                 |     |

| Input Capture                        |     |

| Input Change Notification            |     |

|                                      |     |

| Instruction Addressing Modes                       | 66  |

|----------------------------------------------------|-----|

| File Register Instructions                         | 66  |

| Fundamental Modes Supported                        | 67  |

| MAC Instructions                                   |     |

| MCU Instructions                                   | 66  |

| Move and Accumulator Instructions                  | 67  |

| Other Instructions                                 | 67  |

| Instruction Set                                    |     |

| Overview                                           | 262 |

| Summary                                            | 259 |

| Instruction-Based Power-Saving Modes               | 137 |

| ldle                                               | 138 |

| Sleep                                              | 137 |

| Interfacing Program and Data Memory Spaces         | 71  |

| Internal RC Oscillator                             |     |

| Use with WDT                                       | 257 |

| Internet Address                                   | 346 |

| Interrupt Control and Status Registers             | 90  |

| IECx                                               | 90  |

| IFSx                                               | 90  |

| INTCON1                                            | 90  |

| INTCON2                                            | 90  |

| INTTREG                                            | 90  |

| IPCx                                               | 90  |

| Interrupt Setup Procedures                         | 122 |

| Initialization                                     | 122 |

| Interrupt Disable                                  | 122 |

| Interrupt Service Routine                          | 122 |

| Trap Service Routine                               |     |

| Interrupt Vector Table (IVT)                       |     |

| Interrupts Coincident with Power Save Instructions |     |

| •                                                  |     |

### J

| JTAG Boundary Scan Interface | 251 |

|------------------------------|-----|

| JTAG Interface               | 258 |

# L

```

LEBCONx (PWMx Leading-Edge Blanking Control) ...... 202

```

### Μ

| Master Clear (MCLR)                         | 18  |

|---------------------------------------------|-----|

| Memory Organization                         | 37  |

| Microchip Internet Web Site                 | 346 |

| Modulo Addressing                           | 68  |

| Applicability                               |     |

| Operation Example                           | 68  |

| Start and End Address                       |     |

| W Address Register Selection                | 68  |

| MPLAB ASM30 Assembler, Linker, Librarian    | 268 |

| MPLAB Integrated Development                |     |

| Environment Software                        | 267 |

| MPLAB PM3 Device Programmer                 | 270 |

| MPLAB REAL ICE In-Circuit Emulator System   | 269 |

| MPLINK Object Linker/MPLIB Object Librarian | 268 |

|                                             |     |

### 0

| Open-Drain Configuration     | 147 |

|------------------------------|-----|

| Oscillator                   |     |

| External Pins                | 19  |

| Value Conditions on Start-up | 20  |

| Oscillator Configuration     | 123 |

| Output Compare               | 179 |

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2011-2012, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

#### ISBN: 978-1-62076-494-7

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.