Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 9КВ (3К х 24)                                                                   |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

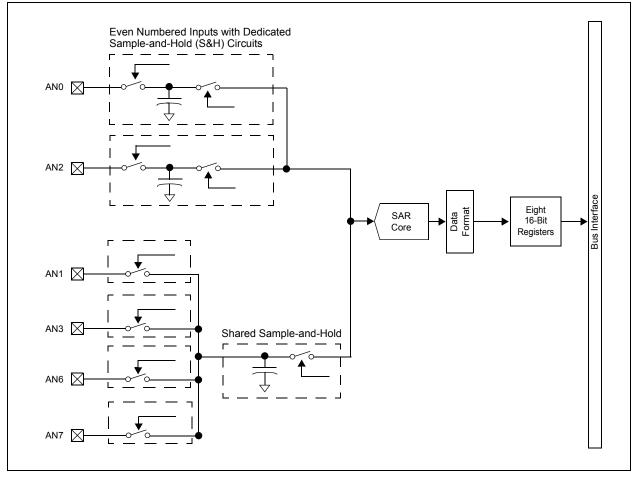

| Data Converters            | A/D 8x10b; D/A 2x10b                                                            |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 36-VFTLA Exposed Pad                                                            |

| Supplier Device Package    | 36-VTLA (5x5)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj09gs302-i-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS001/101A/102A/ 202A and dsPIC33FJ09GS302 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 2.** "CPU" (DS70204) in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The CPU module has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for DSP. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space. The actual amount of program memory implemented varies from device to device. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

The dsPIC33FJ06GS001/101A/102A/202A and dsPIC33FJ09GS302 devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can serve as a Data, Address or Address Offset register. The sixteenth working register (W15) operates as a software Stack Pointer (SP) for interrupts and calls.

There are two classes of instruction: MCU and DSP. These two instruction classes are seamlessly integrated into a single CPU. The instruction set includes many addressing modes and is designed for optimum C compiler efficiency. For most instructions, the devices are capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing A + B = C operations to be executed in a single cycle.

A block diagram of the CPU is shown in Figure 3-1, and the programmer's model is shown in Figure 3-2.

## 3.1 Data Addressing Overview

The data space can be addressed as 32K words or 64 Kbytes and is split into two blocks, referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear data space. Certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y data space boundary is device-specific.

Overhead-free circular buffers (Modulo Addressing mode) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. Furthermore, the X AGU Circular Addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms.

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K program word boundary defined by the 8-bit Program Space Visibility Page (PSVPAG) register. The program-to-data space mapping feature lets any instruction access program space as if it were data space.

## 3.2 DSP Engine Overview

The DSP engine features a high-speed, 17-bit by 17-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bidirectional barrel shifter. The barrel shifter is capable of shifting a 40-bit value up to 16 bits, right or left, in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been designed for optimal realtime performance. The MAC instruction and other associated instructions can concurrently fetch two data operands from memory while multiplying two W registers and accumulating and optionally saturating the result in the same cycle. This instruction functionality requires that the RAM data space be split for these instructions and linear for all others. Data space partitioning is achieved in a transparent and flexible manner through dedicating certain working registers to each address space.

## REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 2 | STKERR: Stack Error Trap Status bit                |

|-------|----------------------------------------------------|

|       | 1 = Stack error trap has occurred                  |

|       | 0 = Stack error trap has not occurred              |

| bit 1 | <b>OSCFAIL:</b> Oscillator Failure Trap Status bit |

|       | 1 = Oscillator failure trap has occurred           |

|       | 0 = Oscillator failure trap has not occurred       |

| bit 0 | Unimplemented: Read as '0'                         |

© 2011-2012 Microchip Technology Inc.

| U-0          | U-0                                                                                                | R/W-0                            | U-0             | U-0                          | U-0                 | U-0             | U-0     |

|--------------|----------------------------------------------------------------------------------------------------|----------------------------------|-----------------|------------------------------|---------------------|-----------------|---------|

| —            |                                                                                                    | INT2IF                           |                 |                              |                     |                 | _       |

| bit 15       |                                                                                                    |                                  |                 |                              |                     |                 | bit 8   |

|              |                                                                                                    |                                  |                 |                              |                     |                 |         |

| U-0          | U-0                                                                                                | U-0                              | R/W-0           | R/W-0                        | R/W-0               | R/W-0           | R/W-0   |

| —            | —                                                                                                  | —                                | INT1IF          | CNIF                         | AC1IF <sup>(1</sup> | MI2C1IF         | SI2C1IF |

| bit 7        |                                                                                                    |                                  |                 |                              |                     |                 | bit     |

| Legend:      |                                                                                                    |                                  |                 |                              |                     |                 |         |

| R = Readab   | le bit                                                                                             | W = Writable                     | bit             | U = Unimpler                 | mented bit, read    | 1 as '0'        |         |

| -n = Value a |                                                                                                    | '1' = Bit is set                 |                 | '0' = Bit is cle             |                     | x = Bit is unki | าดพท    |

|              |                                                                                                    |                                  |                 |                              |                     |                 | -       |

| bit 15-14    | Unimplemen                                                                                         | ted: Read as '                   | 0'              |                              |                     |                 |         |

| bit 13       | INT2IF: Exter                                                                                      | rnal Interrupt 2                 | Flag Status bi  | t                            |                     |                 |         |

|              | 1 = Interrupt request has occurred                                                                 |                                  |                 |                              |                     |                 |         |

|              | •                                                                                                  | request has no                   |                 |                              |                     |                 |         |

| bit 12-5     | -                                                                                                  | ited: Read as '                  |                 |                              |                     |                 |         |

| bit 4        |                                                                                                    | rnal Interrupt 1                 | •               | t                            |                     |                 |         |

|              |                                                                                                    | request has oc<br>request has no |                 |                              |                     |                 |         |

| bit 3        | -                                                                                                  | Change Notifica                  |                 | Flag Status hit              |                     |                 |         |

| bit 0        |                                                                                                    | request has oc                   |                 | r lag Olalas bit             |                     |                 |         |

|              |                                                                                                    | request has no                   |                 |                              |                     |                 |         |

| bit 2        | AC1IF: Analo                                                                                       | og Comparator                    | 1 Interrupt Fla | ig Status bit <sup>(1)</sup> |                     |                 |         |

|              |                                                                                                    | request has oc                   |                 |                              |                     |                 |         |

|              | 0 = Interrupt                                                                                      | request has no                   | t occurred      |                              |                     |                 |         |

| bit 1        |                                                                                                    | C1 Master Even                   | •               | ag Status bit                |                     |                 |         |

|              | <ol> <li>I = Interrupt request has occurred</li> <li>Interrupt request has not occurred</li> </ol> |                                  |                 |                              |                     |                 |         |

|              | -                                                                                                  | 1 Slave Events                   |                 | . Statua hit                 |                     |                 |         |

| hit 0        |                                                                                                    |                                  |                 |                              |                     |                 |         |

| bit 0        |                                                                                                    | request has oc                   |                 |                              |                     |                 |         |

Note 1: This bit is not implemented in dsPIC33FJ06GS101A/102A devices.

## 8.4 Oscillator Control Registers

| REGISTER   | <b>、8-1: OSCC</b>                                                                            | ON: OSCILL                                                                                                                                     | ATOR CON                                                                    | TROL REGIS                          | STER                              |                                          |                    |  |  |

|------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------|-----------------------------------|------------------------------------------|--------------------|--|--|

| U-0        | R-0                                                                                          | R-0                                                                                                                                            | R-0                                                                         | U-0                                 | R/W-y                             | R/W-y                                    | R/W-y              |  |  |

|            |                                                                                              | COSC<2:0>                                                                                                                                      |                                                                             |                                     |                                   | NOSC<2:0>(2)                             |                    |  |  |

| bit 15     | ·                                                                                            |                                                                                                                                                |                                                                             |                                     |                                   |                                          | bit                |  |  |

| R/W-0      | R/W-0                                                                                        | R-0                                                                                                                                            | U-0                                                                         | R/C-0                               | U-0                               | U-0                                      | R/W-0              |  |  |

| CLKLOC     |                                                                                              | LOCK                                                                                                                                           |                                                                             | CF                                  |                                   |                                          | OSWEN              |  |  |

| bit 7      |                                                                                              | LOOK                                                                                                                                           |                                                                             | 01                                  |                                   |                                          | bit                |  |  |

|            |                                                                                              |                                                                                                                                                |                                                                             |                                     |                                   |                                          |                    |  |  |

| Legend:    |                                                                                              | •                                                                                                                                              | •                                                                           | ration bits on P                    |                                   |                                          |                    |  |  |

| R = Reada  |                                                                                              | W = Writable                                                                                                                                   |                                                                             | •                                   | mented bit, rea                   |                                          |                    |  |  |

| -n = Value | at POR                                                                                       | '1' = Bit is set                                                                                                                               |                                                                             | '0' = Bit is cl€                    | eared                             | x = Bit is unkr                          | nown               |  |  |

| bit 15     | Unimplemen                                                                                   | ted: Read as '                                                                                                                                 | 0'                                                                          |                                     |                                   |                                          |                    |  |  |

| bit 14-12  | COSC<2:0>:                                                                                   | Current Oscilla                                                                                                                                | ator Selection                                                              | bits (read-only                     | ()                                |                                          |                    |  |  |

|            | 101 = Low-Po<br>100 = Reserv<br>011 = Primar<br>010 = Primar<br>001 = Fast R                 | C Oscillator (Fl<br>ower RC Oscill<br>yed<br>y Oscillator (XT<br>y Oscillator (XT<br>C Oscillator (Fl<br>C Oscillator (Fl                      | ator (LPRC)<br>, HS, EC) wit<br>, HS, EC)<br>RC) with PLL                   | -                                   |                                   |                                          |                    |  |  |

| oit 11     | Unimplemen                                                                                   | Unimplemented: Read as '0'                                                                                                                     |                                                                             |                                     |                                   |                                          |                    |  |  |

| bit 10-8   | NOSC<2:0>:                                                                                   | New Oscillator                                                                                                                                 | Selection bit                                                               | S <sup>(2)</sup>                    |                                   |                                          |                    |  |  |

|            | 110 = Fast R<br>101 = Low-Po<br>100 = Reserv<br>011 = Primar<br>010 = Primar<br>001 = Fast R | C Oscillator (FI<br>C Oscillator (FI<br>ower RC Oscilla<br>red<br>y Oscillator (XT<br>y Oscillator (XT<br>C Oscillator (FI<br>C Oscillator (FI | RC) with divid<br>ator (LPRC)<br>, HS, EC) wit<br>, HS, EC)<br>RC) with PLL | le-by-16                            |                                   |                                          |                    |  |  |

| oit 7      |                                                                                              | Clock Lock Ena                                                                                                                                 |                                                                             |                                     |                                   |                                          |                    |  |  |

|            | 1 = Clock sw                                                                                 | itching is disab                                                                                                                               | led, system c                                                               | lock source is                      | locked                            | SC<7:6>) bits =                          |                    |  |  |

| oit 6      | 1 = Peripheri                                                                                |                                                                                                                                                | locked, write                                                               |                                     |                                   | sters is not allow<br>registers is allow |                    |  |  |

| oit 5      | LOCK: PLL L                                                                                  | ock Status bit (                                                                                                                               | read-only)                                                                  |                                     |                                   |                                          |                    |  |  |

|            |                                                                                              | that PLL is in I<br>that PLL is ou                                                                                                             |                                                                             |                                     |                                   | L is disabled                            |                    |  |  |

|            | Writes to this regis<br>in the <i>"dsPIC33F/</i> F                                           |                                                                                                                                                |                                                                             |                                     |                                   | cillator (Part IV                        | <b>)"</b> (DS70307 |  |  |

| 2:         | Direct clock switch<br>ted. This applies to<br>FRC mode as a tra                             | es between an<br>clock switche                                                                                                                 | y Primary Os<br>s in either dire                                            | cillator mode w<br>ection. In these | vith PLL and Fl<br>instances, the |                                          |                    |  |  |

|            | This register is res                                                                         |                                                                                                                                                |                                                                             |                                     |                                   |                                          |                    |  |  |

## **REGISTER 8-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup>

3: This register is reset only on a Power-on Reset (POR).

### 8.5 Clock Switching Operation

Applications are free to switch among any of the four clock sources (primary, LP, FRC and LPRC) under software control at any time. To limit the possible side effects of this flexibility, devices have a safeguard lock built into the switch process.

Note: Primary Oscillator mode has three different submodes (XT, HS and EC), which are determined by the POSCMD<1:0> Configuration bits. While an application can switch to and from Primary Oscillator mode in software, it cannot switch among the different primary submodes without reprogramming the device.

#### 8.5.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the FOSC Configuration register must be programmed to '0'. (Refer to **Section 22.1 "Configuration Bits"** for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and Fail-Safe Clock Monitor function are disabled. This is the default setting.

The NOSC<2:0> control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSC<2:0> bits (OSCCON<14:12>) reflect the clock source selected by the FNOSC Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled. It is held at '0' at all times.

#### 8.5.2 OSCILLATOR SWITCHING SEQUENCE

To perform a clock switch, the following basic sequence is required:

- 1. If desired, read the COSC<2:0> bits to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- Write the appropriate value to the NOSC<2:0> control bits for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit (OSCCON<0>) to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically as follows:

- The clock switching hardware compares the COSC<2:0> status bits with the new value of the NOSC<2:0> control bits. If they are the same, the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the LOCK (OSCCON<5>) and the CF (OSCCON<3>) status bits are cleared.

- The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware waits until the Oscillator Start-up Timer (OST) expires. If the new source is using the PLL, the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSC<2:0> bit values are transferred to the COSC<2:0> status bits.

- The old clock source is turned off at this time, with the exception of LPRC (if WDT or FSCM is enabled).

Note 1: The processor continues to execute code throughout the clock switching sequence. Timing-sensitive code should not be executed during this time.

- 2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- 3: Refer to Section 42. "Oscillator (Part IV)" (DS70307) in the "dsPIC33F/ PIC24H Family Reference Manual" for details.

| U-0           | U-0                  | U-0                                  | U-0         | U-0              | U-0                   | U-0                         | U-0   |

|---------------|----------------------|--------------------------------------|-------------|------------------|-----------------------|-----------------------------|-------|

|               | —                    | —                                    |             | —                | —                     | —                           | —     |

| bit 15        |                      |                                      |             |                  |                       |                             | bit 8 |

|               |                      |                                      |             |                  |                       |                             |       |

| U-0           | U-0                  | R/W-1                                | R/W-1       | R/W-1            | R/W-1                 | R/W-1                       | R/W-1 |

|               |                      |                                      |             | OCFA             | R<5:0> <sup>(1)</sup> |                             |       |

| bit 7         |                      |                                      |             |                  |                       |                             | bit 0 |

|               |                      |                                      |             |                  |                       |                             |       |

| Legend:       |                      |                                      |             |                  |                       |                             |       |

| R = Readabl   | e bit                | W = Writable I                       | oit         | U = Unimplei     | mented bit, read      | l as '0'                    |       |

| -n = Value at | t POR                | '1' = Bit is set                     |             | '0' = Bit is cle | ared                  | x = Bit is unkr             | nown  |

|               |                      |                                      |             |                  |                       |                             |       |

| bit 15-6      | Unimplemen           | nted: Read as '                      | )'          |                  |                       |                             |       |

| bit 5-0       | OCFAR<5:0>           | Assign Output                        | t Compare A | (OCFA) to the    | Corresponding         | RPn Pin bits <sup>(1)</sup> | )     |

|               |                      | out tied to Vss                      |             |                  |                       |                             |       |

|               |                      | out tied to RP35                     |             |                  |                       |                             |       |

|               |                      | out tied to RP34                     |             |                  |                       |                             |       |

|               |                      | out tied to RP33<br>out tied to RP32 |             |                  |                       |                             |       |

|               | •                    |                                      |             |                  |                       |                             |       |

|               | •                    |                                      |             |                  |                       |                             |       |

|               | •                    |                                      |             |                  |                       |                             |       |

|               | 00000 <b>= Inn</b> i | ut tied to RP0                       |             |                  |                       |                             |       |

|               | 00000 mpc            |                                      |             |                  |                       |                             |       |

### REGISTER 10-6: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

**Note 1:** These bits are not implemented in the dsPIC33FJ06GS001 device.

| U-0                                | U-0     | R/W-1        | R/W-1            | R/W-1                              | R/W-1              | R/W-1 | R/W-1 |

|------------------------------------|---------|--------------|------------------|------------------------------------|--------------------|-------|-------|

| _                                  | —       |              |                  | FLT1                               | R<5:0>             |       |       |

| bit 15                             |         |              |                  |                                    |                    |       | bit 8 |

|                                    |         |              |                  |                                    |                    |       |       |

| U-0                                | U-0     | U-0          | U-0              | U-0                                | U-0                | U-0   | U-0   |

| —                                  | _       | —            | _                | —                                  |                    | —     | —     |

| bit 7                              |         |              |                  |                                    |                    |       | bit 0 |

| Legend:                            |         |              |                  |                                    |                    |       |       |

| R = Readab                         | ole bit | W = Writable | bit              | U = Unimplemented bit, read as '0' |                    |       |       |

| -n = Value at POR '1' = Bit is set |         |              | '0' = Bit is cle | ared                               | x = Bit is unknown |       |       |

#### REGISTER 10-10: RPINR29: PERIPHERAL PIN SELECT INPUT REGISTER 29

bit 15-14 Unimplemented: Read as '0'

bit 13-8

8 FLT1R<5:0>: Assign PWM Fault Input 1 (FLT1) to the Corresponding RPn Pin bits

111111 = Input tied to Vss 100011 = Input tied to RP35 100010 = Input tied to RP34 100001 = Input tied to RP33 100000 = Input tied to RP32 • • •

bit 7-0 Unimplemented: Read as '0'

### **15.2 Feature Description**

The PWM module is designed for applications that require:

- High-resolution at high PWM frequencies

- The ability to drive Standard, Edge-Aligned, Center-Aligned Complementary mode, and Push-Pull mode outputs

- · The ability to create multiphase PWM outputs

For Center-Aligned mode, the duty cycle, period, phase and dead-time resolutions will be 8.32 ns.

Two common, medium power converter topologies are push-pull and half-bridge. These designs require the PWM output signal to be switched between alternate pins, as provided by the Push-Pull PWM mode.

A phase-shifted PWM describes the situation where each PWM generator provides outputs, but the phase relationship between the generator outputs is specifiable and changeable. A multiphase PWM is often used to improve DC/DC Converter load transient response, and reduce the size of output filter capacitors and inductors. Multiple DC/DC Converters are often operated in parallel, but phase-shifted in time. A single PWM output, operating at 250 kHz, has a period of 4  $\mu$ s, but an array of four PWM channels staggered by 1  $\mu$ s each, yields an effective switching frequency of 1 MHz. Multiphase PWM applications typically use a fixed-phase relationship.

A variable phase PWM is useful in Zero Voltage Transition (ZVT) power converters. Here, the PWM duty cycle is always 50%, and the power flow is controlled by varying the relative phase-shift between the two PWM generators.

| R/W-0           | R/W-0                                                                                                                                                                                    | U-0                                                   | U-0                                                      | U-0                                                   | U-0              | U-0             | UW-0  |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------|------------------|-----------------|-------|--|--|--|

| HRPDIS          | HRDDIS                                                                                                                                                                                   | _                                                     |                                                          | _                                                     | _                | _               | _     |  |  |  |

| bit 15          |                                                                                                                                                                                          |                                                       |                                                          |                                                       |                  |                 | bit 8 |  |  |  |

|                 |                                                                                                                                                                                          |                                                       |                                                          |                                                       |                  |                 |       |  |  |  |

| U-0             | U-0                                                                                                                                                                                      | R/W-0                                                 | R/W-0                                                    | R/W-0                                                 | R/W-0            | R/W-0           | R/W-0 |  |  |  |

|                 | CHOPSEL<3:0>     CHOPHEN CHOPLEN                                                                                                                                                         |                                                       |                                                          |                                                       |                  |                 |       |  |  |  |

| bit 7           |                                                                                                                                                                                          |                                                       |                                                          |                                                       |                  |                 | bit 0 |  |  |  |

| Legend:         |                                                                                                                                                                                          |                                                       |                                                          |                                                       |                  |                 |       |  |  |  |

| R = Readable    | bit                                                                                                                                                                                      | W = Writable b                                        | oit                                                      | U = Unimpler                                          | mented bit, read | d as '0'        |       |  |  |  |

| -n = Value at F | POR                                                                                                                                                                                      | '1' = Bit is set                                      |                                                          | '0' = Bit is cle                                      | ared             | x = Bit is unkr | Iown  |  |  |  |

| bit 15          | 1 = High-reso                                                                                                                                                                            | h-Resolution PV<br>Ilution PWMx pe<br>Ilution PWMx pe | eriod is enabl                                           | led                                                   |                  |                 |       |  |  |  |

| bit 14          | <ul> <li>HRDDIS: High-Resolution PWMx Duty Cycle Disable bit</li> <li>1 = High-resolution PWMx duty cycle is enabled</li> <li>0 = High-resolution PWMx duty cycle is disabled</li> </ul> |                                                       |                                                          |                                                       |                  |                 |       |  |  |  |

| bit 13-6        | Unimplemen                                                                                                                                                                               | ted: Read as '0                                       | ,                                                        |                                                       |                  |                 |       |  |  |  |

| bit 5-2         | The selected<br>1001 = Reset<br>0111 = Reset<br>0110 = Reset<br>0101 = Reset<br>0100 = PWM<br>0011 = Reset<br>0010 = PWM<br>0001 = PWM                                                   | rved<br>rved<br>rved<br>rved<br>4H is selected a      | as CHOP clo<br>as CHOP clo<br>as CHOP clo<br>as CHOP clo | e (CHOP) the s<br>ck source<br>ck source<br>ck source | selected PWM>    | coutputs.       |       |  |  |  |

| bit 1           | 1 = PWMxH c                                                                                                                                                                              | PWMxH Output<br>chopping functio                      | n is enabled                                             |                                                       |                  |                 |       |  |  |  |

| bit 0           | CHOPLEN: F<br>1 = PWMxL c                                                                                                                                                                | WMxL Output (<br>hopping function<br>hopping function | Chopping En<br>n is enabled                              | able bit                                              |                  |                 |       |  |  |  |

#### REGISTER 15-21: AUXCONx: PWMx AUXILIARY CONTROL REGISTER

## REGISTER 18-1: U1MODE: UART1 MODE REGISTER (CONTINUED)

| bit 4   | URXINV: Receive Polarity Inversion bit <sup>(3)</sup><br>1 = U1RX Idle state is '0'<br>0 = U1RX Idle state is '1'                                             |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | <ul> <li>BRGH: High Baud Rate Enable bit<sup>(3)</sup></li> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> </ul>         |

|         | 0 = BRG generates 16 clocks per bit period (16 baud clock, Standard mode)                                                                                     |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits <sup>(3)</sup>                                                                                                     |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul> |

| bit 0   | <b>STSEL:</b> Stop Bit Selection bit <sup>(3)</sup><br>1 = Two Stop bits<br>0 = One Stop bit                                                                  |

- **Note 1:** Refer to **Section 17. "UART**" (DS70188) in the *"dsPIC33F/PIC24H Family Reference Manual"* for information on enabling the UART module for receive or transmit operation.

- **2:** This feature is only available for the 16x BRG mode (BRGH = 0).

- 3: This bit is not available in the dsPIC33FJ06GS001 device.

#### **REGISTER 19-6:** ADCPC1: ADC CONVERT PAIR CONTROL REGISTER 1

| R/W-0                 | R/W-0                              | R/W-0                                | R/W-0                       | R/W-0                   | R/W-0           | R/W-0              | R/W-0     |

|-----------------------|------------------------------------|--------------------------------------|-----------------------------|-------------------------|-----------------|--------------------|-----------|

| IRQEN3 <sup>(1</sup>  | <sup>I)</sup> PEND3 <sup>(1)</sup> | SWTRG3 <sup>(1)</sup>                |                             |                         | TRGSRC3<4:(     | )>(1)              |           |

| bit 15                |                                    |                                      |                             |                         |                 |                    | bit 8     |

| R/W-0                 | R/W-0                              | R/W-0                                | R/W-0                       | R/W-0                   | R/W-0           | R/W-0              | R/W-0     |

| IRQEN2(2              |                                    | SWTRG2 <sup>(2)</sup>                | -                           |                         | TRGSRC2<4:(     |                    |           |

| bit 7                 |                                    |                                      |                             |                         |                 |                    | bit (     |

| <u> </u>              |                                    |                                      |                             |                         |                 |                    |           |

| Legend:<br>R = Readat | ala h:t                            |                                      |                             | II — Ileinen le         | mented bit was  |                    |           |

| -n = Value a          |                                    | W = Writable I<br>'1' = Bit is set   | DIL                         | 0' = Onimple            | mented bit, rea | x = Bit is unkr    |           |

|                       |                                    |                                      | (4)                         |                         | ealeu           |                    | IOWIT     |

| bit 15                |                                    | errupt Request E                     |                             |                         |                 |                    |           |

|                       | 1 = Enables<br>0 = IRQ is no       |                                      | wnen reques                 | ted conversio           | n of channels A | N7 and AN6 is o    | completed |

| bit 14                |                                    | ding Conversior                      | n Status 3 bit <sup>(</sup> | 1)                      |                 |                    |           |

|                       |                                    |                                      |                             |                         | et when select  | ed trigger is asse | erted     |

|                       |                                    | on is complete                       | (4)                         |                         |                 |                    |           |

| bit 13                |                                    | oftware Trigger                      |                             |                         |                 | (J)                |           |

|                       |                                    | nversion of AN7<br>tomatically clear |                             |                         |                 |                    |           |

|                       |                                    | on has not start                     |                             |                         | ENDO DIL 13 SC  |                    |           |

| bit 12-8              | TRGSRC3<4                          | I:0>: Trigger 3 S                    | Source Select               | ion bits <sup>(1)</sup> |                 |                    |           |

|                       |                                    | er source for cor                    |                             | nalog channels          | s AN7 and AN6   | ð.                 |           |

|                       | 11111 = Im<br>•                    | er2 period matc                      | n                           |                         |                 |                    |           |

|                       | •                                  |                                      |                             |                         |                 |                    |           |

|                       | •<br>11011 <b>= Res</b>            | anvad                                |                             |                         |                 |                    |           |

|                       |                                    | M Generator 4 (                      | current-limit A             | DC trigger              |                 |                    |           |

|                       | 11001 <b>= Res</b>                 | served                               |                             |                         |                 |                    |           |

|                       |                                    | M Generator 2 of<br>M Generator 1 of |                             |                         |                 |                    |           |

|                       | 10111 <b>– P W</b>                 |                                      |                             |                         |                 |                    |           |

|                       | •                                  |                                      |                             |                         |                 |                    |           |

|                       | •                                  |                                      |                             |                         |                 |                    |           |

|                       | 10010 <b>= Res</b>                 | served                               |                             |                         |                 |                    |           |

|                       |                                    | M Generator 4                        | secondary trig              | gger is selecte         | d               |                    |           |

|                       | 10000 = Res                        | erved<br>M Generator 2 s             | secondary tri               | naer is selecte         | h               |                    |           |

|                       |                                    | M Generator 1                        |                             |                         |                 |                    |           |

|                       | 01101 = Res                        | served                               |                             |                         |                 |                    |           |

|                       | 01100 = lim                        | er1 period matc                      | h                           |                         |                 |                    |           |

|                       | •                                  |                                      |                             |                         |                 |                    |           |

|                       | •                                  |                                      |                             |                         |                 |                    |           |

|                       | 01000 = Res                        | M Generator 4                        | orimary trigge              | r is selected           |                 |                    |           |

|                       | 00110 <b>= Res</b>                 | served                               |                             |                         |                 |                    |           |

|                       |                                    | M Generator 2<br>M Generator 1       |                             |                         |                 |                    |           |

|                       |                                    | M Special Even                       |                             |                         |                 |                    |           |

|                       | 00010 <b>= Glo</b>                 | bal software trig                    | ger is selecte              | ed                      |                 |                    |           |

|                       |                                    | vidual software<br>conversion is er  |                             | ected                   |                 |                    |           |

| •• • • =              |                                    |                                      |                             |                         |                 |                    |           |

|                       | This bit is availabl               |                                      |                             |                         |                 |                    |           |

| 2: 7                  | This bit is availabl               |                                      | 0003102A/2                  |                         | -22L108G230     | z devices only.    |           |

3: The trigger source must be set as a global software trigger prior to setting this bit to '1'. If other conversions are in progress, conversion will be performed when the conversion resources are available.

#### **REGISTER 19-7:** ADCPC3: ADC CONVERT PAIR CONTROL REGISTER 3<sup>(1)</sup> (CONTINUED)

```

bit 4-0

TRGSRC6<4:0>: Trigger 6 Source Selection bits

Selects trigger source for conversion of analog channels AN13 and AN12.

11111 = Timer2 period match

11011 = Reserved

11010 = PWM Generator 4 current-limit ADC trigger

11001 = Reserved

11000 = PWM Generator 2 current-limit ADC trigger

10111 = PWM Generator 1 current-limit ADC trigger

10110 = Reserved

10010 = Reserved

10001 = PWM Generator 4 secondary trigger is selected

10000 = Reserved

01111 = PWM Generator 2 secondary trigger is selected

01110 = PWM Generator 1 secondary trigger is selected

01101 = Reserved

```

01101 = Timer1 period match 01100 = Timer1 period match 01000 = Reserved 00111 = PWM Generator 4 primary trigger is selected 00101 = PWM Generator 2 primary trigger is selected 00100 = PWM Generator 1 primary trigger is selected 00011 = PWM Special Event Trigger is selected 00011 = Global software trigger is selected 00001 = Individual software trigger is selected

00000 = No conversion is enabled

- **Note 1:** If other conversions are in progress, conversion will be performed when the conversion resources are available.

- 2: AN13 is internally connected to Vref in all devices. AN12 is internally connected to the EXTREF pin in the dsPIC33FJ06001/202A and dsPIC33FJ09GS302 devices. The dsPIC33FJ06GS101A/102A devices not have an EXTREF pin; therefore, any data read on the corresponding AN12 input will be invalid.

NOTES:

| U-0             | U-0 | U-0              | U-0 | U-0                                     | U-0     | U-0 | U-0    |

|-----------------|-----|------------------|-----|-----------------------------------------|---------|-----|--------|

| —               |     | —                | _   | —                                       | _       | —   | —      |

| bit 23          |     |                  |     |                                         |         |     | bit 16 |

|                 |     |                  |     |                                         |         |     |        |

| U-0             | U-0 | U-0              | U-0 | U-0                                     | U-0     | U-0 | U-0    |

| —               | _   | —                | —   | —                                       | —       |     | —      |

| bit 15          |     |                  |     |                                         |         |     | bit 8  |

|                 |     |                  |     |                                         |         |     |        |

| U-0             | U-0 | R-0              | R-0 | R-0                                     | R-0     | R-0 | R-0    |

| _               | _   |                  |     | CCSC                                    | AL<5:0> |     |        |

| bit 7           |     |                  |     |                                         |         |     | bit 0  |

|                 |     |                  |     |                                         |         |     |        |

| Legend:         |     |                  |     |                                         |         |     |        |

| R = Readable    | bit | W = Writable     | bit | bit U = Unimplemented bit, read as '0'  |         |     |        |

| -n = Value at F | POR | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |         |     | nown   |

#### REGISTER 22-1: CONSTANT CURRENT SOURCE CALIBRATION REGISTER

bit 23-6 Unimplemented: Read as '0'

bit 5-0 CCSCAL<5:0>: Constant Current Source Calibration bits

The value of these bits must be copied into the ISRCCAL<5:0> bits (ISRCCON<5:0>). Refer to the Current Source Control register (Register 21-1) in **Section 21.0** "**Constant Current Source**".

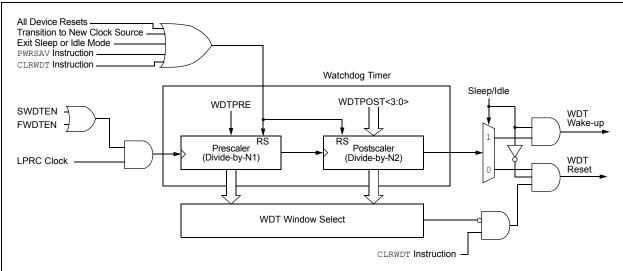

### 22.4 Watchdog Timer (WDT)

The Watchdog Timer (WDT) is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

#### 22.4.1 PRESCALER/POSTSCALER

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit (FWDT<4>). With a 32 kHz input, the prescaler yields a nominal WDT time-out period (TWDT) of 1 ms in 5-bit mode or 4 ms in 7-bit mode.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>), which allow the selection of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods ranging from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSC<2:0> bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

#### 22.4.2 SLEEP AND IDLE MODES

If the WDT is enabled, it will continue to run during Sleep or Idle modes. When the WDT time-out occurs, the device will wake the device and code execution will continue from where the PWRSAV instruction was executed. The corresponding SLEEP bit (RCON<3>) or IDLE bit (RCON<2>) will need to be cleared in software after the device wakes up.

#### 22.4.3 ENABLING WDT

The WDT is enabled or disabled by the FWDTEN Configuration bit in the FWDT Configuration register (FWDT<7>). When the FWDTEN Configuration bit is set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTEN Configuration bit has been programmed to '0'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user application to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

The WDT flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

#### FIGURE 22-2: WDT BLOCK DIAGRAM

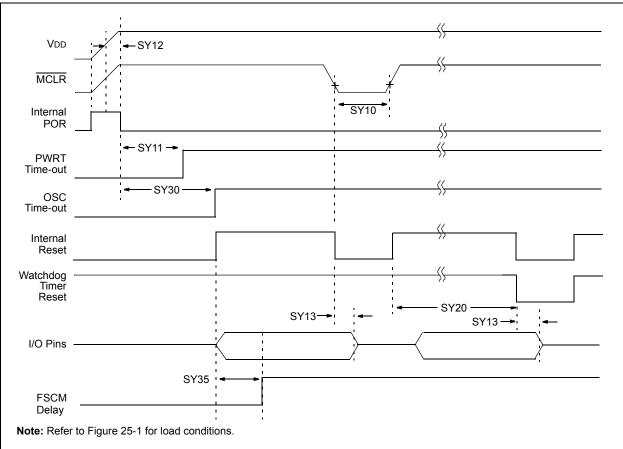

#### TABLE 25-22: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER TIMING REQUIREMENTS

|        |        |                                                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                    |  |

|--------|--------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------|--|

| Param. | Symbol | Characteristic <sup>(1)</sup>                               | Min.                                                                                                                                                                                                                                                                                    | Typ. <sup>(2)</sup> | Max. | Units | Conditions         |  |

| SY10   | TMCL   | MCLR Pulse Width (low)                                      | 2                                                                                                                                                                                                                                                                                       | —                   | _    | μS    | -40°C to +125°C    |  |

| SY11   | TPWRT  | Power-up Timer Period                                       | —                                                                                                                                                                                                                                                                                       | 64                  | _    | ms    | -40°C to +125°C    |  |

| SY12   | TPOR   | Power-on Reset Delay                                        | 3                                                                                                                                                                                                                                                                                       | 10                  | 30   | μS    | -40°C to +125°C    |  |

| SY13   | Tioz   | I/O High-Impedance from MCLR<br>Low or Watchdog Timer Reset | 0.68                                                                                                                                                                                                                                                                                    | 0.72                | 1.2  | μS    |                    |  |

| SY30   | Tost   | Oscillator Start-up Time                                    | —                                                                                                                                                                                                                                                                                       | 1024 Tosc           | _    | _     | Tosc = OSC1 period |  |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

| АС СНА | RACTERIST | $\begin{tabular}{ l l l l l l l l l l l l l l l l l l l$ |                              |                                         |      |         |       |                                                                           |

|--------|-----------|----------------------------------------------------------|------------------------------|-----------------------------------------|------|---------|-------|---------------------------------------------------------------------------|

| Param. | Symbol    | Characte                                                 | eristic                      | Min.                                    | Тур. | Max.    | Units | Conditions                                                                |

| TB10   | ТтхН      | TxCK High Time                                           | Synchronous                  | Greater of:<br>20 ns or<br>(Tcy + 20)/N | _    | _       | ns    | Must also meet<br>Parameter TB15<br>N = prescale<br>value (1, 8, 64, 256) |

| TB11   | ΤτxL      | TxCK Low Time                                            | Synchronous                  | Greater of:<br>20 ns or<br>(Tcy + 20)/N | _    | _       | ns    | Must also meet<br>Parameter TB15<br>N = prescale<br>value (1, 8, 64, 256) |

| TB15   | ΤτχΡ      | TxCK Input Period                                        | Synchronous,<br>no prescaler | Tcy + 40                                | -    | —       | ns    | N = prescale<br>value (1, 8, 64, 256)                                     |

|        |           |                                                          | Synchronous, with prescaler  | Greater of:<br>20 ns or<br>(Tcy + 40)/N |      |         |       |                                                                           |

| TB20   | TCKEXTMRL | Delay from Externa<br>Edge to Timer Incre                |                              | 0.5 TCY                                 | _    | 1.5 TCY | _     |                                                                           |

#### TABLE 25-24: TIMER2 EXTERNAL CLOCK TIMING REQUIREMENTS

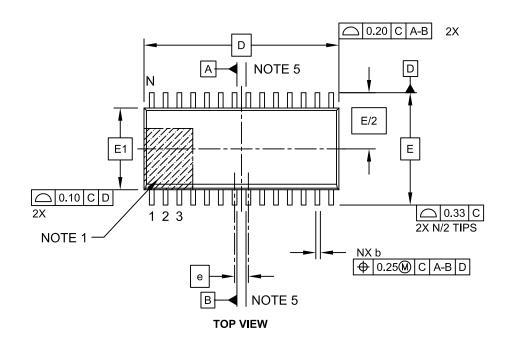

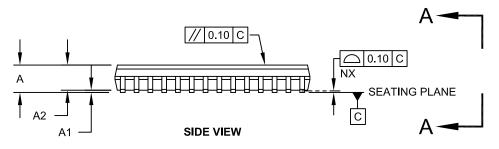

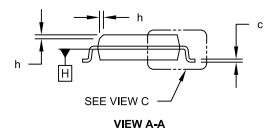

### 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-052C Sheet 1 of 2

| RPINR7 (Peripheral Pin Select Input 7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 157                                                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RPOR0 (Peripheral Pin Select Output 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 168                                                                                                                                                                                                          |

| RPOR1 (Peripheral Pin Select Output 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 168                                                                                                                                                                                                          |

| RPOR16 (Peripheral Pin Select Output 16)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                              |

| RPOR17 (Peripheral Pin Select Output 17)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                              |

| RPOR2 (Peripheral Pin Select Output 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 169                                                                                                                                                                                                          |

| RPOR3 (Peripheral Pin Select Output 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                              |