#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 9КВ (3К х 24)                                                                    |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 8x10b; D/A 2x10b                                                             |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj09gs302t-i-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

# Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

# Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

# **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

|                                |                                                            | #0 DE00             | RIPTION                  |                                                                                                                                                                                                      |

|--------------------------------|------------------------------------------------------------|---------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                       | Pin NamePin<br>TypeBuffer<br>TypePPS<br>CapableDescription |                     |                          |                                                                                                                                                                                                      |

| AN0-AN7                        | I                                                          | Analog              | No                       | Analog input channels.                                                                                                                                                                               |

| CLKI                           | I                                                          | ST/CMOS             | No                       | External clock source input. Always associated with OSC1 pin                                                                                                                                         |

| CLKO                           | 0                                                          | _                   | No                       | function.<br>Oscillator crystal output. Connects to crystal or resonator in Crysta<br>Oscillator mode. Optionally functions as CLKO in RC and EC<br>modes. Always associated with OSC2 pin function. |

| OSC1                           | I                                                          | ST/CMOS             | No                       | Oscillator crystal input. ST buffer when configured in RC mode;                                                                                                                                      |

| OSC2                           | I/O                                                        | _                   | No                       | CMOS otherwise.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC<br>modes.                                    |

| CN0-CN15                       | I                                                          | ST                  | No                       | Change notification inputs. Can be software programmed for internal weak pull-ups on all inputs.                                                                                                     |

| IC1                            | I                                                          | ST                  | Yes                      | Capture Input 1.                                                                                                                                                                                     |

| OCFA<br>OC1                    | I<br>O                                                     | ST<br>—             | Yes<br>Yes               | Compare Fault A input (for Compare Channel 1).<br>Compare Output 1.                                                                                                                                  |

| INT0<br>INT1<br>INT2           |                                                            | ST<br>ST<br>ST      | No<br>Yes<br>Yes         | External Interrupt 0.<br>External Interrupt 1.<br>External Interrupt 2.                                                                                                                              |

| RA0-RA4                        | I/O                                                        | ST                  | No                       | PORTA is a bidirectional I/O port.                                                                                                                                                                   |

| RB0-RB15 <sup>(1)</sup>        | I/O                                                        | ST                  | No                       | PORTB is a bidirectional I/O port.                                                                                                                                                                   |

| RP0-RP15 <sup>(1)</sup>        | I/O                                                        | ST                  | No                       | Remappable I/O pins.                                                                                                                                                                                 |

| T1CK<br>T2CK                   |                                                            | ST<br>ST            | Yes<br>Yes               | Timer1 external clock input.<br>Timer2 external clock input.                                                                                                                                         |

| U1CTS<br>U1RTS<br>U1RX<br>U1TX | <br>0<br> <br>0                                            | ST<br>—<br>ST<br>—  | Yes<br>Yes<br>Yes<br>Yes | UART1 Clear-to-Send.<br>UART1 Ready-to-Send.<br>UART1 receive.<br>UART1 transmit.                                                                                                                    |

| SCK1<br>SDI1<br>SDO1<br>SS1    | I/O<br>I<br>O<br>I/O                                       | ST<br>ST<br>—<br>ST | Yes<br>Yes<br>Yes<br>Yes | Synchronous serial clock input/output for SPI1.<br>SPI1 data in.<br>SPI1 data out.<br>SPI1 slave synchronization or frame pulse I/O.                                                                 |

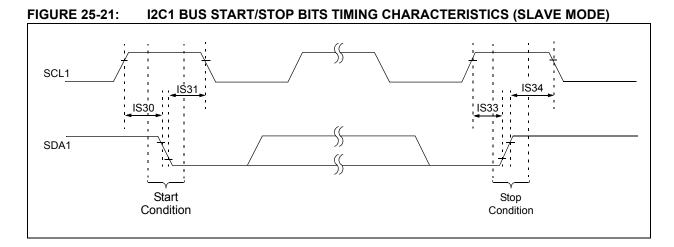

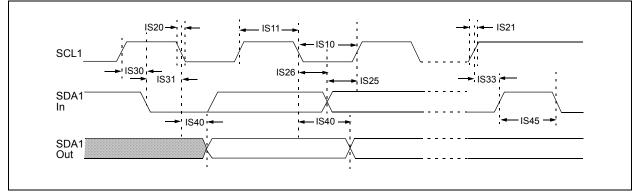

| SCL1<br>SDA1                   | I/O<br>I/O                                                 | ST<br>ST            | No<br>No                 | Synchronous serial clock input/output for I2C1.<br>Synchronous serial data input/output for I2C1.                                                                                                    |

| TMS<br>TCK<br>TDI<br>TDO       | <br> <br> <br> <br>0                                       | TTL<br>TTL<br>TTL   | No<br>No<br>No<br>No     | JTAG Test mode select pin.<br>JTAG test clock input pin.<br>JTAG test data input pin.<br>JTAG test data output pin.                                                                                  |

# TABLE 1-1:PINOUT I/O DESCRIPTIONS

ST = Schmitt Trigger input with CMOS levels<br/>TTL = Transistor-Transistor LogicP = PowerO = OutputPPS = Peripheral Pin Select— = Does not applyNote 1:Not all pins are available on all devices. Refer to the specific device in the "Pin Diagrams" section for

availability.2: This pin is available on dsPIC33FJ09GS302 devices only.

NOTES:

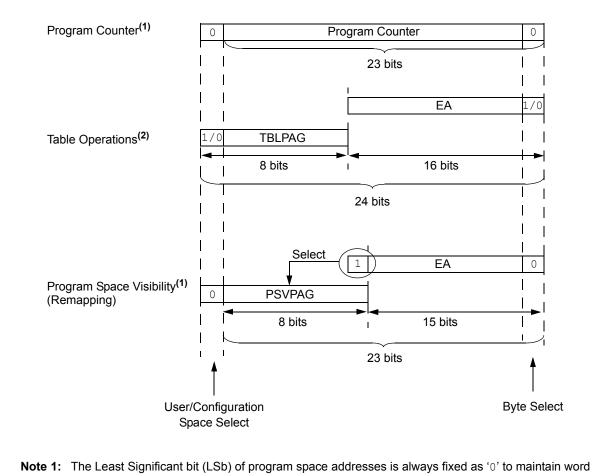

# 4.7 Interfacing Program and Data Memory Spaces

The device architecture uses a 24-bit wide program space and a 16-bit wide data space. The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the device architecture provides two methods by which program space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the program space

- Remapping a portion of the program space into the data space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look ups from a large table of static data. The application can only access the least significant word of the program word.

# 4.7.1 ADDRESSING PROGRAM SPACE

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Page register (TBLPAG) is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the Most Significant bit of TBLPAG is used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

For remapping operations, the 8-bit Program Space Visibility Register (PSVPAG) is used to define a 16K word page in the program space. When the Most Significant bit of the EA is '1', PSVPAG is concatenated with the lower 15 bits of the EA to form a 23-bit program space address. Unlike table operations, this limits remapping operations strictly to the user memory area.

Table 4-41 and Figure 4-8 show how the program EA is created for table operations and remapping accesses from the data EA. Here, P<23:0> refers to a program space word, and D<15:0> refers to a data space word.

|                          | Access                           | Program Space Address         |            |                                    |                    |       |  |

|--------------------------|----------------------------------|-------------------------------|------------|------------------------------------|--------------------|-------|--|

| Access Type              | Space                            | <23>                          | <22:16>    | <15>                               | <14:1>             | <0>   |  |

| Instruction Access       | struction Access User 0 PC<22:1> |                               |            | 0                                  |                    |       |  |

| (Code Execution)         |                                  |                               | 0xx xxxx x |                                    | x xxxx xxx0        |       |  |

| TBLRD/TBLWT              | User                             | TBLPAG<7:0>                   |            | Data EA<15:0>                      |                    |       |  |

| (Byte/Word Read/Write)   |                                  | 0xxx xxxx xxxx xxxx xxxx      |            |                                    |                    |       |  |

|                          | Configuration                    | TB                            | LPAG<7:0>  | Data EA<15:0>                      |                    |       |  |

|                          |                                  | 1xxx xxxx xxxx xxxx xxxx xxxx |            |                                    |                    |       |  |

| Program Space Visibility | User                             | 0                             | PSVPAG<7   | <7:0> Data EA<14:0> <sup>(1)</sup> |                    | 0>(1) |  |

| (Block Remap/Read)       |                                  | 0                             | XXXX XXXX  |                                    | XXX XXXX XXXX XXXX |       |  |

# TABLE 4-41: PROGRAM SPACE ADDRESS CONSTRUCTION

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

#### FIGURE 4-8: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

- alignment of data in the program and data spaces.

- 2: Table operations are not required to be word-aligned. Table read operations are permitted in the configuration memory space.

| U-0          | R/W-1                                                          | R/W-0                                                                           | R/W-0          | U-0                    | R/W-1            | R/W-0           | R/W-0 |  |  |  |  |

|--------------|----------------------------------------------------------------|---------------------------------------------------------------------------------|----------------|------------------------|------------------|-----------------|-------|--|--|--|--|

| —            | U1RXIP<2:0> <sup>(1)</sup> — SPI1IP<2                          |                                                                                 |                |                        | SPI1IP<2:0>(1)   |                 |       |  |  |  |  |

| oit 15       |                                                                |                                                                                 |                |                        |                  |                 | bit   |  |  |  |  |

|              |                                                                |                                                                                 |                |                        |                  |                 |       |  |  |  |  |

| U-0          | R/W-1                                                          | R/W-0                                                                           | R/W-0          | U-0                    | U-0              | U-0             | U-0   |  |  |  |  |

|              |                                                                | SPI1EIP<2:0>(1)                                                                 | )              | —                      |                  | —               | _     |  |  |  |  |

| bit 7        |                                                                |                                                                                 |                |                        |                  |                 | bit   |  |  |  |  |

|              |                                                                |                                                                                 |                |                        |                  |                 |       |  |  |  |  |

| Legend:      |                                                                |                                                                                 |                |                        |                  |                 |       |  |  |  |  |

| R = Readab   | le bit                                                         | W = Writable b                                                                  | oit            | U = Unimpler           | nented bit, read | d as '0'        |       |  |  |  |  |

| -n = Value a | t POR                                                          | '1' = Bit is set                                                                |                | '0' = Bit is cle       | ared             | x = Bit is unkn | own   |  |  |  |  |

|              |                                                                |                                                                                 |                |                        |                  |                 |       |  |  |  |  |

| bit 15       | Unimplem                                                       | ented: Read as 'o                                                               | )'             |                        |                  |                 |       |  |  |  |  |

| bit 14-12    | U1RXIP<2:                                                      | <b>U1RXIP&lt;2:0&gt;:</b> UART1 Receiver Interrupt Priority bits <sup>(1)</sup> |                |                        |                  |                 |       |  |  |  |  |

|              | 111 = Inter                                                    | 111 = Interrupt is Priority 7 (highest priority interrupt)                      |                |                        |                  |                 |       |  |  |  |  |

|              | •                                                              |                                                                                 |                |                        |                  |                 |       |  |  |  |  |

|              |                                                                |                                                                                 |                |                        |                  |                 |       |  |  |  |  |

|              | •<br>001 = Interrupt is Priority 1                             |                                                                                 |                |                        |                  |                 |       |  |  |  |  |

|              |                                                                | rupt source is disa                                                             | abled          |                        |                  |                 |       |  |  |  |  |

| bit 11       | Unimplem                                                       | ented: Read as 'o                                                               | )'             |                        |                  |                 |       |  |  |  |  |

| bit 10-8     | SPI1IP<2:0>: SPI1 Event Interrupt Priority bits <sup>(1)</sup> |                                                                                 |                |                        |                  |                 |       |  |  |  |  |

|              | 111 = Interrupt is Priority 7 (highest priority interrupt)     |                                                                                 |                |                        |                  |                 |       |  |  |  |  |

|              | •                                                              | •                                                                               |                |                        |                  |                 |       |  |  |  |  |

|              | •                                                              | •                                                                               |                |                        |                  |                 |       |  |  |  |  |

|              | 001 = Inter                                                    | •<br>001 = Interrupt is Priority 1                                              |                |                        |                  |                 |       |  |  |  |  |

|              |                                                                | rupt source is disa                                                             | abled          |                        |                  |                 |       |  |  |  |  |

| bit 7        | Unimplem                                                       | ented: Read as 'o                                                               | )'             |                        |                  |                 |       |  |  |  |  |

| bit 6-4      | SPI1EIP<2                                                      | :0>: SPI1 Error In                                                              | terrupt Priori | ty bits <sup>(1)</sup> |                  |                 |       |  |  |  |  |

|              | 111 = Inter                                                    | 111 = Interrupt is Priority 7 (highest priority interrupt)                      |                |                        |                  |                 |       |  |  |  |  |

|              | •                                                              |                                                                                 |                |                        |                  |                 |       |  |  |  |  |

|              | •                                                              |                                                                                 |                |                        |                  |                 |       |  |  |  |  |

|              |                                                                | rupt is Priority 1<br>rupt source is disa                                       | abled          |                        |                  |                 |       |  |  |  |  |

|              |                                                                | •                                                                               |                |                        |                  |                 |       |  |  |  |  |

# Note 1: These bits are not implemented in the dsPIC33FJ06GS001 device.

| REGISTER      | 9-5: PMD6                                                                                                 | : PERIPHER                       | AL MODULE      | E DISABLE C                             | ONTROL RE       | GISTER 6              |        |

|---------------|-----------------------------------------------------------------------------------------------------------|----------------------------------|----------------|-----------------------------------------|-----------------|-----------------------|--------|

| U-0           | U-0                                                                                                       | U-0                              | U-0            | R/W-0                                   | U-0             | R/W-0                 | R/W-0  |

| _             | _                                                                                                         | —                                |                | PWM4MD <sup>(1)</sup>                   | —               | PWM2MD <sup>(2)</sup> | PWM1MD |

| bit 15        |                                                                                                           |                                  |                |                                         |                 |                       | bit 8  |

| U-0           | U-0                                                                                                       | U-0                              | U-0            | U-0                                     | U-0             | U-0                   | U-0    |

|               |                                                                                                           |                                  |                | <u> </u>                                |                 |                       |        |

| bit 7         |                                                                                                           |                                  |                |                                         |                 |                       | bit 0  |

| Legend:       |                                                                                                           |                                  |                |                                         |                 |                       |        |

| R = Readable  | e bit                                                                                                     | W = Writable                     | bit            | U = Unimplem                            | ented bit, read | d as '0'              |        |

| -n = Value at | POR                                                                                                       | '1' = Bit is set                 |                | '0' = Bit is cleared x = Bit is unknown |                 |                       | own    |

| bit 15-12     | Unimplomon                                                                                                | ted: Read as '                   | ۰,             |                                         |                 |                       |        |

| bit 11        | •                                                                                                         | NM Generator                     |                | able bit(1)                             |                 |                       |        |

|               | 1 = PWM Ger                                                                                               | nerator 4 modu<br>nerator 4 modu | le is disabled |                                         |                 |                       |        |

| bit 10        | Unimplement                                                                                               | ted: Read as '                   | )'             |                                         |                 |                       |        |

| bit 9         | PWM2MD: PV                                                                                                | WM Generator                     | 2 Module Disa  | able bit <sup>(2)</sup>                 |                 |                       |        |

|               | <ul> <li>1 = PWM Generator 2 module is disabled</li> <li>0 = PWM Generator 2 module is enabled</li> </ul> |                                  |                |                                         |                 |                       |        |

| bit 8         | PWM1MD: PV                                                                                                | WM Generator                     | 1 Module Disa  | able bit                                |                 |                       |        |

|               |                                                                                                           | nerator 1 modu<br>nerator 1 modu |                |                                         |                 |                       |        |

| bit 7-0       | Unimplement                                                                                               | ted: Read as '                   | )'             |                                         |                 |                       |        |

**Note 1:** This bit is not implemented in dsPIC33FJ06GS102A/202A devices.

**2:** This bit is not implemented in dsPIC33FJ06GS001/101A devices.

| U-0             | U-0 | R/W-0            | R/W-0                    | R/W-0            | R/W-0           | R/W-0           | R/W-0 |  |

|-----------------|-----|------------------|--------------------------|------------------|-----------------|-----------------|-------|--|

| —               | _   |                  | RP9R<5:0> <sup>(1)</sup> |                  |                 |                 |       |  |

| bit 15          |     |                  |                          |                  |                 |                 | bit 8 |  |

|                 |     |                  |                          |                  |                 |                 |       |  |

| U-0             | U-0 | R/W-0            | R/W-0                    | R/W-0            | R/W-0           | R/W-0           | R/W-0 |  |

|                 | _   |                  | RP8R<5:0> <sup>(1)</sup> |                  |                 |                 |       |  |

| bit 7           |     |                  |                          |                  |                 |                 | bit 0 |  |

|                 |     |                  |                          |                  |                 |                 |       |  |

| Legend:         |     |                  |                          |                  |                 |                 |       |  |

| R = Readable    | bit | W = Writable     | bit                      | U = Unimpler     | nented bit, rea | d as '0'        |       |  |

| -n = Value at F | POR | '1' = Bit is set |                          | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |  |

# **REGISTER 10-20: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4**

| bit 15-14 | Unimplemented: Read as '0'                                                                           |

|-----------|------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP9R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP9 Output Pin bits <sup>(1)</sup> |

|           | (see Table 10-2 for peripheral function numbers)                                                     |

| bit 7-6   | Unimplemented: Read as '0'                                                                           |

| bit 5-0   | <b>RP8R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP8 Output Pin bits <sup>(1)</sup> |

|           | (see Table 10-2 for peripheral function numbers)                                                     |

Note 1: These bits are not implemented in dsPIC33FJ06GS001/101A devices.

# **REGISTER 10-21: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5**

| U-0    | U-0 | R/W-0                     | R/W-0                     | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|---------------------------|---------------------------|-------|-------|-------|-------|

| —      |     | RP11R<5:0> <sup>(1)</sup> |                           |       |       |       |       |

| bit 15 |     |                           |                           |       |       |       | bit 8 |

|        |     |                           |                           |       |       |       |       |

| U-0    | U-0 | R/W-0                     | R/W-0                     | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|        |     |                           | RP10R<5:0> <sup>(1)</sup> |       |       |       |       |

| bit 7  |     |                           |                           |       |       |       | bit 0 |

|        |     |                           |                           |       |       |       |       |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

- RP11R<5:0>: Peripheral Output Function is Assigned to RP11 Output Pin bits<sup>(1)</sup> bit 13-8 (see Table 10-2 for peripheral function numbers) bit 7-6 Unimplemented: Read as '0'

- RP10R<5:0>: Peripheral Output Function is Assigned to RP10 Output Pin bits<sup>(1)</sup> bit 5-0 (see Table 10-2 for peripheral function numbers)

Note 1: These bits are not implemented in dsPIC33FJ06GS001/101A devices.

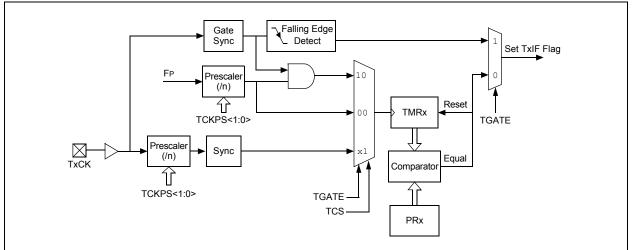

# 12.0 TIMER2 FEATURES

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS001/101A/102A/ 202A and dsPIC33FJ09GS302 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 11. "Timers"** (DS70205) in the *"dsPIC33F/PIC24H Family Reference Manual"*, which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Timer2 is a Type B timer with an external clock input (TxCK) that is always synchronized to the internal device clock and the clock synchronization is performed after the prescaler.

The Timer2 module can operate in one of the following modes:

- Timer mode

- Gated Timer mode

- Synchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FCY). In Synchronous Counter mode, the input clock is derived from the external clock input at the TxCK pin.

The Timer modes are determined by the following bits:

- TCS (TxCON<1>): Timer Clock Source Control bit

- TGATE (TxCON<6>): Timer Gate Control bit

The Timer control bit settings for different operating modes are given in Table 12-1.

| TABLE 12-1: TIMER MODE SETTINGS | TABLE 12-1: | TIMER MODE SETTINGS |

|---------------------------------|-------------|---------------------|

|---------------------------------|-------------|---------------------|

| Mode                | TCS | TGATE |

|---------------------|-----|-------|

| Timer               | 0   | 0     |

| Gated Timer         | 0   | 1     |

| Synchronous Counter | 1   | х     |

# 12.1 16-Bit Operation

To configure any of the timers for individual 16-bit operation:

- 1. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 2. Set the Clock and Gating modes using the TCS and TGATE bits.

- 3. Load the Timer Period value into the PRx register.

- 4. If interrupts are required, set the Timerx Interrupt Enable bit, TxIE. Use the priority bits, TxIP<2:0>, to set the interrupt priority.

- 5. Set the TON bit.

# FIGURE 12-1: TYPE B TIMER BLOCK DIAGRAM (x = 2)

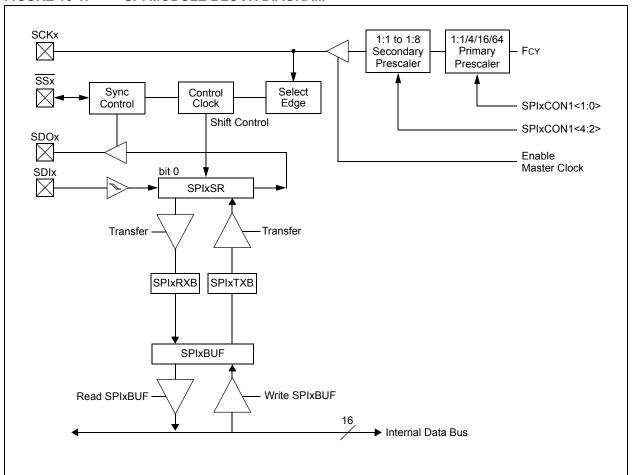

# 16.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ06GS001/101A/102A/ 202A and dsPIC33FJ09GS302 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 18. "Serial Peripheral Interface (SPI)" (DS70206) of the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, Analog-to-Digital Converters, etc. The SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP.

Each SPI module consists of a 16-bit shift register, SPIxSR (where x = 1 or 2), used for shifting data in and out, and a buffer register, SPIxBUF. A control register, SPIxCON, configures the module. Additionally, a status register, SPIxSTAT, indicates status conditions.

The serial interface consists of 4 pins:

- · SDIx (serial data input)

- · SDOx (serial data output)

- · SCKx (shift clock input or output)

- SSx (active-low slave select)

In Master mode operation, SCKx is a clock output; in Slave mode, it is a clock input.

# FIGURE 16-1: SPI MODULE BLOCK DIAGRAM

| U-0                 | U-0                                                                                                                                                                                                                                    | U-0                                   | R/W-0            | R/W-0                   | R/W-0            | R/W-0           | R/W-0              |  |  |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------|-------------------------|------------------|-----------------|--------------------|--|--|--|

| —                   | _                                                                                                                                                                                                                                      |                                       | DISSCK           | DISSDO                  | MODE16           | SMP             | CKE <sup>(1)</sup> |  |  |  |

| pit 15              |                                                                                                                                                                                                                                        |                                       |                  |                         |                  |                 | bit                |  |  |  |

|                     | DAMO                                                                                                                                                                                                                                   | DAMA                                  | DAMA             | DAALO                   | DAMA             | DAMA            | <b>D</b> 444 0     |  |  |  |

| R/W-0               | R/W-0                                                                                                                                                                                                                                  | R/W-0                                 | R/W-0            | R/W-0                   | R/W-0            | R/W-0           | R/W-0              |  |  |  |

| SSEN <sup>(3)</sup> | CKP                                                                                                                                                                                                                                    | MSTEN                                 |                  | SPRE<2:0> <sup>(2</sup> | -)               | PPRE<           | :1:0> <b>(2)</b>   |  |  |  |

| pit 7               |                                                                                                                                                                                                                                        |                                       |                  |                         |                  |                 | bit                |  |  |  |

| _egend:             |                                                                                                                                                                                                                                        |                                       |                  |                         |                  |                 |                    |  |  |  |

| R = Readable        | bit                                                                                                                                                                                                                                    | W = Writable                          | bit              | U = Unimpler            | nented bit, read | as '0'          |                    |  |  |  |

| n = Value at l      | POR                                                                                                                                                                                                                                    | '1' = Bit is set                      | :                | '0' = Bit is cle        | ared             | x = Bit is unkr | iown               |  |  |  |

|                     |                                                                                                                                                                                                                                        |                                       |                  |                         |                  |                 |                    |  |  |  |

| oit 15-13           | Unimplemen                                                                                                                                                                                                                             | ted: Read as '                        | 0'               |                         |                  |                 |                    |  |  |  |

| oit 12              | DISSCK: Dis                                                                                                                                                                                                                            | able SCKx Pin                         | bit (SPI Maste   | er modes only)          |                  |                 |                    |  |  |  |

|                     | 1 = Internal S                                                                                                                                                                                                                         | SPI clock is disa                     | abled; pin func  | tions as I/O            |                  |                 |                    |  |  |  |

|                     | 0 = Internal SPI clock is enabled                                                                                                                                                                                                      |                                       |                  |                         |                  |                 |                    |  |  |  |

| pit 11              |                                                                                                                                                                                                                                        | DISSDO: Disable SDOx Pin bit          |                  |                         |                  |                 |                    |  |  |  |

|                     | <ul> <li>1 = SDOx pin is not used by module; pin functions as I/O</li> <li>0 = SDOx pin is controlled by the module</li> </ul>                                                                                                         |                                       |                  |                         |                  |                 |                    |  |  |  |

|                     | •                                                                                                                                                                                                                                      |                                       | •                |                         |                  |                 |                    |  |  |  |

| oit 10              | MODE16: Word/Byte Communication Select bit                                                                                                                                                                                             |                                       |                  |                         |                  |                 |                    |  |  |  |

|                     | <ol> <li>Communication is word-wide (16 bits)</li> <li>Communication is byte-wide (8 bits)</li> </ol>                                                                                                                                  |                                       |                  |                         |                  |                 |                    |  |  |  |

| oit 9               |                                                                                                                                                                                                                                        | SMP: SPIx Data Input Sample Phase bit |                  |                         |                  |                 |                    |  |  |  |

|                     | Master mode                                                                                                                                                                                                                            |                                       |                  |                         |                  |                 |                    |  |  |  |

|                     |                                                                                                                                                                                                                                        | <u>.</u><br>a is sampled at           | end of data o    | utput time              |                  |                 |                    |  |  |  |

|                     | 0 = Input data is sampled at middle of data output time                                                                                                                                                                                |                                       |                  |                         |                  |                 |                    |  |  |  |

|                     | Slave mode:                                                                                                                                                                                                                            |                                       |                  |                         |                  |                 |                    |  |  |  |

|                     | SMP must be cleared when SPIx is used in Slave mode.                                                                                                                                                                                   |                                       |                  |                         |                  |                 |                    |  |  |  |

| oit 8               |                                                                                                                                                                                                                                        | lock Edge Sele                        |                  | <b>,</b> ,,             |                  |                 | 1.11.02            |  |  |  |

|                     | <ul> <li>1 = Serial output data changes on transition from active clock state to Idle clock state (see bit 6)</li> <li>0 = Serial output data changes on transition from Idle clock state to active clock state (see bit 6)</li> </ul> |                                       |                  |                         |                  |                 |                    |  |  |  |

| oit 7               |                                                                                                                                                                                                                                        |                                       |                  |                         |                  |                 |                    |  |  |  |

|                     | <b>SSEN:</b> Slave Select Enable bit (Slave mode) <sup>(3)</sup><br>1 = SSx pin is used for Slave mode                                                                                                                                 |                                       |                  |                         |                  |                 |                    |  |  |  |

|                     | 1 = SSX pin is used for Slave mode<br>0 = SSx pin is not used by module; pin is controlled by port function                                                                                                                            |                                       |                  |                         |                  |                 |                    |  |  |  |

| oit 6               | <b>CKP:</b> Clock Polarity Select bit                                                                                                                                                                                                  |                                       |                  |                         |                  |                 |                    |  |  |  |

|                     | 1 = Idle state for clock is a high level; active state is a low level                                                                                                                                                                  |                                       |                  |                         |                  |                 |                    |  |  |  |

|                     | 0 = Idle state                                                                                                                                                                                                                         | for clock is a lo                     | ow level; active | e state is a higł       | n level          |                 |                    |  |  |  |

| oit 5               | MSTEN: Mas                                                                                                                                                                                                                             | ster Mode Enat                        | ole bit          |                         |                  |                 |                    |  |  |  |

|                     | 1 = Master m                                                                                                                                                                                                                           | ode                                   |                  |                         |                  |                 |                    |  |  |  |

|                     | 0 = Slave mo                                                                                                                                                                                                                           |                                       |                  |                         |                  |                 |                    |  |  |  |

# REGISTER 16-2: SPIXCON1: SPIX CONTROL REGISTER 1

- bit to '0' for the Framed SPI modes (FRMEN = SPI modes. Pr JYI ⊥).

- **2:** Do not set both Primary and Secondary prescalers to a value of 1:1.

- 3: This bit must be cleared when FRMEN = 1.

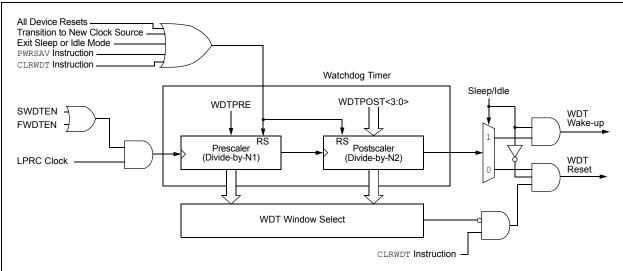

# 22.4 Watchdog Timer (WDT)

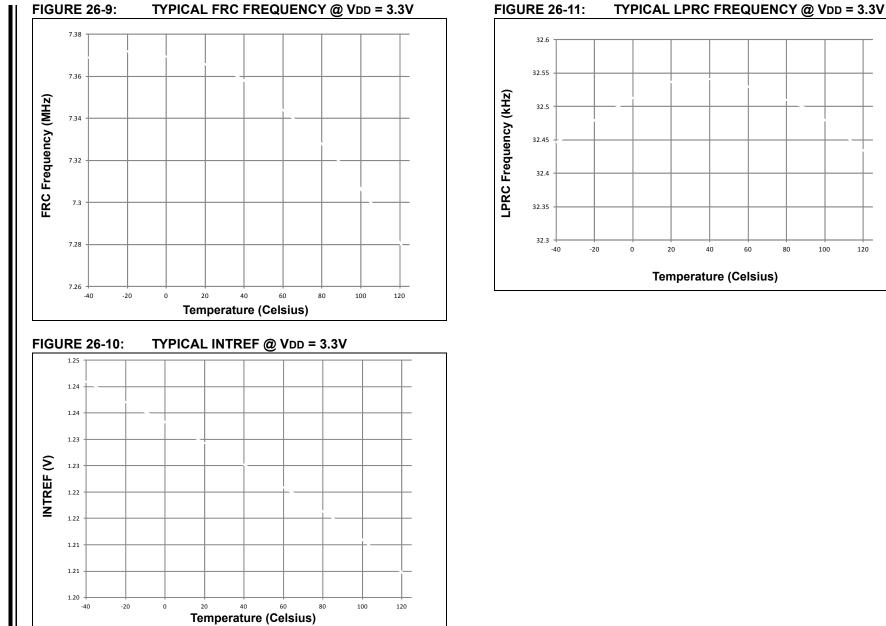

The Watchdog Timer (WDT) is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

### 22.4.1 PRESCALER/POSTSCALER

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit (FWDT<4>). With a 32 kHz input, the prescaler yields a nominal WDT time-out period (TWDT) of 1 ms in 5-bit mode or 4 ms in 7-bit mode.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>), which allow the selection of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods ranging from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSC<2:0> bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

## 22.4.2 SLEEP AND IDLE MODES

If the WDT is enabled, it will continue to run during Sleep or Idle modes. When the WDT time-out occurs, the device will wake the device and code execution will continue from where the PWRSAV instruction was executed. The corresponding SLEEP bit (RCON<3>) or IDLE bit (RCON<2>) will need to be cleared in software after the device wakes up.

#### 22.4.3 ENABLING WDT

The WDT is enabled or disabled by the FWDTEN Configuration bit in the FWDT Configuration register (FWDT<7>). When the FWDTEN Configuration bit is set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTEN Configuration bit has been programmed to '0'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user application to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

The WDT flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

# FIGURE 22-2: WDT BLOCK DIAGRAM

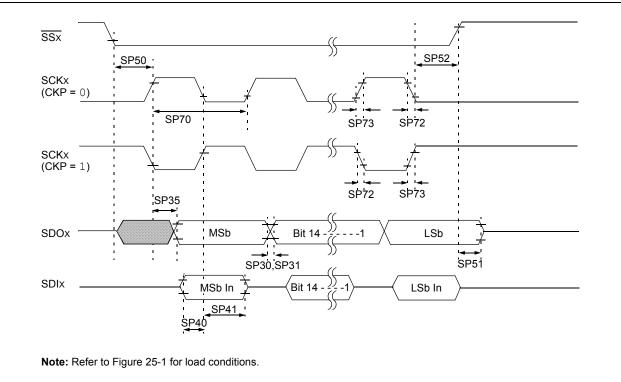

# TABLE 25-33:SPIx SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0)TIMING REQUIREMENTS

| АС СНА       |                       | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |              |                    |     |       |                                      |

|--------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------|-----|-------|--------------------------------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                                                                                                                                                       | Min          | Тур <sup>(2)</sup> | Max | Units | Conditions                           |

| SP70         | TscP                  | Maximum SCKx Input Frequency                                                                                                                                                                                                                                                        | _            | —                  | 15  | MHz   | See Note 3                           |

| SP72         | TscF                  | SCKx Input Fall Time                                                                                                                                                                                                                                                                | —            | _                  |     | ns    | See Parameter DO32 and <b>Note 4</b> |

| SP73         | TscR                  | SCKx Input Rise Time                                                                                                                                                                                                                                                                | —            | _                  |     | ns    | See Parameter DO31 and Note 4        |

| SP30         | TdoF                  | SDOx Data Output Fall Time                                                                                                                                                                                                                                                          | —            |                    |     | ns    | See Parameter DO32 and <b>Note 4</b> |

| SP31         | TdoR                  | SDOx Data Output Rise Time                                                                                                                                                                                                                                                          | —            | _                  |     | ns    | See Parameter DO31 and <b>Note 4</b> |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                                                                                                                                                                                                                           | —            | 6                  | 20  | ns    |                                      |

| SP36         | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                                                                                                                                                                                                                                        | 30           |                    | _   | ns    |                                      |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                                                                                                                                                                                                                                          | 30           | _                  |     | ns    |                                      |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input<br>to SCKx Edge                                                                                                                                                                                                                                        | 30           | _                  | _   | ns    |                                      |

| SP50         | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx Input                                                                                                                                                                                                                        | 120          |                    |     | ns    |                                      |

| SP51         | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance                                                                                                                                                                                                                                              | 10           | —                  | 50  | ns    | See Note 4                           |

| SP52         | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                                                                                                                                                                                                                                                 | 1.5 Tcy + 40 | —                  | _   | ns    | See Note 4                           |

| SP60         | TssL2doV              | SDOx Data Output Valid after                                                                                                                                                                                                                                                        | —            | _                  | 50  | ns    |                                      |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 66.7 ns. Therefore, the SCKx clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

NOTES:

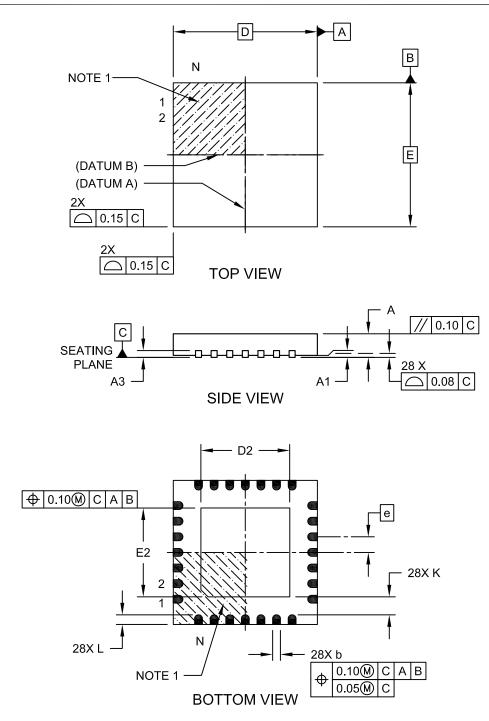

# 28-Lead Plastic Quad Flat, No Lead Package (MM) - 6x6x0.9mm Body [QFN-S] With 0.40 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-124C Sheet 1 of 2

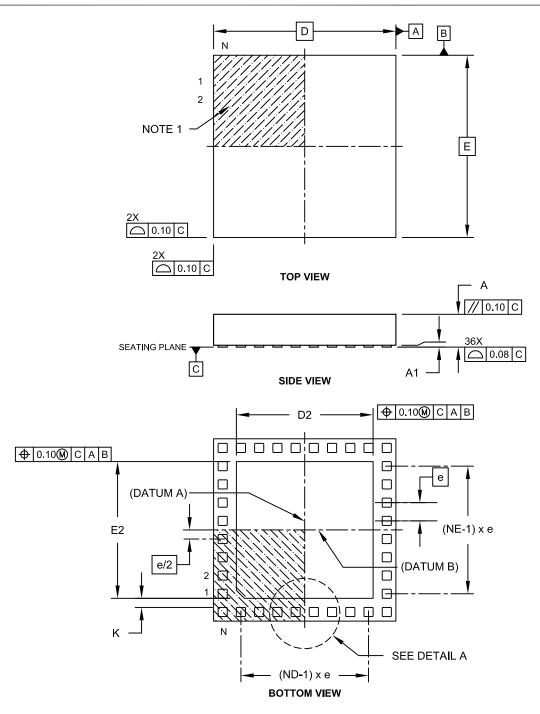

# 36-Terminal Very Thin Thermal Leadless Array Package (TL) – 5x5x0.9 mm Body with Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-187C Sheet 1 of 2

# **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| TO:<br>RE:                                                                   | Technical Publications Manager<br>Reader Response                                        | Total Pages Sent            |  |  |  |  |  |

|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------|--|--|--|--|--|

| From:                                                                        | Name                                                                                     |                             |  |  |  |  |  |

|                                                                              | Company<br>Address<br>City / State / ZIP / Country                                       |                             |  |  |  |  |  |

|                                                                              | Telephone: ()                                                                            | FAX: ()                     |  |  |  |  |  |

| Application (optional):                                                      |                                                                                          |                             |  |  |  |  |  |

| Would you like a reply?YN                                                    |                                                                                          |                             |  |  |  |  |  |

| Devic                                                                        | e: dsPIC33FJ06GS001/101A/102A/202A and<br>dsPIC33FJ09GS302                               | Literature Number: DS75018C |  |  |  |  |  |

| Quest                                                                        | tions:                                                                                   |                             |  |  |  |  |  |

| 1. W                                                                         | hat are the best features of this document?                                              |                             |  |  |  |  |  |

| 2. How does this document meet your hardware and software development needs? |                                                                                          |                             |  |  |  |  |  |

| 3. D                                                                         | Do you find the organization of this document easy to follow? If not, why?               |                             |  |  |  |  |  |

| 4. W                                                                         | What additions to the document do you think would enhance the structure and subject?     |                             |  |  |  |  |  |

| _                                                                            |                                                                                          |                             |  |  |  |  |  |

| 5. W                                                                         | What deletions from the document could be made without affecting the overall usefulness? |                             |  |  |  |  |  |

| _                                                                            |                                                                                          |                             |  |  |  |  |  |

| 6. Is                                                                        | Is there any incorrect or misleading information (what and where)?                       |                             |  |  |  |  |  |

| _                                                                            |                                                                                          |                             |  |  |  |  |  |

| 7. H                                                                         | ow would you improve this document?                                                      |                             |  |  |  |  |  |

| _                                                                            |                                                                                          |                             |  |  |  |  |  |

|                                                                              |                                                                                          |                             |  |  |  |  |  |